Изобретение относится к-вычислительной технике и может быть использовано для функционального контроля как отдельных корпусов микросхем оперативных запоминающих устройств (ОЗУ), так и построенных на их основе блоков полупроводниковых ОЗУ произвольной емкости и организации.

Цель изобретения - повышение достоверности контроля и расширение функциональных возможностей за счет обеспечения контроля памяти с раздельными и совмещенными входами-выходами, с трансляцией и без трансляции данных на выходы при записи.

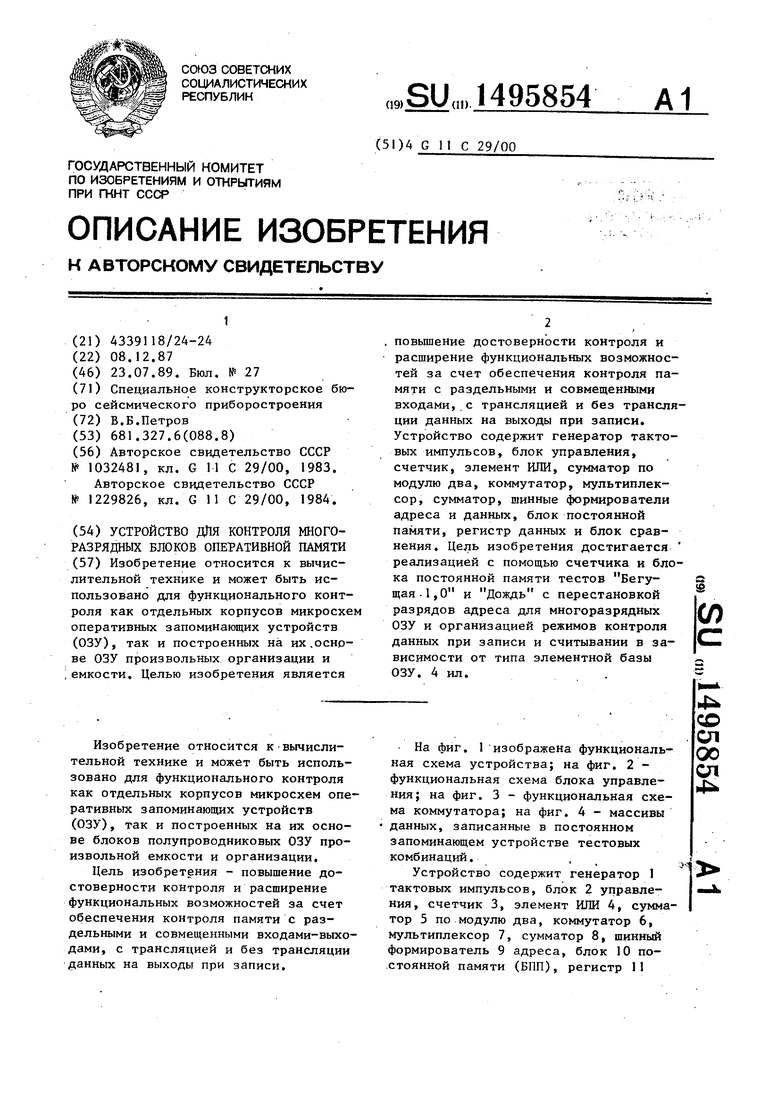

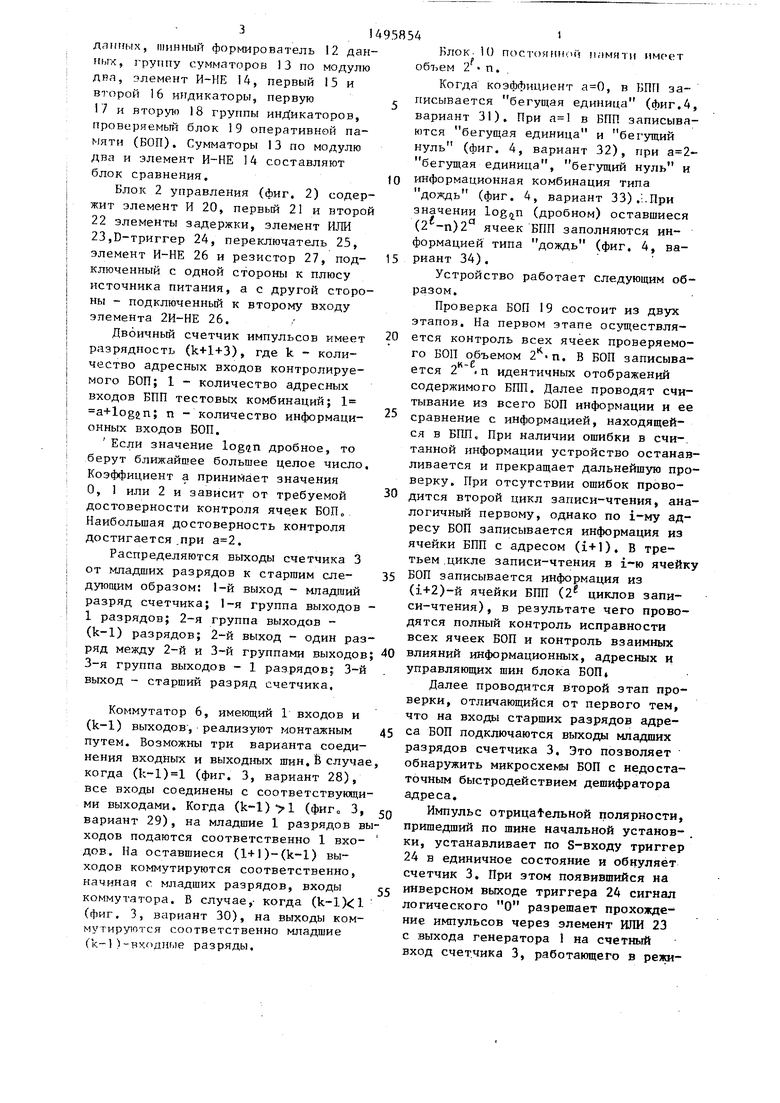

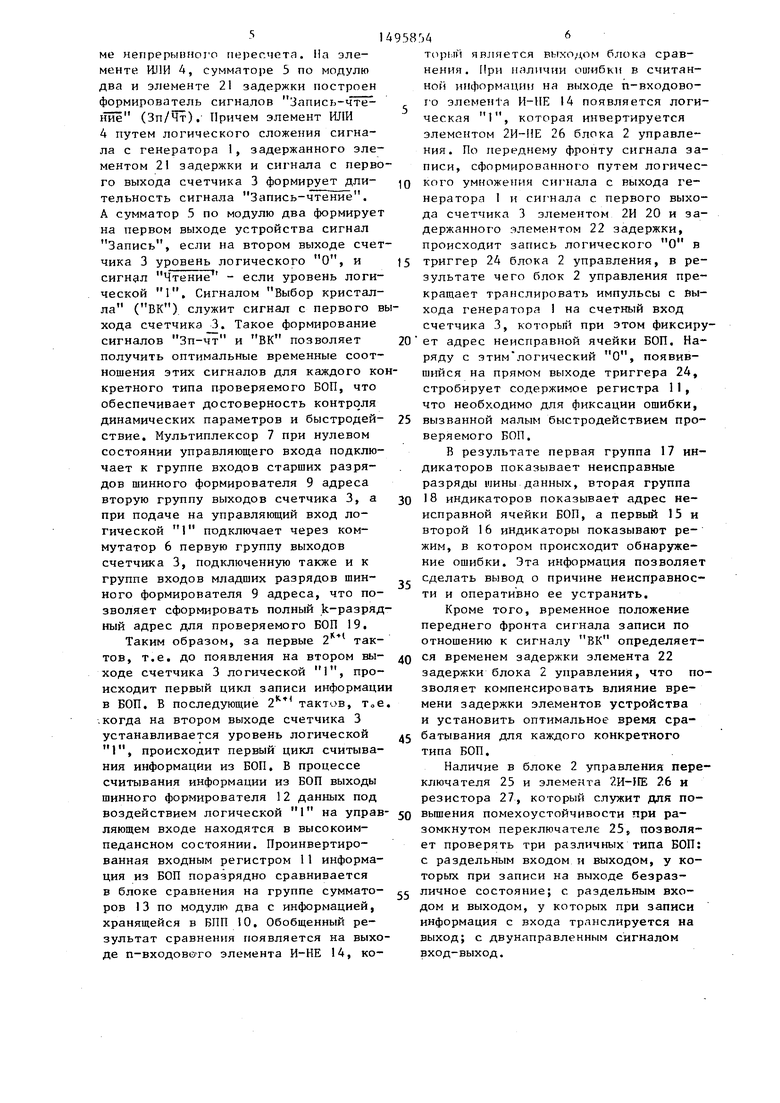

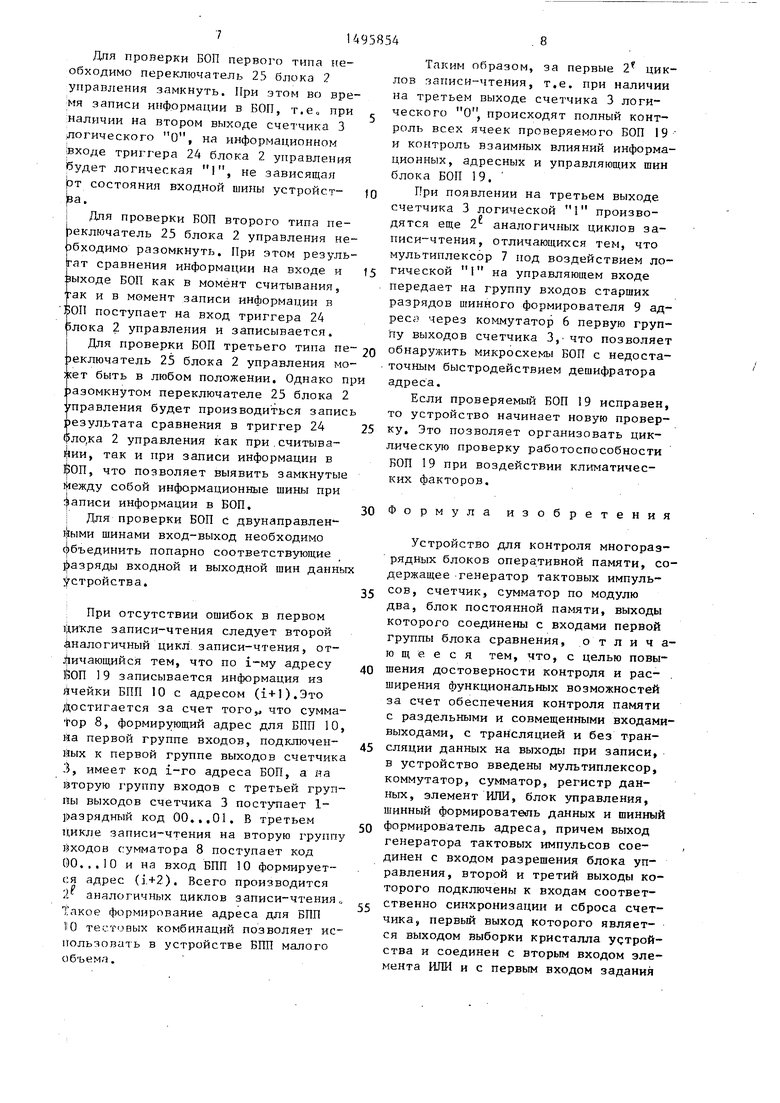

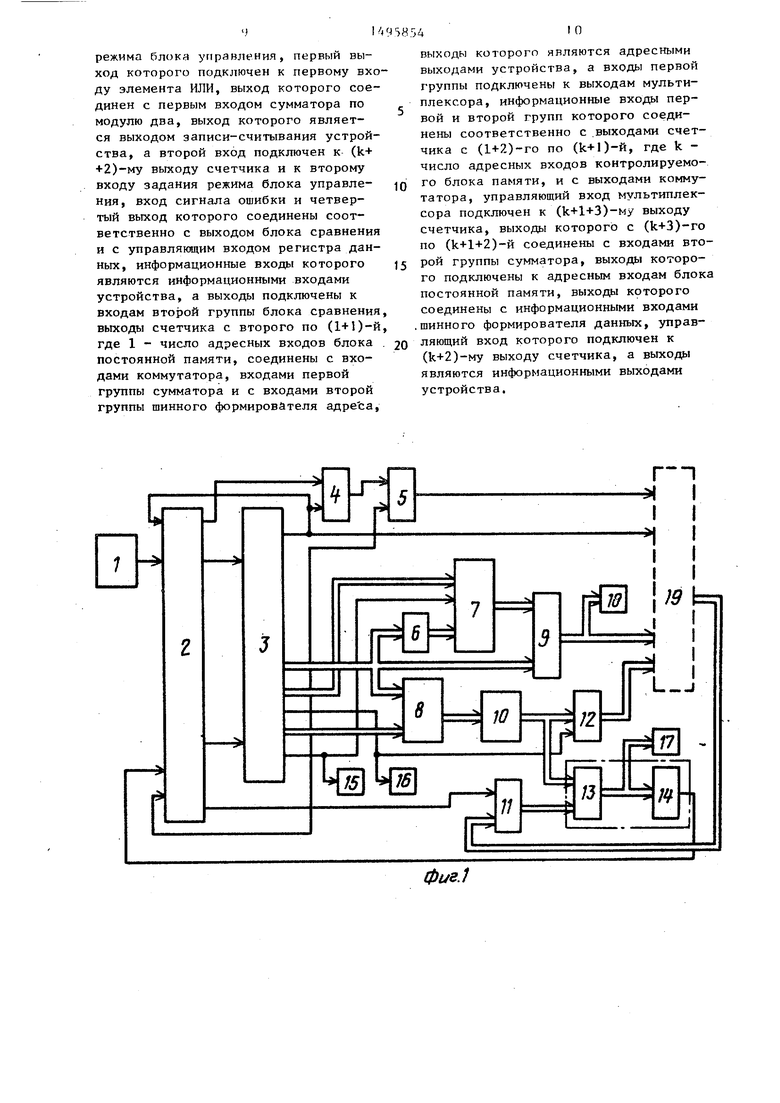

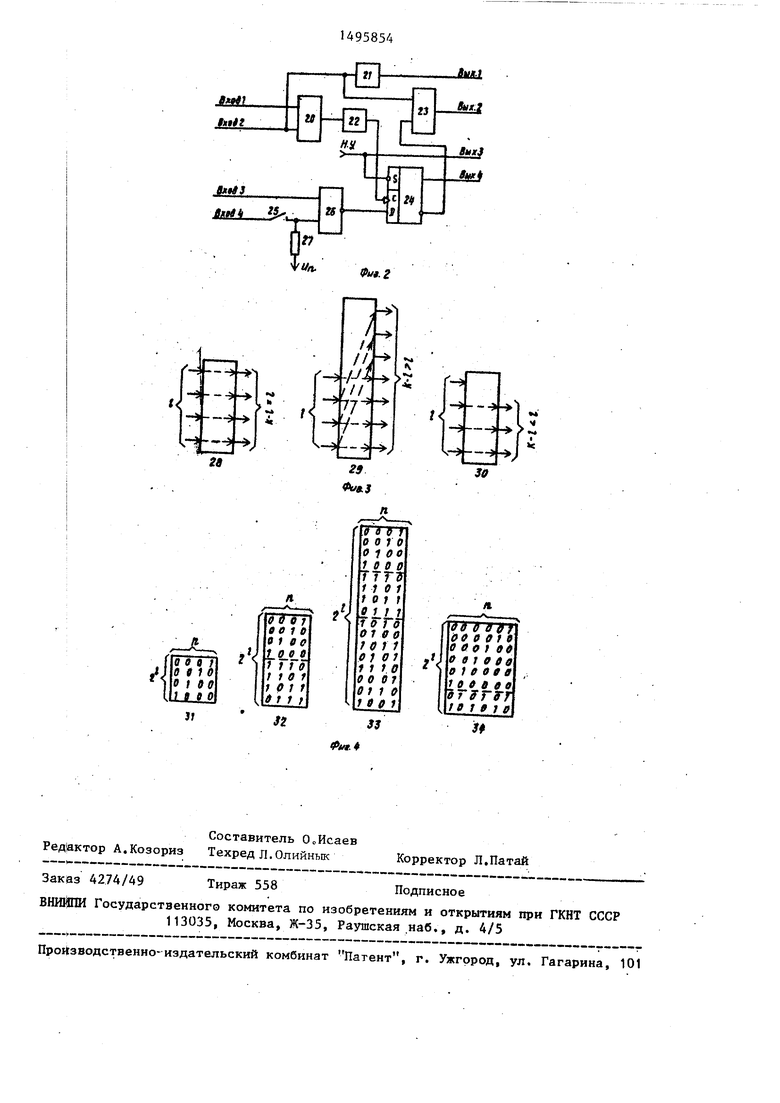

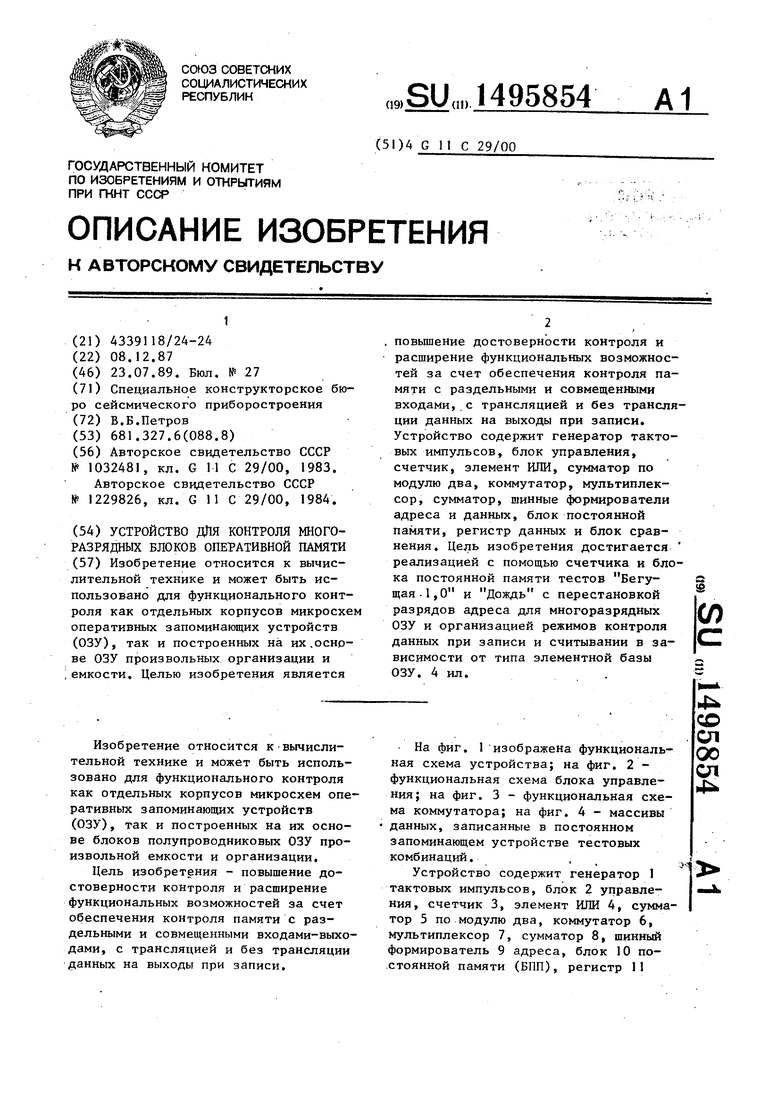

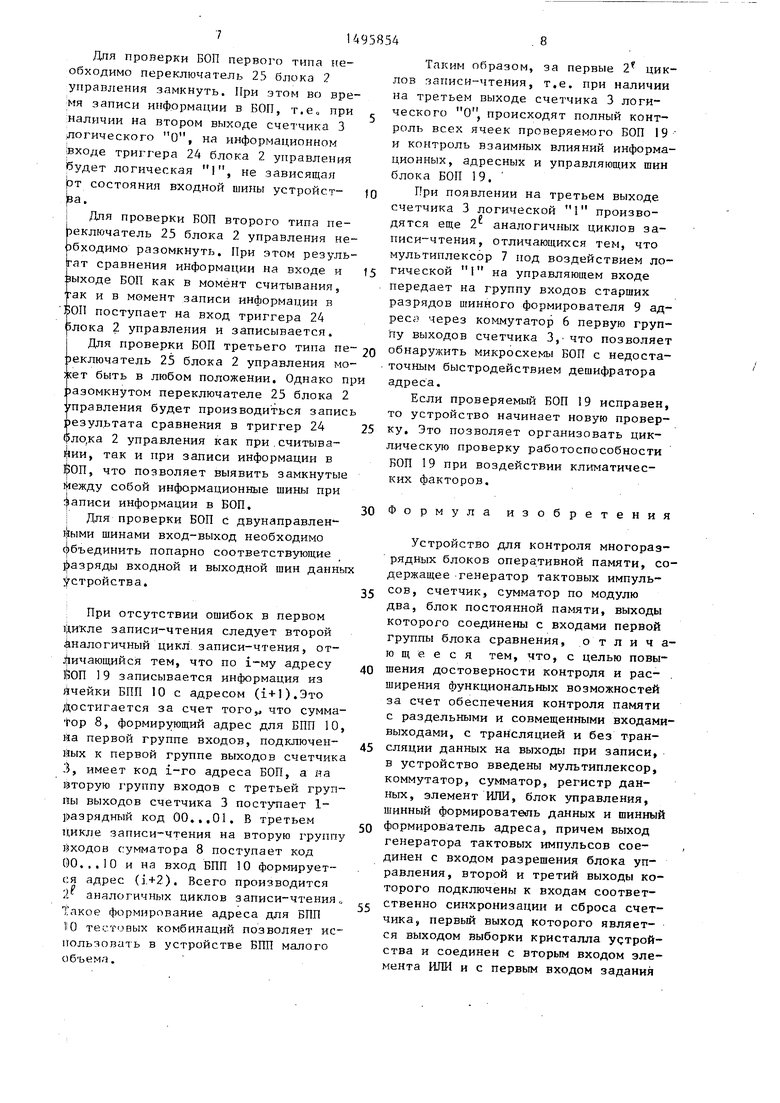

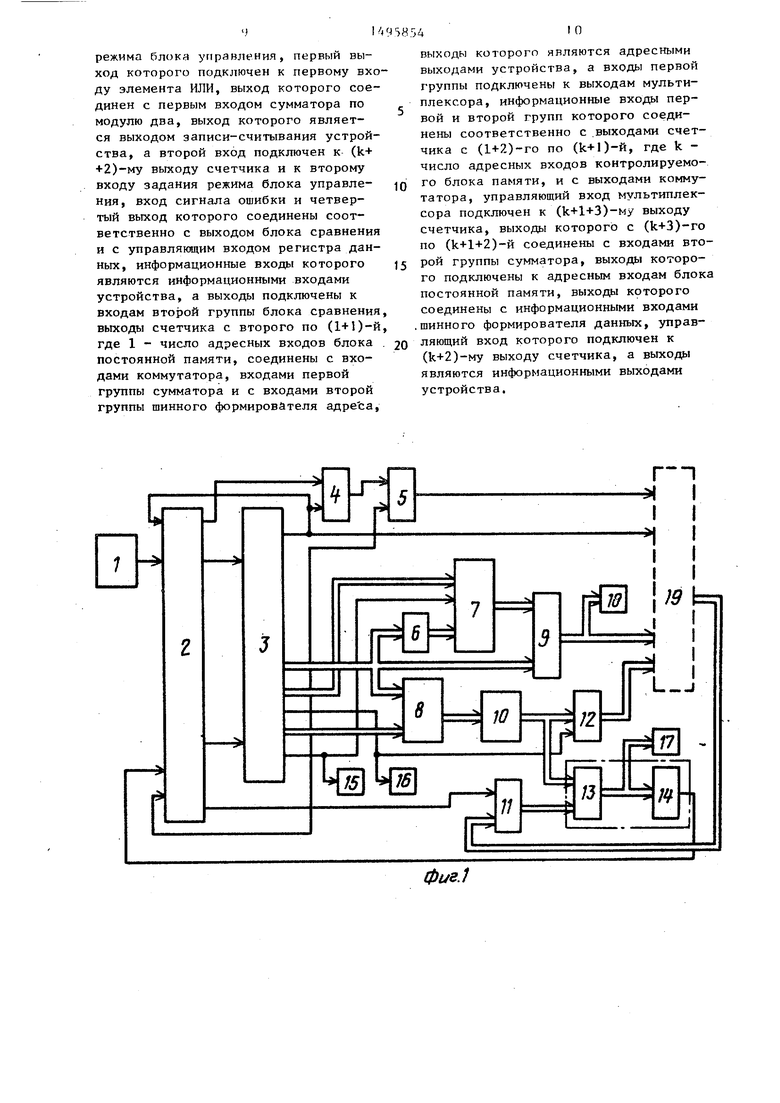

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 - функциональная схема блока управления ; на фиг. 3 - функциональная схема коммутатора; на фиг. 4 - массивы данных, записанные в постоянном запоминающем устройстве тестовых комбинаций., , .

Устройство содержит генератор 1 тактовых импульсов, блок 2 управления, счетчик 3, элемент ИЛИ 4, сумматор 5 по модулю два, коммутатор 6, мультиплексор 7, сумматор 8, шинный формирователь 9 адреса, блок 10 по- .стоянной памяти (БПП), регистр 11

.

со

01

00

сд

Nt

данных, тинный формирователь 12 данных, группу сумматоров 3 по модулю два, элемент 14, первый 15 и второй 16 индикаторы, первую 17 и вторую 18 группы индикаторов, проверяемьй блок 19 оперативной памяти (БОП). Сумматоры 13 по модулю два и элемент И-НЕ 14 составляют блок сравнения,

Блок 2 управления (фиг. 2) содержит элемент И 20, первый 21 и второй 22 элементы задержки, элемент ИЛИ 23,В-триггер 24, переключатель 25, элемент И-НЕ 26 и резистор 27, под- ключенный с одной стороны к плюсу источника питания, а с другой стороны - подключенный к второму входу элемента 2И-НЕ 26.

Двоичный счетчик импульсов имеет разрядность (k+1+З), где k - количество адресных входов контролируемого БОП; 1 - количество адресных входов БПП тестовых комбинаций; 1 a+log2n; п - количество информаци- онных входов БОП.

Если значение дробное, то берут ближайшее большее целое число. Коэффициент а принижает значения О, 1 или 2 и зависит от требуемой достоверности контроля ячеек БОП Наибольшая достоверность контроля достигается.при .

Распределяются выходы счетчика 3 от младших разрядов к старшим еле- дующим образом: 1-й выход - младший разряд счетчика; 1-я группа выходов 1 разрядов; 2-я группа выходов (k-1) разрядов; 2-й выход - один разряд между 2-й и 3-й группами выходов 3-я группа выходов - 1 разрядов; 3-й выход - старший разряд счетчика,

Коммутатор 6, имеющий 1 входов и (k-1) ВЫХОДОВ , реализуют монтажным путем. Возможны три варианта соединения входных и выход 1ых шин, S случа когда (k-l)l (фиг. 3, вариант 28), все входы соединены с соответствующими выходами. Когда (k-l)l (фиго 3, вариант 29), на младшие 1 разрядов входов подаются соответственно 1 входов. На оставшиеся (1+1)(k-1) выходов коммутируются соответственно, начиная с младших разрядов, входы коммутатора. В случае,- когда (k-lXl (фиг. 3, вариант 30), на выходы коммутируются соответственно младшие (k-1)-входные разряды.

г10

й15 20

.

35 - зв; 0 й

45 ае, и, Q выj l 1Блок- И) постоянной памяти имсчгг

в

объем 2 п. .

Когда коэффициент , в записывается бегущая единица (фиг.4, вариант 31), При в БПП записываются бегущая единица и бегущий нуль (фиг. 4, вариант 32), при бегущая единица, бегущий нуль и информационная комбинация типа дождь (фиг. 4, вариант 33) ...При значении log,n (дробном) оставшиеся (2 -0)2 ячеек БПП заполняются информацией типа дождь (фиг. 4, вариант 34).

Устройство работает следующим образом.

Проверка БОП 19 состоит из двух этапов. На первом этапе осуществляется контроль всех ячеек проверяемого БОП объемом . В БОП записываи- 6 ется 2 . п идентичных отображений

содержимого БПП. Далее проводят считывание из всего БОП информации и ее сравнение с информацией, находящейся в БПП, При наличии ошибки в счи-. танной информации устройство останавливается и прекращает дальнейшую проверку. При отсутствии ошибок проводится второй цикл записи-чтения, ана- логичньгй первому, однако по i-му адресу БОП записывается информация из ячейки БПП с адресом (i+l), В третьем .цикле записи-чтения в ячейку БОП записывается информация из (1+2)-й ячейки БПП (2 циклов записи-чтения), в результате чего проводятся полный контроль исправности всех ячеек БОП и контроль взаимных влияний информационных, адресных и управляющих шин блока БОИ

Далее проводится второй этап проверки, отличающийся от первого тем, что на входы старших разрядов адреса БОП подключаются выходы младших разрядов счетчика 3. Это позволяет обнаружить микросхемы БОП с недостаточным быстродействием дешифратора адреса.

Импульс отрнцафельной полярности, пришедший по шине начальной установки, устанавливает по S-входу триггер 24 в единичное состояние и обнуляет счетчик 3, При этом появившийся на инверсном выходе триггера 24 сигнал логического О разрешает прохождение импульсов через элемент ИЛИ 23 с выхода генератора на счетный вход счетчика 3, работающего в режиме непрерыпнот о перег.чета. Па элементе ИЛИ 4, сумматоре 5 по модулю два и элементе 21 задержки построен формирователь сигналов Записг -чтё iTHe (Зп/Чт). Причем элемент ИЛИ 4 путем логического сложения сигнала с генератора 1, задержанного элементом 21 задержки и сигнала с первого выхода счетчика 3 формирует длительность сигнала Запись-чтение. А сумматор 5 по модулю два формирует на первом выходе устройства сигнал Запись, если на втором выходе счетчика 3 уровень логического О, и СИГН9Л Чтение - если уровень логической 1, Сигналом Выбор кристалла (ВК) служит сигнал с первого в хода счетчика 3, Такое формирование сигналов Зп-чт и ВК позволяет получить оптимальные временные соотношения этих сигналов для каждого ко кретного типа проверяемого БОП, что обеспечивает достоверность контроля динамических параметров и быстродействие. Мультиплексор 7 при нулевом состоянии управляющего входа подключает к группе входов старших разрядов шинного формирователя 9 адреса вторую группу выходов счетчика 3, а при подаче на управляющий вход логической 1 подключает через коммутатор 6 первую группу выходов счетчика 3, подключенную также и к группе входов младших разрядов шинного формирователя 9 адреса, что позволяет сформировать полный k-разряд ный адрес для проверяемого БОП 19.

Таким образом, за первые 2 тактов, т.е. до появления на втором выходе счетчика 3 логической 1, происходит первый цикл записи информаци в БОП. В последующие 2 тактов, т„е .когда на втором выходе счетчика 3 устанавливается уровень логической 1, происходит первый цикл считывания информации из БОП. В процессе считывания информации из БОП выходы шинного формирователя 12 данных под воздействием логической 1 на управляющем входе находятся в высокоим- педансном состоянии. Проинвертиро- ванная входным регистром 11 информация из БОП поразрядно сравнивается в блоке сравнения на группе сумматоров 13 по модулю два с информацией, хранящейся в БПП 10. Обобщенный результат сравнения появляется на выходе п-входовето элемента И-НЕ 14, ко.j4

тярый является выходом блока сравнения. При наличии ошибки в считанной информации на выходе п-входово- г о злемеШ-а И-НЕ 14 появляется логическая I, которая инвертируется элементом 2И-ПЕ 26 блока 2 управления. По переднему фронту сигнала записи, сформированного путем логического умножения сигнала с выхода генератора 1 и сигналг1 с первого выхода счетчика 3 элементом 2И 20 и задержанного элементом 22 задержки, происходит запись логического О в

триггер 24 блока 2 управления, в результате чего блок 2 управления прекращает транслировать импульсы с выхода генератора 1 на счетный вход счетчика 3, которьй при этом фиксирует адрес неисправной ячейки БОП. Наряду с этим логический О, появившийся на прямом выходе триггера 24, стробирует содержимое регистра 11, что необходимо для фиксации ошибки,

вызванной малым быстродействием проверяемого БОП.

В результате первая группа 17 индикаторов показывает неисправные разряды шины данных, вторая группа

18 индикаторов показывает адрес неисправной ячейки БОП, а первый 15 и второй 16 индикаторы показывают режим, в котором происходит обнаружение ошибки. Эта информация позволяет

сделать вывод о причине неисправности и оперативно ее устранить.

Кроме того, временное положение переднего фронта сигпала записи по отношению к сигналу ВК определяется временем задержки элемента 22

задержки блока 2 управления, что позволяет компенсировать влияние времени задержки элементов устройства и установить оптимальное время срабатывания для каждого конкретного типа БОП.

Наличие в блоке 2 управления переключателя 25 и элемента 2И-1ГЕ 26 и резистора 27, который служит для повьшгения помехоустойчивости при разомкнутом переключателе 25, позволяет проверять три различных типа БОП: с раздельным входом и выходом, у которых при записи на выходе безразичное состояние; с раздельным вхоом и выходом, у которых при записи информация с входа трлнслируется на выход; с двунаправленным сигналом вход-выход.

7

Для проверки БОП первого типа необходимо переключатель 25 блока управления замкнуть. При этом во время записи информации в БОП, т.е, при наличии на втором выходе счетчика 3 логического О, на информационном Ьходе триггера 24 блока 2 управления будет логическая 1, не зависящая рт состояния входной шины устройства.

I Для проверки БОП второго типа пе- Ьеключатель 25 блока 2 управления не- рбходимо разомкнуть. При этом результат сравнения информации на входе и выходе БОП как в момент считывания, ак и в момент записи информации в lOn поступает на вход триггера 24 5лока 2 управления и записывается.

Для проверки БОП третьего типа пе- 20 обнаружить микросхемы БОП с недостаэеключатель 25 блока 2 управления мо- шт быть в любом положении. Однако при )азомкнутом переключателе 25 блока 2

точным быстродействием дешифратора адреса.

Если проверяемый БОП 19 исправен, то устройство начинает новую провер- 25 ку. Это позволяет организовать циклическую проверку работоспособности БОП 19 при воздействии климатических факторов.

управления будет производиться запись результата сравнения в триггер 24 Фло.ка 2 управления как при.считыва- 1}1ии, так и при записи информации в |ОП, что позволяет выявить замкнутые собой информационные шины при фаписи информации в БОП. I Для проверки БОП с двунаправлен- фыми шинами вход-выход необходимо Объединить попарно соответствующие 1(азряды входной и выходной шин данных }|гстройства.

При отсутствии ошибок в первом цикле записи-чтения следует второй Аналогичный цикл записи-чтения, от- Аичающийся тем, что по адресу ffion 19 записывается информация из ячейки БПП 10 с адресом (1+1).Это Достигается за счет того,, что сумматор 8, формирующий адрес для БПП 10, на первой группе входов, подключенных к первой группе выходов счетчика ., имеет код i-ro адреса БОП, а на вторую группу входов с третьей группы выходов счетчика 3 поступает 1 разрядный код 00,.,01. В третьем цикле записи-чтения на вторую группу №одов с:умматора 8 поступает код (Ю...10 и на вход БПП 10 формируется адрес (J.+2). Всего производится }. аналогичных циклов записи-чтения,; Такое формирование адреса для БПП 10 тестовых комбинаций позволяет использовать в устройстве БПП малого объема.

5854. 8

Таким образом, за первые 2 циклов записи-чтения, т.е. при наличии на третьем выходе счетчика 3 логис ческого происходят полный контроль всех ячеек проверяемого БОП 19 и контроль взаимных влияний информационных, адресных и управляющих шин блока БОП 19.

)Q При появлении на третьем выходе счетчика 3 логической 1 производятся еще 2 аналогичных циклов записи-чтения, отличающихся тем, что мультиплексор 7 под воздействием гической I на управляющем входе передает на группу входов старших разрядов шинного формирователя 9 ад- ресй через коммутатор 6 первую группу выходов счетчика 3, что позволяет

точным быстродействием дешифратора адреса.

Если проверяемый БОП 19 исправен, то устройство начинает новую провер- ку. Это позволяет организовать циклическую проверку работоспособности БОП 19 при воздействии климатических факторов.

Формула изобретения

Устройство для контроля многораз рядных блоков оперативной памяти, содержащее -генератор тактовых импуль

два, блок постоянной памяти, выходы которого соединены с входами первой Группы блока сравнения, от л и ч а- ю П1 е е с я тем, что, с целью повышения достоверности контроля и рас- . ширения функциональных возможностей за счет обеспечения контроля памяти с раздельными и совмещенными входами- выходами, с трансляцией и без трансляции данных на выходы при записи, в устройство введены мультиплексор, коммутатор, сумматор, регистр данных, элемент ИЖ, блок управления, шинный формирователь данных и шинный формирователь адреса, причем выход генератора тактовых импульсов соединен с входом разрешения блока управления, второй и третий выходы которого подключены к входам соответственно синхронизации и сброса счетчика, первьй выход которого является выходом выборки кристалла удтрой- ства и соединен с вторым входом элемента ИЛИ и с первым входом задания

режима блока управления, первый выход которого подключен к первому входу элемента ИЛИ, выход которого соединен с первым входом сумматора по модулю два, выход которого является выходом записи-считывания устройства, а второй вход подключен к (k+ +2)-му выходу счетчика и к второму входу задания режима блока управления, вход сигнала ошибки и четвертый выход которого соединены соответственно с выходом блока сравнения и с управляющим входом регистра данных, информационные входы которого являются информационными входами устройства, а выходы подключены к входам второй группы блока сравнения, выходы счетчика с второго по (1+1)-и, где 1 - число адресных входов блока . постоянной памяти, соединены с входами коммутатора, входами первой группы сумматора и с входами второй группы шинного формирователя адре са.

0

5

0

выходы которого являются адресными выходами устройства, а входы первой группы подключены к выходам мультиплексора, информационные входы первой и второй групп которого соединены соответственно с .выходами счетчика с (1+2)-го по ()-й, где k - число адресных входов контролируемого блока памяти, и с выходами коммутатора, управляющий вход мультиплексора подключен к (k+l+3)-My выходу счетчика, выходы которого с (k+3)-ro по (k+l+2)-й соединены с входами второй группы сумматора, выходы которого подключены к адресным входам блока постоянной памяти, выходы которого соединены с информационными входами .шинного формирователя данных, управляющий вход которого подключен к (k+2)-My выходу счетчика, а выходы являются информационными выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1988 |

|

SU1840538A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1750060A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для контроля состояния объекта | 1983 |

|

SU1119055A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СПЛОШНЫХ ОБРАЗОВ | 1991 |

|

RU2042204C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1994 |

|

RU2108623C1 |

Изобретение относится к вычислительной технике и может быть использовано для функционального контроля как отдельных корпусов микросхем оперативных запоминающих устройств (ОЗУ),так и построенных на их основе ОЗУ произвольных организаций и емкости. Целью изобретения является повышение достоверности контроля и расширение функциональных возможностей за счет обеспечения контроля памяти с раздельными и совмещенными входами, с трансляцией и без трансляции данных на выходы при записи. Устройство содержит генератор тактовых импульсов, блок управления, счетчик, элемент ИЛИ, сумматор по модулю два, коммутатор, мультиплексор, сумматор, шинные формирователи адреса и данных, блок постоянной памяти, регистр данных и блок сравнения. Цель изобретения достигается реализацией с помощью счетчика и блока постоянной памяти тестов"Бегущая 1,0" и "Дождь" с перестановкой разрядов а дреса для многоразрядных ОЗУ и организацией режимов контроля данных при записи и считывании в зависимости от типа элементной базы ОЗУ. 4 ил.

фиг.1

OxttS

:.

г

0001 ее 1 о

9 1 00

LOJ о 1 1 Го

t а О t

д 1 1 t

3Z

Вшж$

8wtt

Фиг. г

о о о о (TJ 00 о ОJ 9 о ff 9 t 00

о о j о о а

01 е о в а

1о о в вв( ЪГ7ГУ7

101010

ЗУ

Jf

| Устройство для контроля полупроводниковой памяти | 1982 |

|

SU1032481A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Оперативное запоминающее устройство с самоконтролем | 1984 |

|

SU1229826A1 |

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1989-07-23—Публикация

1987-12-08—Подача