динены с входом четвертого элемента НЕ, четвертым входом четвертого эле мента И, третьими входами шестого и седьмого элементов И, вторым вход восьмого элемента И и первыми входами двенадцатого и тринадцатого элементов И, установочные входы третьего и четвертого счетчиков соединены соответственно с пятым и шестым установочными входами первого счетчика и подключены соответственно к выходам тринадцатого и четьфнадцатого элементов И, первьй вход четырнадцатого, элемента И соединен с вторым входом двенадцатого элемента И и подключен к пятому выходу дешифратора, вторые входы третьего и пятого элементов И объединены и подключены к шестому выходу дешифратора, седьмой выход которого соединен с пятым входом четвертого элемента И и четвертым входом шестого элемента И, восьмой выход дешифратора соединен с третьими входа}4И второго и восьмого элементов И и вторым входом тринадцатого элемента И, третий вход кото рого объ единен с первым входом пятнадцатого элемента И и подключен к выходу третьего элемента НЕ, вторые входы девятого и пятнадцатого элеме тов И объединены и подключены к девятому выходу дешифратора, десятый выход которого соединен с четвертым входом седьмого элемента И, второй, вход четырнадцатого элемента И подключен к выходу четвертого элемента НЕ, третий выход дешифратора сое динен с первыми входами первого и второго элементов ИЖ, второй вход первого элемента ИЛИ соединен с чет вертым ВЫХОДОМ дешифратора, одиннад цатый выход которого подключен к первому входу третьего элемента ИЛИ вторые входы второго и третьего элементов ИЛИ объединены и подключе Hfci к выходу двенадцатого элемента И выход второго элемента И подключен к первому входу первого триггера, причем первый и второй входы первого и второго триггеров соединены соответственно с. вьгходами третьего пятого элементов И блока управления прямой и инверсный выходы первого и второго триггеров соединены соответ ственно с первым и вторым входами первого и второго коммутаторов, третьи и четвертые входы первого и второго коммутаторовобъединены и 5 подключены к выходам блока анализа, тактовые входы которого подключены к выходу первого элемента ИЛИ блока управления и четвертому выходу дешифратора блока управления, выходы первого и второго коммутаторов соединены соответственно с группой управляющих входов первого и второго преобразователей кодов, управляющие входы которых объединены с управляющими входами третьего и четвертого преобразователей кодов и подключены к выходу первого элемента ИЛИ блока управления,первый выход дешифратора блока управления и выход девятого элемента И блока управления подключены к управляющим входам регистра правой части, информационные входы которого соединены с информационными входами узла, выход регистра правой . части соединен с вторым информационным входом регистра частных сумм, второй вход первого триггера блока управления, седьмой установочный вход первого счетчика блока управления и счетньм вход второго счетчика блока управления подключены к информационным входам узла, выходы шестого, восьмого, двенадцатого и тринадцатого элементов И, первый и одиннадцатый выходы дешифратора, , выходы второго и третьего элементов ИЛИ являются соответствующими выходами блока управления. 2. Узел по п. 1, отличающийся тем, что преобразователь кодов выполнен в виде элемента НЕ, первого, второго и третьего элементов И, триггера и элементна ИЛИ, первьй вход которого соединен с выходом первого элемента И, первьй вход которого подключен .к инверсному выходу триггера, прямой выход которого подключен к первым входам второго и третьего элементов И, / вторые входы которых объединены и через элемент НЕ соединены с вторым входом первого элемента И, первьй вход Триггера соединен с выходом второго элемента И, третий вход которого соединен с третьим входом третьего элемента И, выход которого соединен с вторым входом элемента РШИ, выход которого является выходом преобразователя кодов, второй вход триггера является управляющим входом преобразователя кодов, третий вход третьего элемента И и четвертый вход второго элемента И образуют группу управляющих преобразователя кодов, второй входов третьего элемента И является информавход . ционным входом преобразователя кодов. 1132295

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Вычислительный узел цифровой сетки | 1987 |

|

SU1501053A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин с мультипликативной автокоррекцией | 1984 |

|

SU1185604A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ОБРАЗОВ | 2010 |

|

RU2430415C1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Устройство для измерения фазового сдвига | 1984 |

|

SU1190294A1 |

| Арифметическое устройство | 1979 |

|

SU849206A2 |

ВЫЧИСЛИТЕЛЬНЫЙ УЗЕЛ ЦИФ-. РОВОЙ СЕТКИ по авт. св. К 800997, отличающийся тем, что, с целью повышения точности решения дифференциальных уравнений, в узел дополнительно введены первьш и второй триггеры, первый и второй коммутаторы и регистр правой части, а блок управления выполнен в виде первого и второго триггеров, первого, ;второго, третьего, четвертого, пятого, шестого, седьмого, восьмого, девятого,десятого,одиннадцатого,двенадцатого,тринадцатого,четырнадцато,го и пятнадцатого элементов И,первого, второго, третьего и четвертого счетчиков, первого, второго, третьего . и четвертого элементов НЕ, элемента И-НЕ, первого, второго и третьего элементов ИЛИ, дешифратора и генератора тактовьк импульсов, выход которого соединен с первым входом первого элемента И, второй вход которого соеданен с выходом первого триггера, первый вход которого соединен с первым установочным входом первого счетчика, счетный вход которого подключен к выходу первого элемента И, выходы разрядов первого счетчика подключены к входам дешифратора, первый выход которого подключен к второму установочному входу первого счетчика, второй выход дешифратора подключен к первому входу второго триггера, выход которого соединен с первыми входами второго, третьего и четвертого элементов Ни через первьш элемент НЕ - с первыми входами пятого, шестого и седьмого элементов И, выход последнего соединен с вторым входом второго тригге(Л ра, выходы четвертого и седьмого элементов И подключены к третьему и четвертому установочным входам с с; первого счетчика, выход четвертого элемента И соединен со счетным входом второго счетчика, выходы разрядов которого через элемент И-НЕ соединены с вторым входом второго :о ю элемента .И и входом второго элемента НЕ, выход которого подключен к второSD ГГ му входу четвертого элемента И, третий вход которого соединен с :л вторыми входами шестого и седьмого элементов И, первыми входами восьмого и девятого элементов И и входом третьего элемента НЕ и подключен к выходу десятого элемента И, входы которого соединены с выходами третьего счетчика, счетный вход которого соединен с третьим выходом дешифратора, четвертый выход которого соединен со счетным входом четвертого счетчика, выходы которого через одиннадцатый элемент И сое

f

Изобретение относится к области вычислительной техники и предназначено для построения устройств, ориентированных на решение задач математической физики, описываемых дифференциальными уравнениями, в частных производных.

По основному авт. св. № 800997 известен вычислительный узел цифровой сетки, содержащий мцоговходовьш сумматор, сдвиговый регистр и группу элементов И, выходы которых являются группой выходов узла, а входы подключены к группе выходов сдвигового регистра, тактовые вхоДы сдвигового регистра, элементов И группы соединены с тактовым входом узла, регистры коэффициентов, преобразователи кодов, регистр частичны сумм и блок анализа, входы регистров коэффициентов соединены с информационным входом узла, а выходы с входами соответствующих преобразователей кодов, выходы которых соединены с группой входов многовходового сумматора, выход которого соединен с первым входом регистра частиных сумм, второй вход которого соединен с информационньм входом узла, а выход с входом многовходового сумматора и входом сдвигового регистра, вход блока анализа соединен с выходом сдвигового регистра, а выход с управляющим выходом узла, тактовые входы регистров коэффициентов, регистра частичных сумм и блока анализа соединены с тактовым входом узла, S- управляющие входы преобразователей кодов - с управляющим входом узла, управляющие, входы-регистров коэффициентов, регистра частичных сумм, сдвигового регистра, группы элементов И и блока анализа соединен с управляющей шиной, блок анализа содержит элементы памяти, а также элементы И и ИЛИ, причем первые входы элементов памяти соединены с тактовым входом блока, вход первого элемента памяти подключен к входу

блока, первые выходы элементов памя;ти соединены соответственно с первыми входами первого и второго элементов И, выходы которых соединены с соответствующими входами элемента ИЛИ, выход каждого является выходом блока, второй выход второго, элемента памяти соединен с входом второго элемента памяти, втофым входом второго элемента И и выходом блока, второй выход второго элемента памяти соединен с вторым входом первого .элемента И, преобразователь кодов содержит два элемента НЕ, два элемента И и элемент ИЛИ, причем выходы первого и второго элементов НЕ соединены соответственно с первыми входами первого и второго элементов И, выходы которых подключены к , соответствующим входам элемента.ИЛИ, выход которого является выходом преобразователя, вторые входы элементов И и третий вход первого элемента И соединены соответственно с управляющим входом преобразователя, вход которого соединен с входом первого элемента НЕ и третьим входом второго элемента И lj .

Недостатком известного устройства является низкая точность рещения.

Цель изобретения - повышение точности решения дифференциальньпс уравнений.

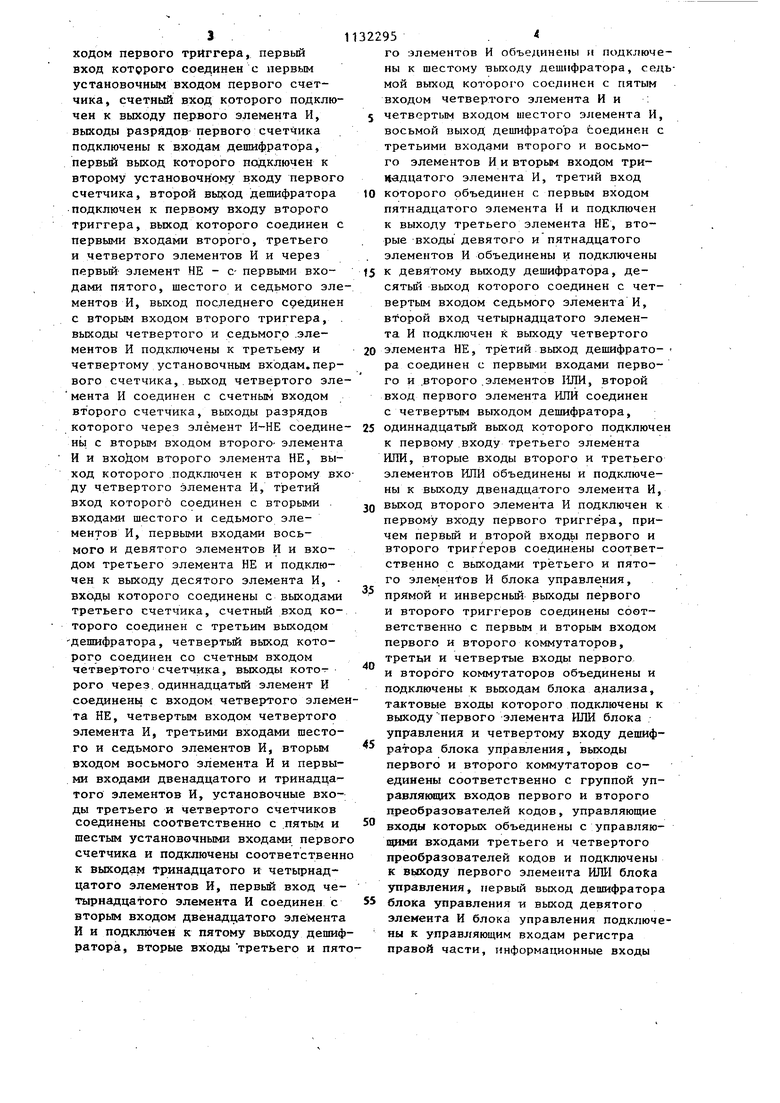

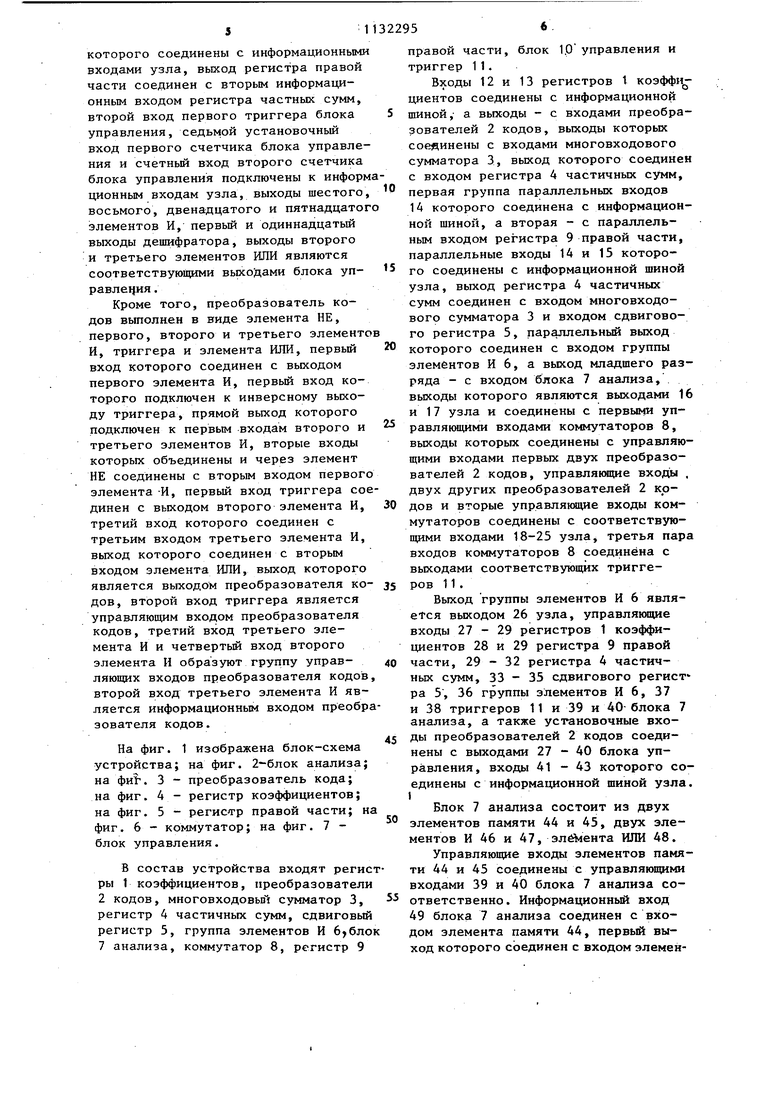

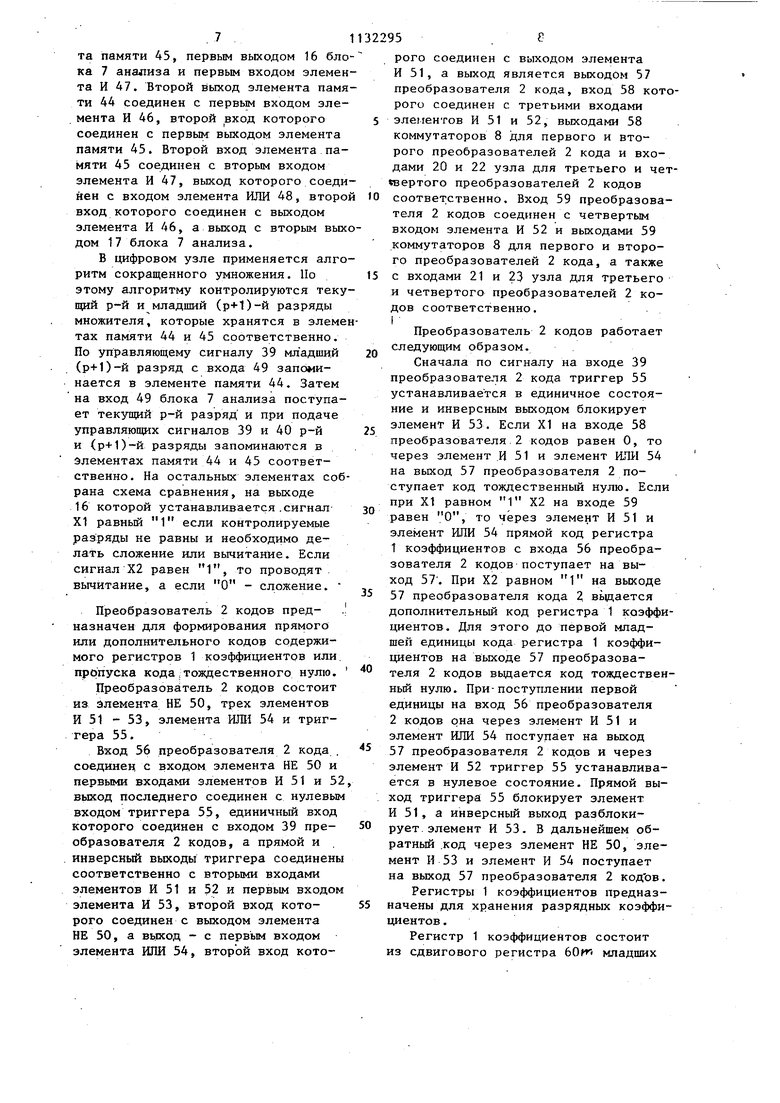

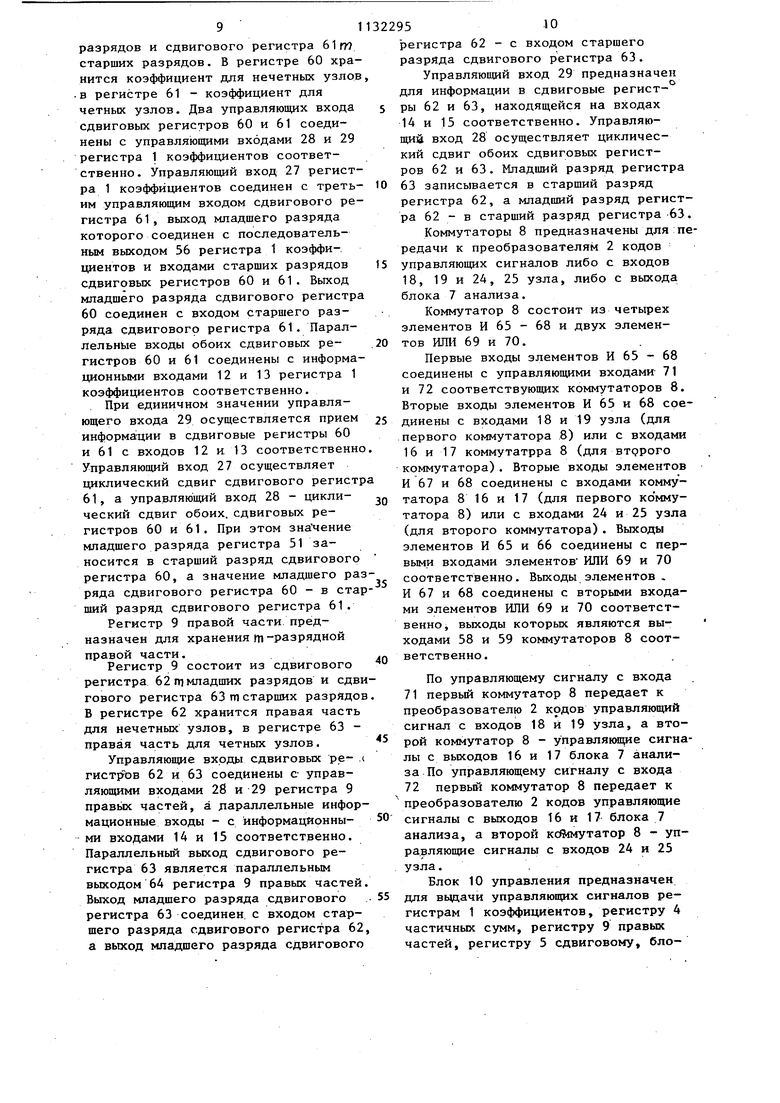

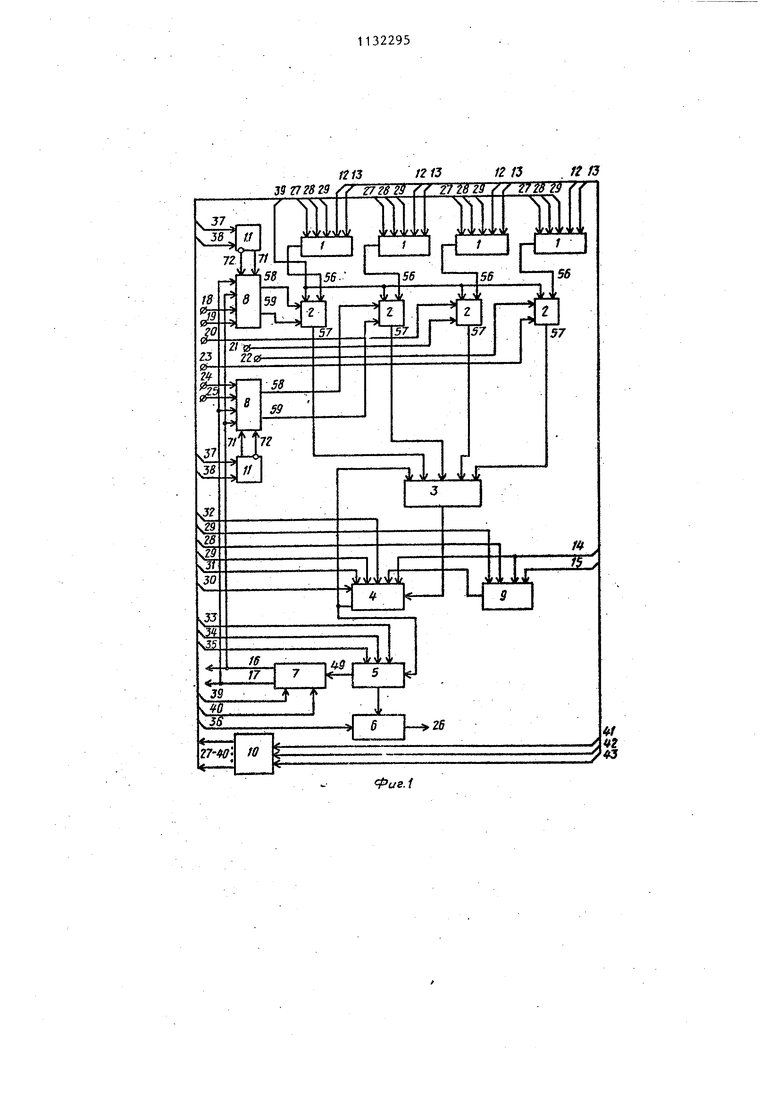

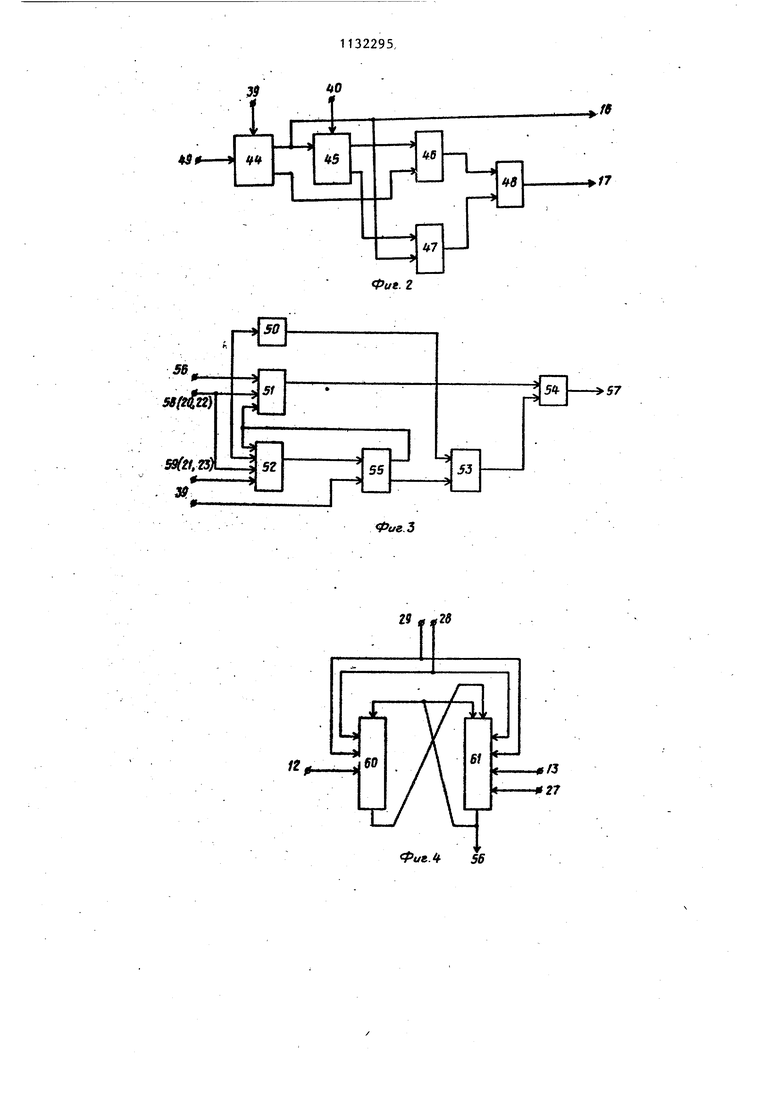

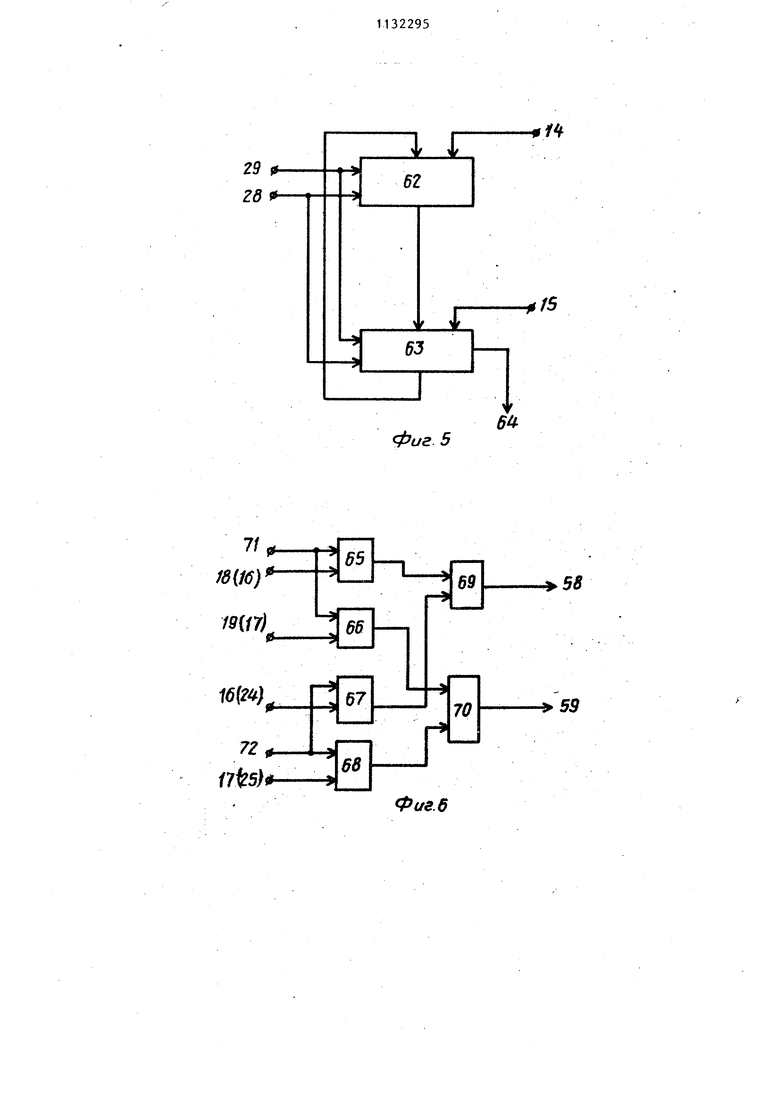

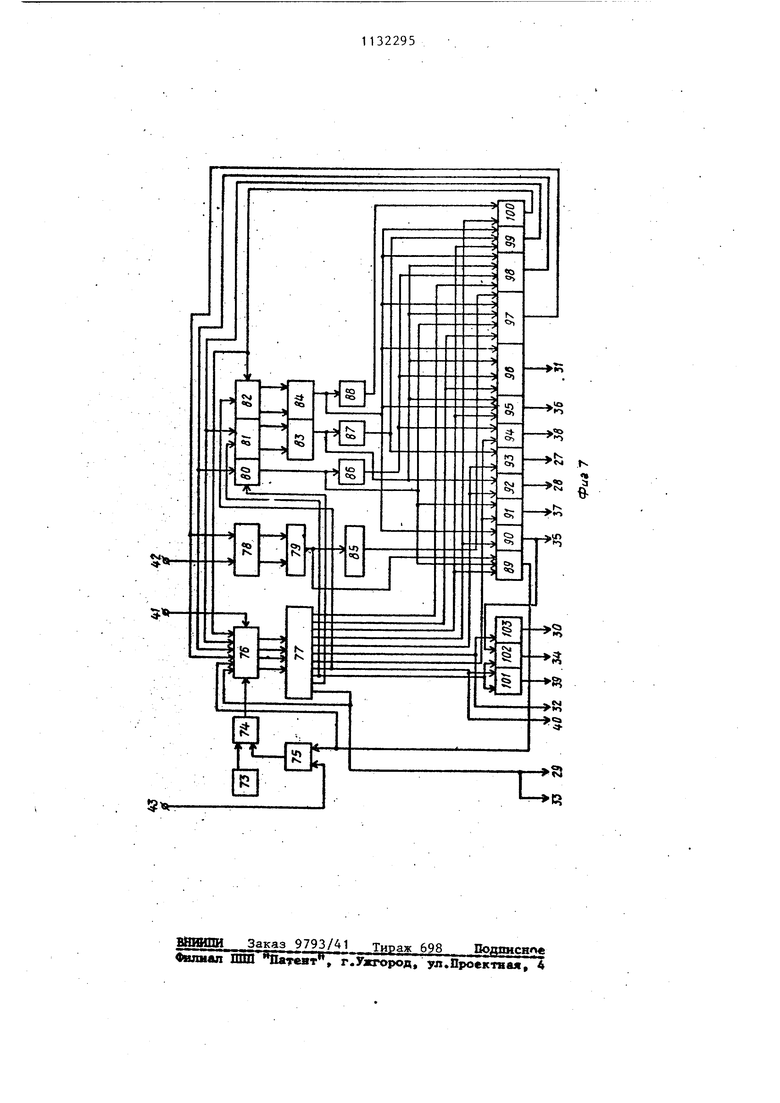

Поставленная цель достигается тем, что в вычислительный узел цифровой сетки дополнительно введены первьй и второй триггеры, первый и второй коммутаторы и регистр правой части, а блок управления выполнен в виде первого и второго триггеров , первого - пятнадцатого элементов И, первого - четвертого счетчиков, первого - четвертого элементов НЕ, элемента И-НЕ, первого, второго и третьего элементов ИЛИ, дешифратора и генератора тактовых импульсов, выход которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом первого триггера, первый вход которого соединен с первым установочным входом первого счетчика, счетньй вход которого подключен к выходу первого элемента И, выходы разрядов первого счетчика подключены к входам дешифратора, первый выход которого подключен к второму установочному входу первого счетчика, второй выход дешифратора подключен к первому входу второго триггера, выход которого соединен с первыми входами второго, третьего и четвертого элементов И и через первый элемент НЕ - с- первыми входами пятого, шестого и седьмого эле ментов И, выход последнего сдединен с вторым входом второго триггера, выходы четвертого и седьмого .элементов И подключены к третьему и четвертому установочным входам,первого счетчика, выход четвертого эле мента И соединен с счетным входом второго счетчика, выходы разрядов которого через элемент И-НЕ соедине ны с вторым входом второго- элемента И и второго элемента НЕ, выход которого подключен к второму вх ду четвертого элемента И, третий вход которого соединен с вторыми . входами шестого и седьмого элементов И, первыми входами восьмого и девятого элементов И и входом третьего элемента НЕ и подключен к выходу десятого элемента И, входы которого соединены с выходами третьего счетчика, счетный вход которого соединен с третьим выходом Дешифратора, четвертьй выход которого соединен со счетным входом четвертогосчетчика, выходы которого через, одиннадцатый элемент И соединены с входом четвертого элеме та НЕ, четвертым входом четвертого элемента И, третьими входами шестого и седьмого элементов И, вторым входом восьмого элемента И и первыми входами двенадцатого и тринадцатого элементов И, установочные входы третьего и четвертого счетчиков соединены соответственно с .пятьм и шестым установочными входами первог счетчика и подключены соответственн к выходам тринадцатого и четырнадцатого элементов И, первый вход четырнадцатого элемента И соединен с вторым входом двенадцатого элемента И и подключен к пятому выходу дешиф ратора, вторые входы третьего и пят го элементов И объединены и подключены к шестому вьсходу дешифратора, седьмой выход которого соединен с пятым входом четвертого элемента И и ; четвертым входом шестого элемента И, восьмой выход дешифратора Соединен с третьими входами второго и восьмого элементов И и вторым входом тринадцатого элемента И, третий вход которого объединен с первым входом пятнадцатого элемента И и подключен к выходу третьего элемента НЕ, вторые входы девятого и пятнадцатого элементов И объединены и подключены к девятому выходу дешифратора, десятьп выход которого соединен с четвертым входом седьмого элемента И, второй вход четырнадцатого элемента И подключен к выходу четвертого элемента НЕ, третий выход дешифратора соединен с первь1ми входами первого и .второго .элементов 1ШИ, второй вход первого элемента ИЛИ соединен с четвертым выходом дешифратора, одиннадцатый выход которого подключен к первому входу третьего элемента Ш1И, вторые входы второго и третьего элементов РШИ объединены и подключены к выходу двенадцатого элемента И, выход второго элемента И подключен к первому входу первого триггера, причем первый и второй входы первого и второго триггеров соедин.ены соответственно с выходами третьего и пятого элементов И блока управления, прямой и инверсный выходы первого и второго триггеров соединены соответственно с первым и вторым входом первого и второго коммутаторов, третьи и четвертые входы первого и второго коммутаторов объединены и подключены к выходам блока анализа, тактовые входы которого подключены к выходу первого элемента ИЛИ блока управления и четвертому входу дешифратора блока управления, выходы первого и второго коммутаторов соединены соответственно с группой управляющих входов первого и второго преобразователей кодов, управляющие входы которых объединены с управляющими входами третьего и четвертого преобразователей кодов и подключены к выходу первого элемента ИЛИ блока управления, первый выход дешифратора блока управления и выход девятого элемента И блока управления подключены к управляющим входам регистра правой части, информационные входы которого соединены с информационными входами узла, выход регистра правой части соединен с вторым информационным входом регистра частных сумм, второй вход первого триггера блока управления, седьмой установочньй вход первого счетчика блока управления и счетный вход второго счетчика блока управления подключены к информ ционным входам узла, выходы шестого восьмого, двенадцатого и пятнадцатог элементов И, первый и одиннадцатый выходы дешифратора, выходы второго и третьего элементов ИЛИ являются соответствующими выходами блока управлеция. Кроме того, преобразователь кодов вьтолнен в виде элемента НЕ, первого, второго и третьего элементо И, триггера и элемента ИЛИ, первый вход которого соединен с выходом первого элемента И, первьй вход которого подключен к инверсному выходу триггера, прямой выход которого подключен к первым входам второго и третьего элементов И, вторые входы которых объединены и через элемент НЕ соединены с вторым входом первого элемента -И, первый вход триггера сое динен с выходом второго элемента И, третий вход которого соединен с третьим входом третьего элемента И, выход которого соединен с вторым входом элемента ИЛИ, выход которого является выходом преобразователя коДОН, второй вход триггера является управляющим входом преобразователя кодов, третий вход третьего элемента И и четвертьш вход второго элемента И образуют группу управЛЯЮ1ЦИХ входов преобразователя кодов второй вход третьего элемента И является информационным входом преобр зователя кодов. На фиг. 1 изображена блок-схема устройства; на фиг. 2-блок анализа; на . 3 - преобразователь кода; на фиг. 4 - регистр коэффициентов; на фиг. 5 - регистр правой части; на фиг. 6 - коммутатор; на фиг. 7 блок управления. В состав устройства входят регис ры 1 коэффициентов, преобразователи 2 кодов, многовходовьп сумматор 3, регистр 4 частичных сумм, сдвиговый регистр 5, группа элементов И 6,бло 7 анализа, коммутатор 8, регистр 9 956 правой части, блок 1.0 управления и триггер 11. Входы 12 и 13 регистров I коэфф циентов соединены с информационной шиной,- а выходы - с входами преобразователей 2 кодов, выходы которьк соединены с входами многовходового сумматора 3, вькод которого соединен с входом регистра 4 частичных сумм, первая группа параллельных входов 14 которого соединена с информационной шиной, а вторая - с параллельным входом регистра 9 правой части, параллельные входы 14 и 15 которого соединены с информационной шиной узла, выход регистра 4 частичных сумм соединен с входом многовходового сумматора 3 и входом сдвигового регистра 5, параллельный выход которого соединен с входом группы элементов И 6, а выход младшего разряда - с входом блока 7 анализа, выходы которого являются выходами 16 и 17 узла и соединены с первыми управляющими входами коммутаторов 8, выходы которых соединены с управляющими входами первых двух преобразователей 2 кодов, управляющие входы . двух других преобразователей 2 кодов и вторые управляющие входы коммутаторов соединены с соответствующими входами 18-25 узла, третья пара входов коммутаторов 8 соединена с выходами соответствующих триггеров 11. Выход группы элементов И 6 является выходом 26 узла, управляющие входы 27 - 29 регистров 1 коэффициентов 28 и 29 регистра 9 правой части, 29 - 32 регистра 4 частичных сумм, 33-35 сдвигового регистра 5, 36 группы элементов И 6, 37 и 38 триггеров 11 и 39 и 40-блока 7 анализа, а также установочные входы преобразователей 2 кодов соединены с выходами 27 - 40 блока управления, входы 41 - 43 которого соединены с информационной шиной узла. Блок 7 анализа состоит из двух элементов памяти 44 и 45, двух элементов И 46 и 47, ИЛИ 48. Управляющие входы элементов памяти 44 и 45 соединены с управляющими входами 39 и 40 блока 7 анализа соответственно. Информационный вход 49 блока 7 анализа соединен с вхоом элемента памяти 44, первьй выход которого соединен с входом элемен7та памяти 45, первым выходом 16 бл ка 7 анализа и первым входом элеме та И 47. Второй выход элемента пам ти 44 соединен с первьм входом эле мента И 46, второй вход которого соединен с первым выходом элемента памяти 45. Второй вход элемента па мяти 45 соединен с вторым входом элемента И 47, выход которого соед нен с входом элемента ИЛИ 48, втор вход которого соединен с выходом элемента И 46, а выход с вторым вых дом 17 блока 7 анализа. В цифровом узле применяется алг ритм сокращенного умножения. Но этому алгоритму контролируются тек щий р-й и младший (р+1)-й разряды множителя, которые хранятся в элем тах памяти 44 и 45 соответственно. По управляющему сигналу 39 младший (р+1)-й разряд с входа 49 запоминается в элементе памяти 44. Затем на вход 49 блока 7 анализа поступает текущий р-й разряд и при подаче управляющих сигналов 39 и 40 р-й и (р+1)-й разряды запоминаются в элементах памяти 44 и 45 соответственно. На остальных элементах соб рана схема сравнения, на выходе 16 которой устанавливается.сигнал XI равный 1 если контролируемые разряды не равны и необходимо делать сложение или вычитание. Если сигнал Х2 равен 1, то проводят вычитание, а если О - сложение. Преобразователь 2 кодов предназначен для формирования прямого или дополнительного кодов содержимого регистров 1 коэффициентов или пропуска кода;тождественного нулю. Преобразователь 2 кодов состоит из элемента НЕ 50, трех элементов И 51 - 53, элемента ИШ1 54 и триггера 55. Вход 56 преобразователя 2 кода . соединен с входом элемента НЕ 50 и первыми входами элементов И 51 и 52 выход последнего соединен с нулевым входом триггера 55, единичный вход которого соединен с входом 39 преобразователя 2 кодов, а прямой и инверсный выходы триггера соединены соответственно с вторыми входами элементов И 51 и 52 и первым входом элемента И 53, второй вход которого соединен с выходом элемента НЕ 50, а вькод - с первым входом элемента ИЛИ 54, второй вход кото5 . рого соединен с выходом элемента И 51, а выход является выходом 57 преобразователя 2 кода, вход 58 которого соединен с третьими входами элементов И 51 и 52, выходами 58 коммутаторов 8 для первого и второго преобразователей 2 кода и входами 20 и 22 узла для третьего и чет«вертого преобразователей 2 кодов соответственно. Вход 59 преобразователя 2 кодов соединен с четвертым входом элемента И 52 и выходами 59 коммутаторов 8 для первого и второго преобразователей 2 кода, а также с входами 21 и 23 узла для третьего и четвертого преобразователей 2 кодов соответственно. Преобразователь 2 кодов работает следующим образом. Сначала по сигналу на входе 39 преобразователя 2 кода триггер 55 устанавливается в единичное состояние и инверсным выходом блокирует элемент И 53. Если XI на входе 58 преобразователя.2 кодов равен О, то через элемент .И 51 и элемент ИЛИ 54 на выход 57 преобразователя 2 поступает код тождественный нулю. Если при XI равном 1 Х2 на входе 59 равен О, то через элемент И 51 и элемент ИЛИ 54 прямой код регистра t коэффициентов с входа 56 преобразователя 2 кодов поступает на выход 57. При Х2 равном 1 на выходе 57 преобразователя кода 2 вьщается дополнительный код регистра 1 коэффициентов. Для этого до первой младшей единицы кода регистра 1 коэффициентов на выходе 57 преобразователя 2 кодов вьщается код тождественньш нулю. При-поступлении первой единицы на вход 56 преобразователя 2кодов она через элемент И 51 и элемент ИЛИ 54 поступает на выход 57 преобразователя 2 кодов и через элемент И 52 триггер 55 устанавливается в нулевое состояние. Прямой выход триггера 55 блокирует элемент И 51, а инверсный выход разблокирует элемент И 53. В дальнейшем обратный .код через элемент НЕ 50, элемент И 53 и элемент И 54 поступает на выход 57 преобразователя 2 кодов. Регистры 1 коэффициентов предназначены для хранения разрядных коэффициентов . Регистр 1 коэффициентов состоит из сдвигового регистра младших разрядов и сдвигового регистра 61rW старших разрядов, В регистре 60 хранится коэффициент для нечетных узлов в регистре 61 - коэффициент для четных узлов. Два управляющих входа сдвиговых регистров 60 и 61 соединены с управляющими входами 28 и 29 регистра 1 коэффициентов соответственно. Управляющий вход 27 регистра 1 коэффициентов соединен с третьим управляющим входом сдвигового регистра 61, выход младшего разряда которого соединен с последовательным выходом 56 регистра 1 коэффициентов и входами старших разрядов сдвиговых регистров 60 и 61. Выход младшего разряда сдвигового регистра 60 соединен с входом старшего разряда сдвигового регистра 61. Параллельные входы обоих сдвиговых регистров 60 и 61 соединены с информационными входами 12 и 13 регистра 1 коэффициентов соответственно. При единичном значении управляющего входа 29 осуществляется прием информации в сдвиговые регистры 60 и 61 с входов 12 и 13 соответственно Управляющий вход 27 осуществляет циклический сдвиг сдвигового регистр 61, а управляющий вход 28 - циклический сдвиг обоих, сдвиговых регистров 60 и 61. При этом значение младшего разряда регистра 51 заносится в старший разряд сдвигового регистра 60, а значение младшего раз ряда сдвигового регистра 60 - в стар ший разряд сдвигового регистра 61. Регистр 9 правой части предназначен для хранения ш-разрядной правой части. Регистр 9 состоит из сдвигового регистра 621Т мпадших разрядов и сдви гового регистра 63гпстарших разрядов В регистре 62 хранится правая часть для нечетных узлов, в регистре 63 правая часть для четных узлов. Управляющие входы сдвиговых ре- д гистров 62 и 63 соединены с управляющими входами 28 и 29 регистра 9 правьк частей, а лараллельные информационные входы - с информационными входами 14 и 15 соответственно. Параллельный выход сдвигового регистра 63 является параллельным выходом 64 регистра 9 правых частей Выход младшего разряда сдвигового регистра 63 соединен с входом старшего разряда сдвигового регистра 62 а выход младшего разряда сдвигового регистра 62 - с входом старшего разряда сдвигового регистра 63, Управляющий вход 29 предназначен для информации в сдвиговые регистры 62 и 63, находящейся на входах 14 и 15 соответственно. Управляющий вход 28 осуществляет циклический сдвиг обоих сдвиговых регистров 62 и 63, Младший разряд регистра 63 записывается в старший разряд регистра 62, а младший разряд регистра 62 - в старший разряд регистра 63, Коммутаторы 8 предназначены для передачи к преобразователям 2 кодов управляющих сигналов либо с входов 18, 19 и 24, 25 узла, либо с выхода блока 7 анализа, Коммутатор 8 состоит из четырех элементов И 65 - 68 и двух элементов ИЛИ 69 и 70, Первые входы элементов И 65 - 68 соединены с управляющими входами 71 и 72 соответствуюпщх коммутаторов 8, Вторые входы элементов И 65 и 68 соединены с входами 18 и 19 узла (для первого коммутатора 8) или с входами 16 и 17 коммутатрра 8 (для втррого коммутатора). Вторые входы элементов И 67 и 68 соединены с входами коммутатора 8 16 и 17 (для первого коммутатора 8) или с входами 24 и 25 узла (для второго коммутатора), Выходы элементов И 65 и 66 соединены с первыми входами элементов ИЛИ 69 и 70 соответственно. Выходы элементов И 67 и 68 соединены с вторыми входами элементов ИЛИ 69 и 70 соответственно, выходы которых являются выходами 58 и 59 коммутаторов 8 соответственно. По управляющему сигналу с входа 71первый коммутатор 8 передает к преобразователю 2 кодов управляющий сигнал с входов 18 и 19 узла, а второй коммутатор 8 - управлякяцие сигналы с выходов 16 и 17 блока 7 анализа По управляющему сигналу с входа 72первый коммутатор 8 передает к преобразователю 2 кодов управляющие сигналы с выходов 16 и 17 блока 7 анализа, а второй ксОмутатор 8 - упра ляющие сигналы с входов 24 и 25 узла,. Блок 10 управления предназначен для вьщачи управляющих сигналов регистрам 1 коэффициентов, регистру 4 частичных сумм, регистру 9 правых частей, регистру 5 сдвиговому, бло111 ,ку 7 анализа и группе элементов И 6 и установочных сигналов для триггеров 11 и преобразователей 2 кодов. Блок 10 управления состоит из генератора 73 тактовых импульсов, элемента И 74, триггера 75, четырехразрядного счетчика 76, дешифратора 77, счетчика 78, элемента И-НЕ 79, триггера 80 (четная итерация - О, нечетная - 1), счетчиков 81 и 82, двух элементов И 83 и 84, четырех элементов НЕ 85-88, элементовИ 89100 и элементов ШШ 101-103. Выход генератора 73 тактовых импульсов соединен с первым входом элемента И 74, второй вход которого соединен с прямым выходом триггера 75, а выход с тактовым входом счетчика 76, четыре которого пода ются на входы дешифратора 77. Входы 43, 41 и 42 блока 10 управления заведены соответственно на единичньй вход триггера 75, на первые входы счетчиков 76 и 78, выходы счетчиков 81 и 82 соединены с входами элементов И 83 и 84 соответственно. Первый выход дешифратора 77 соединен с выходами .29 и .33 блока 10 управления и вторым входом счетчика 76, второй выход - с нулевым входом триг гера 80, третий выход - с первым входом счетчика 81 и первыми входами элементов ИЛИ 101 и 102, выходы которых являются выходами 39 и 34 блока 10 управления, четвертый: выходс вторыми входами счетчика 82, элемента РШИ 101 и выходом 40 блока 10 управления, пятый выход - с первыми входами элементов И 91 и 94, выходы которых являются выходами 37 и 38 блока 10 управления соответственно, седьмой выход - с первыми входами элементов И 92 и 93, выходы которых являются выходами 28 и 27 блока 10 управления. Шестой выход дешифратора 77 является выходом 32 блока 10 управления и заведен на первый вход элемента ИЛИ 103, выход которого является выходом 30 блока 10 управления. Восьмой выход дешифратора 77 соединен с первыми входами элементов .И 90 и 100, выход последнего соединен с вторым входом счетчика 82 и третьим входом счетчика 76, девятый выход - с перрыми входами элементов И 89, .95 и 99, Выход элемент И 89 соединен с нулевым входом триг гера 75 я четвертым входом счетчика 5 76, пятый вход которого соединен с вторымВХОДОМ счетчика 81 и выходом элемента И 99. Десятьй выход дешифратора 77 соединен с первыми входами элементов И 96 и 97, причем выход элемента И 96 является выходом 31 блока 10 управления, а выход элемента И 97 соединен с шестым входом счет чика 76 и вторым входом счетчика 78, «выходы которого подключены к входам элемента И-НЕ 79. Одиннадцатый выход дешифратора 77 соединен с первым входом элемента И 98, выход кото-, рого соединен с единичным входом триггера 80 и седьмым входом счетчика 76. Выход элемента И-НЕ 79 соединен с вторым входом эле,мента И 89 и входом элемента НЕ 85, выход которого соединен с вторыми входами элемента И 91, третьим входом элемента И 89, выходом триггера 80 и входом элемента НЕ 86, выход KOTopoio соединен с вторыми входами элемен.тов И 94, 96 и 98, при этом третий вход элемента И 98 соединен с четвертым входом элемента И 97, третьим входом И 96, вторьми входами элемента И 92 и 95, выходом элемента И 83 и входом элемента НЕ 87, выход которого соединен с вторыми входами элементов И 93 и 99. Выход 35 блока управления соединен с вторыми входами элементов ИЛИ 102 и 103, выходом элемента И 90, второй вход которого соединен с третьим входом элемента И 95, вькод которого является выходом 36 блока 10 управления, с четвертыми входами элементов И 96 и 98, пятым входом элемента И 97, третьим входом элемента И 99, выходом элемент И 88 и входом элемента НЕ 88, выход которого соединен с вторым входом элемента И 100. Блок 10 управления работает следующим образом. В счетчик 78 по входу 42 записывается число итераций и обнуляется счетчик 76. После прихода сигнала Пуск на вход 43 триггер 75 устанавливается в единичное состояние. Этот сигнал снимает блокировку с цепи генератора 73 тактовых импульсов. По каждому тактовому импульсу генератора 73 через элемент И 74 счетчик 76 переключается в состояние 1,2,..., 2 -1. В качестве примера рассмотрим случай, когда №. 4. Дешифратор 77 на выходе формирует последовательность состояний- а , а«, . .. ,a. Для каждого состояния группы элементов И 89-100 и эл ментов ИЛИ 101-103 вьфабатываются упра ляющие сигналы 27-40, которые управляют работой регистров 1 коэффициентов, преобразователей 2, тригге ров 11, регистра 4 частичных сумм, регистров 9 правых частей, сдвигового регистра 5, блока анализа 7 и группы элементов И 6, и управляющие сигналы, управляющие работой счетчика 76, 78, 81 и 82, триггеров 80 и 75. Элемент И-НЕ 79 выраба;тыва сигнал, который равен единице при нулевом состоянии счетчика 78. Эле ентыИ 83 и 84 формируют на вькоде 1, если значения соответствующих счетчиков 81 и 82 равны С где щ количество разрядов представления информации). Предлагаемый вычислительный узел цифровой сетки позволяет вычислить приближения к решению в двух сосед- них узлах сеточной области по формуламir-si,,b,,«|;;.c,,.,,,. J,-:Ul, ,V:.. i ,н «О «iu,J .. .. . ir.,jH i.j+t 4i,M .j „..1ГЧи, .J + i J.. где jj и j - индексы строки и столбца сеточной области; номер итерации; и - искомое решение задачи в узлах сетки; I - правая часть разностных уравнений, к которым сводится решение дифференциальных уравнений с переменными коэффициента ми разностным методом. Устройство работает по следующему алгоритму. . На входы 43 и 41 с информационной шины поступают в блок 10 управления два сигнала. Сигнал с входа 41 обнуляет счетчик 76, а сигнал 43 устанав ливает в единичное состояние триггер 75, который открывает элемент И 74, первый тактовый импульс с генератора 73 переключает счетчик 76 в состояние 1. На первом выходе дешифратора 77 устанавливается сигнал 1, т.е. состояние а. На выходе блока 10 управления вьфабйтьшается управляющий сигнал 29, по которому в регистры бОпт младших разрядов регистров 1 коэффициентов с входов 12 заносятся коэффициенты для нечетных узлов, а в регистры 61 - коэффициенты для четных узлов с входов 13. По этому же сигналу в регистры 62 и 63 регистра 9 правой части заносятся значения правых частей для нечетных и четных узлов с входов 14 и 15 соответственнОу в регистр 4 частичных сумм - правая часть управлений ( 1) для четных узлов и в счетчик 78 с входа 42 заносится чис-по итераций. В этом же такте по сигналу 33 обнуляется содержимое сдвигового регистра 5. В следующем такте а триггер 80 устанавливается в нулевое состояние, т.е. вычисляются приближения к решению в четных узлах сеточнрй области по формуле (1). Б следующем такте счетчик 76 устанавливается в состояние а, по которому блок 10 управления вьщает сигналы 39 и 34 с выходов элементов ИЛИ 101 и 102 соответственно. По этим сигналам в элементе памяти 44 блока 7 анализа .запоминается младший разряд сдвигового регистра 5 и осуществляется сдвиг регистра 5 в сторону младших разрядов. В этом же такте обнуляется счетчик 81. По следующему тактовому циклу импульсов с генератора 73 счетчик 76 переключается в состояние аь, вьщаются управляющие сигналы 40 и с выхода элемента ИЛИ 101 сигнал 39. По сигналу 40 в элемент памяти 45 блока анализа заносится значение элемента памяти 44, т.е. младщий разряд регистра 5 сдвигов, а по сигналу 39 в элементе памяти 44 запоминается текущий разряд регистра 5, триггер 53 преобразователя 2 кодов устанавливается в 1. На блоке 7 анализа происходит анализ двух мпадших разрядов сдвигового регистра 5 и результат анализа поступает на последовательные входы соседних узлов и на вход одного из коммутаторов 8. Б этом такте обнуляется счетчик 82. В пятом такте осуществляется настройка коммутаторов 8 для пропуска информации на управляющие входы первых двух преобразователей 2 коов. Если выполняется четная итерация (триггер признаков итерации в

нулевом состоянии), то с выхода элемента И выдается управляющий сигнал 38, по которому первьш триггер 11 устанавливается в 1 и первый коммутатор 8 подает на вход первого преоб- 5 разователя кода два управляющих сигнала с выходов 18 и 19 соседнего узл сетки, а второй триггер 11 устанавли вается в О и второй коммутатор 8 Подает на входы второго преобразователя 2 кодов сигналы с блока 7 анализа. Если вьшолняется нечетная итерация, то по сигналу 37 с выхода элемента И 91 первьш триггер 11 устанавливается в О и первый коммута тор 8 к первому преобразователю 2 кодов подает сигналы с выхода блока анализа, а второй триггер 11 устанав ливается в 1 и второй коммутатор 8 передает на входы соответствующего преобразователя 2 кодов сигналы с входов 24 и 25 соседнего узла. Преобразователи 2 кодов настраиваются на пропуск прямого или дополнительного кода регистров 1 коэффициентов. Происходит суммирование младших разрядов регистра 4 частичньгх сумм с регистром 1 коэффициентов на многовходовом сумматоре 3.В этом такте управляющий автомат переключается в состояние а, и вьщает управляющие сигналы 32 и 30 с выхода элемента ИЛИ 103. По этим сигналам регистр .4 частичных сумм сдвигается на один разряд в сторону младших разрядов -и в старщий разряд с выхода многовходо вого сумматора заносится результат суммирования младших разрядов регистров 4 и 1 частичных сумм и коэффициентов . Управляющийавтомат переходит в состояние a-jr. В этом такте осуществляется подготовка для сложения следующих разрядов. Для это го с выхода элемента И 93 выдается управляющий сигнал 27, по которому осуществляется циклический сдвиг в регистре 61 старших разрядов регистра 1 коэффициентов. Таким образом, восстановление коэффициентов в каждо цикле, кроме последнего, осуществляе ся наш тактов. Б последнем |п-м цикл (значение счетчика циклов равно tn, т.е. на выходе многовходового элемен та И 83 присутствует 1) значения коэффициентов и правой части для ура нения (1) по управляющему сигналу 28 с выхода элемента И 92 циклически перезаписьгоаются в регистры 60 и 62 соответственно регистров 1 коэффициентов и регистров 9 части, а в регистры 61 и 63 соответственно регистров коэффициентов и правой части циклически перезаписываются коэффициенты и правая часть для уравнения (2) из регистров 60 и 62 регистров 1 и 9. Если просуммированы не все разряды.коэффициентов и правой части, то в состоянии ад по сигналу с выхода элемента И 100 значение счетчика 82 увеличивается на 1 и по этому же сигналу счетчик тактов переключается в состояние а и все повторяется, т.е. происходит суммирование следуюТаким образом, за Ш щих разрядов тактов (для двумерных задач) в регистре 4 частичных сумм получается сумма частичных произведений от умножения коэффициентов на младший разряд сдвигового регистра 5, которая поступает на вход данного регистра с выхода многовходового сумматора 3. В tT)-M такте (выход логического элемента И 83 равен 1) регистр 4 частичных сумм сдвигается в сторону младших разрядов для уменьшения суммы частичных произведений в два раза, а сдвиговьш регистр 5 - для умножения на следующий разряд, в старший разряд которого перезаписьшается значение младшего разряда регистра 4 частичных сумм. Для выполнения этих операций блок управления в состоянии ag вьщает соответствующие сигналы: с выхода элемента ИЛИ ЮЗ сигнал зО, с, выхода элемента ИЛИ 102 сигнал 34 и с выхода элемента И 90 сигнал 35. На этом заканчивается очередной цикл. Для выполнения следукяцего цикла блок 10 управления переходит в состояние 3.0 и элемент И 99 вьщает сигнал, по которому содержимое счетчика 83 увеличивается на единицу и счетчик 76 устанавливается в состояние а и все повторяется по вышеописанному алгоритму. Таким образом, в последнемт-м такте пг1-го цикла в сдвиговом регистре 5 получается значение очередного приближения, а в регистрах 61 и 62 регистров 1 и 9 записаны-значения коэффициентов и правой части для уравнения (2) . При необходимости индицировать результат или передать его для дальнейшей обработки блок 10 управления в состоянии а при единичном значении выхода элемента И 83 (значение счетчика 81 равно т) 17 вьщает управляющий сигнал 36, по которому значение сдвигового регистра 5 поступает через группу элементов И 6 на выход 26 узла. Если решалось уравнение (1), т.е. триггер 80 равен О, то далее вычисление осуществляется по формуле (2). Для этого счетчик тактов устанавливается в состояние а, управлякяций сигнал 31 с выхода элемента И 96 поступает на управляющий вход регистра 4 частичных сумм и зна чение регистра 61 старших разрядов регистра 5 правой части заносится в регистр 4, т.е. правая часть уравнения (2) пересылается в регистр 4 частичных сумм. Блок управления переходит в состояние а, и управляющий сигнал с выхода элемента И 98 устана 95 ливает триггер 80 в f (вьшолняетсь нечетная итерация) и переключается счетчик 76 в состояние а. Дальнейшие вычисления аналогичны вычислению по формуяе (1). Если решалось уравнение (2), т.е. триггер 80 равен 1, то выполняется следукнцая итерация. Для этого счет-чик 76 переходит в состояние а, с выхода элемента И 97 сигнал поступает на счетный вход счетчика 78, уменьшая его значение на единицу и переводит счетчик тактов в состояние а-. Остальное аналогично вьш1еописанному гшгоритму. Предлагаемое устройство благодаря наличию новых блоков и связей между ними позволяет повысить точность решения дифференциальных уравнений.

12 1Ъ

213

12 1Ъ

Лчг On

Фие. 2

19

27

ФигЛ 56

R

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Вычислительный узел цифровойСЕТКи | 1979 |

|

SU800997A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-30—Публикация

1983-08-12—Подача