(54) ЦИФРОВОЙ КОРРЕЛЯТОР ДЛЯ ОБНАРУЖЕНИЯ ЭХО-СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелятор для обнаружения эхосигналов | 1979 |

|

SU879595A1 |

| Цифровой коррелятор | 1980 |

|

SU940172A1 |

| Цифровой коррелятор | 1980 |

|

SU900289A1 |

| Цифровой коррелятор | 1980 |

|

SU903892A1 |

| Цифровой коррелятор | 1982 |

|

SU1073776A1 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНОГО СИГНАЛА | 1986 |

|

RU2069934C1 |

| Цифровой коррелятор для обнаружения эхо-сигналов | 1983 |

|

SU1107135A1 |

| Цифровой коррелятор для обнаружения эхо-сигналов | 1987 |

|

SU1418748A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 2000 |

|

RU2170444C1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1998 |

|

RU2131612C1 |

. Изобретение ОТНОСИТСЯ к области специализированных средств Вычислительной техники, предназначенной дяя взаимнокорреляционной обработки эхо-сигналов.

Известен аи фрсшой коррелятор содержащий, частотно-импульсный преоб разоватеЛь, логические блоки, блок Задержки, реверсивные счетчики flj.

Однако данный коррелятор характеризуется недостаточно высоким отношением сигнал г шум на выходе.

Изйестен также коррелятрр содержадий Два блока задержки, арифметический блок накапливающий сумматор и блок управления t2j« ;

Недостатком этого корреЛятора является нёидентичность обработки cHt налов (опорного и входного), так как в первый блок задержки записываются прореженные выборки опорного сигнала, а непрореженные выборки входно- го сигнала со второго блока задержки подвергаются перед подачей в арифметический- блок предварительному суммированию. Это приводит к уменьшению трчности вычисления ординат взаимокорреляционной функции (ВКФ)V при чем величины ошибок различны при формировании различных зондирующих сигналов. Кроме того, при обработке непрерьтных сигналов или сигналов значительной длительности требуется непрерывное обновление памяти не только второго, но и первого блока задержки.

Цель изобретения - повышение точности вычисления ординат ВКФ и расигарение функционсшьных возможностей

10 коррелятора.

Сущность изобретения заключается в TOi, что обеспечивается идентичность обработки входного и опорного сигналов включая непрерывное обнов15ление информации в коррёклятора..

Поставленная цель достигаете тем, что в цифровой коррелятор хшя обнаружения эхо-сигналов, содержащий первый

20 и второй блоки задержки, входы которых являются соответственно первым и вторым входами коррелятора, в выход второго блока задержки соединен со входом nepBOJTo накапливающего сум25матора, выход которого подключен к первому входу арифметического блока, входы синхронизации арифметического блока и накапливакхкего сумматора подключены к Первому выходу блока уп30рав ления в торой выход которого срединен с управляющими входами блоков задержки, введен второй накапливающий сумматор, вход которого подключе к выходу первого блока задержки, выход соединен со вцорым входом арифметического блока, а вход синхрониэации второго накапливайщего сумматора подключен к первому блока управления.

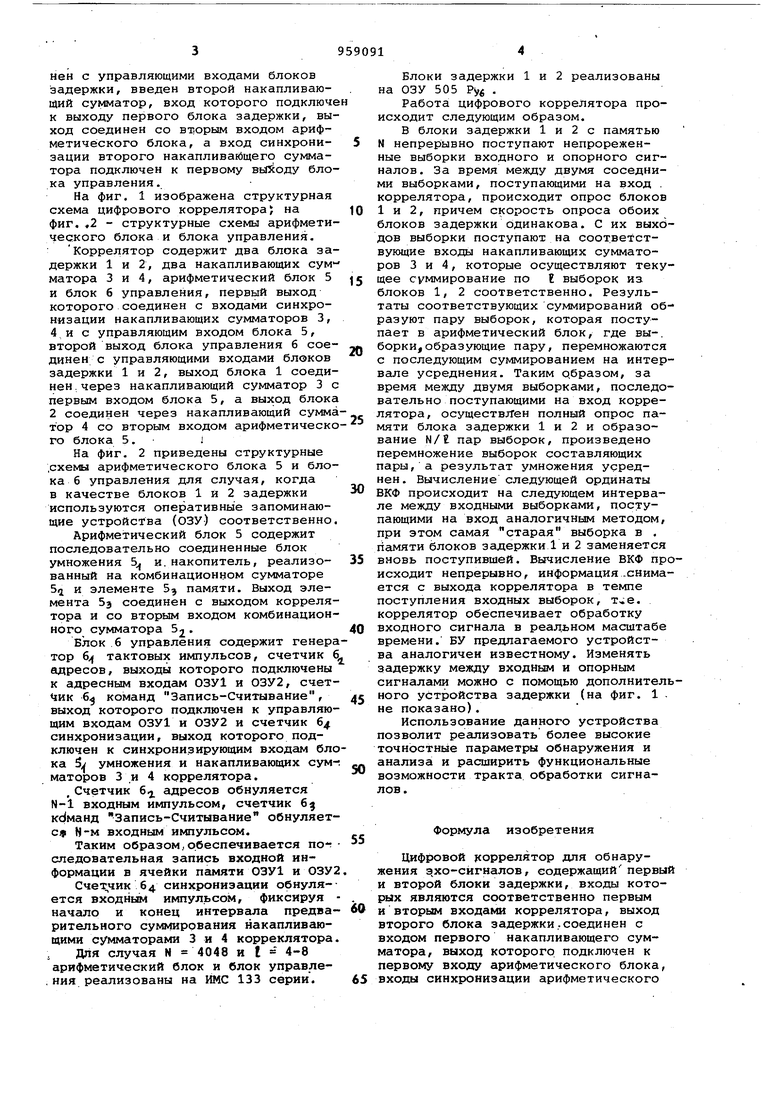

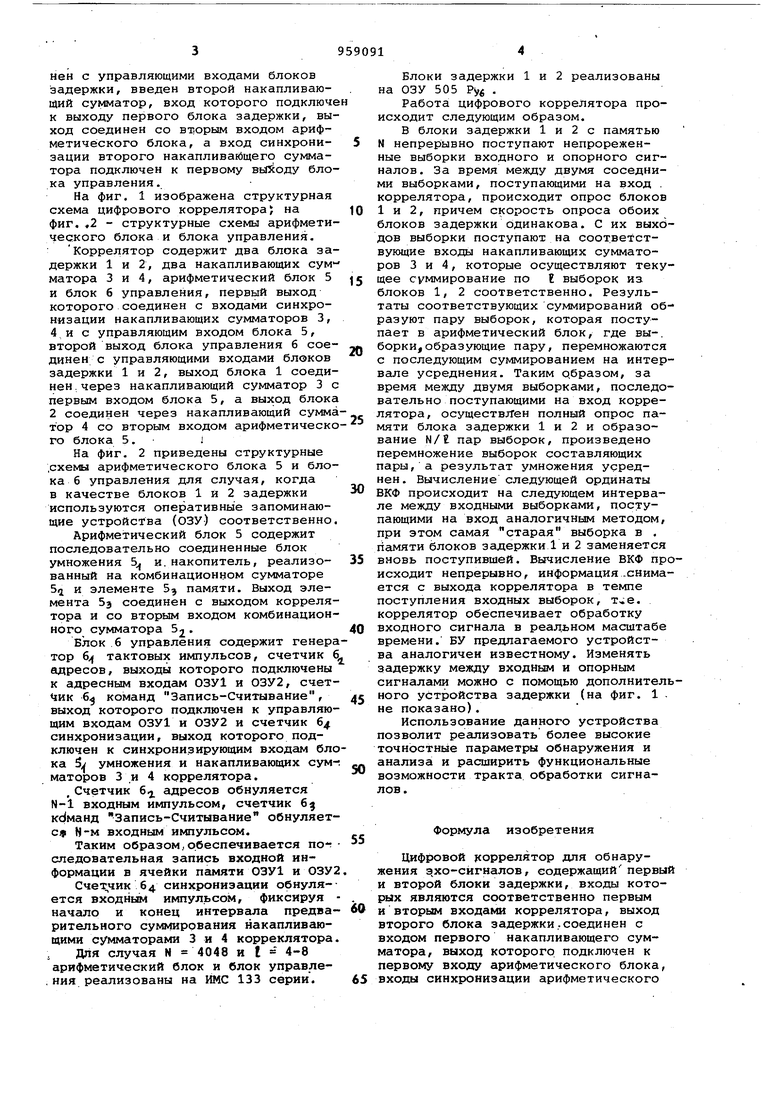

На фиг. 1 изображена структурная схема цифрового коррелятора на фиг. ,2 - структурные схемы арифметического блока и блока управления. Коррелятор содержит два блока задержки 1 и 2, два накапливающих сум матора 3 и 4, арифметический блок 5 и блок 6 управления, первый выход которого соединен с входами синхронизации накапливающих сумматоров 3, 4 и с управляющим входом блока 5, второй выход блока управления б соединен с управляющими входами блоков задержки 1 и 2, выход блока 1 соединен ,через накапливающий сумматор 3 с первым входом блока 5, а выход блока 2 соединен через накапливающий сумма тор 4 со вторым входом арифметического блока 5. J

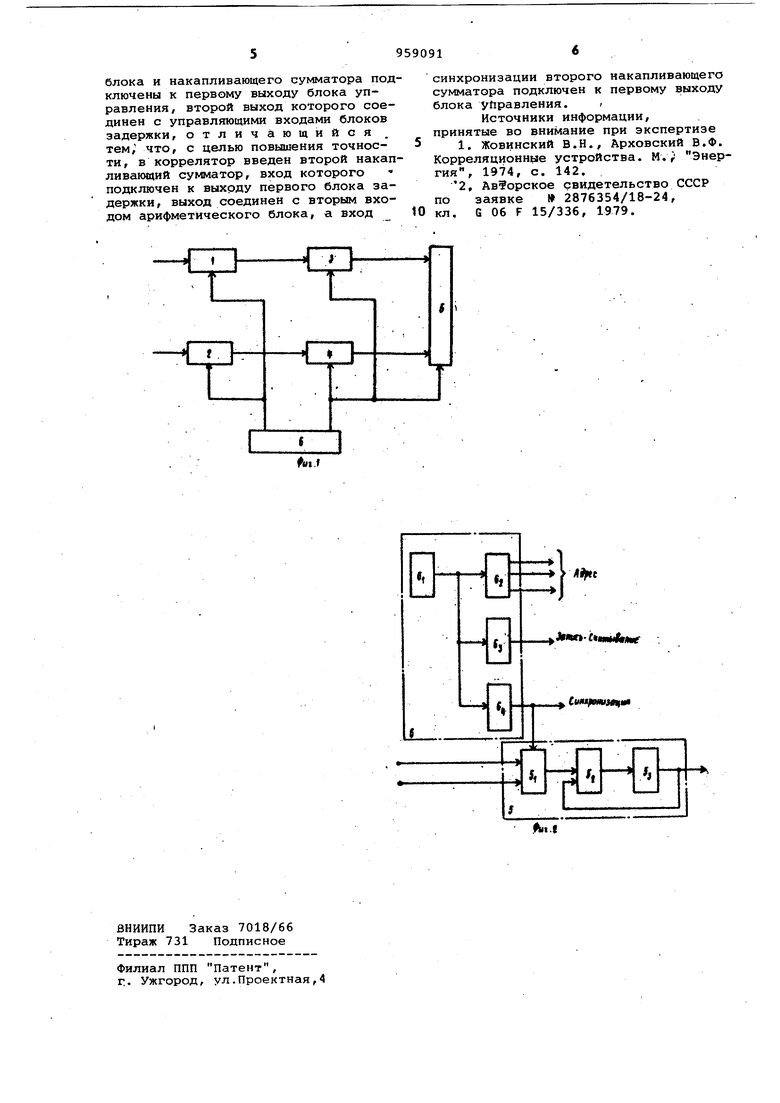

На фиг. 2 приведены структурные .схемы арифметического блока 5 и блока 6 управления для случая, когда в качестве блоков 1 и 2 задержки используются оперативные запоминающие устройства (ОЗУ) соответственно.

Арифметический блок 5 содержит последовательно соединенные блок умножения 5| и.накопитель, реализованный на комбинационном сумматоре и элементе БЗ памяти. Выход элемента 5э соединен с выходом коррелятора и со вторым входом комбинационного сумматора 5.

Блок 6 управления содержит генератор 6 тактовых импульсов, счетчик 6 адресов, выходы которого подключены к адресным входам ОЗУ1 и ОЗУ2, счет 1ик 6 команд Запись-Считывание, выход которого подключен к управляющим входам ОЗУ1 и ОЗУ2 и счетчик 64 синхронизации, выход которого подключен к синхронизирующим входам блока 3v умножения и накапливающих сумматоров 3 и 4 коррелятора.

, Счетчик 6 адресов обнуляется N-i входным импульсом, счетчик 6 Запись-Считывание обнуляетcjf входным импульсом.

Таким образом, обеспечивается по-г следовательная запись входной информации в ячейки пс1мяти ОЗУ1 и ОЗУ2

64 синхронизации обнуляется входнь1М импульсом, фиксируя начало и конец интервгша предварительного суммирования накапливающими сумматорами 3 и 4 корреклятора.

Для случая N 4048 и I 4-8 арифметический блок и блок управле.ния реализованы на ИМС 133 серии.

Блоки задержки 1 и 2 реализованы на ОЗУ 505 Ру .

Работа цифрового коррелятора происходит следующим образом.

В блоки задержки 1 и 2 с памятью N непрерывно поступают непрореженные выборки входного и опорного сигналов. За время между двумя соседними выборками, поступающими на вход . коррелятора, происходит опрос блоков 1 и 2, причем скорость опроса обоих блоков задержки одинакова. С их выходов выборки поступают на соответствующие входы накапливающих сумматоров 3 и 4, которые осуществляют текущее суммирование по выборок из блоков 1, 2 соответственно. Результаты соответствующих суммирований образуют пару выборок, которая поступает в арифметический блок, где вы-. борки,образующие пару, перемножаются с последующим суммированием на интервале усреднения. Таким о,бразом, за время между двумя выборками, последовательно поступающими на вход коррелятора, осуществЛен полный опрос памяти блока задержки 1 и 2 и образование N/E пар выборок, произведено перемножение выборок составляющих пары, а результат умножения усреднен. Вычисление следующей ординаты ВКФ происходит на следующем интервале между входными выборками, поступающими на вход аналогичным методом, при этом самая старая выборка в . Пс1мяти блоков задержки 1 и 2 заменяется вновь поступившей. Вычисление ВКФ присходит непрерывно, информация .снимается с выхода коррелятора в темпе поступления входных выборок, т-;е. коррелятор обеспечивает обработку входного сигнала в реадьном масштабе времени. БУ предлагаемого устройства аналогичен известному. Изменять задержку между входным и опорным сигналами можно с помощью дополнителного устройства задержки (на фиг. 1 не показано).

Использование данного устройства позволит реализовать более высокие точностные параметры обнаружения и анализа и расширить функциональные возможности тракта обработки сигналов.

Формула изобретения

Цифровой коррелятор для обнаружения э,хо-сйгналов, содержащий первы и второй блоки задержки, входы которых являются соответственно первым и вторым входами коррелятора, выход второго блока задержки ..соединен с входом первого накапливающего сумматора, выход которого подключен к первому входу арифметического блока, входы синхронизации арифметического

блока и накапливающего сумматора подключены к первому выходу блока управления, второй выход которого соединен с управляющими входами блоков задержки, отличающийся тем, что, с целью повышения точности, в коррелятор введен второй накапливающий сумматор, вход которого подключен к выходу первого блока задержки, выход соединен с вторым входом арифметического блока, а вход

синхронизации второго накапливающего сумматора подключен к первому выходу блока уйравления. i

Источники информации, принятые во внимание при экспертизе

1, Жовинский В.Н., Арховский В.Ф. Корреляционные устройства. М. Энергия, 1974, с. 142.

2, Авторское свидетельство СССР по заявке 2876354/18-24, кл. G 06 F 15/336, 1979.

/tiftt

Дтп-амм1м|«,CuMfH ite e

Авторы

Даты

1982-09-15—Публикация

1980-12-11—Подача