лов, выполнякяцих операции умножения и усреднения.

Целью изобретения является упрощение коррелятора, снижение потребляемой мощности, и увеличение его надежности, за счет сокращения количества каналов АУ, а также уменьшение объема памяти в одном из уст- ройств задержки.

Поставленная- цель достигается тем, что в цифровой коррелятор для обнаружения эхосигналов, содержащий два блока задержки, входы которых Являются соответственно первым и вторым входами коррелятора, и арифметический блок, первый вход которого соединен с выходом первого блока задержки. Управляющие входы арифметического блока и блоков задержки соединены с соответствукяцими выходами блока управления, введен накапливагаций сумматор, вход которого подключен к выходу второго блока задержки, выход соединен со вторь1м входом арифметического блока, а вход синхронизации накапливакхцего сумматора объединен с управляющим входом арифметического блока.

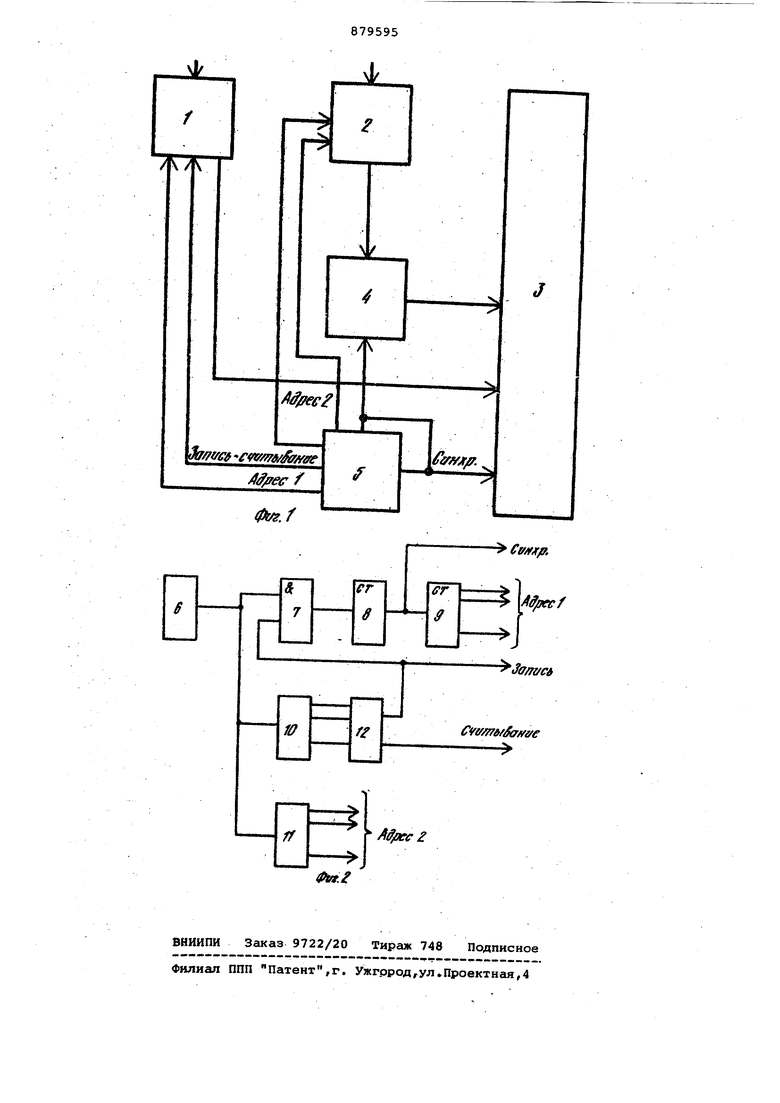

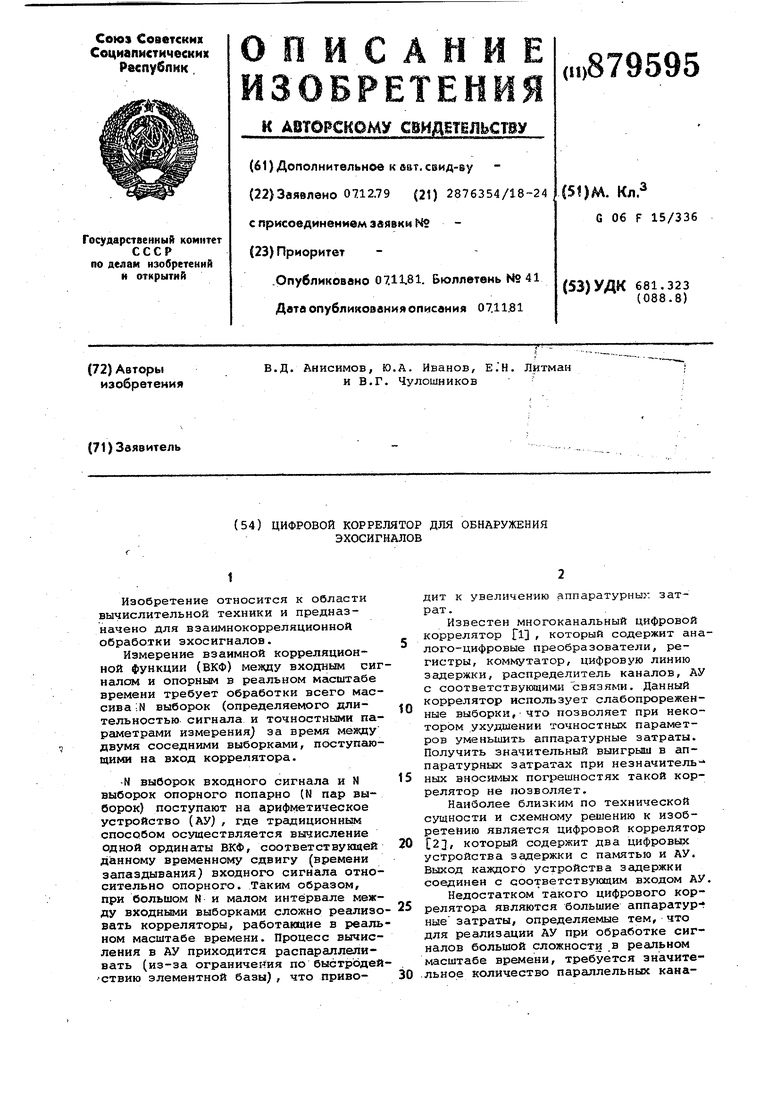

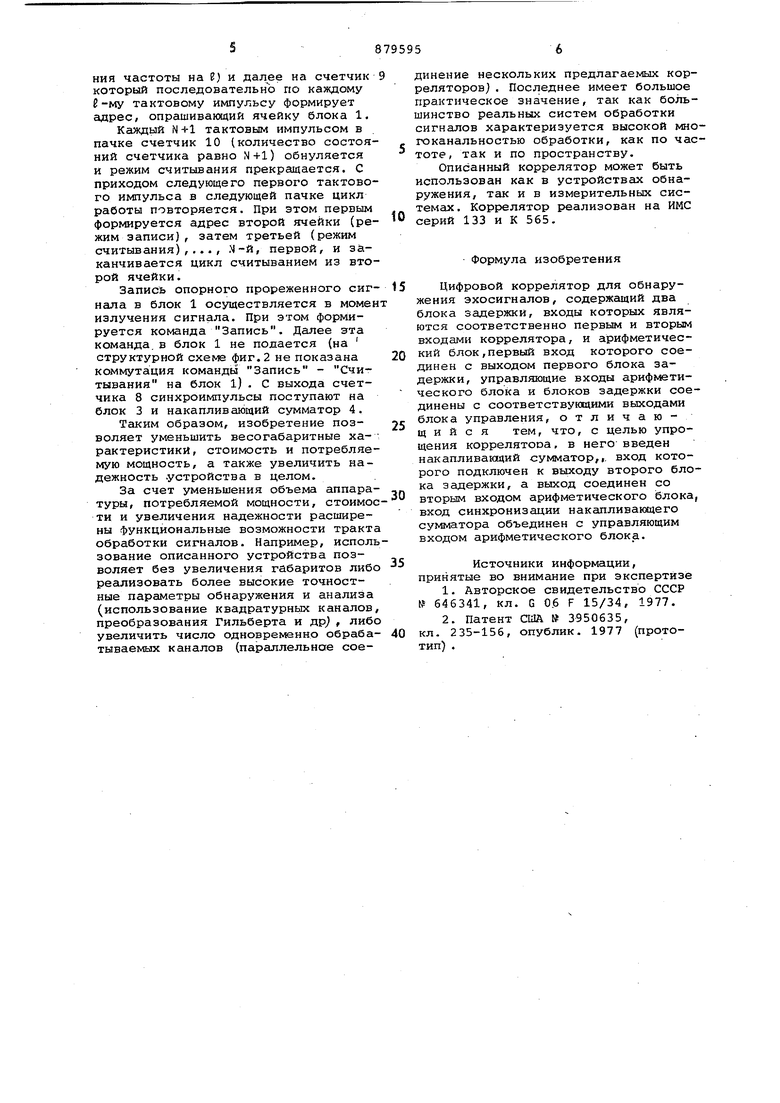

На фиг.1 показана структурная схема цифрового коррелятора для обнаружения эхосигналов) нафиг.2 структурная схема блока управления. Коррелятор содержит два блока 1, 2 задержки, арифметический блок 3, накапливающий cyivMaTop 4, блок 5 управления, генератор б тактовых импульсов, элемент И 7, счетчики 8-11 и дешифратор 12.

Цифровой коррелятор для обнаружения эхосигналов работает следующим .образом.

в блок 1 задержки (с памятью) объемом N/8 записываются (обычно в момент излучения зондирующего сигнала) прбреженные М/ выборок опорного сигнала, где 6 - количество непрореженных выборок входного сигнала н интервале двумя соседними прореженными выборками опорного сигнала. В блок 2 задержки (с памятью N) непрерывно поступают непрореженные выборки входного сигнала. За время между двумя выборками, поступаквдими на вход блока 2, происходит опрос блоков 1,2, причем скорость опроса блока 1 в Р раз меньше, чем скорост опроса блока 2. Накапливающий сумматор 4 осуществляет суммирование непрореженных выборок из блока 2. Результат суммирования совместно с соответствующей прореженной вйборкой (поступающей из блока 1 в момен снятия результата суммирования) образуют пару выборок, которая поступет в арифметический блок 3, где выборки, образующие пару, перемножаются, а результаты перемножения суммируются и накапливаются в арифметическом блоке 3. Таким образом, за время между двумя непрореженными

выборками, последовательно поступающими на вход коррелятора, осуществлен полный опрос памяти блоков 1 и 2, образовано N/E пар выборок, произведено перемножение выборок, составляющих пары, а результат умножения усреднен. Вычисление очередной ординаты происходит на следующем интервале между выборками, поступающими на вход аналогичным методом. При этом самая старая выборка в

памяти блока 2 заменяется вновь поступившей. Вычисление ВКФ происходит непрерывно, информация снимается с выхода коррелятора в темпе поступления информации на вход, т.е. корj релятор обеспечивает обработку сигнала в реальном масштабе времени.

Это позволяет, не изменяя шага дискретности вычисления ВКФ,уменьшать количество выборок, поступающих

,. в блок 3 на интервале усреднения, что приводит к уменьшению аппаратурных затрат в арифметическом блоке 3 и объема памяти одного блока задержки.

Блок 5 управления работает следующим образом. Генератор 6 периоди5 чески-формирует пачки по N+1 импульсов. Первые импульсы в пачках совпадают с моментами прихода входных выборок на коррелятор. Выход генератора б соединен с соответствующими входами элемента 7 И и счетчиков 10 и 11. На йыходах счетчика 11 (количество состояний счетчика равно N) устанавливается адрес блока задержки 2, По каждому первому тактовому импульJ су в пачке осуществляется запись в соответствующую ячейку блока 2 входной выборки.сигнала. Счетсик 11 последовательно формирует ,V адресов (каждому первому тактовому импульсу в пачке соответствует свой адрес),

а после N-ro адреса цикл повторяется. После блока 2 очередная входная выборка записывается в ячейку, в которой хранилась самая старая выборка. Таким образом, информация блока 2 постоянно обновляется, и в нем хранится N последних текущих выборок входного сигнала. Каждый первый тактовый импульс в пачке, поступающий на счетчик 10, устанавливает его

0 состояние, при котором на выходе.дешифратора 12 формируется команда, - переводящая блок 2 в режим записи и 3апрешакшая прохождение тактовых импульсов через элемент И 7.

Со второго по N+1 тактовыми импульсами в пачках осуществляется опрос всех ячеек блоков 1 и 2. Счетчик 10 совместно с дешифратором 12 вторыми тактовыми импульсами в пачках формируют вместо команды Запись - коО манду Считывание и снимает запрет на прохождение тактовых импульсов через элемент 7.

N тактовых импульсов (с 2-го по N+1) в каждой пачке поступают на счетчик 8 (работающий в режит е деления частоты на ) и далее на счетчик который последовательнЪ по каждому -му тактовому импульсу формирует адрес, опрашивающий ячейку блока 1. Каждый N-i-1 тактовым импульсом в пачке счетчик 10 (количество состоя ний счетчика равно N+1) обнуляется и режим считывания прекращается. С приходом следующего первого тактово го импульса в следующей пачке цикл работы повторяется. При этом первым формируется адрес второй ячейки (режим записи), затем третьей (режим считывания),..., , первой, и заканчивается цикл считыванием из вто рой ячейки. Запись опорного прореженного сиг нала в блок 1 осуществляется в момен излучения сигнала. При этом формируется команда Запись. Далее эта команда.в блок 1 не полается (на структурной схеме фиг. 2 не показана коммутация команды Запись - Считывания на блок 1). С выхода счетчика 8 синхроимпульсы поступают на блок 3 и накапливающий сумматор 4. Таким образом, изобретение позволяет уменьшить весогабаритные характеристики, стоимость и потребляемую мощность, а также увеличить надежность .устройства в целом. За счет уменьшения объема аппаратуры, потребляемой мощности, стоимос ти и увеличения надежности расширены функциональные возможности тракта обработки сигналов. Например, исполь зование описанного устройства позволяет без увеличения габаритов либо реализовать более высокие точностные параметры обнаружения и анализа (использование квадратурных каналов, преобразования Гильберта и др , либо увеличить число одновременно обрабатываемых каналов (параллельное соединение нескольких предлагаемых корреляторов) . Последнее имеет большое практическое значение, так как большинство реальных систем обработки сигналов характеризуется высокой мноххэканальностью обработки, как по частоте, так и по пространству. Описанный коррелятор может быть использован как в устройствах обнаружения, так и в измерительных системах. Коррелятор реализован на ИМС серий 133 и К 565. Формула изобретения Цифровой коррелятор для обнаружения эхосигналов, содержащий два блока задержки, входы которых являются соответственно первым и вторым входами коррелятора, и арифметический блок,первый вход которого соединен с выходом первого блока задержки, управляющие входы арифметического блока и блоков задержки соединены с соответствующими выходами блока управления, отличающийся тем, что, с целью упрощения коррелятооа, в него введен накапливающий сумматор,, вход которого подключен к выходу второго блока задержки, а выход соединен со вторым входом арифметического блока, вход синхронизации накгипливающего сумматора объединен с управляющим входом арифметического блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 646341, кл. G 06 F 15/34, 1977. 2.Патент США № 3950635, кл. 235-156, опублик. 1977 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелятор для обнаружения эхо-сигналов | 1980 |

|

SU959091A1 |

| Цифровой коррелятор | 1980 |

|

SU940172A1 |

| Цифровой коррелятор | 1980 |

|

SU903892A1 |

| Цифровой коррелятор | 1980 |

|

SU900289A1 |

| Цифровой коррелятор для обнаружения эхо-сигналов | 1983 |

|

SU1107135A1 |

| Цифровой коррелятор | 1982 |

|

SU1073776A1 |

| Цифровой фильтр | 1985 |

|

SU1264308A1 |

| Цифровой коррелятор | 1984 |

|

SU1264201A1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| Цифровой коррелятор | 1986 |

|

SU1328825A1 |

Авторы

Даты

1981-11-07—Публикация

1979-12-07—Подача