(54) УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ОДНОКРАТНЫХ . ПРОЦЕССОВ 1 Изобретение относится к вычислительной и измерительной технике и может быть использовано для исследования формы однократного процесса и измерения его параметров. Известно устройство для регистрации однократных процессов, содержащее усилитель, выход которого соединен с входом аналого-цифрового преобразователя, первый блок памяти, вход которого подключен к первому выходу блока управления, а выходы соединены с входами дешифратора, выходы которого подключены к входам первой группы блока отображения, с входами второй rpiynnbi которого соединены выходы блока развертки, вход которого подключен к первому выходу генератора тактовых импульсов и первому входу блока управления, второй выход которого соединен с входом генератора тактовых импульсов, второй выход которого подключен к входу индикатора длительности развертки 1. Недостатком этого устройства является большая погрешность регистрации формы однократного процесса, когда условия эксперимента усугублены наличием шумовых компонент, т. е. при регистрации смеси сигнала и шума на блок отображения выводятся дискретные отсчеты, по которым трудно судить о форме исследуемого процесса и тем более производить измерения его параметров. Наиболее близким к предлагаемому является устройство, содержащее усилитель, выход которого соединен с входом аналогоцифрового преобразователя и входом блока выделения границ сообщения, первый и второй коммутаторы, входы групп которых подключень к выходам аналого-цифрового преобразователя и вьГходам первого блока памяти, входы группы которого соединены с выходами третьего коммутатора, входы группы третьего коммутатора .подключены к выходам второго и третьего блоков памяти, входы групп которых соединены соответственно с выходами первого и второго коймутаторов, входы первого, второго и третьего блоков памяти, первого, второго и третьего коммутаторов подключены к выходам групп блока управления соответственно, выходы первого блока памяти соединены с

входами дешифратора, выходы которого подключены к входам первой группы блока отображения, входы второй группы которого соединены с выходами блока развертки, вход которого подключен к первому выходу генератора тактовых импульсов и первому входу блока управления, второй вход которого соединен с выходом блока выделения границ сообщения, выход блока управления подключен к входу генератора тактовых импульсов, второй выход которого соединен с индикатором длительности развертки 2.

Недостатком этого устройства является потеря половины информации в процессе регистрации исследуемого сигнала вследствие исключения отдельных отсчетов из-за ограниченного объема памяти, что также вносит дополнительную погрешность.

Цель изобретения - повышение надежности устройства путем восстановления сигналов в процессе адаптации к их длительности.

Поставленная цель достигается тем, что в устройство, содержащее усилитель, соединенный с аналого-цифровым преобразователем и блоком выделения границ сообщения, первый и второй блоки памяти, первый и второй коммутаторы, первые входы которых подключены к первому и второму выходам блока управления дешифратор, выходы которого соединены с одними входами блока отображения, другие входы которого подключены к выходам блока развертки, вход которого подключен к первому выходу генератора тактовых импульсов и к первому входу блока управления, второй вход которого соединен с выходом блока выделения границ сообщения, а третий выход блока управления соединен с входом генератора тактовых импульсов, второй выход которого подключен к входу индикатора длительности развертки, введены первый, второй, третий и четвертый регистры, первый и второй сумматоры, блок формирования кода адреса, причем выходы аналого-цифрового преобразователя соединены с входами групп входов первого и второго регистров, входы которых подключены к четвертому и пятому выходам блока управления, выходы первого и второго регистров соединены с соответствующими вхо дами первого сумматора, выходы которого подключены к входам первой группы первого коммутатора, входы второй группы первого коммутатора подключены к выходам второго сумматора, выходы первого коммутатора соединены с входами первых групп первого и второго блоков памяти, входы вторых групп которых подключены к выходам первой и второй групп блока формирования кода адреса соответственно, третий выход блока формирования кода адреса с третьим входом блока управления, шестой выход которого подключен к входу блока формирования кода адреса, выходы первого и второго блоков памяти соединены с выходами первой и второй групп второго коммутатора, выходы которого подключены к входам дешифратора и к входам групп входов третьего и четвертого регистров, входы которых подключены к седьмому и восьмому выходам блока управления, выходы третьего и четвертого регистров соединены с соответствую0 щими входами второго сумматора.

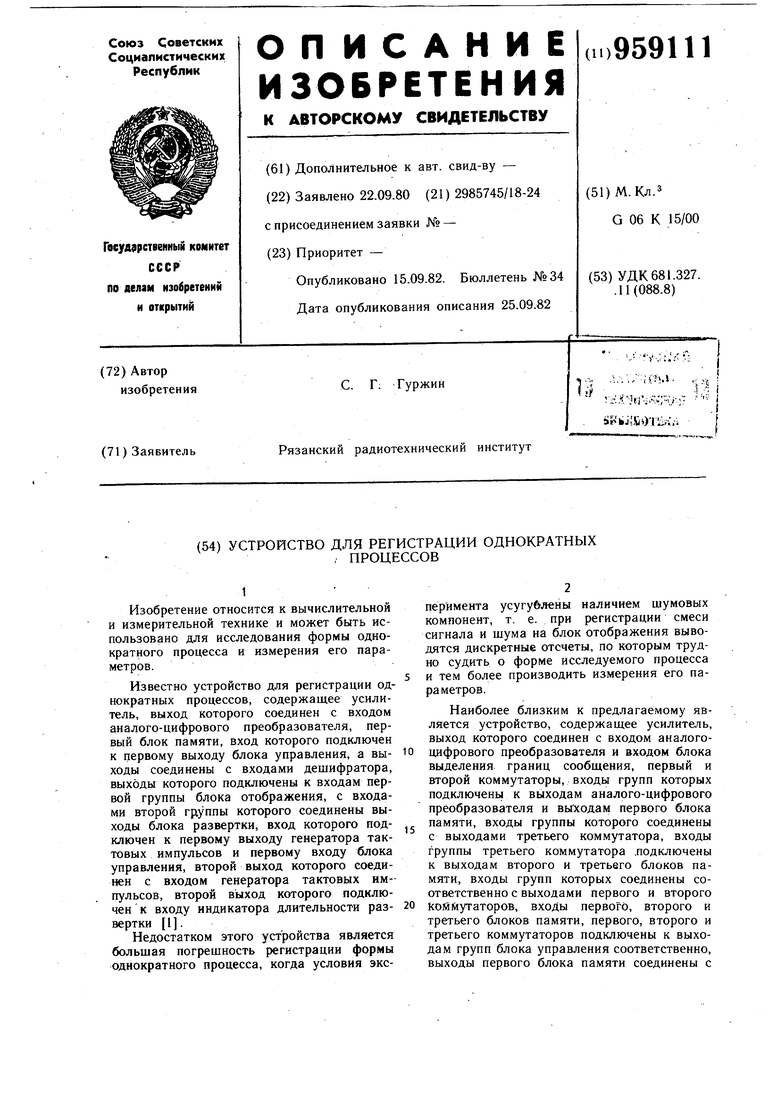

Кроме того, блок формирования кода адреса содержит первый и второй триггеры, третий и четвертый коммутаторы и первый и второй счетчики, причем входы первого и второго триггеров, первый вход третьего коммутатора и первый вход первого и второго счетчиков являются входами блока формирования кода, первый выход первого триггера соединен с вторым входом третьего коммутатора и первым входом

четвертого коммутатора, второй выход первого триггера подключен к третьему входу третьего коммутатора и к второму входу четвертого коммутатора, первый выход второго триггера соединен с третьим входом четвертого коммутатора, четвертый и пятый входы которого соединены с первым выходом первого и второго счетчиков, второй выход второго триггера подключен к четвертому входу третьего коммутатора, выходы которого соединены с вторым входом первого и второго счетчиков, выходы группы первого счетчика и первый выход четвертого коммутатора являются первым выходом блока формирования кода адреса, выходы группы второго счетчика и второй выход четвертого коммутатора являются

5 вторым выходом блока формирования кода адреса, а первые выходы первого и второго счетчиков являются третьим выходом блока формирования кода адреса.

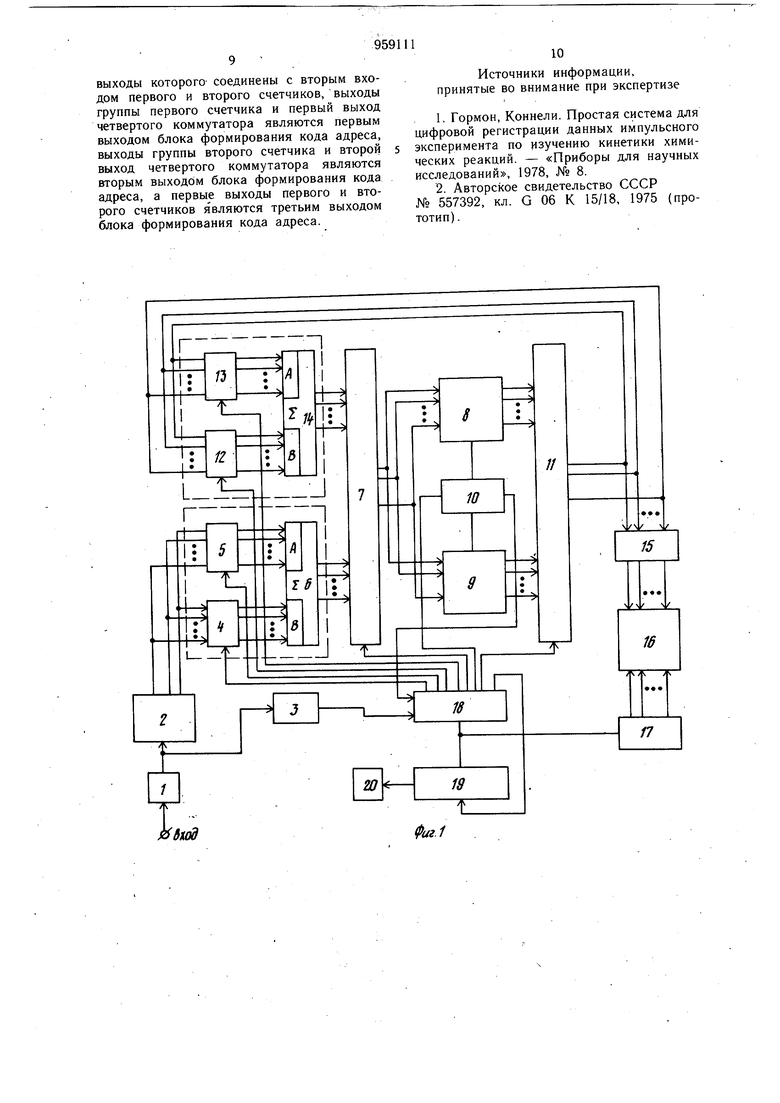

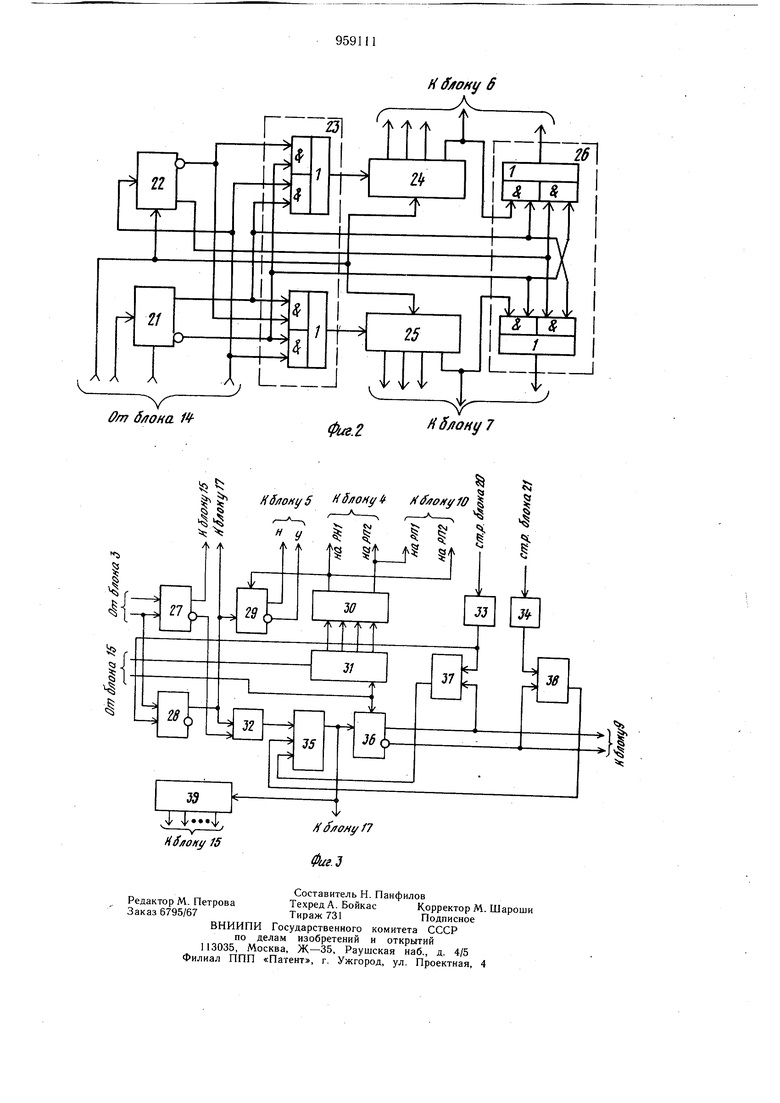

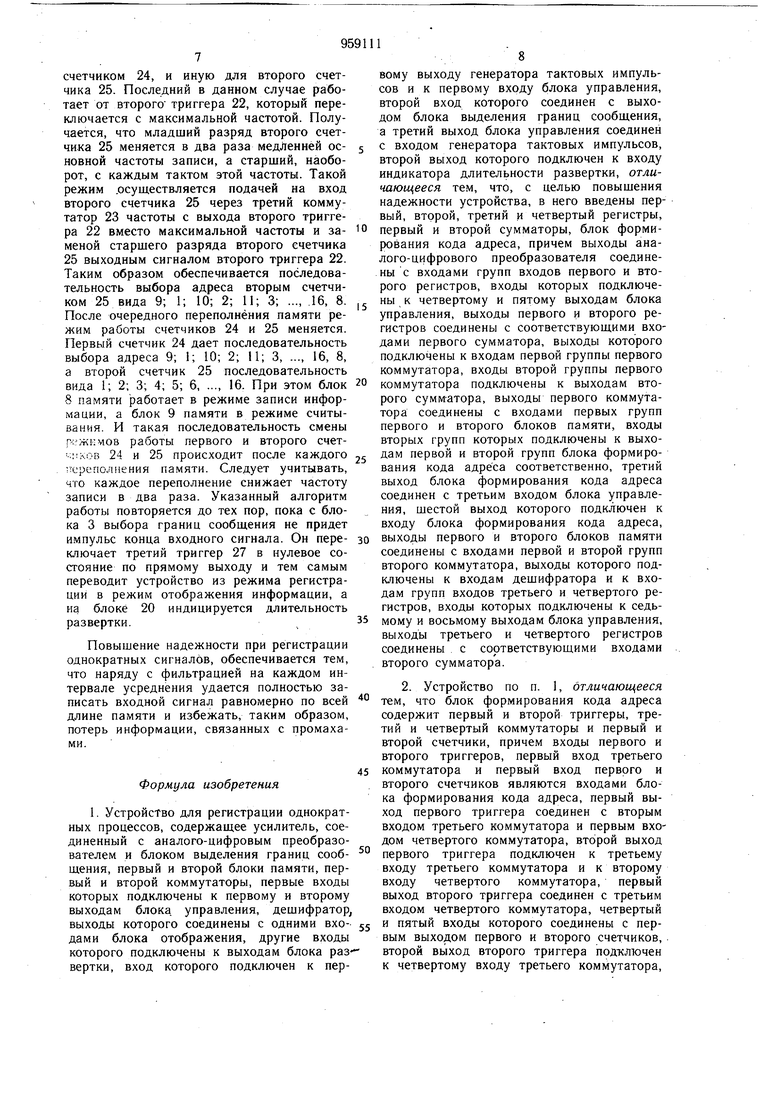

На фиг. 1 изображена структурная схеQ ма предлагаемого устройства; на фиг. 2 - структурная схема блока формирования кода адреса; на фиг. 3 - структурная схема блока управления.

Устройство для регистрации однократных процессов содержит усилитель 1, аналого-цифровой преобразователь 2, блок 3 выделения границ сообщения, первый регистр 4, второй регистр 5, первый, сумматор 6, первый коммутатор 7, первый блок 8 памяти, второй блок 9 памяти, блок 10 ° формирования кода -адреса, второй коммутатор 11, третий регистр 12, четвертый регистр 13, второй сумматор 14, первый дешифратор 15, блок 16 отображения, блок 17 развертки, блок 18 управления, генератор тактовых импульсов 19, индикатор длительности развертки 20, первый триггер 21, второй триггер 22, третий коммутатор 23, первый счетчик 24, второй счетчик 25, четвертый коммутатор 26, третий триггер 27, четвертый триггер 28, пятый триггер 29, второй дешифратор 30, третий счетчик 31, первый формирователь 32, второй формирователь 33, третий формирователь 34, элемент ИЛИ 35, шестой триггер 36, элементы И 37 и 38, четвертый счетчик 39.

Принцип работы устройства заключается в следующем.

Входной сигнал вместе с помехой, усиленный усилителем 1, поступает на аналогоцифровой преобразователь 2 и одновременно на блок 3 выделения граТ1иц сообщения. Сигнал, характеризующий начало процесса, с блока 3 выделения границ сообщения устанавливают через блок 18 управления, генератор тактовых импульсов 19 в режим генерирования максимальной частоты. Эта частота проходит на блок 18 управления, где осуществляется ее временное распределение на такты записи кодированных значений ординат входного сигнала, поступающих с выходов аналого-цифрового преобразователя 2, в регистры памяти 4 и 5. Средние значения попарно взятых отсчетов подаются с выходов первого сумматора 6 усреднителя через первый коммутатор 7 на входы обоих блоков 8 и 9 памяти. Блок 18 управления при этом устанавливает с помощью блока 10 формирования кода адреса первый блок 8 памяти в режим записи информации, а второй блок 9 памяти в режим считывания. С этого момента происходит заполнение первого блока 8 памяти средними значениями последовательно взятых попарно соседних ординат регистрируемого процесса с максимально возможной частотой генератора тактовых импульсов 19.

Импульс, свидетельствующий о начале однократного сигнала, поступает с блока 3 сообщения и устанавливает третий триггер 27 в единичное состояние по прямому выходу. Эта команда обеспечивает включение генератора тактовых импульсов 19 и поступление максимальной частоты записи. Одновременно импульсом начала производится переключение четвертого триггера 28, который своим выходом устанавливает в единичное состояние первый триггер 21 и пятый триггер 29 по прямым выходам и держит их в этом состоянии до момента первого переполнения блока 8 памяти. Таким образом обеспечивается пропускание на входы блока 8 цамяти через первый коммутатор 7 только средних значений новых отсчетов и выбор адреса счет чиком 24 в виде последовательности 1, 2, 3, 4, 5, ..., 16 на начальном периоде усреднения в режиме работы «Запись блока 8 памяти. Взятие новых отсчетов осуществляется тактами с дешифратора 30, разнесенными на один период основной частоты. Частота поступает с генератора тактЬвых импульсов 19 и обеспечивает работу счетчика 31. Установка режима работы блоков 8 и 9 памяти осуществляется шестым триггером 36, который срабатывает в первый момент от импульса «Начдло, поступающего с первого формирователя 32 через элемент ИЛИ 35. Этот же импульс подтверждает состояние первого триггера 21 по счетному входу и записывает в четвертом счетчике 39 первый диапазон. Последний используется как для управления генератором тактовых импульсов 19, т. е. выборки интервала усреднения, так и для определения диапазона длительности, в котором находится исследуемый сигнал.

С приходом первого импульса переполнения с блока 8 памяти, поступающего через второй формирователь 33 на четвертый триггер 28, снимается запрет с первого триггера 21 и пятого триггера 29 и разрешается работа по их счетным входам. Пятый триггер 29 своими выходами начинает переключать первый коммутатор 7, пропуская на вход памяти то средние значения новых отсчетов, то средние значения усредненных отсчетов. Коммутация проводится в середине интервала усреднения. Первый триггер 21 переключается импульсами переполнения первого и второго счетчиков 24 и 25, тем самым попеременно меняя их функции или последовательность выбора адреса. Этими же импульсами переполнения, поступающими с выходов второго и третьего формирователей 33 и 34, через одну из схем И и схему ИЛИ 35 производится поочередное переключение шестого триггера 36 и смена диапазона четвертого счетчика 39. Выходы пятого триггера 29 управляют вторым коммутатором 11, осуществляя прохождение информации то с одного, то с другого блоков 8 и 9 памяти.

Одновременно с блоком 18 управления работает блок 10 формирования кода адреса. Импульс, соответствующий началу входного сигнала, поступающий с блока 18 управления, устанавливает первый триггер 21 в единичное состояние по прямому выходу, что обеспечивает прохождение максимальной частоты через третий коммутатор 23 на вход первого счетчика 24 и подключение старшего разряда первого счетчика 24 через четвертый коммутатор 26 к блоку 8 памяти. В этом режиме осуществляется обычный, последовательный перебор адресов О, 1, 2, 3, 4, 5, ..., 16. Блок 8 памяти в этом случае работает в режиме записи информации. После выбора последнего адреса 16 производится смена режима работы блоков 8 и 9 памяти. Блок 8 памяти переключается в режим считывания информации, а блок 9 памяти в режим записи. Первый триггер 21 остается в прежнем состоянии, чем обеспечивает ту же последовательность выбора адреса первым счетчиком 24, и иную для второго счетчика 25. Последний в данном случае работает от второго триггера 22, который переключается с максимальной частотой. Получается, что младший разряд второго счетчика 25 меняется в два раза медленней основной частоты записи, а старший, наоборот, с каждым тактом этой частоты. Такой режим .осуществляется подачей на вход второго счетчика 25 через третий коммутатор 23 частоты с выхода второго триггера 22 вместо максимальной частоты и заменой старшего разряда второго счетчика 25 выходным сигналом второго триггера 22. Таким образом обеспечивается последовательность выбора адреса вторым счетчиком 25 вида 9; 1; 10; 2; 11; 3; ..., .16, 8. После очередного переполнения памяти режим работы счетчиков 24 и 25 меняется. Первый счетчик 24 дает последовательность выбора адреса 9; 1; 10; 2; 11; 3, ..., 16, 8, а второй счетчик 25 последовательность вида 1; 2; 3; 4; 5; 6, ..., 16. При этом блок 8 памяти работает в режиме записи информации, а блок 9 памяти в режиме считывания. И такая последовательность смены г-:--жкмов работы первого и второго счет -;:ixoB 24 и 25 происходит после каждого переполнения памяти. Следует учитывать, что каждое переполнение снижает частоту записи в два раза. Указанный алгоритм работы повторяется до тех пор, пока с блока 3 выбора границ сообщения не придет импульс конца входного сигнала. Он переключает третий триггер 27 в нулевое состояние по прямому выходу и тем самым переводит устройство из режима регистрации в режим отображения информации, а на блоке 20 индицируется длительность развертки. Повышение надежности при регистрации однократных сигналов, обеспечивается тем, что наряду с фильтрацией на каждом интервале усреднения удается полностью записать входной сигнал равномерно по всей длине памяти и избежать, таким образом, потерь информации, связанных с промахами. Формула изобретения 1. Устройство для регистрации однократных процессов, содержащее усилитель, соединенный с аналого-цифровым преобразователем и блоком выделения границ сообщения, первый и второй блоки памяти, первый и второй коммутаторы, первые входы которых подключены к первому и второму выходам блока, управления, дешифратор, выходы которого соединены с одними входами блока отображения, другие входы которого подключены к выходам блока развертки, вход которого подключен к первому выходу генератора тактовых импульсов и к первому входу блока управления, второй вход которого соединен с выходом блока выделения границ сообщения, а третий выход блока управления соединен с входом генератора тактовых импульсов, второй выход которого подключен к входу индикатора длительности развертки, отличающееся тем, что, с целью повыщения надежности устройства, в него введены первый, второй, третий и четвертый регистры, первый и второй сумматоры, блок формирования кода адреса, причем выходы аналого-цифрового преобразователя соединены с входами групп входов первого и второго регистров, входы которых подключены к четвертому и пятому выходам блока управления, выходы первого и второго регистров соединены с соответствующими входами первого сумматора, выходы которого подключены к входам первой группы первого коммутатора, входы второй группы первого коммутатора подключены к выходам второго сумм-атора, выходы первого коммутатора соединены с входами первых групп первого и второго блоков памяти, входы вторых групп которых подключены к выходам первой и второй групп блока формирования кода адреса соответственно, третий выход блока формирования кода адреса соединен с третьим входом блока управления, шестой выход которого подключен к входу блока формирования кода адреса, выходы первого и второго блоков памяти соединены с входами первой и второй групп второго коммутатора, выходы которого подключены к входам дешифратора и к входам групп входов третьего и четвертого регистров, входы которых подключены к седьмому и восьмому выходам блока управления, выходы третьего и четвертого регистров соединены с соответствующими входами второго сумматора. 2. Устройство по п. 1, отличающееся тем, что блок формирования кода адреса содержит первый и второй триггеры, третий и четвертый коммутаторы и первый и второй счетчики, причем входы первого и второго триггеров, первый вход третьего коммутатора и первый вход первого и второго счетчиков являются входами блока формирования кода адреса, первый выход первого триггера соединен с вторым входом третьего коммутатора и первым входом четвертого коммутатора, второй выход первого триггера подключен к третьему входу третьего коммутатора и к второму входу четвертого коммутатора, первый выход второго триггера соединен с третьим входом четвертого коммутатора, четвертый и пятый входы которого соединены с первым выходом первого и второго счетчиков, второй выход второго триггера подключен к четвертому входу третьего коммутатора. выходы которого соединены с вторым входом первого и второго счетчиков, выходы группы первого счетчика и первый выход четвертого коммутатора являются первым выходом блока формирования кода адреса, выходы группы второго счетчика и второй выход четвертого коммутатора являются вторым выходом блока формирования кода адреса, а первые выходы первого и второго счетчиков являются третьим выходом блока формирования кода адреса. Источники информации, принятые во внимание при экспертизе 1.Гормон, Коннели. Простая система для цифровой регистрации данных импульсного эксперимента по изучению кинетики химических реакций. - «Приборы для научных исследований, 1978, № 8. 2.Авторское свидетельство СССР № 557392, кл. G Об К 15/18, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для считывания графической информации | 1986 |

|

SU1377882A1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ НА ГАЗОРАЗРЯДНОЙ ИНДИКАТОРНОЙ ПАНЕЛИ | 1992 |

|

RU2042216C1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Устройство для вывода графической информации | 1989 |

|

SU1644208A1 |

| Генератор нестационарного случайного импульсного процесса | 1981 |

|

SU1008739A1 |

| Устройство для отображения информации | 1988 |

|

SU1501135A1 |

| Устройство для управления изображением | 1981 |

|

SU1001077A1 |

| Устройство для отображения однократных электрических сигналов | 1983 |

|

SU1141445A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1988 |

|

SU1575231A1 |

6за)д

Фиг.1

Gm б/юна Ifфиг.г

К ffjiOMy 6

J

r

Нблону 7

Авторы

Даты

1982-09-15—Публикация

1980-09-22—Подача