(54) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1981 |

|

SU1022221A1 |

| Устройство связи для вычислительной системы | 1982 |

|

SU1062678A1 |

| Устройство для управления оперативной памятью | 1985 |

|

SU1291992A1 |

| Запоминающее устройство с исправлением ошибок | 1980 |

|

SU955207A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1249584A1 |

| Устройство для формирования адреса буферной памяти | 1983 |

|

SU1126954A1 |

| УСТРОЙСТВО АДАПТИВНОЙ КОММУТАЦИИ СООБЩЕНИЙ | 2009 |

|

RU2416121C2 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

| Устройство для обработки структур данных | 1990 |

|

SU1698891A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1241287A1 |

Изобретение относится к вычислительной технике и может feiTb использовано в цифровой вычислительной машине.

Известны, оперативные запоминающие устройства (ОЗУ), содержащие основной накопитель, блок . контроля, регистры данных и адресов. ЕмкостЬ: основного накопителя таких ЗУ существенно увеличина, и если какая-либо область основного накопителя рабогтает ненадежно (дает частые сбои), то nporpeiMMa из этой области перемещается в другую I.

Недостатком этих запоминающих устройств является большая избыточность основного накЬпителя-И необходимость специальной разработки математического обеспечения.

Наиболее близким к предлагаемому по технической сущности является оперативное ЗУ (ОЗУ), содержащее , основной накопитель, блок контроля, регистр данных, регистр адреса строки, регистр адреса столбца, дешифратор адреса столбца, буферные накопители, накопители адресов и признаков активности. Для обеспечения высокой скорости обращений к основной памяти, используется буферная

память. Имеются средства, позволяющие отключить неисправную часть буферной памяти или всю буфернуюпамять 2.

5 J

Недостаток запоминающего устройства заключается в том, что неисправность в основном накопителе требует остановки и ремонта системы.

Цель изобретения - повышение на10дежности ОЗУ.

Поставленная цель достигается тем, что в ОЗУ, содержащее основной накопитель, информационные входы которого подключены к одним инфор15мационньм входам коммутатора, к информационным входам буферных накопителей и к выходам регистра данных, одни из которых подключены к ) выходам основного накопителя и ко

20 входам блока контроля, другие являются информационными входами устройства, а выход блока контроля управляющим выходом устройства, одни адресные входы основного накопи25теля подключены к адресным входам буферных накопителей, к адресным входам накопителей адресов и к входам дешифратора и к выходам регистра адреса столбцов, другие адресные

30 входы основного накопителя подключены к одним входам схем сравнения, к информационным входам накопителей адресов и к выходам регистра адреса строки, входы регистров адресов столбца и строки являются адресными входами устройства, выходы накопителей адресов подключены- к другим входам схем сравнения, выходы которых подключены к одним управляющим входам буферных накопителей и к входам первого элемента ИЛИ, выходы буферных накопителей подключены к другим информационным входам коммутатора, выходы которого являются информационными выходами устройства, выход первого элемента ИЛИ подключен к входу элемента НЕ, к одному входу первого элемента И и к одному входу триггера, выход которого подключен к управляющему входу коммутатора и к одному входу второго элемента И, второй выход триггера подключен к одному входу третьего элемента И, другой вход которого подключен к соответствующему управляющему входу основного накопителя и является одним управляющим входом устройства, другой вход второго элемента И подключен к другому входу первого элемента И, к соответствующему управляющему входу основного накопителя, к первым входам элементов И группы, и -является другим управляющим входом устройства, выходы первого и второго элементов И подключены д входам второго элемента ИЛИ, выход которого подключен к другим управляющим входам буферных накопителей, вторые входы элементов И группы подключены к выходсш элементов ИЛИ первой группы, входы которьах подключены к соответствующим выходам накопителей признаков приоритета, первые и вторые управляющие входы накопителей признаков приоритета подключены соответственно к выходам дешифратора и к выходу первого элемента И, третьи входы элементов И группы подключены к JBHходу элемента НЕ, дополнительно введены накопители признаков режима, адресные входы которых подключены к выходам регистра адреса строки, информационные входы - к выходу блока контроля, а управляющие входы накопителей признаков режима подключены к выходам соответствующих схем сравнения, элементы ИЛИ второй группы, одни входы которых подключены к выходам накопителей признаков режима, другие входы - к выходам соответствующих схем сравнения, а выходы элементов ИЛК второй группы к информационным входам накопителей признаков приоритета, и четвертый, элемент И, первый вход которого подключен к выходу блока контроля.

второй вход - к другому выходу триггера, а входы группы входов четверт го элемента И подключены к выходам соответствующих накопителей признаков режимов, выход .четвертого эле-мента И являетсй другим управляющим выходом устройства.

Кроме того, накопитель признаков режима содержит триггеры, группы элементов И, элемент ИЛИ и дешифратор, входы которого являются адресными входами накопителя признаков режима, выходы дешифратора; подключены к первым входам соответствующи элементов И первой и второй групп, вторые входы элементов И первой группы объединены и являются управляющими входами накопителя признаков режима, третьи входы элементов И первой группы подключены к первым выходам соответствующих триггеров, вторые входы которых подключены ко вторым входам элементов И второй группы, вторые выходы элементов И первой группы подключены к. первым входам соответствующих триггеров, вторые входы которых объединены и являются информационными входами накопителя признаков режима, вьйсоды элементов И второй группы подключены к входам элемента ИЛИ, выход которого является выходом накопителя признаков режима.

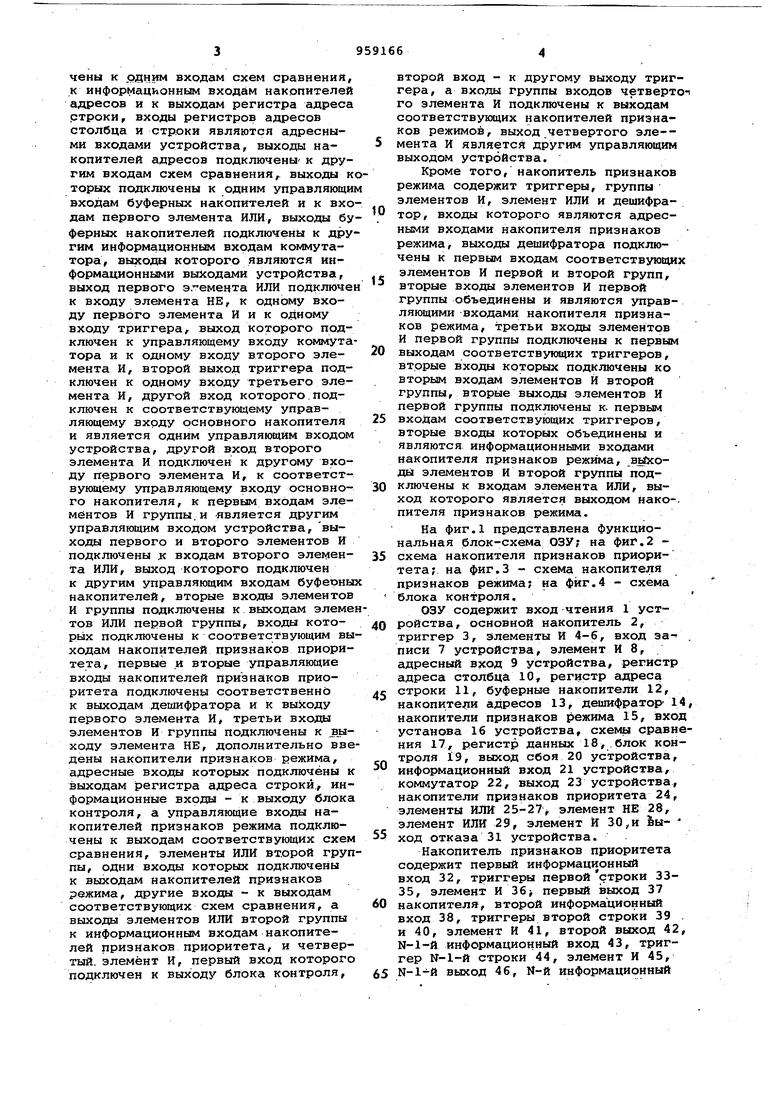

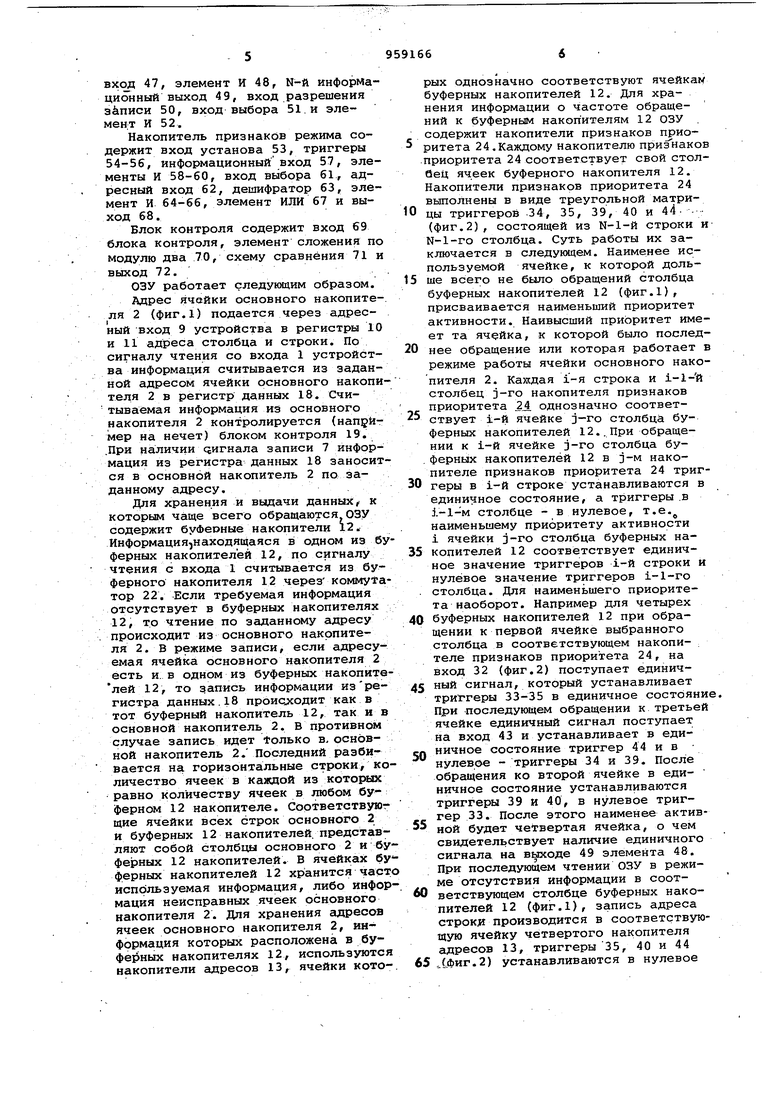

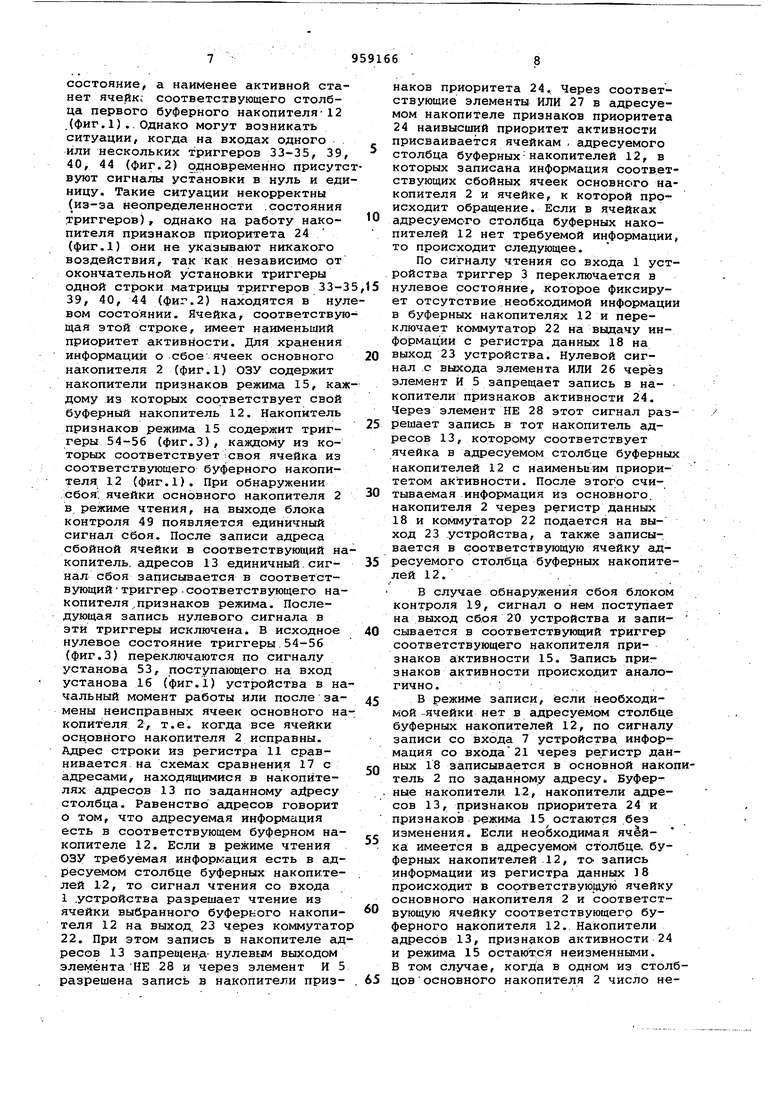

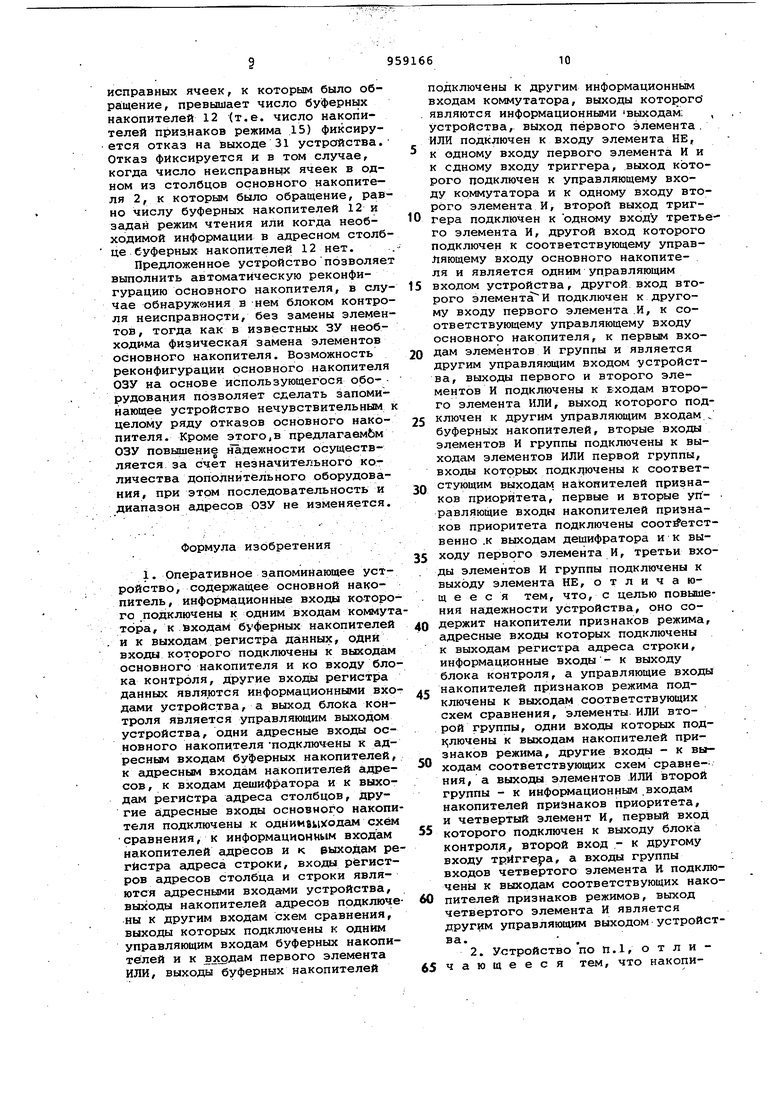

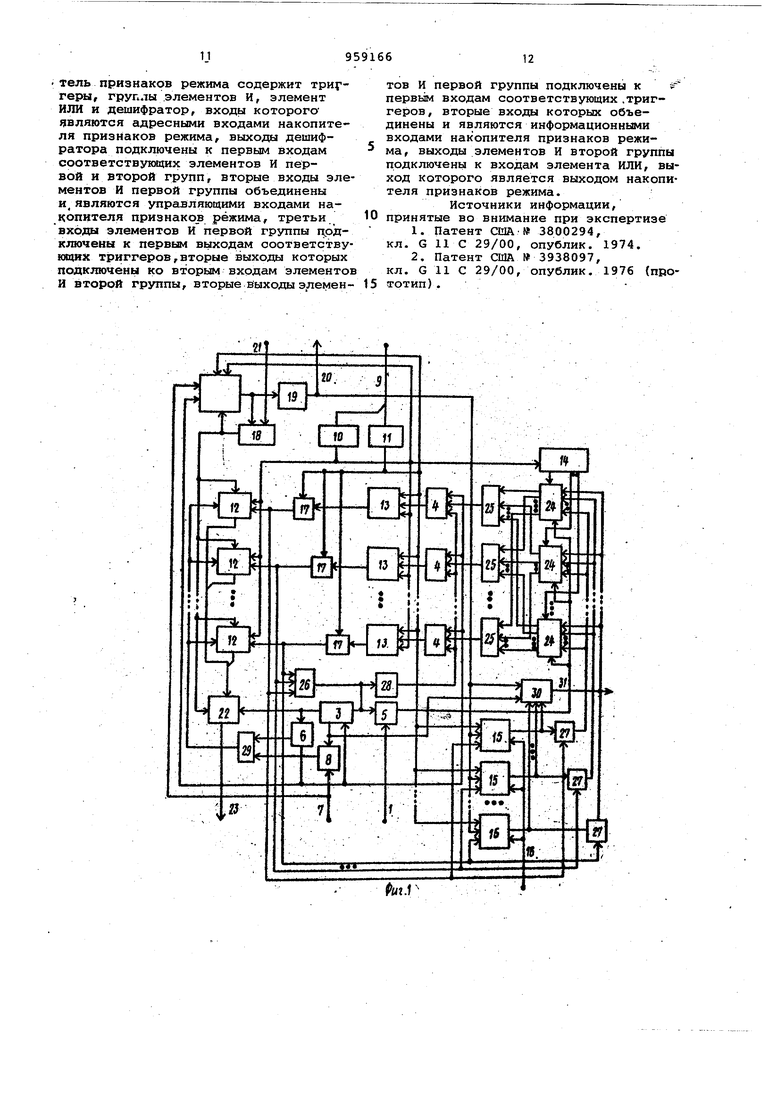

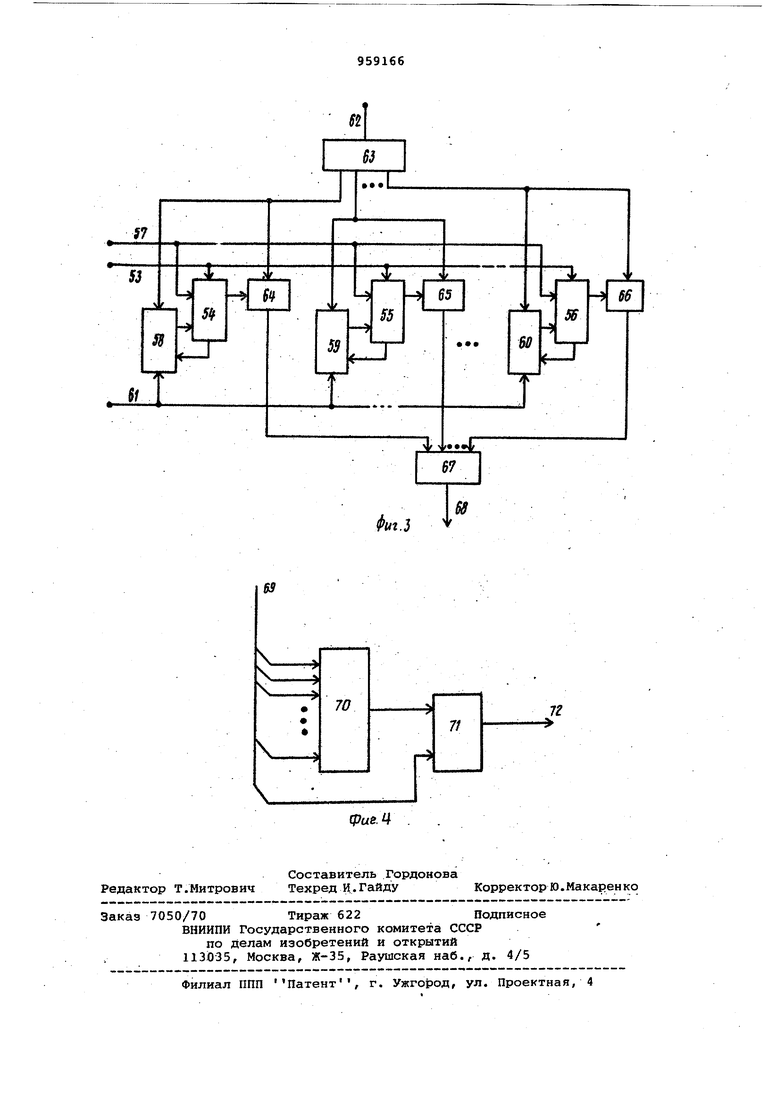

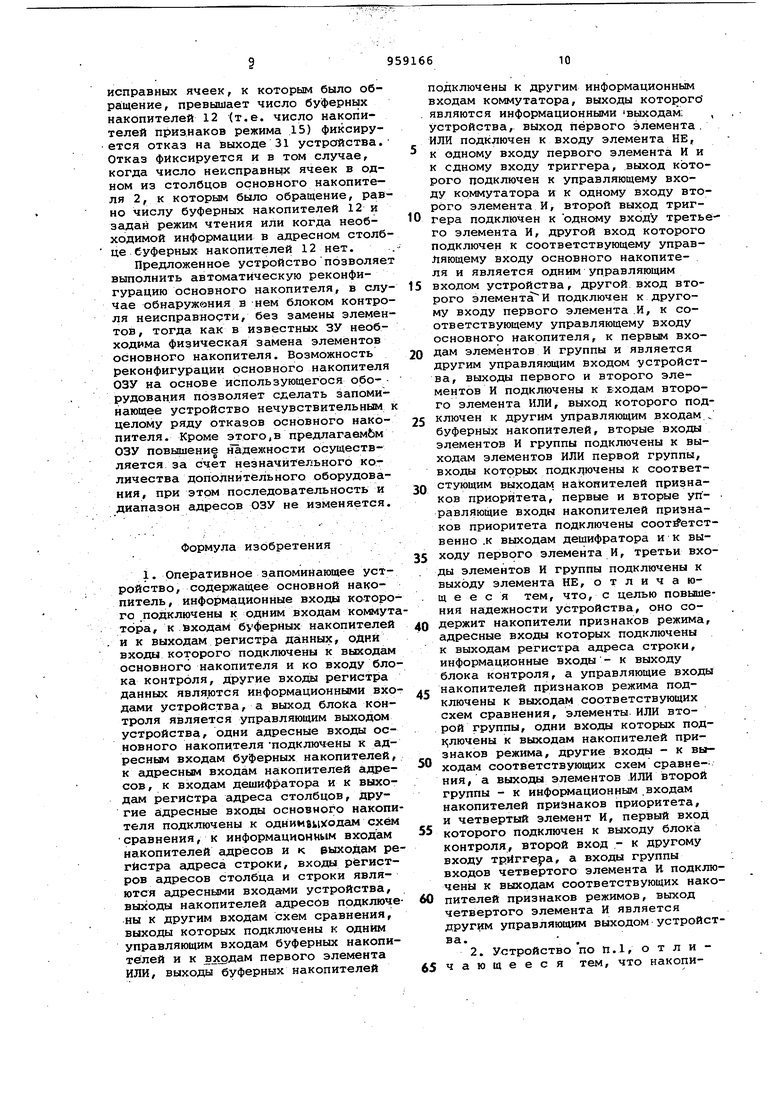

На фиг.1 представлена функциональная блок-схема ОЗУ; на фиг.2 схема накопителя признаков приоритета; на фиг.З - схема накопителя признаков режима на фиг.4 - схема блока контроля.

ОЗУ содержит вход чтения 1 устройства, основной накопитель 2, триггер 3, элементы И 4-6, вход записи 7 устройства, элемент И 8, адресный вход 9 устройства, регистр адреса столбца 10, регистр адреса строки 11, буферные накопители 12, накопителей адресов 13, дешифратор 1 накопители признаков режима 15, вхо установа 16 устройства, схемы сравнния 17, регистр данных 18, блок контроля 19, выход сбоя 20 устройства, информационный вход 21 устройства, коммутатор 22, выход 23 устройства, накопители признаков приоритета 24, элементы ИЛИ 25-27, элемент НЕ 28, элемент ИЛИ 29, элемент И 30.,и ыход отказа 31 устройства.

Накопитель признаков приоритета содержит первый информационный вход 32, триггеры первойстроки 3335, элемент И 36 первый выход 37 накопителя, второй информационный вход 38, триггеры второй строки 39 и 40, элемент И 41, второй выход 42 N-1-й информационный вход 43, триггер N-1-й строки 44, элемент И 45, N-1-й выход 46, N-й информационный

вход 47, элемент И 48, N-й информационный выход 49, вход разрешения Зс1писи 50, вход выбора 51 и элемент И 52,

Накопитель признаков режима содержит вход установа 53, триггеры 54-56, информационный вход 57, элементы И 58-60, вход вьабора 61, адресный вход 62, дешифратор 63, элемент И 64-66, элемент ИЛИ 67 и выход 68.

Блок контроля содержит вход 69 блока контроля, элемент сложения по модулю два 70, схему сравнения 71 и выход 72.

ОЗУ работает следующим образом.

Адрес ячейки основного накопителя 2 (фиг.1) подается через адресный вход 9 устройства в регистры 10 и 11 адреса столбца и строки. По сигналу чтения со входа 1 устройства информация считывается из заданной адресом ячейки основного накопителя 2 в регистр данных 18. Считываемая информация из основного накопителя 2 контролируется (например на нечет) блоком контроля 19. .При наличии сигнала записи 7 информация из регистра данных 18 заносится в основной накопитель 2 по заданному адресу.

Для хранения и выдачи данных, к которым чаще всего обращаются ОЗУ содержит буферные накопители 12. Информация находящаяся в одном из буферных накопителей 12, по сигналу чтения с входа 1 считывается из буферного накопителя 12 через коммутатор 22. Если требуемая информация отсутствует в буферных накопителях 12, то чтение по заданному адресу происходит из основного накопителя 2. В режиме записи, если адресуемая ячейка основного накопителя 2 есть и, в одном из буферных накопите лей 12, то запись информации изрегистра данных.18 происходит как в тот буферный накопитель 12, так и в основной накопитель 2. В противном случае запись идет Только в, основной накопитель 2/ Последний разбивается на горизонтальные строки, количество ячеек в каждой из котогадх равно количеству ячеек в любом буферном 12 накопителе. Соответствуют щие ячейки всех строк основного 2 и буферных 12 накопителей, представляют собой столбцы основного 2 и буферных 12 накопителей. В ячейках бУ ферных накопителей 12 хранится част используемая информация, либо инфор мация неисправных ячеек основного накопителя 2. Для хранения гщресов ячеек основного накопителя 2, информация которых расположена в буфе1 ных накопителях 12, используются накопители адресов 13, ячейки которых однозначно соответствуют ячейкам буферных накопителей 12. Для хранения информации о частоте обращений к буферным накопителям 12 ОЗУ содержит накопители признаков приоритета 24,Каждому накопителю признаков приоритета 24 соответствует свой столбец ячеек буферного накопителя 12. Накопители признаков приоритета 24 вьшолнены в виде треугольной матри0цы триггероб 34, 35, 39, 40 и 44- (фнг.2), состоящей из N-1-й строки и N-1-го столбца. Суть работы их заключается в следующем. Наименее используемой ячейке, к которой доль5ше всего не было обращений столбца буферных накопителей 12 (фиг.1), присваивается наименьший приоритет активности. Наивысший приоритет имеет та ячейка, к которой было послед0нее обращение или которая работает в режиме работы ячейки основного накопителя 2. Каждая i-я строка и 1-1-й столбец j-ro накопителя признаков приоритета 2А однозначно соответ5ствует i-й ячейке j-ro столбца буферных накопителей 12..При обращении к i-й ячейке j-ro столбца буферных накопителей 12 в j-м накопителе признаков приоритета 24 триг0геры в i-й строке устанавливаются в единичное состояние, а триггеры .в столбце - в нулевое, т.е. наименьшему приоритету активности i ячейки j-ro столбца буферных на5копителей 12 соответствует единичное значение триггеров i-й строки и нулевое значение триггеров i-1-го столбца. Для наимен1эшего приоритета наоборот. Например для четырех буферных накопителей 12 при обра0щении к первой ячейке выбранного столбца в соответствующем накопи- , теле признаков приоритета 24, на вход 32 (фиг.2) поступает единичный сигнал, который устанавливает

5 триггеры 33-35 в единичное состояние. При -последующем обращении к третьей ячейке единичный сигнал поступает на вход 43 и устанавливает в единичное состояние триггер 44 и в

0 нулевое - триггеры 34 и 39. После обращения ко второй ячейке в единичное состояние устанавливаются триггеры 39 и 40, в нулевое триггер 33. После этого наименее актив5ной будет четвертая ячейка, о чем свидетельствует наличие единичного сигнала на 49 элемента 48. При последующем чтении ОЗУ в режиме отсутствия информации в соот0ветствующем столбце буферных накопителей 12 (фиг.1), запись адреса строки производится в соответствуютцую ячейку четвертого накопителя адресов 13, триггеры 35, 40 и 44

5 ,JJbwr.2) устанавливаются в нулевое

состояние, а наименее активной станет ячейк; соответствующего столбца первого буферного накопителя-12 (фиг.1)..Однако могут возникать ситуации, когда на входах одного или нескольких триггеров 33-35, 39, 40, 44 (фиг.2) одновременно присутс вуют сигналы установки в нуль и единицу. Такие ситуации некорректны (из-за неопределенности .состояния .триггеров) , однако на работу накопителя признаков приоритета 24 (фиг.1) они не указывают никакого воздействия, так как независимо от окончательной установки триггеры одной строки матрицы триггеров 33-3 39, 40, 44 (фиг.2) находятся в нул вом состоянии. Ячейка, соответствующая этой строке, имеет наименьший приоритет активности. Для хранения информации о сбое ячеек основного накопителя 2 (фиГ.1) ОЗУ содержит накопители признаков режима 15, каждому из которых соответствует свой буферный накопитель 12. Накопитель признаков режима 15 содержит триггеры 54-56 (фиг.З), каждому из которых соответствует :своя ячейка из соответствующего буферного накопителя. 12 (фиг.1). При обнаружении ;сбоя. ячейки основного накопителя 2 в режиме чтения, на выходе блока контроля 49 появляется единичный сигнал сбоя. После записи адреса сбойной ячейки в соответствующий накопитель, адресов 13 единичный.сигнал сбоя записывается в соответствующий триггер.соответствующего накопителя признаков режима. Последующая запись нулевого сигнала в эти триггеры исключена. В исходное нулевое состояние триггеры.54-56 (фиг.З) переключаются по сигналу установа 53, поступающего на вход установа 16 (фиг.1) устройства в начальный момент работы или после замены неисправных ячеек основного накопителя 2, т.е. когда все ячейки основного накопителя 2 исправны. .Адрес строки из регистра 11 сравнивается на схемах сравнения 17 с адресами, находящимися в накопителях адресов 13 по заданному адресу столбца. Равенство адресов говорит

0том, что адресуемая информация есть в соответствующем буферном накопителе 12. Если в режиме чтения ОЗУ требуемая информация есть в адресуемом столбце буферных накопителей 12, то сигнал чтения со входа

По сигналу чтения со входа 1 устройства триггер 3 переключается в нулевое состояние, которое фиксирует отсутствие необходимой информации в буферных накопителях 12 и переключает коммутатор 22 на вьвдачу информации с регистра данных 18 на выход 23 устройства. Нулевой сигнал с выхода элемента ИЛИ 26 через элемент И 5 запрещает запись в накопители признаков активности 24. Через элемент НЕ 28 этот сигнал разрешает запись в тот накопитель адресов 13, которому соответствует ячейка в адресуемом столбце буферных накопителей 12 с наименьшим приоритетом активности. После этого считываемая информация из основного, накопителя 2 через регистр данных 18 и коммутатор 22 подается на выход 23 .устройства, а также записывается в соответствующую ячейку адресуемого столбца буферных накопителей 12..

В случае о.бнаружения сбоя блоком контроля 19, сигнал о нем поступает на выход сбоя 20 устройства и записывается в соответствующий триггер соответствующего накопителя признаков активности 15. Запись признаков активности происходит аналогично. ; . . . .

в режиме записи, если необходимой -ячейки нет в адресуемом столбце буферных накопителей 12, по сигналу записи со входа 7 устройства информация со входа21 через регистр данных 18 записывается в основной накопитель 2 по заданному адресу. Буферные накопители 12, накопители адресов 13, признаков приоритета 24 и признаков режима 15 остаются без изменения. Если необходимая ячейка имеется в адресуемом столбце, буферных накопителей 12, тО запись информации из регистра данных 18 происходит в соответствующую ячейку основного накопителя 2 и соответствующую ячейку соответствующего буферного накопителя 12. Накопители адресов 13, признаков активности 24 и режима 15 остаются неизменными. В том случае, когда в одном из столбцов основного накопителя 2 число неисправных ячеек, к которым было обращение, превышает число буферных накопителей 12 (т.е. число накопителей признаков режима 15) фиксируется отказ на выходе 31 устройства. Отказ фиксируется и в том случае, когда число нексправнврс ячеек в одном из столбцов основного накопителя 2, к которым было обращение, равно числу буферных накопителей 12 и задан режим чтения или когда необходимой информации в адресном столбце буферных накопителей 12 нет.

Предложенное устройство позволяет выполнить автоматическую реконфигурацию основного накопителя, в случае обнаружения в нем блоком контроля неисправности, без замены элементов, тогда как в известных ЗУ необходима физическая замена элементов основного накопителя. Возможность реконфигурации основного накопителя ОЗУ на основе использующегося обо- рудования позволяет сделать запоминающее устройство нечувствительным к целому ряду отказов основного накопителя. Кроме этого.в предлагаемЬм ОЗУ повышение надежности осуществляется за Счет незначительного количества дополнительного оборудования, при этрм последовательность и диапазон адресов ОЗУ не изменяется.

Формула изобретения

подключены к другим информационным входам коммутатора, выходы которого являются информационными выходам; устройства, выход первого элемента. ИЛИ подключен к входу элемента НЕ, к одному входу первого элемента И и к одному входу триггера, выход которого подключен к управляющему входу коммутатора и к одному входу второго элемента И, второй выход триггера подключен к одному входу третьего элемента И, другой вход которого подключен к соответствующему управляющему входу основного накопителя и является одним управляющим

входом устройства, другой вход второго элементами подключен к другому входу первого элемента .И, к соответствующему управляющему входу основного накопителя, к первым входам элементов И группы и является другим управляющим входом устройства, выходы первого и второго элементов И подключены к выходам второго элемента ИЛИ, выход которого подключен к другим управляющим входам . буферных накопителей, вторые входы элементов И группы подключены к выходам элементов ИЛИ первой группы, входы которых подключены к соответстующим выходам накопителей признаков приоритета, первые и вторые управляющие входы накопителей признаков приоритета подключены соответственно .к выходам дешифратора и к выходу первого элемента И, третьи входы элементов И группы подключены к выходу элемента НЕ,отличающ е е с я тем, что, с целью повышения надежности устройства, оно содержит накопители признаков режима, адресные входы которых подключены к выходам регистра адреса строки, информационные входы- к выходу блока контроля, а управляющие входы

накопителей признаков режима подключены к выходам соответствующих схем сравнения, элементы ИЛИ второй группы, одни входы которых подк;лючены к выходам накопителей признаков режима, другие входы - к выходам соответствующих схем сравнения, а выходы элементов .ИЛИ второй группы - к инфоЕ 1ационным входам накопителей признаков приоритета, и четвертый элемент И, первый вхоД

которого подключен к выходу блока контроля, второй вход - к другому входу триггера, а входы группы входов четвертого элемента И подключены к выходам соответствующих накопителей признаков режимов, выход четвертого элемента И является другим управляющим выходом устройства.

Источники информации,

принятые во внимание при экспертизе

кл. G И С 29/00, опублик. 1974.

кл. G 11 С 29/00, опублик. 1976 {прототип).

Фиг.

S8

Фиг.

Авторы

Даты

1982-09-15—Публикация

1980-12-11—Подача