Изобретение относится к вычисли- ельной технике и может быть использовано в процессорах ЭВМ

Цель изобретения - повышение ыстродействия устройства.

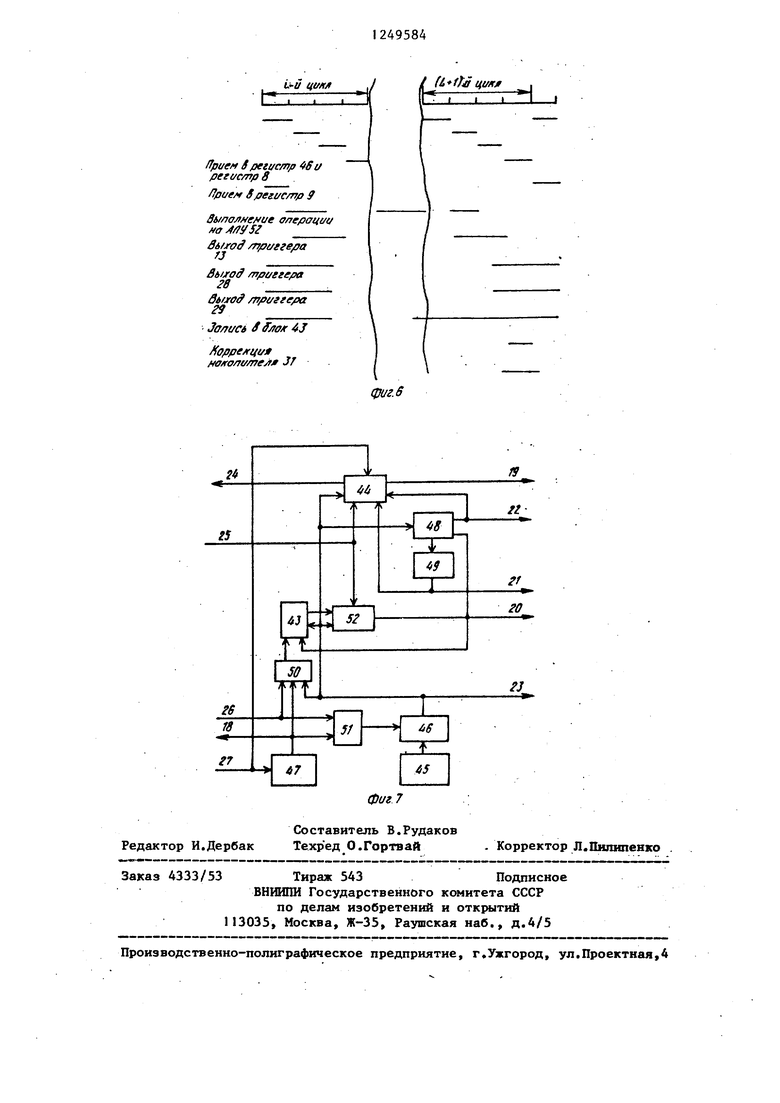

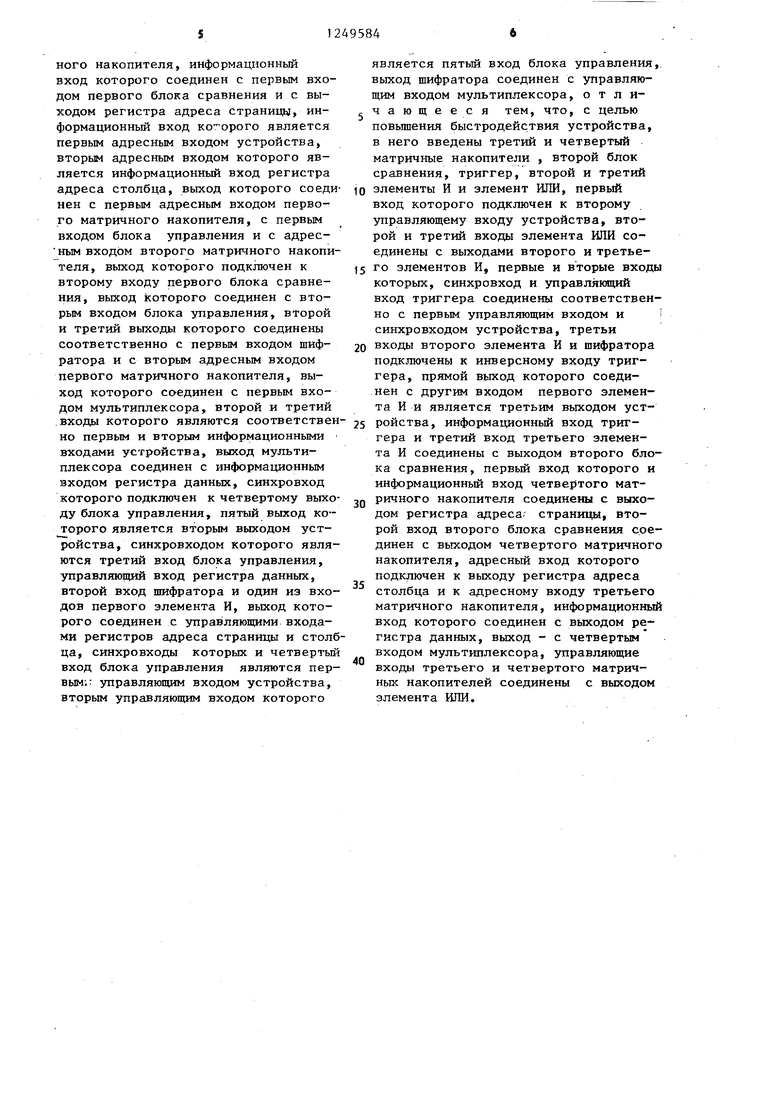

На фиг. 1 изображена структурная схема буферного запоминающего устройства; на фиГо 2 - структурная схема блока управления; на фиг.З - структурная схема второго матричного накопителя; на фиг.4-6 - времен-: ные диаграммы работы устройства; на фиг о 7 - функциональная схема процессора, в котором используется буферное запоминающее устройство.

Буферное запоминающее устройство (фиг.1) содержит первый матричный накопитель 1, являющийся накопителем данных буферной памяти, второй матричный накопитель 2, являющийся накопителем адресов буферной памяти, третий матричшлй накопитель 3, служащий для хранения данных сверхоперативной буферной памяти, четвертый матричный накопитель 4, служащий для хранения адресов сверхоперативной буферной памяти, первый 5 и второй 6 блоки сравнения, регистры адреса страницы 7, и адреса столбца 8, регистр 9 данных, мультиплексор 10, шифратор 11, блок 12 управления, триггер 13, первый 4, второй 15 и третий 6 элементы И и элемент ИЛИ 17. Также обозначены синхровход 18 устройства, первый 19 и второй -20 информационные входы устройства, первый 21 и второй 22 адресные входы устройства, первый 23 и второй 24 управляющие входы устройства, первый 25, второй 26 и третий 27 выходы устройства.

Блок 12 управления (фиг.2} содержит триггеры 28 и 29, элемент 30 задержки, накопитель 31, первый 32 и Второй 33 шифраторы, мультиплексор 34, элементы И 35 - 37 и элементы ИЛИ 38 - 40. Накопитель 2 (фиг.З) содержит матрицы 41 памяти и дешифратор 42.

I

Процессор, в котором используется буферное запоминающее устройство, содержит (фиг,7) блоки локальной 43,

оперативной 44 и управляющей 45 памяти, регистр 46 микрокоманд, узел 47 синхронизации, узел 48 формирования адреса, буферный блок 49 переадресации, элементы И 50 и 51 и арифметико-логическое устройство 52 АЛУ.

Накопитель 2 содержит и (число строк) матриц памяти. В каждой матрице 41 может храниться m (число столбцов);адресов (номеров страниц

оперативной памяти), соответствуилцих блокам данных, хранящихся в накопителе 1. Запись в накопитель и в матрицы 41 вьшолняются при появлении на выходе элемента ИЛИ 39, которая

вызьшает появление сигнала, разрешающего запись в одну из матриц 41 в зависимости от кода на информацион- ньк входах дешифраторов 42. 1 на выходе элемента ИЛИ 39 появляется,

если есть сигнал на управляющем вхог де 24 устройства, либо по синхроимпульсу, если на управляющем входе 23 устройства задана микрооперация записи в память и есть 1 на выходе элемента ИЛИ 40.

Регистр 7 адресует страницу (строку) оперативной памяти, которая разбивается наш столбцов. Регистр 8 адресует столбец блока 44,

накопителя 1, накопителя 2, одно слово накопителя 3, одну запись в накопителе 4 и ячейку памяти накопителя 31 . . Накопитель 3 организован по схеме прямого соответствия, т.е. адрес, вьщаваемый процессором, однозначно определяет только одну ячейку памяти, в которой может храниться требуемая процессору информация.

Емкость накопителя 3 не должна превьш1ать размера одной страницы виртуальной и оперативной памяти. Если его объем меньше размера страницы, то он адресуется не всеми разрядами регистра 8, а только частью. Остальная часть вместе с адресом страницы в этом случае хранится в накопителе 4. Адреса, хранящиеся в накопителе 4, указывают на месторасположение, в оперативной памяти слов, которые в данное время находятся в накопителе 3

Запись в накопители 4 и 3 производится по сигналу, появлякяцемуся на выходе элемента ИЛИ 17.

Прием информации в регистры 7 и 8 производится по импульсу ТИ 1 на синхровходе 18 устройства (в каждом цикле работы устройства на его синхровходе 18 появляется четыре тактовых импульса: ТИ 1, ТИ 2, ТИ 3 и ТИ 4), если триггер 13 установлен в 1 и на управляющем вхо- jse 23 устройства задана микроопера

ция, разрешающая прием в данные регистры.

Запись в накопители 3 и 4 производится в следующих случаях: на управляющем входе 24 устройства по- явился сигнал, указывающий на то, что требуемые данные считаны из one ративной памяти (а); .на управляющем входе 23 задана микрооперация записи в память и- информация из ячейки, в которую производится запись,находится в накопителе 3, Тое. на выходе блока 6 появилась 1 (б); задана микрооперация чтения из памяти и триггер 13 находится в О (в)..В слу- чае (б) и (в) запись производится соответственно по импульсам ТИ 4 и ТИ 2 на синхровходе 18 устройства.

Шифратор 11 формирует сигналы для управляющих входов мультиплексо- ра 10 в соответствии с таблицей.

Входы шифратора 11 Значение сигнала

I

44 52

Рассмотрим работу устройства на примере выполнений микрокоманды, в которой заданы следумщие действия: чтение одного операнда из блока 43, чтение второго операнда из памяти (иерархической системы памяти, включающей блок 44, накопители 1 и 3), вьшолнение заданной операции над этими операндами на АЛУ 52 и запись результата в блок 43,

Рассмотрим случай, когда второй операнд находится в накопителе 3 (фиг.4).

По импульсу ТИ 1 в регистр 46 заносится микрокоманда, в которой заданы перечисленные операции, :а в регистр 8 заносится младшая часть адреса, указьшающего местонахождение в памяти второго операнда. Старшая часть адреса ( адрес виртуальной страницы) начинает преобразовыватьс блоком 49 в реальный адрес страницы.

g ю 15

20

25

30

5

0

5

0

Из блока 43 по адресу, заданному в регистре 46, выбирается первьш one- ранд и подается на вход АЛУ 52. Из накопителя 3 по адресу, запомненному в регистре 8, выбирается второй операнд (в предйоложенйи, что это. действительный операнд). Он заносится по импульсу ТИ 2 в рег истр 9 и подается по выходу 25 на вход АЛУ 52.

После этого на «АЛУ 52 начинает выполняться заданная операция. Одновременно по содержимому регистра 8 из накопителя 4 и из матрицы 41 выбираются адреса страниц, которые подаются на входы блоков 6 и 6 соответственно.

Реальный адрес страницы с выхода блока 49 заносится по импульсу ТИ 2 в регистр 7 и подается на входы блоков 5 и 6. Результаты сравнения по импульсу ТИ 3 заносятся в триггеры 13 и 28.

Если требуемые данные есть в наг копителе 3, то в триггер 13 заносится 1, которая разрешает запись через элемент И 50 (по импульсу . ТИ 4) результата, полученного на выходе АЛУ 52, в блок 43.

На этом вьшолнение данной микрокоманды заканчивается. В следующем цикле в регистр 46 заносится новая микрокоманда.

Другой случай вьтолнения этой же микрокоманды (второго операнда нет

;В накопителе 3, но он есть в накопителе 1 ) иллюстрируется временными диаграммами, изображенными на фиг.5, третий случай (второго операнда нет в накопителях 1 и 3) на фиг.6. По этим диаграммам можно проследить работу устройства в этих случаях.

Формула изобретения

Буферное запоминающее устройство, содержащее первый и второй матричные накопители, первый блок сравнения, регистр адреса столбца, регистр адреса страницы, первый элемент И, шифратор, илок управления, мультиплексор и регистр данных, выход которого соединен с информационным входом первого матричного накопителя и является первым выходом устройства, управляющий вход перчо- го матричного накопителя соединен с первым выходом блока управления и управляющим входом второго матричного накопителя, информационный вход которого соединен с первым входом первого блока сравнения и с выходом регистра адреса страницы информационный вход ко- орого является первым адресным входом устройства, вторым адресным входом которого является информационный вход регистра адреса столбца, выход которого соединен с первым адресным входом первого матричного накопителя, с первым входом блока управления и с адрес- ным входом второго матричного накопителя, выход которого подключен к второму входу первого блока сравнения, выход которого соединен с вторым входом блока управления, второй и третий выходы которого соединены соответственно с первым входом шифратора и с вторым адресным входом первого матричного накопителя, выход которого соединен с первым входом мультиплексора, второй и третий входы которого являются соответственно первым и вторым информационными входами устройства, выход мультиплексора соединен с информационным входом регистра данных, синхровход которого подключен к четвертому выходу блока управления, пятый выход которого является вторым выходом устk- i.

ройства, синхровходом которого являются третий вход блока управления, управляющий вход регистра данных, второй вход шифратора и один из входов первого элемента И, выход которого соединен с управляющими входами регистров адреса страницы и столбца, синхровходы которых и четвертый вход блока управления являются первым;: управляющим входом устройства, вторым управляющим входом которого

является пятый вход блока управления,, выход шифратора соединен с управляющим входом мультиплексора, о т л ичающееся тем, что, с целью повышения быстродействия устройства, в него введены третий и четвертый матричные накопители , второй блок сравнения, триггер, второй и третий

элементы И и элемент ИЛИ, первый вход которого подключен к второму управляющему входу устройства, второй и третий входы элемента ИЛИ соединены с выходами второго и третьего элементов И, первые и вторые входы которых, синхровход и управляющий вход триггера соединены соответственно с первым управляющим входом и i синхровходом устройства, третьи

входы второго элемента И и шифратора подключены к инверсному входу триггера, прямой выход которого соединен с другим входом первого элемента И и является третьим выходом устройства, информационный вход триггера и третий вход третьего элемента И соединены с выходом второго блока сравнения, первый вход которого и информационный вход четвертого матричного накопителя соединены с выходом регистра адреса- страницы, второй вход второго блока сравнения соединен с выходом четвертого матричного накопителя, адресный вход которого подключен к выходу регистра адреса столбца и к адресному входу третьего матричного накопителя, информационный вход которого соединен с выходом ре-- гистра данных, выход - с четвертым входом мультиплексора, управляющие входы третьего и четвертого матрич- ньпс накопителей соединены с выходом элемента ИЛИ.

г)

фиг.З

l-i/ цияд

Tff

Прие t//f(popffou(/i/ fpeeuc/fffl 46 V e/afsi/c/rrp в

/Jpt/e Sflciuc/np 9

et/na/iHCH на

ue олерочии

Лриен S peai/c/np 7

SbUfoff /приггера 7J

43

t-rtf tft/fjf

HfO/fff врегис/7у 4S ирегос/пр 8

flpueft fpeevcfnp S

Выполмение операции

fipwft врееис/пр 7

Обигод /пруггера fj

3 r/fvc6 -S fftfxo/iy/nejn J и ffoxo/ru/rre/ft 4

3 угисл SSffojf J

/fOPPMtfVJt fffffro/rvтепя Jf

фиг. 5

ц«/гл

ор И.Дербак 4333/53

фиг 7

Составитешь В.Рудаков Техр ед О.Гортвай

. Корректор

Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

. Корректор Л.Пштпенко

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией ошибок | 1980 |

|

SU942160A2 |

| Буферное запоминающее устройство | 1984 |

|

SU1241287A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для формирования адреса буферной памяти | 1983 |

|

SU1126954A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Буферное запоминающее устройство | 1981 |

|

SU1022221A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1990 |

|

SU1795510A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

Изобретение относится к области вычислительной уехники и может быть использовано в процессорах ЭВМ. Цель изобретения - повышение быстродействия устройства. Устройство со,держит первый и второй матричные накопители, служащие соответственно для хранения данных и адресов буферной памяти, третий и четвертый матричные накопители,, служащие соответственно для хранения данных и адресов буферной сверхоперативной памяти, блоки сравнения, регистры адреса страницы, адреса столбца и данных, мультиплексор, шифратор, : блок управления и элементы И и ИЛИ. Второй матричный накопитель содержит п (число строк матриц ти, в каждой из которых может храниться m (число столбцов) адресов (номера страниц оперативной памяти), соответствующих блокам данных, хранящихся в первом матричном накопителе с Третий матричный накопитель организован по схеме прямого соответствия, т.е. адрес, выдаваемый процессором однозначно, определяет только одну ячейку, в которой может храниться требуемая процессору инфор мация. Адреса, хранящиеся в четвертом матричном накопителе, указьшают на место расположения в оперативной памяти слов, которые в данное время находятся в третьем матричном накопителе. 7 ил. § (Л с 00 4

| Патент ,США № 3764996, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Патент США № 3840863, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

Авторы

Даты

1986-08-07—Публикация

1984-11-30—Подача