оцийнаццатого триггера, к вторым входам пятого и шестого регистров, к информационному входу четвёртого триггера и к входу первого элемента НЕ, выход ко торого подключен к первому входу третьег элемента И, второй вход третьего элемента И подключен к информационному входу седьмого триггера, выход первого триггера подключен к первому входу четвёртого элемента И, второй вход которого подключен к первым входам пятого и шестого элементов И, к информационному входу . шестого триггера и к выходу третьего триггера, выход второго триггера подключен к вторым входам пятого, шестого элементов И и пятого триггера и к пер вому входу седьмого элемента И, второй вход которого подключен к выходу второго блока сравнения и к входу второго элемента НЕ, выход седьмого триггера подключен к третьему входу пятого регистра, к входу третьего элемента НЕ и к информационному, входу восьмого триг гера, выход которого подключен к второму входу второго элемента И, выход четвертого триггера подключен к третьему входу пятого элемента И, к первому входу восьмого элемента И и к входу чевертого элемента НЕ, выход которого подключен к третьему входу шестого элемента Пик третьему входу седьмого элемента И, четвертый вход которого подключен к информационному входу шестого триггера, выход пятого триггера подключен к второйу входу восьмого элемента И, третий вход которого подклю чен к выходу шестого триггера, первые входы девятого и десятого элементов И подключены соответственно к выходу 10 21 девятого триггера и к выходу первого элемента НЕ, вторые входы девятого и десятого элементов И подключены соот ветственно к выходу третьего триггера и к информационному входу второго триггера, третий вход девятого элемента И подключен к выходу одиннадцатого триггера, выходы второго и третьего элемен- , тов И подключены к входам третьего элемента ИЛИ, выход которого подключен к третьему входу второго мультиплексора, выход четвертого элемента И подключен к первому входу четвертого элемента ИЛИ, второй и третий входы которого подключены соответственно к выходу пятого элемента Ник выходу шестого элемента И, выход четвертого элемента ИЛИ подключен к информационному входу одиннадцатого триггера, тактовый вход которого подключен к тактовому входу первого триггера, выход седьмого элемента И подключен к первому входу пятого элемента ИЛИ, второй вход,которого подключен к выходу восьмого элемента И, выход пятого элемента ИЛИ подключен к информационному входу десятого триггера, выход девятого элемента И подключен к первому входу шестого элемента ИЛИ, второй вход которого подключен к вькоду десятого элемента И, выход шестого элемента ИЛИ подключен к третьему входу nei вого регистра, выход третьего элемента НЕ подключен к третьему входу шестого регистра, четвертые, входы пятого и шестого регистров подключены к тактовому входу восьмого триггера, выход второго элемента НЕ подключен к четвертому входу шестого элемента И

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1984 |

|

SU1249584A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для формирования адреса буферной памяти | 1983 |

|

SU1126954A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1241287A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Устройство для распаковки команд | 1981 |

|

SU972507A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

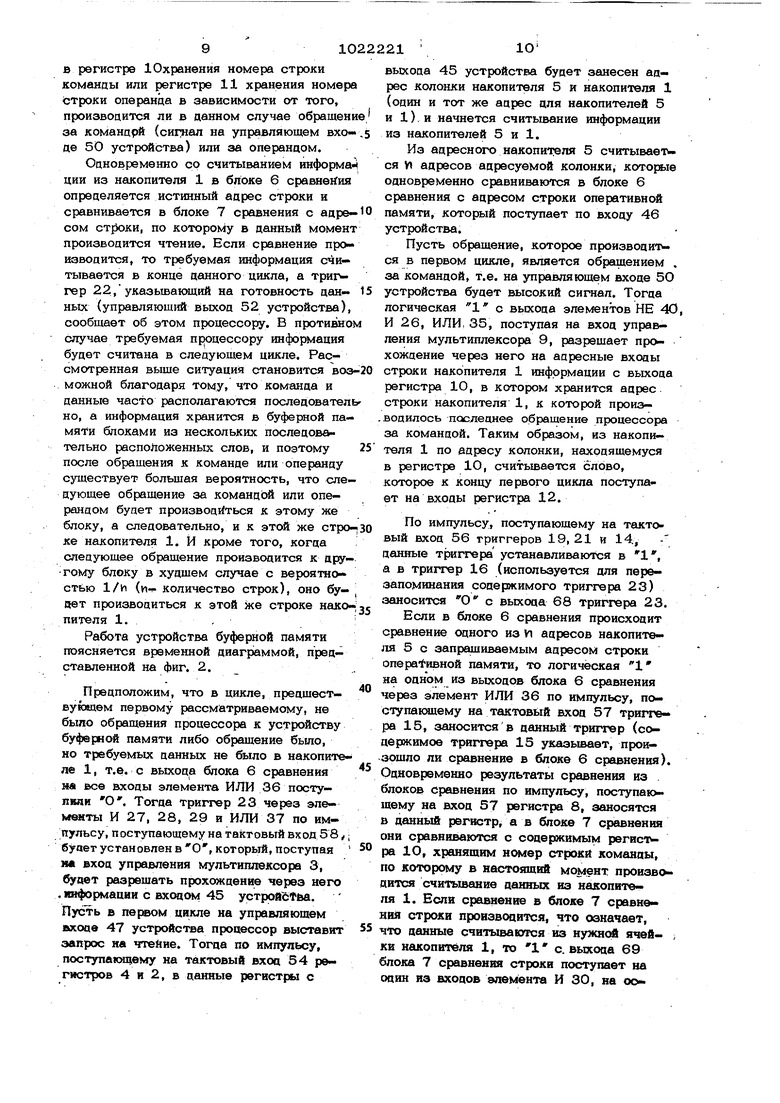

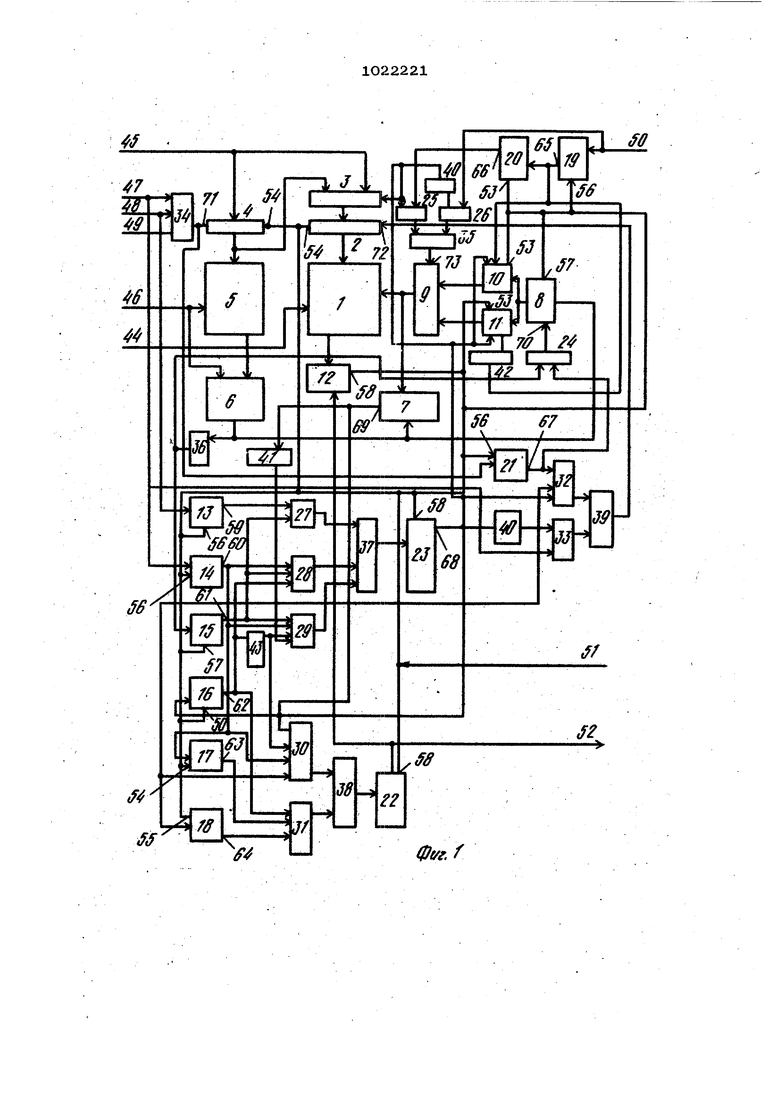

БУФЕРНСЖЗАПОМИНАКЩЕБ УСТРОЙСТВО, соцержашее информационный накопитель, первый вхоа которого поцключен к выходу первого регистра, первый вхоа первого регистра поаключев к выхоцу первого мультиплексора, первый вхоа которого 51вляется оаним аарес ным вхоаом устройства и подключен к первому вхоау второго регистра, второй вхоц которого подключен к выходу элемента ИЛИ, выход второго регистра подключен к второму входу первого муль типлексора и к первому входу адресного накопителя, второЛ вход которого .$10ляется другим адресным входом устройства и подключен к первому входу первого блока сравнения, выход адресного накопителя подключен к второму входу первого блока сравнения, выход которого подключен к первому входу третьего регистра и к BXCN дам второго элемента ИЛИ, а выход информационного нак(И1втеля подключен к первому входу четвертого регистра, второй вход которого является управлякяаю« . входом устройства, першлй шсод первого элемента ИЛИ является щрвым управляю.; щим входом устройспаа и подклкмен х ав формацвонному входу первого гратул. SUttl) 1022221 ЭС50 Q11C19/0 вторбй вход первого элемента ИЛИ является вторьп управляющим входом устройства и подключен к инфо{й«1ационному входу, второго триггера, третий вход первого элемента ИЛИ является третьим управляющим входом устройства, выход второго элемента ИЛИ подключен к информационному третьего триггера, тактовый вход которого slвл8eтcя четвертым управляю1аим входом устройства и подключен к тактсюым. вх(Х1ам первого, второго, третьего, четвертого, пятого, шестого, седьмого, восыиюго, девятого и десятого триггеров, к вторым входам первого, третьего и четвертого регистров и к третьему входу второго регистра, выход десятого триггера. является выходом устройства и подключен (Л к ттретьему входу четвертого регистра, отличающее с я тем, что, с целью псшышения быстродействия устройства, оно содержит второй блок сравнения 5 регистры, триггеры, элементы И, элементы ИЛИ, элементы НЕ и второй мульти.плексор, выход которого подключен к третьему входу информационного накопителя и к первому входу второго блока сравнения, 1юрвый и второй входы второго м мультиплексора подключены к выходам соответственно гаггого и шестого регист ров, первые входы которых подключены к выходу третьего регистра, третий вход третьего регистра подключен к выходу первого элемента И, первый и второй входы которого подключены соответственI во к выходу второго элемента ИЛИ и к шхооу оевятсяч) т|р«ггера, вход второго (Элемента Или соединен с вторым входом второго блока , первый вхоа второго алемента И подключен к третьему вэсоау 1шрвого мультиплексора, к выходу

Изобретение относится к вычислительной технике и может быть использовано в электронной вычислительной машине.

Ввиду разрыва во временах работы процессора и оперативной памяти в вычислительных машинах применяются различные технические решения, ускоряюшие получение данных из оперативной памяти. Одним из наиболее эффективных решений является включение между оперативной памятью и процессор-ом; буферной памяти.

Устройство буферной памяти содержит накопитель буферной памяти, в котором хранится наиболее часто используемая процессором информация, матрицу адресов, храняшую адреса информации, расположенную в буферной памяти, и блок сравнения адресов.

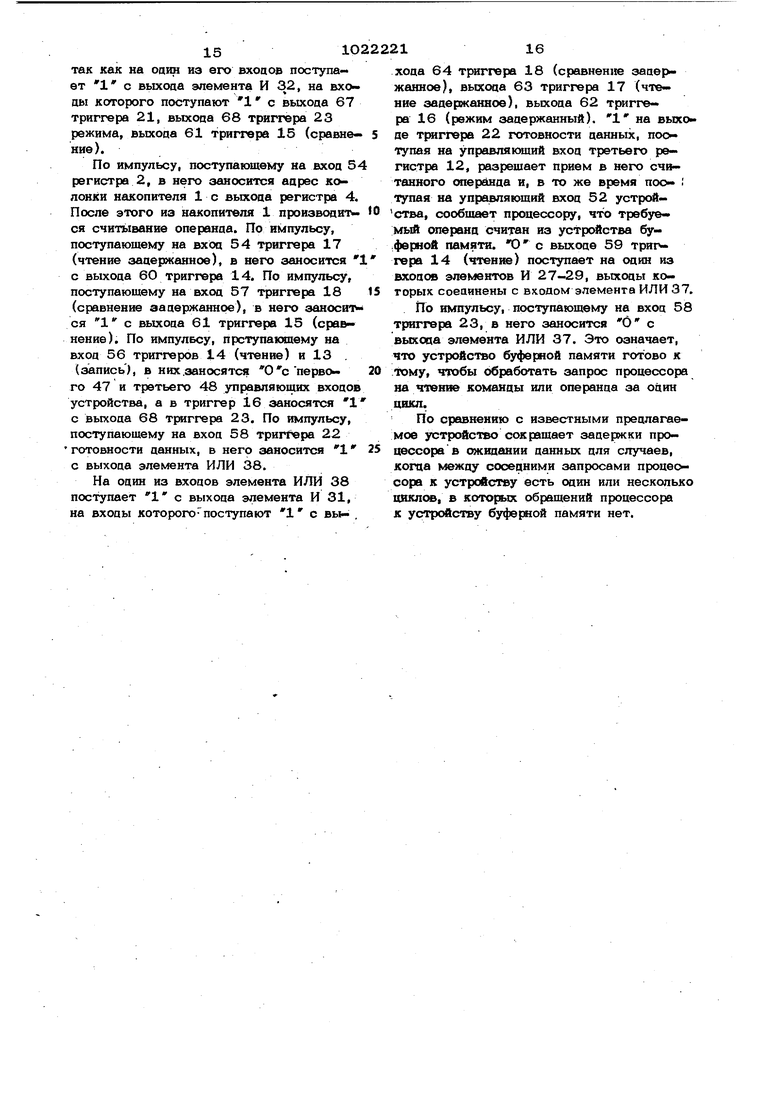

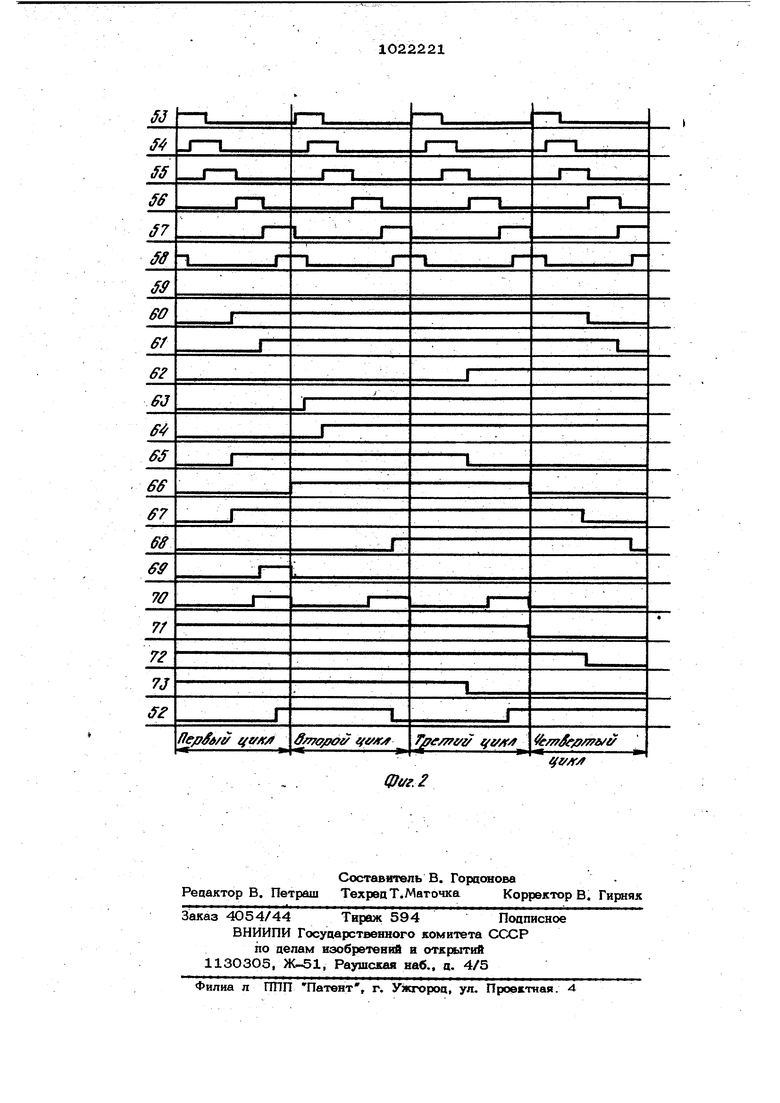

Известно устройство буферной памяти, в котором с целью уменьшения оборудования блока сравнения накопитель буферной памяти и соответственно матрица адресов разбивакугся на строки и колонки ИнформашГия из зацанной колонки оператив ной памяти может быть помешена в любу строку только соответствующей колонки буферной памяти. Причём в данном устройстве не может быть начата обработка очередного запроса до тех пор, пока не буцет заве|шена обработка предыдущего запроса tlj . Недостаток данного устройства - ере нительно Низкая пропускная спосо ость буферной памяти. Наиболее близким к.предлагаемому является устройство, которое состоит на накопителя буфе1жой памяти, первый вход которого является первым входом устройства, второй вход соединён с выходом первого регистра, вход которого соединен с выходом мультиплексора, первый вход которого является вторым входом устройства и соединен с входом второго регис ра, выход которого соединен с вторым вж дом мультиплексора и с первым входом матрицы адресов, второй вход которой я& ляется третьим входом устройства и сое- динен с первым входом блока сравнения, выход матрицы адресов соединен с вторы входом блока сравнения, выходы которого .соединены с входами регистра строки и входами первого элемента ИЛИ, выход которого соединен с входом первого гера первой группы триггеров; выходы второго и третьего тригге юв которой являются соответственно первым и вторы управляющими входами устройства, третий управляющий вход устройства соеди«нен с входом первого триггера и первым входом второго элемента 11ЛИ, второй и третий входы которого являются соогветственно первым и четвертым управляющими входами устройства , а выхсн соединен с управляющим входом второго регистра и с входом второго триггера, выходы триггеров первой группы соединены с входами триггеров второй группы, выход накопите ля буферяюй памяти рое динен с входом третьего регистра, управляющий вход JEOторого является выходом устройства и соединен с выходом триггера готовности даннь«, синхровходы всех триггеров и ре. гистров соединены с соответотвуюшимн линиями входной синхронизирующей шины устройства 2 3 . Несмотря На то, что временные пара метры схемы позволяют считать данные в ароавссор только через два цикла после выставления запроса (цепочка действий: считьшание, соответствующих адресов из матрицы адресов, сравнение их с запрашиваемым адресом, формирование адреса ячейки накопителя буферной памяти и считывание по этому адресу данных из накопителя буферной памяти), иэвест;ное устройство может выдавать данные каждый цикл прсжессора (если запросяы к устройству существуют постоянно) за счет того, что одновременно со считьтва нием данных иэ накопителя буферной па- мяти для текущего запроса (требуется один цикл процессора) производится формирование адреса накопителя буфертойпамяти для следующего запроса прооессора (считывание адресов из матрицы адресов и сравнение их с запрашиваемым адресом и по результатам сравнения формирование полного адреса ячейки нсисопителя буферной памяти), на что также требувтся один цикл процессора. Однако устройство характеризуется недостаточным бьютродействием, так как в случаях, когда запросы к памя-га не выставляютсяв каждом цикле, для считывания данных из буферной памяти требуется два цикла процессора.. Цель изобретения - повьш1ение быстродейстаия устройства. Поставленная цель достигается тем, что буфертое запоминающее устройство, содержащее информационный накопитель, вход которого подключен к: выходу первого регистра, первый вход регистра подключен к выходу первого мультиплексора, первый вход которого являет ся. одним адресным входом устройства и подключен к первому входу второго регистра, второй вход которого-подключен к юосоду первого элемента ИЛИ, выход второго регистра подключен к второму входу первого мультиплексора и к первому входу адресного накопителя, второй вход которого яв яется другим адресным вхоцам устройства и подключен к первому ходу первого блока сравнения, выход адресного накопителя подключен к входу первого блока сравнения, выход которого поаключен к первому входу третьего регистра н к входам второго злеменга ИЛИ, « вьиГод информационного накопителя „ооключен Гпервому входу четвертого регистра, второй вход которого является управляющим входом устройства, первый вход первого элемента ИЛИ является первым управляющим входом устройства и пооключен к информационному входу первого триггера, sTopcrft вход первого элемента ИЛИ является вторьтм управляющим 510 ВХОПОМ устройства и подключен к инф6р мационному входу второго триггера, третий вход первого элемента ИЛИ является третьим управляющим входом устройства, выход второго элемента ИЛИ подключен к первому входу третьего триггера, тактовый вход которого являет ся четвертым управляющим входом устройства и подключен к тактовым входам первого, второго, третьего, четвертого, пятого, щестого, седьмого, восьмого, девятого и десятого триггеров, к вторым .входам первого, третьего и четверотого регистров и к третьему входу второго регистра, выход десятого триггера является выходом устройства и подключен к третьему входу четвертого регистра, дополнительно содер жт второй блок сравнения, регистры, триггеры, элементы И, элементы ИЛИ, элементы НЕ и второй мультиплексор, выход которого подключен к третьему входу информационного накопителя и к первому входу второго блока сравнения, первый и второй входы второго мультиплексора подключены к выходам соответственно пятого и шестого регистров, первые входы которых подключены к выходу третьего регистра, третий вход третьего регистра подключен к выходу первого элемента И, первый и второй входы которого подключены COOTiветственно к выходу второго элемента ИЛ и к выходу девятого триггера, вход второ го элемента ИЛИ соединен с вторым вхо Дом второго блока сравнения, первый вход iвторого элемента И подключен к третьему входу первого мультиплексора, к выходу одиннадцатого триггера, к вторым входам пятого и щестого регистров. к информационному входу четвертого триггера и к вхйду первого элемента НЕ, выход которого подключен к первому входу третье-. го элемента И, второй вход третьего элемента И подключен к информационному входу седьмого триггера, выход первого триггера подключен к первому входу четвертого элемента И, второй вход которого подключен к первым входам пятого и шестого элементов И, к информационному входу шестого триггера и к выходу третьего триггера, выход второго триггера подключен к вторым входам пятого, шестого элементов И и пятого триггера и. к первому входу седьмого элемента И,, второй вход которого поаключен к выходу второго блока сравнения и к входу второго элемента НЕ, выход седьмого триггер подключен третьему входу пятого реги21стра, ко входу третьего элемента НЕ и к 1шформационному входу восьмого тригi pa, выход которого подключен к второму входу второго элемента И, выход четвертого триггера подключен к третьему входу пятого элемента И, к первому входу восьмого элемента И и к входу четвертого элемента НЕ, выход которого подключен к третьему входу щестого элемента И и к третьему входу седьмого элемента И, четвертый вход которого подключен к информационному входу шестого триггера, выход пятого триггера подключен к второму входу восьмого элемента И, третий вход которого подключен к выходу щестого триггера, первью входы девятого и десятого элементов И подключены соответственно к выходу девятого триггера и к выходу первого элемента НЕ, вторые входы девятого и десятого элементов И подключены соответственно к выходу третьего триггера и к инфорь. мационному ъходу второго триггера, третий вход девятого элемента И подключен к выходу одиннадцатого триггера, выходы второго и третьего элементов И подключены к входам третьего элемента ИЛИ, выход которого подключен к третьему входу второго мультиплексора, выход четвертого элемента И подключен к первому входу четвертого элемента ИЛИ, второй и третий входы которого подключены соответственно к вьЕкоду пятого элемента. И и к выходу шестого элемента И, выход четвертого элемента ИЛИ подключен к информационному входу одиннадцатого триггера, тактовый вход которого подключен к тактовому входу первого триггера, выход седьмого элемента И подключен к первому входу пятого элемента ИЛИ, второй вход которого подключен к вьрсоду восьмого элемента И, выход пятого элемента ИЛИ подключен к информационному входу десятого триггера, выход девятого элемента И подключен к первому входу шестого .элемента ИЛИ, второй вход которого подключен к выходу йесятого элемента И, выход щестого элемента ИЛИ подключен к третьему входу первого регистра, выход третьего элемента НЕ подключен к третьему входу шестого регистра, четвертые входы пятого и шестого регистров подключены к тактовому входу восьмого триггера, выход второго элемента НЕ подключен к четвертому входу шео того элемента И. На фиг. 1 изобрюкена блок-схема буферного запоминающего устройства; на фиг. 2 - временные диаграммы рабо ты устройства. Буферное запоминающее устройство состоит из информационного накопителя регистра 2,мультиплексора 3, регист ра 4, адресного накопителя 5, блока 6 сравнения, второго блока 7 сравнения, регистра 8, мультиплексора 9, регистров 1О-12, триггеров 13-23, элементов И 24-33, элементов ИЛИ ЭГ4-39, элементов НЕ 40-43, Ш1фор«1аш1онного входа 44, адресных входов 45 и 46, управляющих входов 47-51, управлякиаег выхода 52, тактовых входов 53-58 бло ков, выходов 59-67 триггеров, выходы 68 триггера 23, выхода 69 блока 7, входа 70 регистра 8, входа 71 регисч .ра 4, входа 72 регистра 2 и входа 73 мультиплексора 9. В информационном накопителе 1 може храниться (hi)(H) блоков инфор«1ации, а в адресном накопителе 5 - (vflidl) адресов соответствующих блоков, где hi- число колонок; и - число строк. Регистры 2 и 4 выполнены на двухтактных /1Л5-тригг pax, имеют по раз рядов и адресую колсшку накопителя 1 и 5 соответственно. Регистр 8 имеет VI разрядов и адресует строку накопителя 1 буферной памяти. Блок 6 сравнения состоит иа П схем сравнения по EOg разрядов, где VI-число строк оперативней памяти, и имеет и выходов. Блок 7 сравнения стро ки представляет собс одну схему сравне ния на У разрядов. Работа устройства иницируется при поступлении сигнала на входы 47, 48 .или49. Сигнал на входе 47 или 48 устройства означает, что производится обращение процессора к памяти для считьшания или записи информации. Сигнал на управляющем входе 49 уст|хЛства устанавливается при записи каналом информации в память. На входе 5О устройства устанавливается в случае, если процессор обращается к за коман дой, а в случае обращения aia операндом устанавливается О. Сигнал на уп{ авляк тем входе 47 зап(ж«ннается сначала в тртггере 14, а затем в т|даггере 17, Сигнал на управляющем входе 48 запоминается в триггере 13, а аа управля щем входе 50 устройства - сначала в триггере 19, а затем в триггере 2О. На личйе сигнала хотя бы на одном из упра лякяцих входов 47-49 устройства фиксируется в триггере 21. Всякий раз, когда на одном из входных; управляющих входов 47-49 устройства появляется 1, в регистр 4 заносится адрес колонки накопителя 5 адресов. Из адресуемой колонки накопителя 5 адресов считывается ц адресов, которые соответствуют информации, размещенной в у строках соответствукяпей колонки накопителя 1. Затем в блоке 6 сравнения данные И адресов сравнивают с запращиваемым адресом, поступающим по входу 46 устройства. Результат сравнения заносится в регистр 8 и выбирает одну из И строк накопителя 1. В следующем цикле из накопителя 1 считывается запреиииваемый блок информации. В регистре 10 строки команды н регистре 11 строки операнда хранятся адреса строки накопителя 1, к торой производилось последнее обращение за командой и операндом. В зависимости от состояния триггера 23 СО или ) ннформа ция может считьшаться из накопителя 1 либо в том же цикле, в котором процессор выставляет запрос на чтение на управляющем входе 42 устройства, либо в следующем цикле. Вд1шичное значение триггера 23 режима означает, что в данном цикле из накопителя 1 считывается (либо записывается) информация в соответствии с запросом процессора на чтение или запись, выставпенном на 47 или 48 управляющих входах устройства в предыдущем цикле. Причем в начале данного цикла адрес колсмки нак(Я1ителя 1 заносится из регистра 4 в регистр 2, а адрес строки (результат сравне|н11я) накопителя 1 из регистра 8 строки заносится в регистр 1О строки команды или регистр 11 строки операнда в зависимости от того, производится ли обрапюние за комешдой или операндом. Результат сравнения за11ос1ггся в регистр 8 из блока 6 сравнения в конце предыдущего цикла. Нулевое аначенкю триггера 23 режима означает, что в предыдущем цикле не было обращения к устройству буферной памяти и что, если в аанном цикле процессор выставит запрос на чтение на управляющем вводе 47 устройства, информация будет сйагвиА из накопителя 1 в этом же цикле, П|Я1чем aapiec коловки нак(Н1Итвля 1 заносится в начале никла с входа 45 устройства в регистры 2 и 4. В качестве адреса строки иак я1ителя 1 будит использован аорес, по которому производилось предыцушее обрашение. Этот адрес находится в регистре 1 Охранения номера строки команды или регистре 11 хранения номер строки операнда в зависимости от того, производится ли в данном случае обращен за командрй (сигяал на управляющем входе 50 устройства) или за операндом. Одновременно со считыванием информа ции из накопителя 1 в блоке 6 сравнения определяется истинный адрес строки и сравнивается в блоке 7 сравнения с адре- сом строки, по которому в данный момен производится чтение. Если сравнение производится, то требуемая информация считывается в конце данного цикла, а триггер 22,указывающий на готовность данных (управляющий Выход 52 устройства), сообщает об этом процессору. В противно случае требуемая процессору информация будет считана в следующем цикле. Рассмотренная выще ситуация становится воз можной благодаря тому, что команда и данные часто располагаются последовател но, а информация хранится в буферной памяти блоками из нескольких последовательно расположенных слов, и поэтому после обращения к команде или операнду существует большая вероятность, что сле дующее обращение за командЫ1 или операндом будет производиться к этому же блоку, а следовательно, и к этой же стро ке накопителя 1. И кроме того, когда следующее обращение производится к дру- гому блоку в худшем случае с вероятностью 1/и (и- количество строк), оно будет производиться к этой же строке нако пителя 1.. Работа устройства буферной памяти поясняется временной диаграммой, представленной на фиг. 2. Предположим, что в цикле, предшествукшем первому рассматриваемому, не было обращения процессора к устройству буферной памяти либо обращение бьшо, но требуемых данных не было в накопителе 1, т.е. с выхода блока 6 сравнения на все входы элемента ИЛИ 36 поступили О. Тогда триггер 23 через элеметсты И 27, 28, 29 и ИЛИ 37 по имиульсу, поступающему на тактовый вход 5 8 будет усгановлен в О, который, поступая в вход управления мультиплексора 3, будет разрешать прохождение через него , информации с входом 45 устррЯсТьа. Пусть в переом цикле на управляющем входе 47 устройства процессор выставит запрос на чтейие. Тогда по импульсу, поступакяцему на тактовый вход 54 регистров 4 и 2, в данные регистры с выхода 45 устройства будет занесен адрес колонки накопителя 5 и накопителя 1 (один и тот же адрес для накопителей 5 и 1). и начнется считывание информации из накопителей 5 и 1. Из адресного накопителя 5 считывает ся У адресов адресуемой колонки, которые одновременно сравниваются в блоке 6 сравнения с адресом строки оперативной памяти, который поступает по входу 46 устройства. Пусть обращение, которое производится в первом цикле, является обращением . за командой, т.е. на управляющем входе 5О устройства будет высокий сигнал. Тогда логическая 1 с выхода элементов НЕ 40, И 26, ИЛИ, 35, поступая на вход управления мультиплексора 9, разрешает прохождение через него на адресные входы строки накопителя 1 информации с выхода регистра 10, в котором хранится адрес строки накопителя 1, к которой производилось последнее обращение процессора за командой. Таким образом, из накопителя 1 по адресу колонки, находящемуся в регистре 10, считывается слово, которое к концу первого цикла поступает на входы регистра 12. По импульсу, поступающему на тактовый вход 56 триггеров 19, 21 и 14, данные триггера устанавливаются в 1, а в триггер 16 (используется для перезапоминания содержимого триггера 23) заносится О с выхода 68 триггера 23. Если в блоке 6 сравнения происходит сравнение одного из У адресов накопителя 5 с запрашиваемым адресом строки опера- ивной памяти, то логическая 1 на одном из выходов блока 6 сравнения через элемент ИЛИ 36 по импульсу, по- ступакяцему на тактовый вход 57 триггера 15, заноситсяв данный триггер (содержимое триггера 15 указьюает, прои- -зошло ли сравнение в блоке 6 сравнения). Одновременно результаты сравнения из блоков сравнения по импульсу, nocTynaioшему на вход 57 регистра 8, заносятся в данный репютр, а в блока 7 сравнения они сравниваются с содержимым рагис- |эа 10, храняшнм строки команды, по которому в настоящий момент производится считывание данных из накопителя 1. Если сравнение в блоке 7 сравнения строки произвоаится, что означает, НТО данные считываются из нужной ячей- : ки накопителя 1, то с. выхода 69 блока 7 сравнения строки поступает на один из входов элек4ента И 30, на оо тальнЫе входы которого поступают логические 1 с выхоца 61 триггера 15, вы хода 6О триггера 14, выхода элемента НЕ 43, Hia вход которого поступает О с выхода 62 триггера 16. с выхода элемента И 30 через элемент ИЛИ 38 заносится в триггер 22 готовности данных по импульсу, поступающему на тактовый, вход 58 данного триггера. По этому же импульсу в Tpaivгер 23 заносится О с выхода элемента ИЛИ 37, на входы которого поступа ют О с выходсю элементов И 27-29. 1 на Bbixcxie триггера 2 2 готовности данньЁк, с одной сторсжы, разрешает занесение информации, считанной из накопи теля 1 в регистр 12, с Другой стороны, по управляющему выходу 52 устройства сообщает процессору о том, что Ш1фо ация считана из буферной памяти. Таким образом, за один цикл информа ция из буферной памяти считывается в процессор. Предположим, что во втором цикле процессор опять выставляет запрос на чтение оманды. На управляющих входах 47 и 50 устройства будут присутствовать высокие,сигналы. Аналогичн как и в первом цикле, произойдет занесение в регистры 2 и 4, начнется считы вание из накопителей 5 и 1. Пусть в блоке 6 сравнения один из адресов адресуемой колонки накопителя 5 сравнивается с 4аресом, поступающим по входу 46 устройства. Аналогично, как и в первом цикле, триггеры 21, 19, 14 и 15 установятся в а триггер 16, указывающий на режим задержанный, установится в О. Но предположим, что требуемая процессору информация находится не в той строке накопителя 1, из которой в текущий момент производится считывай, а в другой. Адрес строки накопителя 1, из которой должно было происходить считывание информации с выхода блока 6 сравнения, заносится в регистр 8 (по импульсу, поступающему на вход 57 данного регистра). А на вы ходе 69 блока 7 сравнения строки выдается О, который указывает на то, что в данный момент из накопителя 1 считы вается ненужная инфо1Иу|ация (из той же колонки, но из другой строки). О с выхода блока 7 сравнения строки поступ ет на один из входов элекмеЬтов И 30 и НЕ 41. О с выхода элемента И 30 поступа ет на первый вход элементаИЛИ 38, на второй вход которого поступает О с выхода элемента И 31, так как на один из входов этого элемента поступает О с выхода 62 триггера Гб режима, задень жанный таким образом по импульсу, поступающему на тактовый вход триггера 22 готовности данных. Данный триггер устанавливается в О, который по управляющему выходу 52 устройства сигнализирует процессору о том, что информация не была считана из буферной памяти. 1 с выхода элемента НЕ 41 поступает на один из входов элемента И 29. На остальные входы этого элемента поступают 1 с выхода 61 триггера 15, выхода 6О триг гера 14 и выхода элемента НЕ 43, на вход которого поступает О с в ыхода 62 триггера 16, I с выхода элемента ,И 29 через элемент ИЛИ 37 по импульсу, поступающему на тактовый вход 58 триггера 23, заносится в этот триггер, что в данном случае указывает на то, что в следующем цикле из накопителя 1 будет считана информация, которая, не &1ла считана в данном цикле (былд считана, но не из заданной строки). Предположим, что. в третьем цикле процессор выставляет запрос на чтение сжеранда. Логическая - на управляющем входе 47 устрЫ1ства, О - на управляющем входе 5О устройства. И, кроме того, в устройстве буферной памяти должна быть закончена обработка запроса на чтение команды, которая не была закончена в предыдущем цикле. По импульсу, поступающему с входа 51 синхронизации устройства на тактовый вход 53 триггера 2О, в данный триггер заносится С выхода 65 триггера 19. По этому же импульсу инфо гаш1я с выхода регистра 8 заносится в регистр 1О (высокие сигналы на обоих управляющих выходах регистра 1О с выхода 65 триггера 19 и выхода 68 триггера 23 режима). с выхода 56 триггера 20 поступает на один из входов элемента И 25, на второй вход KOTOpoito постзшйет с.выхода 68 триггера 23 режима, которая, также поступая на управляющий вход мультиплексора 3, разрющает прохождение через него информации с выхода второго регистра 4. 1 с выхода элемента И 25 через одни из вхсщов элемента ИЛИ 35 поступает на управляющий ; ахоа 73 мультиплексора 9 строки и тем самым разрещает прохождение информации с выхода регистра 1О строки команды на адресные входы строки накопителя 1 буферн памяти. На вход 71 упраЕшения второго регистра 4 поступает 1 с вы13 10хоца элемента 34ИЛИ С на первом управляющем входе 47 устройства, который соединен с одним иэ входов элемент та ИЛИ 34. На управляющий вход 72 регистра 2 поступает 1 с выхода элемен- та ИЛИ 39, так как на один из ее входов поступает с выхода элемента И 32, на вход которого поступают 1 с выхода 67 триггера 21, выхода 61 триггера 15 и вькода 68 триггера 23 режима. По импульсу, поступающему на тактовый вход 54 регистра 2 и регистра 4, информация с выхода регистра 4 заноситс в регистр 2, а в регистр 4 заносится ин формация, поступающая по входу 45 уст ройства (адрес колонки накопителя 5 адресов для запроса за операндом). После этого из адресуемой колонки накопителя 5 адресов в блок 6 сравнения считывается п адресов, для того чтобы установить, находится ли запрашиваемый операн в накопителе 1. Данные адреса сравниваются с адресом поступающим по входу 46 устройствах В это же время из нужной строки накопи теля 1 считывается команда, запрос на которую был получен устройством буфер ной памяти в начале второго цикла. По импульсу, поступающему с входа 51 синхронизации устройства на тактовый вход 54 триггера 17, в него заносит- ся 1 с выхода 60 триггера 13 (запрос на чтение, который был выставлен во втором цикле). По импульсу, поступающему на тактовый вход триггера 18, в данный триггер заносится 1 с выхода 61 триггера 15 (результат сравнения в блоке 6 сравнения, полученный во втором цикле). По импульсу, поступающему на тактовый вход 56 триггера 19, в него заносится О с выхода 5О уст ройства (запрос за операндом). По этому же импульсу в триггер 21 заносится 1 с выхода элемента ИЛИ 34 в триггер 16 (режим задержанный) заносится с выхода 68 триггера 23 режима, в триггер 14 (чтение) заносится 1 с входа 47 устройства. По импульсу, поступающему на вход 58 триггера 22 готовности данных в негр заносится 1 с выхода элемента ИЛИ 3 на один из входов которого поступает И 31, на входы котос выхода элемента рого поступают 1 с выхода 64 триггера 18, выхода 63 триггера 17, выхода 6 триггера 16 (режим задержанный). 1 на выходе триггера 22 готовности данны разрешает заноситься инфор 1ации, считан 1 ной из накопителя 1, в регистр 12 и по управляющему выходу 52 устройства сообщает процессору о том, что требуемая команда считана из устройства буферной памяти; Предположим, что в блоке 6 сравнения один из адресов накопителя 5 сравнивается с адресом, поступающим по входу 46 устройства, тогда 1 с выхода элемента ИЛИ 36 заносится в триггер 15 (сравнение) по импульсу, поступающему на вход 57 данного триггера. По этому же импульсу результаты сравнения с выходов блока 6 соавнения заносятся в регистр 8 строки. с выхода 61 триггера 15 поступает на один из входов элемента И 28, на остальные входы которого поступают 1 с выхода 60 триггера 14, выхода 62 триггера 16 (режим задержанный). 1 с выхода элемента И 28 через элемент ИЛИ 37 заноси1 ся в триггер 23 режима по импульсу, поступающему на вход 58 этого триггера. В данном случае 1 на выходе 68 тригпгра 23 режима указывает на то, что в следующем цикле из накопителя 1 должен быть считан операнд, запрос на который был получен устройством в начале данного цикла. Пусть в четвертом цикле запрос к устройству буферной памяти не был выотавлен, т.е. на первом .47, втором 48 и третьем 49 управляющих входах уст ройства стоят О. По импульсу, посаупающему на вход 53 триггера 2О, в него заносится О с выхода 65 триг, гера 19 (признак команды), а в регистр 11 заносился информация с выхода регистра 8. На оба управляющих входа регист ра 11 поступают I с выхода 68 триг пэра 23 режима и выхода элемента НЕ 42, на вход которого поступает О с выхода 65 триггера 19. На один из входов эJтeмента И 25 поступает О с выхода 66 триггера 20 (признак команды задерканный), а на один из входов элемента И 26 поступает О с выхода элемента НЕ 4О, на вход которого посту.пает 1 с выхода 68 триггера 23. Выходы элементов И 25 и 26 соединены с входами элемента ИЛИ 35, выход которого соединен с управляющим входом 73 мультиплексора 9. О на управляющем входе мультиплексора 9, строки разрещает прохождение на адресные входы строки на-. копителя 1 информации с выхода регист. ра. 2. На управляющий вход регистра 2 с выхода элемента ИЛИ .поступает 1О так как на ощш иэ его вхоцов поступает с выхоаа элемента И 32, на вхо ды которого поступают 1 с выхода 67 триггера 21, выхода 68 триггера 23 режима, выхода 61 триггера 15 (сравне ние). По импульсу, поступающему на вход 54 регистра 2, в него заносится адрес колонки накопителя 1 с выхода регистра 4. После этого из накопителя 1 производи ся счить1вание операнда. По импульсу, поступающему на вход 54 триггера 17 (чтение задержанное), в него заносится с выхода 60 триггера 14. По импульсу, поступающему на вход 57 триггера 18 (сравнению задержанное), в него заносит ся 1 с выхода 61 триггера 15 (сравнение). По импулБсу, прступаюшему на вход 56 триггеров 14 (чтение) и 13 . (запись ), в них .заносятся Оспервого 47 и третьего 48 управляющих входов устройства, а в триггер 16 заносятся с выхода 68 триггера 23. По импульсу, поступающему на вход 58 триггера 22 готовности данных, в него заносится 1 с выхода элемента ИЛИ 38. На один из входов элемента ИЛИ 38 поступает с выхода элемента И 31, на входы которогопоступают 1 с вы- , 116 хода 64 триггера 18 (сравнение задержанное), выхода 63 триггера 17 (чтение задержанное), выхода 62 триггера 16 (режим задержанный). на выходе триггера 22 готовности данных, поступая на управляющий вход третьего регистра 12, разрешает прием в него считанного (шеранда и, в то же время поо i тупая на управляющий вход 52 устрЫ} ства, сообщает процессору, что требуемый операнд считвн из устрЫ}ства 6у.ферной памята. О с выходе 59 три1 гера 14 (чтение) поступает на один из входов элементов И 27-29, выходы которых соединены с входом элемента ИЛИ 37. По импульсу, поступающему на вход 58 триггера 23, в него заносится О с выхода элемента ИЛИ 37. Это означает, что устройство буферной памяти готово к тому, чтобы обработать запрос процессора на чтение команды или операнда за один цшш. По сравнению с известными предлагаемое устройство сокращает задержки процессора в ожидании данных для случаев, когда между соседними запросами процессора к устройству есть один или несколько цикле, в которых обращений процессора к устройству буферной памяти нет. фуг. 0

QJt/l.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США Mi 3588839, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-06-07—Публикация

1981-12-14—Подача