11

Нзобретение относится к вычислительной технике и может быть использовано в аппаратуре тестового коЕчтро ля и диагностики цифровых блоковj в частности узлов ЭЦВМ, построенных на осгюве цифровых интегральных схем

Цель изобретения - расширение функциональных возможностей за счет обеспечения возможности корректировки тестовых программ в процессе контроля цифрового блока.

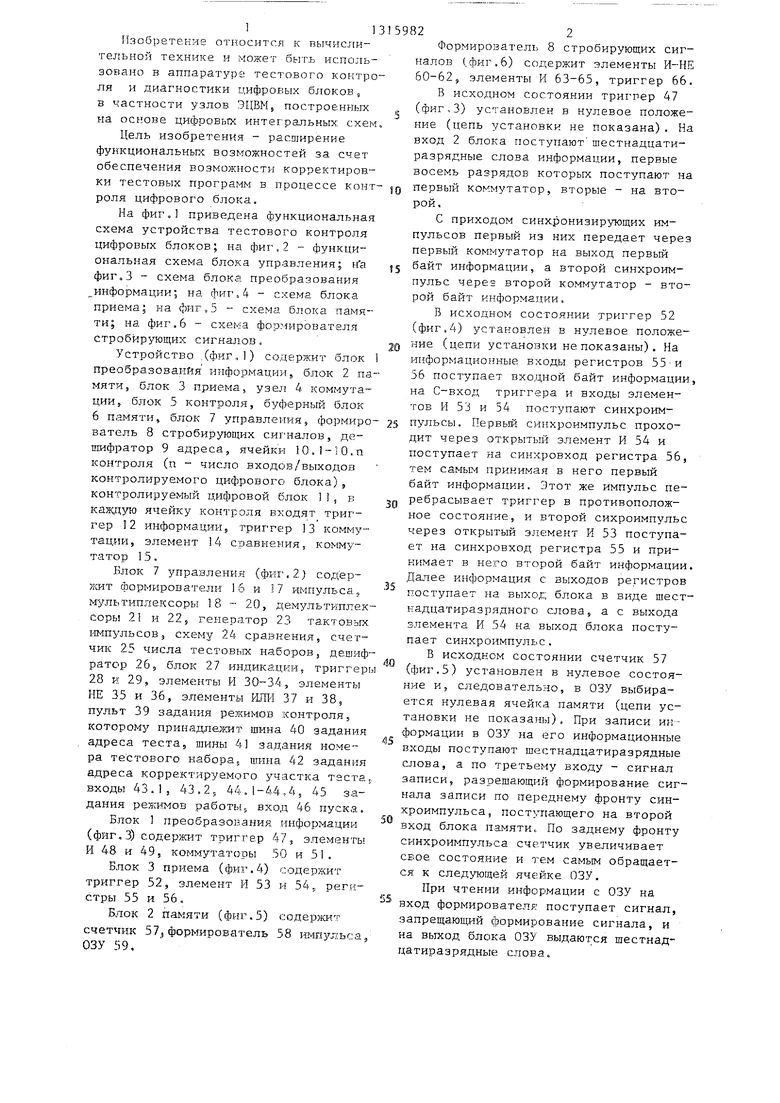

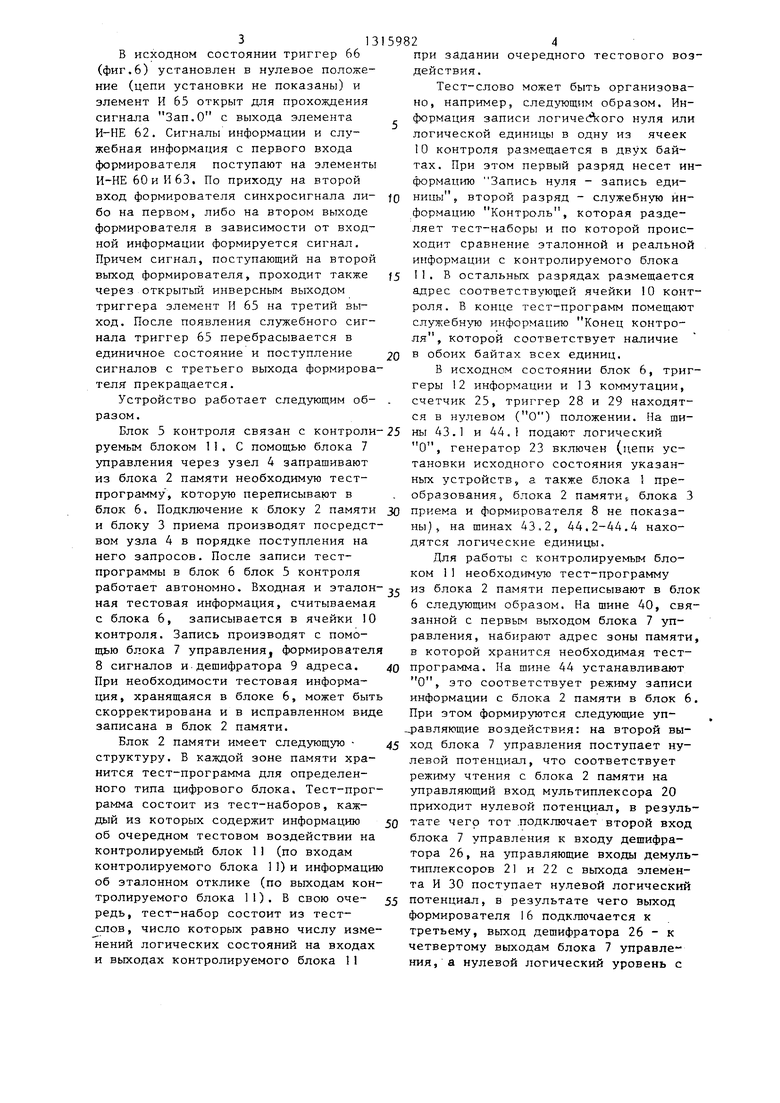

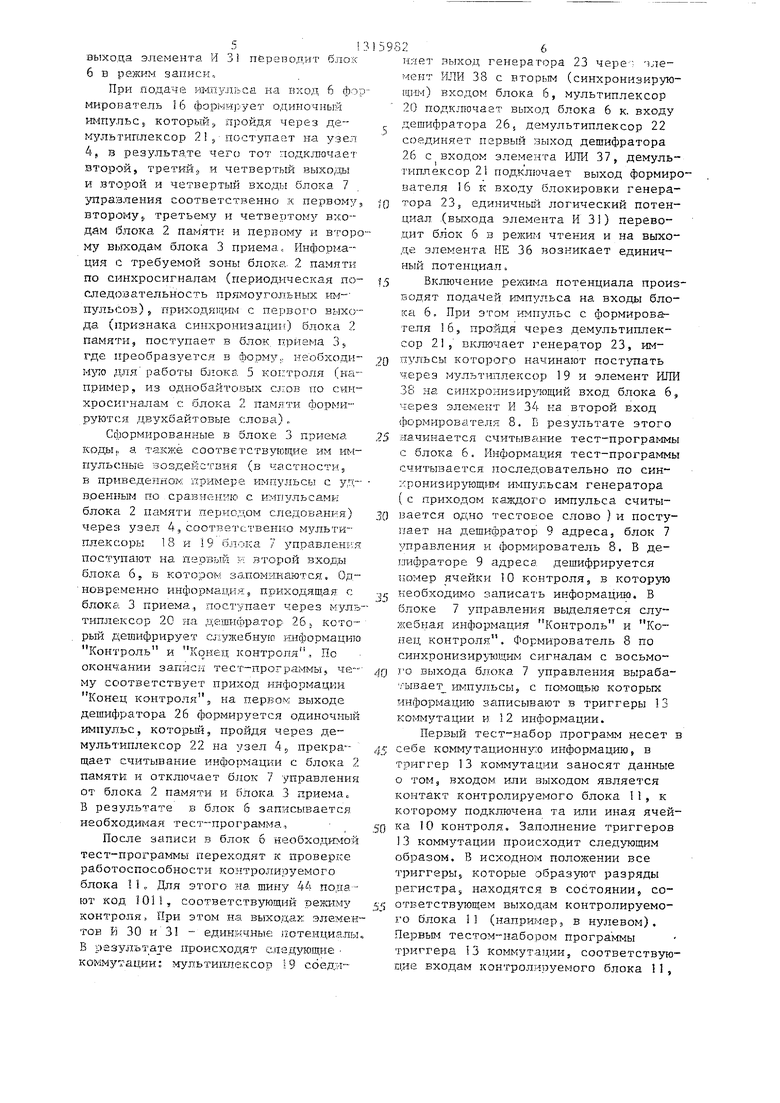

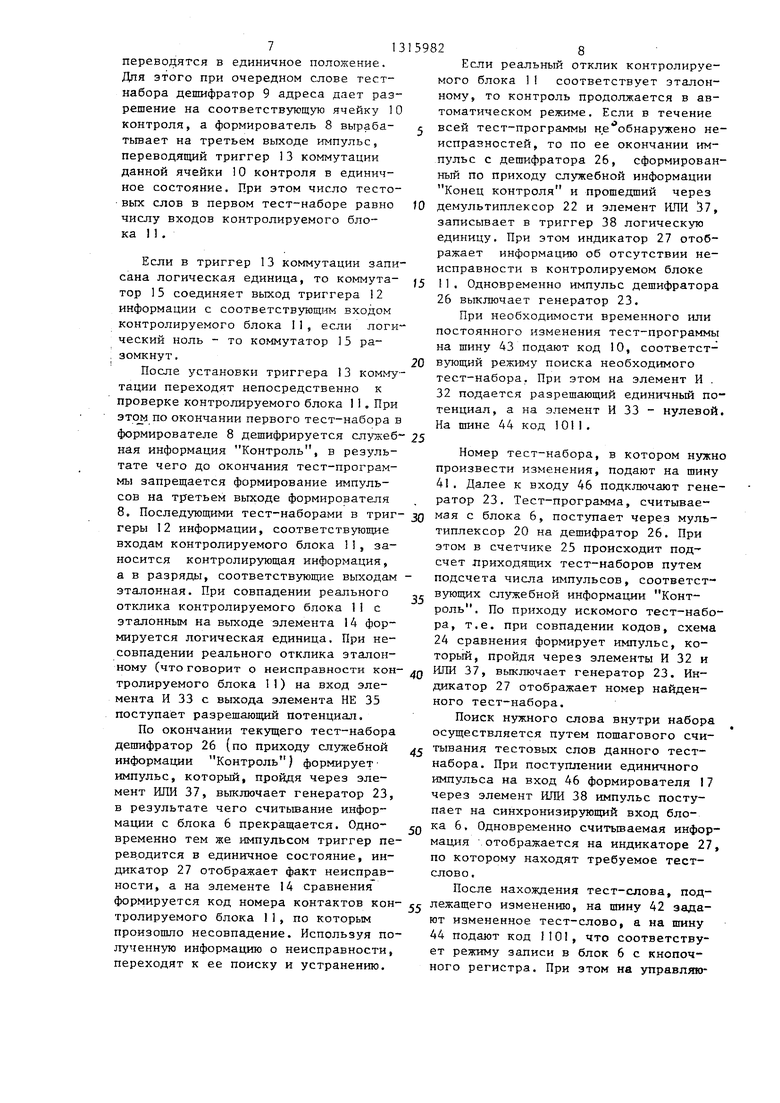

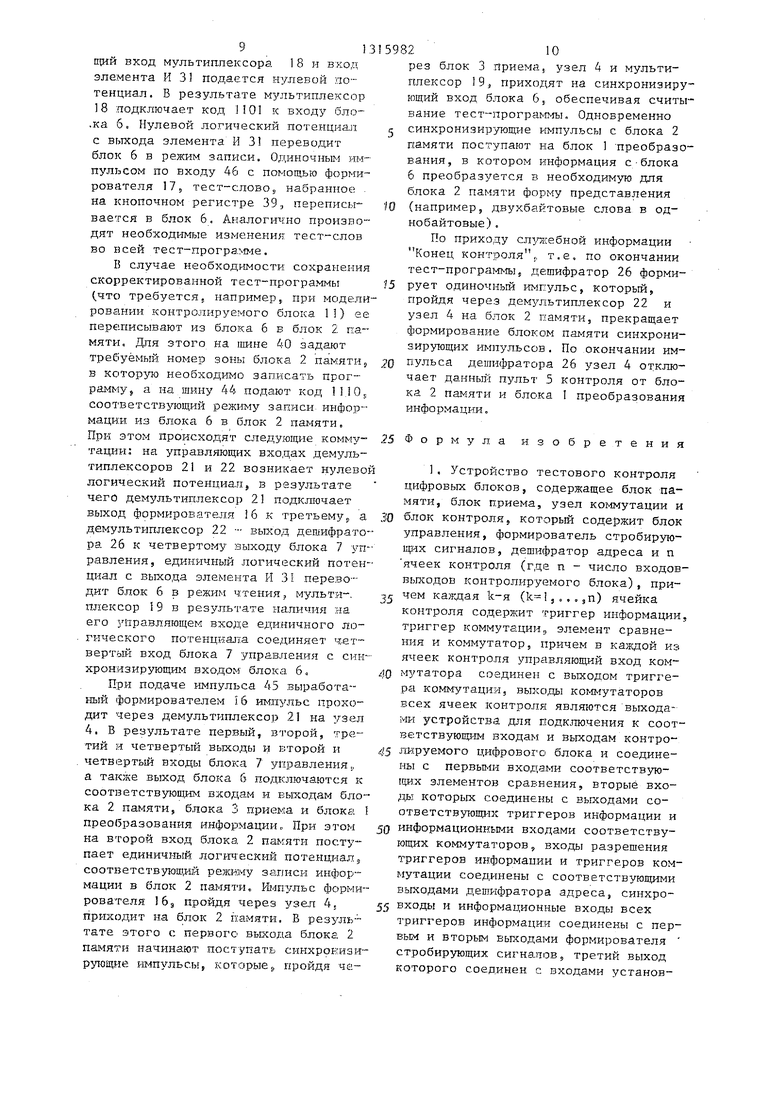

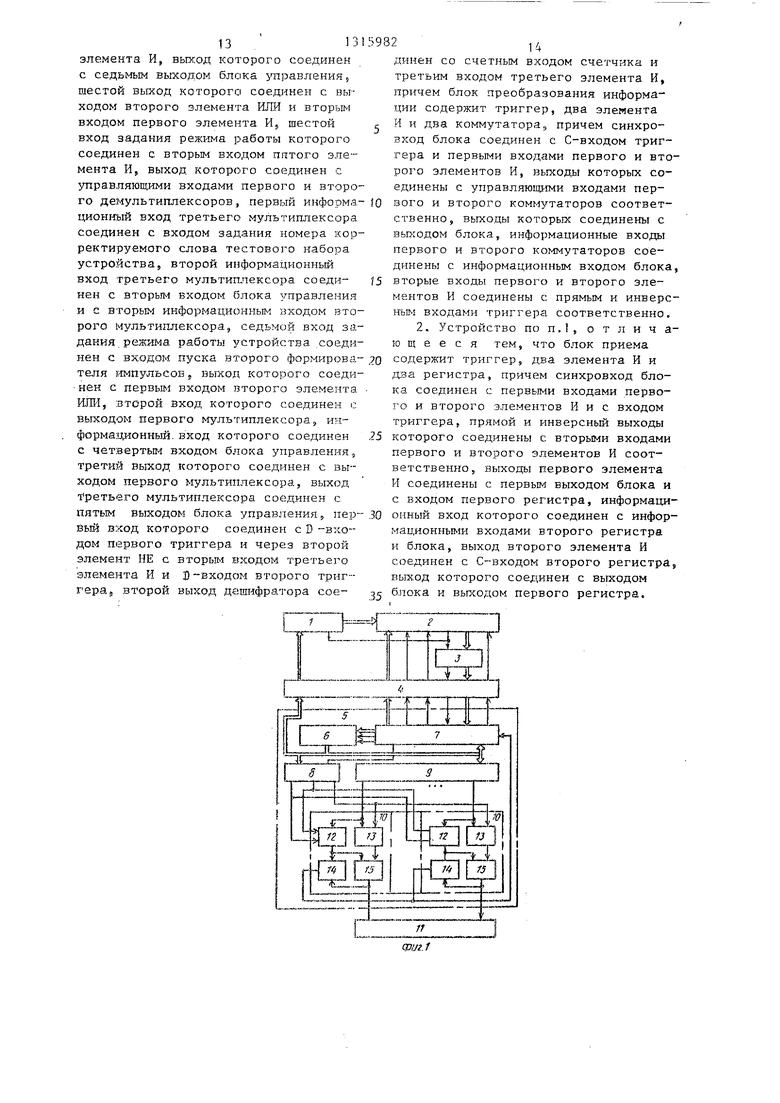

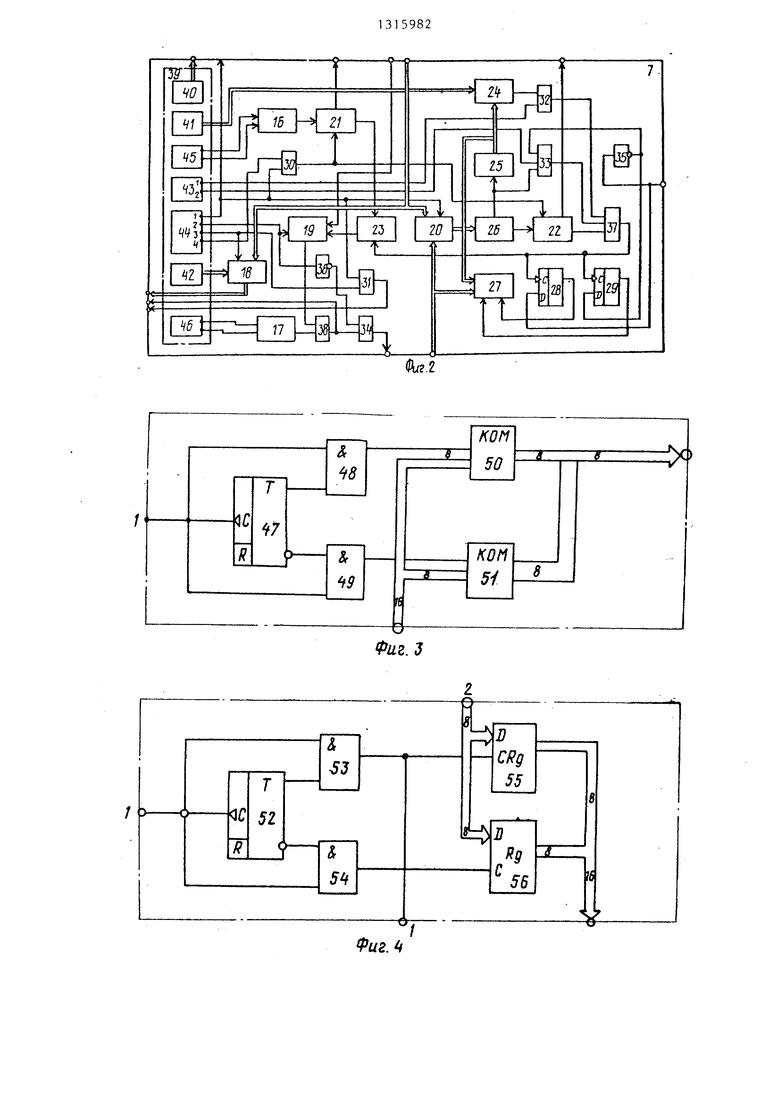

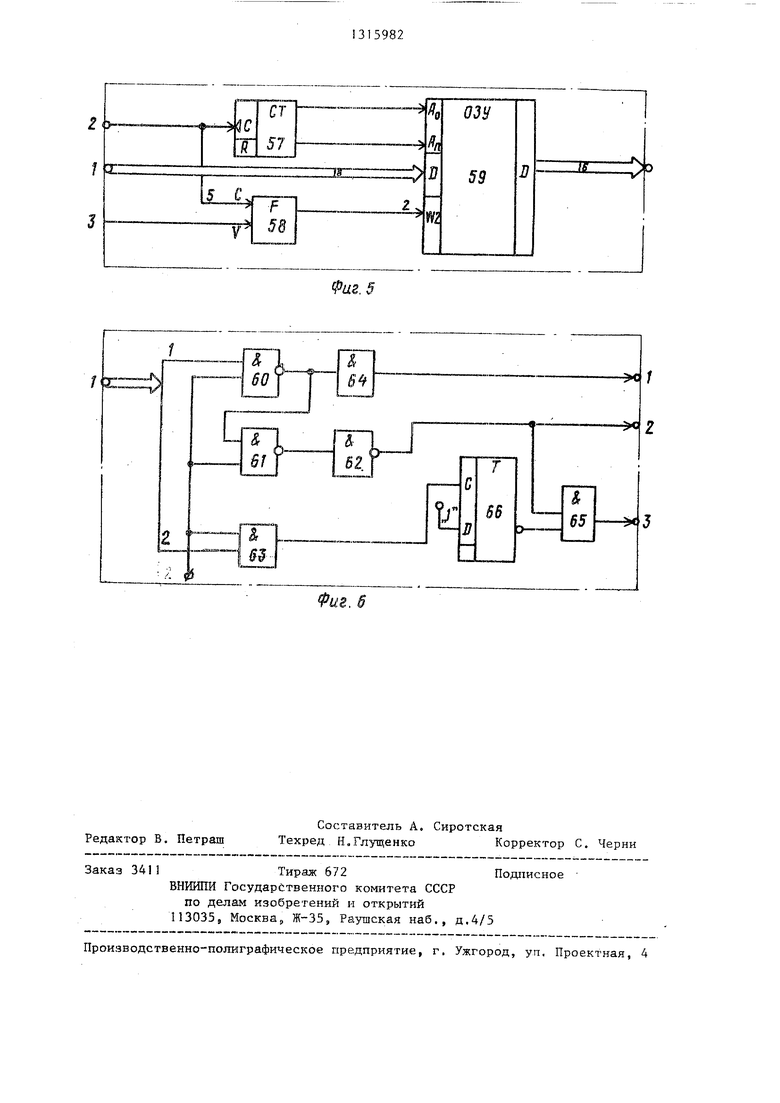

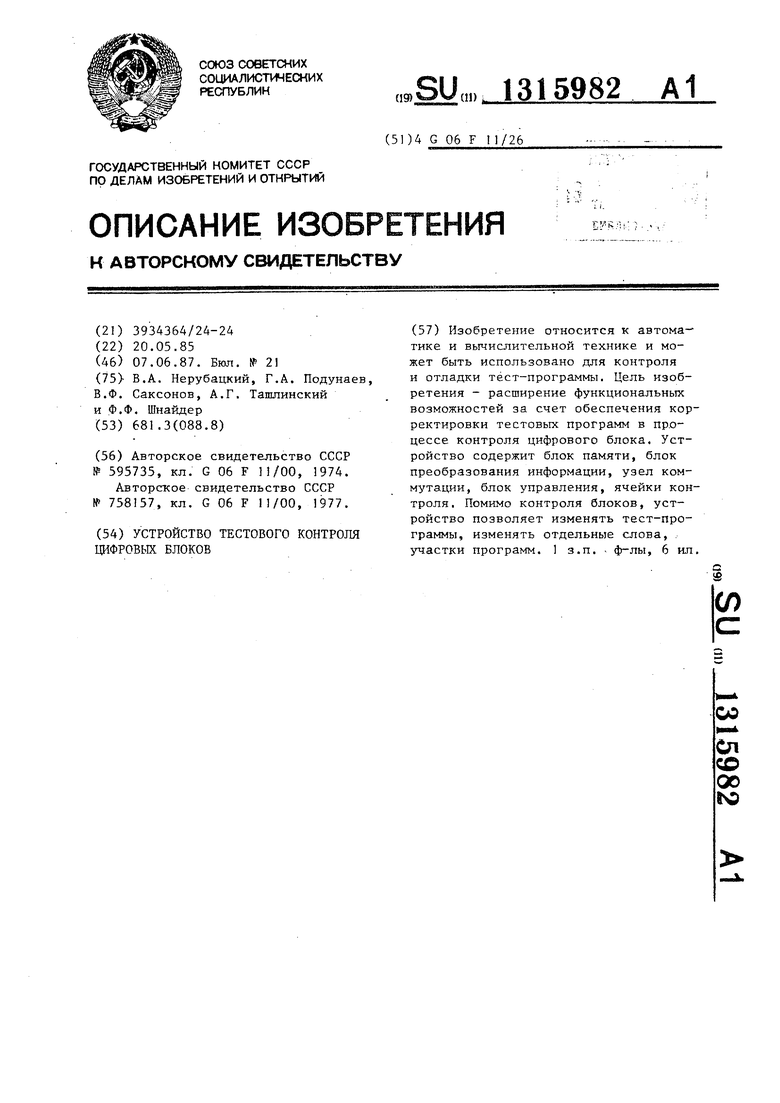

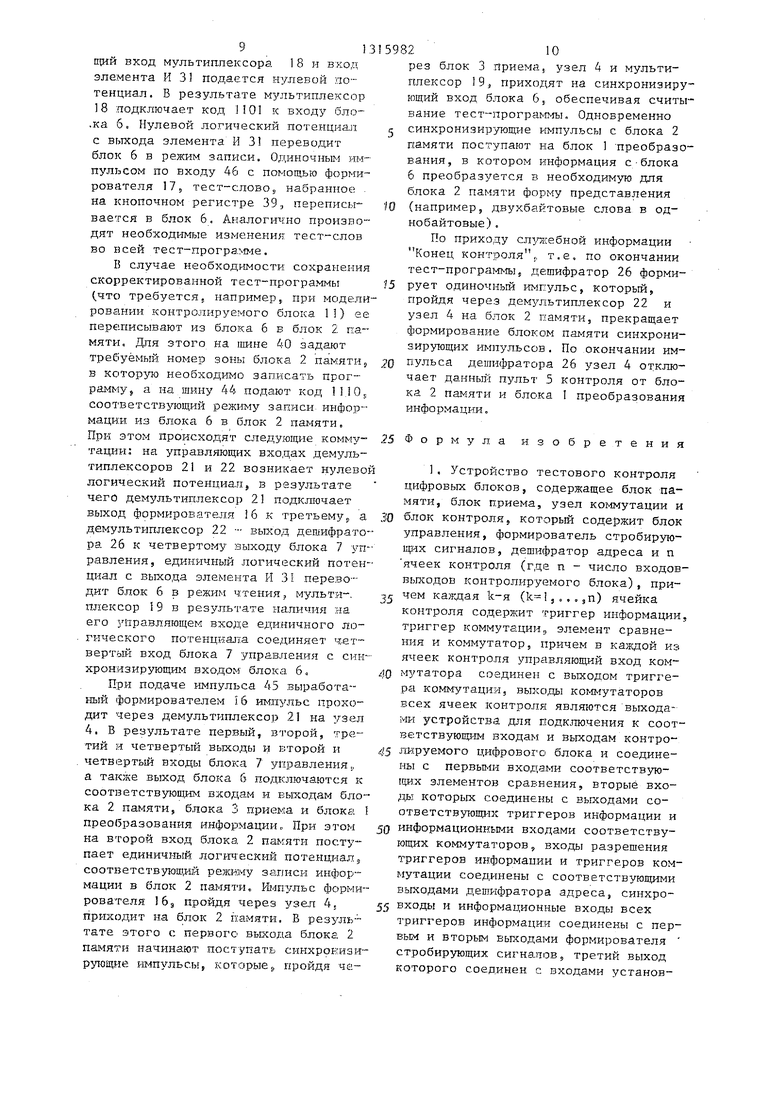

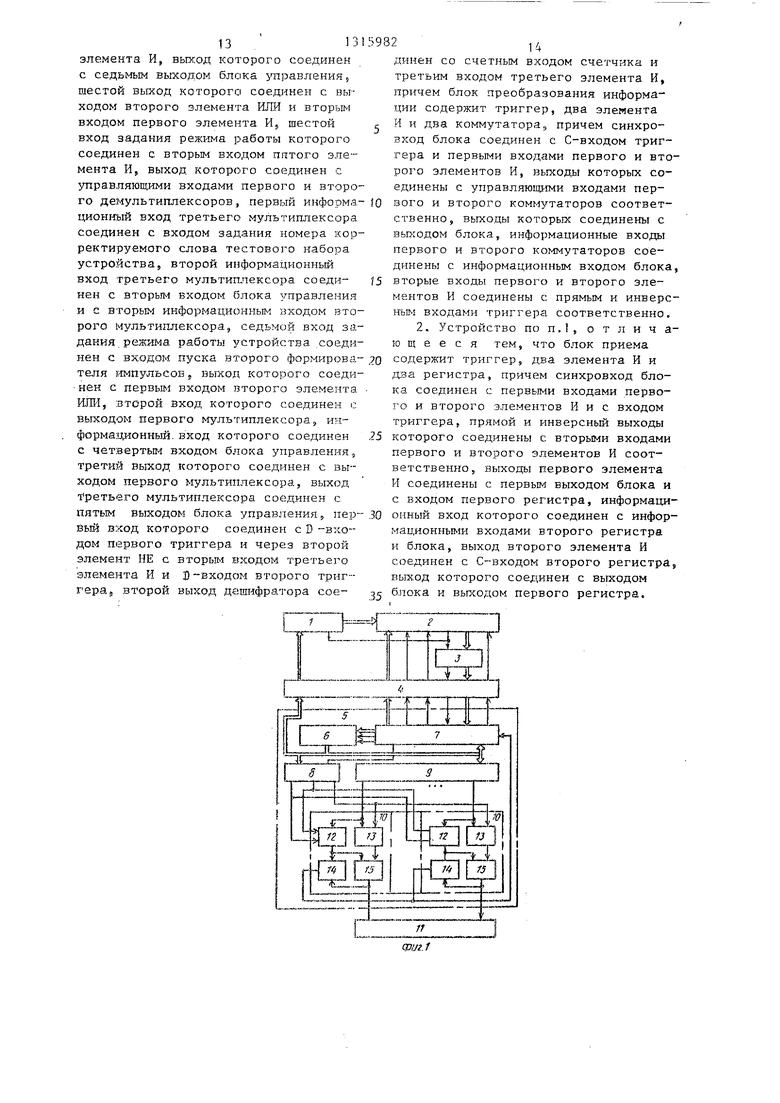

На фиг,1 приведена функциональная схема устройства тестового контроля цифровых блоков; на фиг,2 - функциональная схема блока управления; rfa фиг.З - схема блока преобразования информации; на - схема блока приема; на фиг,5 - схема блока памяти; на фиг,6 - схема формирователя стробирующих сигналов.

Устройство .(фиг„1) содержит блок преобразования информации, блок 2 па мятИэ блок 3 приема, узел 4 коммутации, блок 5 контроля, буферный блок 6 памяти блок 7 управления, формирователь 8 стробирующих сигналов, дешифратор 9 адреса, ячейки 10.1-lO.n контроля (п число входов/выходов контролируемого цифрового блока)j контролируемый цифровой блок П, в каж,цую ячейку контроля входят триггер 12 информации, триггер 13 коммутации, элемент 4 сравнения, коммутатор 15,

Блок 7 управления (фи1 ,2) содер- }кит формирователи 16 и 17 импульса, м:S льтиплeкcopьi 18 - 20, демультиплек сорь 21 и 22 J генератор 23 тактовых 1-1Мпульсов5 схему 24 сравнения, счетчик 25 числа тестовьк наборов, дешифратор 26, блок 27 индикации, триггер 28 и 29, элементы И 30-34, элементы НЕ 35 и 36, элементы РШИ 37 и 38, пульт 39 задания режимов контроля, которому принадлежит шина 40 задания адреса теста, шины 41 задания номера тестового набора5 тина 42 задания адреса корректируемого з частка таста. входы 43.1, 43.2,, 44.1-44,4,, 45 задания ренсимов работь ; вхо,ц 46 пуска.

Блок 1 преобразования информации (фнг.З) содержит триггер 47, элементы И 48 и 49, коммутаторы 50 и 51.

Блок 3 приема (фиг.4) содержит триггер 52, элемент И 53 и 54, регистры 55 и 56.

Блок 2 памяти (фиг.5) содержит счетчик 57, формирователь 58 импз льса ОЗУ 59,

9822

Формирователь 8 стробирующих сигналов (фиг.б) содержит элементы И-НЕ 60-62, элементы И 63-65, триггер 66, В исходном состоянии триггер 47

(фиг.З) установлен в нулевое положение (цепь установки не показана). На вход 2 блока поступают шестнадцатиразрядные слова информации, первые восемь разрядов которых поступают на

первый коммутатор, вторые - на второй,

С приходом синхронизирующих импульсов первый из них передает через первый коммутатор на выход первый

5 байт информации, а второй синхроимпульс черен второй коммутатор - второй байт информации.

В исходном состоянии триггер 52 (фиг.4) установлен в нулевое положе0 ние (цепи установки не показаны), На информационные входь регистров 55-и 56 поступает входной байт информации, на С-вход триггера и входы элементов И 53 и 54 поступают синхроим ) пульсьь Первый синхроимпульс проходит через открытый элемент И 54 и поступает на синхровход регистра 56, тем самым принимая в него первый байт информации. Этот же импульс не,. ребрасывает триггер в противоположное состояние, и второй сихроимпульс через открытый элемент И 53 поступает на синхровход регистра 55 и принимает в него второй байт информации. Далее информация с выходов регистров

поступает на выход блока в виде шестнадцатиразрядного слова, а с выхода элемента И 54 на выход блока поступает синхроимпульс.

В исходном состоянии счетчик 57 0 /, с л

(фиг.З.) установлен в нулевое состояние и, следовательно, в ОЗУ выбирается нулевая ячейка памяти (цепи установки не показаны). При записи информации в ОЗУ на его информационные входы поступают шестнадцатиразрядные сшова, а по третьему входу - сигнал записи, разрешающий формирование сигнала записи по переднему фронту синхроимпульса, поступающего на второй вход блока памяти,. По заднему фронту синхроимпульса счетчик увеличивает свое состояние и тем самьпч обращается к следующей ячейке ОЗУ,

Цри чтении информации с ОЗУ на вход формирователя поступает сигнал, запрещающий формирование сигнала, и на выход блока ОЗУ выдаются шестнадцатиразрядные слова

0

313

в исходном состоянии триггер 66 (фиг.6) установлен в нулевое положение (цепи установки не показаны) и элемент И 65 открыт для прохождения сигнала Зап.О с выхода элемента И-НЕ 62. Сигналы информации и служебная информация с первого входа формирователя поступают на элементы И-НЕ 60 и НбЗ. По приходу на второй вход формирователя синхросигнала либо на первом, либо на втором выходе формирователя в зависимости от входной информации формируется сигнал, Причем сигнал, поступающий на второй выход формирователя, проходит также через открытый инверсным выходом триггера элемент И 65 на третий выход. После появления служебного сигнала триггер 65 перебрасывается в единичное состояние и поступление сигналов с третьего выхода формирователя прекращается.

Устройство работает следующим образом.

Блок 5 контроля связан с контролируемым блоком 1, С помощью блока 7 управления через узел 4 запрашивают из блока 2 памяти необходимую тест- программу, которую переписывак1Т в блок 6. Подключение к блоку 2 памяти и блоку 3 приема производят посредством узла 4 в порядке поступления на него запросов. После записи тест- программы в блок 6 блок 5 контроля работает автономно. Входная и эталонная тестовая информация, считываемая с блока 6, записывается в ячейки 0 контроля. Запись производят с помощью блока 7 управления, формирователя 8 сигналов и-дешифратора 9 адреса. При необходимости тестовая информация, хранящаяся в блоке 6, может быть скорректирована и в исправленном виде записана в блок 2 памяти.

Блок 2 памяти имеет следующую - структуру. В каждой зоне памяти хранится тест-программа для определенного типа цифрового блока. Тест-программа состоит из тест-наборов, каждый из которых содержит информацию об очередном тестовом воздействии на контролируемый блок 11 (по входам контролируемого блока 11) и информацию об эталонном отклике (по выходам контролируемого блока 11). В свою очередь, тест-набор состоит из тест- слов , число которых равно числу изменений логических состояний на входах и выходах контролируемого блока 11

24

при задании очередного тестового воздействия.

Тест-слово может быть организовано, например5 следующим образом. Ин- формация записи логического нуля или логической единицы в одну из ячеек 10 контроля размещается в двух байтах. При этом первый разряд несет информацию Запись нуля - запись единицы, второй разряд - служебную информацию Контроль, которая разделяет тест-наборы и по которой происходит сравнение эталонной и реальной информации с контролируемого блока

П. В остальных разрядах размещается адрес соответствующей ячейки 10 контроля. В конце тест-программ помещают служебную информацию Конец контроля, которой соответствует наличие

в обоих байтах всех единиц.

В исходном состоянии блок 6, триггеры 12 информации и 13 коммутации, счетчик 25, триггер 28 и 29 находятся в нулевом (О) положении. На шины 43.1 и 44.1 подают логический О, генератор 23 включен (цепи установки исходного состояния указанных устройств, а также блока преобразования блока 2 памяти 5 блока 3

приема и формирователя 8 не показаны) , на шинах 43.2, 44.2-44.4 находятся логические единицы.

Для работы с контролируемым блоком 11 необходимую тест-программу

из блока 2 памяти переписывают в блок 6 следующим образом. На шине 40, связанной с первым выходом блока 7 управления, набирают адрес зоны памяти, в которой хранится необходимая тестпрограмма. На шине 44 устанавливают О, это соответствует режиму записи информации с блока 2 памяти в блок 6. При этом формируются следующие уп- -фавляющие воздействия: на второй выход блока 7 управления поступает нулевой потенциал, что соответствует режиму чтения с блока 2 памяти на управляющий вход мультиплексора 20 приходит нулевой потенциал, в результате чего тот .подключает второй вход блока 7 управления к входу дешифратора 26, на управляющие входы демуль- типлексоров 21 и 22 с выхода элемента И 30 поступает нулевой логический

потенциал, в результате чего выход формирователя 16 подключается к третьему, выход дешифратора 26 - к четвертому выходам блока 7 управления, а нулевой логический уровень с

выхода элемента И 3 iifepeводит блок 6 в режим записи.

При подаче импул}ьса на вход 6 формирователь 16 фор1х(ируег одиночный импульс,, который., пройдя через де-- мультигшексор поступает на узел 4s в результате чего тот подклт-зчает второй, третийэ и четвертый выхода и второй и четвертый зходь блока 7 управления соответственно к первому, второмуS. третьему и четвертому входам блок:а 2 памяти и первому и второму выходам блока 3 приема. Информация с требуемой зоны блока 2 памяти по синхросигналам (периодическая последовательность прямоугольных mf- пульсов) 5 приходя1цим с первого выхода (признака синхрониэацигГ) блока 2 памяти, поступает в блок, приема 3, где преобразуется в форму,, необходи- ну,о для работы блока 5 контроля (например, из однобайтовых слов по синхросигналам с блока 2 памяти руются двухбайтовые слова),.

СеЬормированные в блоке 3 приема коды,, а также соответствующие им импульсные воздействия (в частности,

в приведеннок примере и 5пульсы с уд

военным по сравнению с импульсами блока 2 памяти периодом следования) через узел 4, соответственно мульти плексоры 18 и 19 блока 7 управлен1-; я поступают на первый :;-: второй входы блока 6, в котором запоминаются, Од- новременно информация, приходящая с блока 3 приема, поступает через муль-- типлексор 20 на дешисЬратор 26. который дегпифрирует с;Аужебную информацию Контроль и Конец контроля. По окончании записи тест-прогршугмы, че--- му соответствует приход информации Конец контроля, на первом дешифратора 26 формируется одиночный импульс, который, пройдя через де мультиплексор 22 на узел 4,, прекращает считывание информации с блока 2 памяти и отключает блок от блока 2 памяти и блока 3 приема. В результате в блок 6 записывается необходимая тест-программа.

После записи в блок 6 необходимой тест-программы переходят к проверке работоспособности контролируемого блока 1 1 ,. Для этого на шину 44 подают код 101, соответствующий режиму контроля При этом на выходах элементов И 30 и 31 - един:кчные .иотентдиалг, В результате происходят с,)1адук)щие коммутации: мультиплексор 19 сбеди™

59826

няет выход генератора 23 чере-, чле- мент ИЛИ 38 с вторым (синхронизирующие) входом блока 6, мультиплексор 20 подключает выход блока 6 к. входу дешифратора 26, демультиплексор 22 соединяет первый выход дешифратора 26 с входом элемента ИЛИ 37, демультиплексор 21 подключает выход формирователя 16 к входу блокировки генера; ( тора 23, единичньй логический потенциал .(выхода элемента И 31) переводит блок 6 в режим чтения и на выходе элемента НЕ 36 возникает единичный потенциал,

15 Включение режгша потенциала производят подачей импульса на входы блока 6. При этом уклпупъс с формироваг- теля 16, пройдя через демультиплексор 21, включает генератор 23, им;.) пульсы которого начинают через мультиплексор 19 и элемент РШИ 38 на синхронизирующий вход блока 6, через элемент И 34 на второй вход формирователя 8. Б результате этого

25 начинается считывание тест-программы с блока 6. Информация тест-программы считывается последовательно по син- :-:ронизирующим импульсам генератора (с приходом каждого импульса считы30 вается одно тестовое слово ) и поступает на дешифратор 9 адреса, блок 7 управления и формирователь 8. В де- иифраторе 9 адреса дешифрируется 5.омер ячейки 10 контроля, в которую

3,- необходимо записать информацию. В блоке 7 управления выделяется служебная информация Контроль и Конец контроля. Формирователь 8 по синхронизирз;тщим сигналам с восьмо4fj го вЕ)1хода блока 7 управления выраба- гывает импульсы, с помощью которых информацию записывают в триггеры 13 коммутации и 12 информации.

Первый тест-набор программ несет в

45 себе коммутационную информацию, в

триггер 13 коммутации заносят данные управления о том, входом: или выходом является контакт контролируемого блока 11, к которому подключена та или иная ячей50 ка 10 контроля. Заполнение триггеров 13 коммутации происходит следующим образом. В исходном положении все триггеры, которые образуют разряды регистраS находятся в состоянииj ответствующем выходам контролируемого блока (например, в нулевом). Первьм тестом-набором програ ммы триггера 13 коммутации, соответствую- :a;-ie входам контролируемого блока 11 ,

713

переводятся в единичное положение. Для этого при очередном слове тест- набора дешифратор 9 адреса дает разрешение на соответствующую ячейку 10 контроля, а формирователь 8 выраба- тьшает на третьем выходе импульс, переводящий триггер 13 коммутации данной ячейки 10 контроля в единичное состояние. При этом число тесто- вых слов в первом тест-наборе равно числу входов контролируемого блока 1 .

Если в триггер 13 коммутации записана логическая единица, то коммутатор 5 соединяет выход триггера 12 информации с соответствующим входом контролируемого блока I1, если логический ноль - то коммутатор 15 разомкнут.

После установки триггера 13 коммутации переходят непосредственно к проверке контролируемого блока 1 I, При этом по окончании первого тест-набора в формирователе 8 дешифрируется служеб ная информация Контроль, в результате чего до окончания тест-программы запрещается формирование импульсов на тр етьем выходе формирователя 8, Последующими тест-наборами в триггеры 12 информации, соответствующие входам контролируемого блока II, заносится контролирующая информация, а в разряды, соответствующие выходам эталонная. При совпадении реального отклика контролируемого блока 11 с эталонным на выходе элемента 14 формируется логическая единица. При несовпадении реального отклика эталонному (что говорит о неисправности контролируемого блока 11) на вход элемента И 33 с выхода элемента НЕ 35 поступает разрешающий потенциал.

По окончании текущего тест-набора дешифратор 26 (по приходу служебной информации Контроль) формирует импульс, который, пройдя через элемент Ш1И 37, выключает генератор 23, в результате чего считьюание информации с блока 6 прекращается. Одновременно тем же импульсом триггер пе- рев.одится в единичное состояние, индикатор 27 отображает факт неисправности, а на элементе 14 сравнения формируется код номера контактов контролируемого блока 1, по которым произошло несовпадение. Используя полученную информацию о неисправности, переходят к ее поиску и устранению.

59828

Если реальный отклик контролируемого блока 1 соответствует эталонному, то контроль продолжается в автоматическом режиме. Если в течение

всей тест-программы н,е обнаружено неисправностей, то по ее окончании импульс с дешифратора 26, сформированный по приходу служебной информации Конец контроля и прошедший через

10 демультиплексор 22 и элемент ИЛИ 37, записывает в триггер 38 логическую единицу. При этом индикатор 27 отображает информацию об отсутствии неисправности в контролируемом блоке

15 П. Одновременно импульс дешифратора 26 выключает генератор 23,

При необходимости временного или постоянного изменения тест-программы на шину 43 подают код 10, соответст20 вующий режиму поиска необходимого тест-набора. При этом на элемент И . 32 подается разрешающий единичный по тенциал, а на элемент И 33 - нулевой, На шине 44 код 1011.

25

Номер тест-набора, в котором нужно произвести изменения, подают на шину 41. Далее к входу 46 подключают генератор 23. Тест-программа, считывае30 мая с блока 6, поступает через мультиплексор 20 на дешифратор 26. При этом в счетчике 25 происходит подсчет лриходящих тест-наборов путем

подсчета числа импульсов, соответст- эг вующих служебной информации Контроль. По приходу искомого тест-набора, т.е, при совпадении кодов, схема 24 сравнения формирует импульс, который, пройдя через элементы И 32 и

Q ИЛИ 37, выключает генератор 23, Индикатор 27 отображает номер найденного тест-набора,

Поиск нужного слова внутри набора осуществляется путем пошагового счи тывания тестовых слов данного тест- набора. При поступлении единичного импульса на вход 46 формирователя 17 через элемент ИЛИ 38 импульс поступает на синхронизирующий вход ка 6, Одновременно считьшаемая информация отображается на индикаторе 27, по которому находят требуемое тест- слово .

После нахождения тест-слова, лежащего изменению, на шину 42 задают измененное тест-слово, а на шину 44 подают код ПО, что соответствует режиму записи в блок 6 с кнопочного регистра. Прн этом на управляю913

щий вход мультиплексора 18 и вход элемента И 31 подается нулевой потенциал. В результате мультиплексор 18 подключает код 1101 к входу бло- .ка 6. Нулевой логический потенциал с выхода элемента И 31 переводит блок б в режим записи. Одиночным импульсом по входу 46 с помощью формирователя 175 тест-слово5 набранное на кнопочном регистре 39, переписывается в блок 6. АксШогично производят необходимые изменения; тест-слов во всей тест-программе.

В случае необходимости сохранения скорректированной тест-программы (что требуется, например, при моделировании контролируемого блока 11) ее пер€1писывают из блока 6 в блок 2 памяти. Для этого на шине 40 задают требуемый номер зоны блока 2 памяти. в которую необходимо записать программу s а на шину 44 подают код 1IJOj соответствующий режиму записи информации из блока 6 в блок 2 памяти, При этом Происходят следующие коммутации: на управляющих входах демуль- типлексоров 21 и 22 возникает нулево логический потенциал, в результате чего демультиплексор 21 подключает выход формирователя 16 к третьему,, а демультиплексор 22 - выход дешифратора 26 к четвертому выходу блока 7 управления, единичный логический потенциал с выхода элемента И 31 переводит блок 6 в режим чтения, мультн-. плексор 19 в результате наличия на его управляющем входе единичного логического потенциала соединяет ч.ет-- вертый вход блока 7 управления с синхронизирующим входом блока 6,

При подаче импульса 45 выработа-- ный формирователем 16 импульс проходит через демультиплексор 21 на 4. В результате первый, второй, третий и четвертый выходы и второй и четвертый входы блока 7 управления а также выход блока 6 подключаются к соответствующим входам и вы:х;одам бло ка 2 памяти, блока 3 приема и блока прео(5разования информации„ При этом на второй вход блока 2 памяти поступает единичьшй лоп-гч ескнй потенциал, соответствуюшдй режкму записи информации в блок 2 памяти. Илт.ульс формирователя 6д пройдя через узел 4, приходит на блок 2 памяти, В результате этого с первого выхода блока 2 памяти начинают поступать синхронизирующие шлиулъс.ы, которые;, пройдя че210

рез блок 3 приема, узел 4 и мультиплексор 19, приходят на синхронизирующий вход блока 6, обеспечивая считывание тест-программы. Одновременно

синхронизир:;лощие импульсы с блока 2 памяти поступают на блок 1 преобразования, в котором информация сблока 6 преобразуется в необходимую для блока 2 памяти форму представления

(например, двухбайтовые слова в однобайтовые) .

По приходу сл лсебной информации Конец контроля,, т.е. по окончании тест-программы, дешифратор 26 формирует одиночный импульс, который, пройдя через демультиплексор 22 и узел 4 на блок 2 памяти, прекращает формирование блоком памяти синхронизирующих им :ульсов. По окончании импульса дешифратора 26 узел 4 отключает данньш пульт 5 контроля от блока 2 памяти и блока I преобразования информации.

Фор мула изобретения

1, Устройство тестового контроля цифровых блоков, содержащее блок памяти, блок Приема, узел коммутации и

блок контроля, который содержит блок управления, формирователь стробирую- 1Ц1ЧХ сигналов, дешифратор адреса и п ячеек контроля (где п - число входов- выходов контролируемого блока), причем каждая k-я (k-l,,,,,n) ячейка контроля содержит триггер информации, триггер коммутации,, элемент сравнения и коммутатор, причем в каждой из ячеек контроля управляющий вход коммутатора соединен с выходом триггера коммутаци;я, выходы Kot-шутаторов всех ячеек контроля являются выходами устройства для подк.шочения к соответствующим входам и выходам контролв:руемого цифрового блока и соединены с первыми входами соответствую- ци;х элементов сравнения, вторые входы которых соединены с выходами соответствующих триггеров информации и

информационными входами соответствующих коммутаторов, входы разрешения триггеров информации и триггеров коммутации соединены с соответствующими выходами дешифратора адреса, синхровходы и информационные входы всех

триггеров информации соединены с пер- вьЕУ и вторым выходами формирователя стробирующих сигналов, третий выход которого соединен с входами установ111

ки в Г всех триггеров коммутации, выходы всех элементов сравнения соединены с первым входом блока управления, второй вход которого соединен с первым выходом узла коммутации, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения возможности корректировки тестовых программ в процессе контроля цифрового блока, устройство содержит блок преобразования информации, а блок контроля содержит буферный блок памяти, причем выход буферного блока памяти соединен с третьим входом блока управления, первым информационным входом узла коммутации, информационным входом формирователя стробирующих сигналов и информационным входом де- пшфратора адреса, первый, второй, третий и четвертый выходы а также четвертый вход блока управления соединены с вторым и третьим информационными входами, управляющим, четвертым информационным и вторым выходом узла коммутации соответственно, пятый, шестой и седьмой выходы блока управления соединены с адресным и синхрониз ирующим входами и входом чтения буферного блока памятиj восьмой выход блока управления соединен с синхровходом формирователя стробн- рующих сигналов, выход признака синхронизации блока памяти соединен с синхровходами блока приема и блока преобразования информации, выход блока памяти соединен с информационным входом блока приема, первый и второй выходы которого соединены с пятым и шестым информационными входами узла коммутации, адресный вход, вход записи/считывания, вход разрешения и вход блокировки блока памяти соединены с третьим, четвертым, пятым и шестым выходами узла коммутации с оот ветственно, информационный вход блока преобразования информации соединен с седьмым выходом узла коммутации, выход блока преобразования информации соединен с информационньм входом блока памяти, при этом блок управления содержит первый и второй формирователи импульсов, первый, второй и третий мультиплексоры,. первый и второй демультиплексоры, генератор синхроимпульсов, схему сравнения, счетчик, дешифратор индикатор, первый и второй триггеры, первый, второй, третий, четвертый и пятый эле212

менты И, nepBbrii и второй элементы НЕ, первый и второй элементы ИЛИ, при этом первый выход блока управления подключен к шине задания адреса теста устройства, первый вход схемы сравнения подключен к шине задания номера тестового набора устройства, вход пуска которого соединен с входом пуска первого формирователя импульсов, выход которого соединен с информационным входом первого демульти- плексора, выход которого соединен с входом пуска генератора синхроимпульсов , выход которого соединен с синхровходом первого мультиплексора, управляющий вход которого соединен с первым входом задания режима работы устройства и через первый элемент НЕ с первым входом первого элемента И,

выход которого соединен с восьмым

выходом блока управления, третий вход которого соединен с первыми информационными входами второго мультиплексора и индикатора соответственно,

второй вход индикатора соединен с выходом счетчика и вторым входом схемы сравненияS выход Равно которой сое- динен с первым входом второго элемента И, выход которого соединен с первым входом первого элемента ШШ, выход которого соединен с входом блокировки генератора синхроимпульсов и с входами первого и второго триггеров, выходы -которых соединены с третьим

и четвертым входами индикатора соответственно, второй вход задания режима работы устройства соединен с вторым входом второго элемента И, третий вход задания режима работы устройства соединен с первым входом третьего элемента И, выход которого соединен с вторым входом первого элемента ffllH, четвертый вход задания ре- , жима работы устройства соединен с

вторьм выходом блока управления, с первыми входами четвертого и шестого элементов И, с управлящим входом второго мультиплексора, выход которого соединен с информационным входом

дешифратора, первый выход которого соединен с информационным входом второго демультиплексора, первый и второй выходы которых соединены с четвертым выходом блока управления и

третьим входом первого элемента ИЛИ соответственно, пятый вход задания режима работы устройства соединен с управляющим входом третьего мультиплексора и вторым входом четвертого

13 .13

элемента И, выход которого соединен с седьмым выходом блока шравления} шестой выход которого соединен с выходом второго элемента HIM и вторьм входом первого элемента И, шестой вход задания режима работы которого соединен с вторым входом пятого элемента И, выход которого соединен с управляющими входами первого и второго демультиплексоров, первый информационный вход третьего мультиплексора соединен с входом задания номера корректируемого слова тестового набора устройства, второй информационный вход третьего мультиплексора соединен с вторь м входом блока управления и с вторым информационным входом второго мультиплексора, седьмой вход задания, режима работы устройства соединен с входом пуска второго формирователя нмпульсоБ 5 выход которого соеди- ней с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом первого мультиплексора, ин- форма:ционный. вход которого соединен с четвертьм входом блока управления, третий выход которого соединен с выходом первого мультиплексора, Третьего мультиплексора соединен с пятым выходом блока управления,, первый вход которого соединен с D -входом первого триггера и через второй элемент НЕ с вторьм входом третьего элемента И и S-входом второго триггера 5 второй выход детаифратора сое98214

динен со счетным входом счетчика и третьим входом третьего элемента И, причем блок преобразования информации содержит триггер, два элемента с И и два коммутатора, причем синхро- зход блока соединен с С-входом триггера и первьп и входами первого и второго элементов И, выходы которых соединены с управляющими входами перfO вого и второго коммутаторов соответственно, выходы которых соединены с вьпсодом блока, информационные входы первого и второго коммутаторов соединены с информационным входом блока, f5 вторые входы первого и второго элементов И соединень с прямым и инверс- ны входами триггера соответственно,

2. Устройство по п,1, отличающееся тем, что блок приема

20 содержит триггер, два элемента И и

два регистра, причем синхровход блока соединен с первыми входами первого и второго элементов И и с входом триггера 5 прямой и инверсный выходы 25 которого соединены с вторыми входами первого и второго элементов И соответственно, выходы первого элемента И соединены с первым выходом блока и с входом первого регистра, информаци30 онный вход которого соединен с информационными входами второго регистра и блока, выход второго элемента И соединен с С- зходом второго регистра, вьжод которого соединен с выходом j блока и выходом первого регистра.

-f „„ 1--jA-™; «..-.

Фаг. J

Фиг.

Фае. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровыхблОКОВ | 1979 |

|

SU796860A1 |

| Устройство для контроля блоков памяти | 1984 |

|

SU1594610A1 |

| Устройство для диагностирования логических блоков | 1982 |

|

SU1071978A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1179346A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1013960A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для контроля логических узлов | 1980 |

|

SU888127A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1278855A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля и отладки тест-программы. Цель изобретения - расширение функциональных возможностей за счет обеспечения корректировки тестовых программ в процессе контроля цифрового блока, Устройство содержит блок памяти, блок преобразования информации, узел коммутации, блок управления, ячейки контроля . Помимо контроля блоков, устройство позволяет изменять тест-программы, изменять отдельные слова, . участки программ. 1 з.п. - ф-лы, 6 ил. 00 Сл х 00 ю

Фил. б

Редактор В. Петраш

Составитель А, Сиротская Техред , Н.Глущенко Корректор С. Черни

Заказ 3411Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035s МоскваS Ж-35,, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для контроля логических схем | 1976 |

|

SU595735A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 758157, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-07—Публикация

1985-05-20—Подача