(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КОЭФФИЦИЕНТОВ

ПОЛИНОМА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления коэффициентов полинома | 1978 |

|

SU734714A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МЕСТ ПОВРЕЖДЕНИЯ НАПОРНОГО ТРУБОПРОВОДА | 1992 |

|

RU2046251C1 |

| Устройство для обработки сейсмической информации | 1984 |

|

SU1208561A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Устройство для решения нелинейных задач теории поля | 1983 |

|

SU1156101A1 |

| Устройство для измерения параметров жидкости | 1990 |

|

SU1830460A1 |

| Устройство для передачи цифровой информации | 1983 |

|

SU1141436A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

Изобретение относится к вычислительной технике, и может быть использовано в автоматических системах управления. Известно устройство для вычисления коэффициентов полинома 1. Недостатком этого устройства 5шпяет- ся малое быстродействие. Наиболее близким техническим решени ем к предлагаемому является устройство для вычисления коэффициентов полинома, содержащее генератор импульсов, блок ввода, блок памяти переменных, блок умножения, сумматор, первый блок памяти результата, блок регистрации, причем выход блока ввода подсоединен к первому входу блока умножения, второй выход пер вого блока памяти результата подключен к входу блока регистрации, и узел формирования первого импульса последовательности, семь элементов задержки, счет- чик переменных, первый-и второй счетчики, элеме|нт НЕ, семь элементов И, три элемента ИЛИ, блок сравнения, второй блок памяти результата, блок буферной памяти, причем выход генератора импульсов подсоединен к входу узла формирования первого импульса последовательности, первому входу счетчика переменных и первому входу первого элемента И, выход узла формирования первого импульса последовательности подключен к первому входу первого элемента ИЛИ, вторые входы счетчика переменных и первого эле- мента ИЛИ соединены с выходом первого элемента И, а третий вход счетчика переменных подключен к другому выходу блока ввода, выход счетчика переменных подключен к второму входу первого элемента И и второму входу блока памяти переменных, выход блока сравнения подключен к входу элемента НЕ, третьему входу первого элемента И и первому входу второго элемента И, выход первого элемента ИЛИ подсоединен к входу первого элемента задержки, второго элемента задержки, первому входу третьего элемента И и первому входу второго элемента ИЛИ, группы выходов первого и второго счетчиков подключены к соответствующим вкодам бпока сравнения, нулевой вход первого счетчика подсоединен к первому выходу третьего элемента задержки, а единичный вход связан с выходом четвертоrq элемента задержки, выход первого .счетчика подсоединей к второму входу второго элемента И, выход второго элемента ИЛИ подсоединен .к входу четверто го и пятого элемента задержки, выход пя того элемента задержки подключен к первому входу четвертого элемента И, второй вход которого соединен с выходом элемента HEi а выход - с первым входом тр тьего элемента ИЛИ, выход бпока памяти переменных подключен к второму входу третьего элемента И, выход третьего элемента ИЛИ соединен с входом блока умножения, выход которого подключен к вкоду пятого элемента И, второй вход которого и шестого элемента задержки . подсоединены к выходу первого элемента задержки, а выкод шестого элемента задержки - к первому входу шестого элемента И,второй вход которого связан с выходом, сумматора, а выход - с входом блока буферной памяти, с первым входом первого блока памяти результата и вторым входом элемента второго элемента ИЛИ, выход третьего элемента задержки сое . динен с первым входом седьмого элемента И и вторым входом второго блока рапяти результата, выход которого соединен с пер вым входом первого блока памяти резуль тата, выход блока буферной памяти подключен к второму входу седьмого элемен та И, выход которого соединен с вторы входом первого блока памяти результата, выход пятого элемента И соединен с ВХОДОМ сумматора, выход второго элемен та задержкиподключен к третьему входу второго элемента И, выход которого соединен с входами третьего и седьмого элементов задержки, а выход седьмого эяе; {ента задержки подключен к входу вто рого счетчика t 23. Это устройство позволяет вычислять коэффициент полинома VI„у, .). Однако чаще всего аргументы Xi и 4 ( 1 2,.--, и ) имеют смысл вероятности осуществления некоторого события в -i-M опыте (например, вероятность отказа устройства), т.е. X-Pr,V,. Тогда значение коэффициентов а, полиномаloam--n/(.). трактуется как вероятность того, что дискретная целочисленная случайная величина У примет определенное значенйеК P5x-Kl-J,.|.K,o,,,...,H, r-l.illiOii iJlfii) К-ои,...,и ик-ТсГ В ЭТОМ случае значения коэффициентов а„ сначала монотонно возрастают, а затем монотонно стремятся к нулю при К, приближающемся к Vi. (при ,с), Это дает основание для прекращения вычисления последующих коэффициентов при достижении заданного порога значения коэффициентов ay,,, т.е. если при некотором crtvii iS- TO остальные и - К коэффициенты не могут быть больше О у.... В связи с тем, Что диапазон представления чисел в ЦВМ , с некоторого К значениеа | 4(минимальное отличное от нуля число) и все последующие значения (,С1к+1.--, ик) становится равными нулю. Однако известное устройство оканчивает работу только после вычисления всех значений коэффициентов 0,, что приводит к нерациональной трате времени и снижает производительность АСУ. Целью изобретения является увеличение производительности. Эта цель достигается тем, что в устройство, содержащее блок ввода, блок памяти переменных, счетчик переменных, щесть элементов И, элемент И разрешения копирования, три элемента ИЛИ, блок умножения, блок памяти результата, сумматор, блок буферной памяти, генератор импупиьсов, формирователь первого импульса, семь элементов задержки, блок счетчиков адреса памяти результата, счетчик циклов, первый блок сравнения, регистр состояния счетчика циклов, элемент НЕ, блок регистрации, причем первый выход блока ввода соединен с установочными входами счетчика переменных, а второй выход - с информационными входом блока памяти переменных, выход которого соединён с первым входом первого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого подключен к первому входу блока умножения, выхоД которого соединен с первым входом второго элемента И, выход которого соединен с входом сум матора, выход которого соединен с первым входом третьего элемента И, выход которого соединен с входом блока буфер- ной памяти и первым входом второго элемента ИЛИ, выход которого через первый элемент задержки подключен к первому входу четвертого элемента И, а через второй элемент задержки к счетному входу счетчика циклов, выходы которого поД ключены к первой группе входов первого блока сравнения и первому входу элемента И разрешения копирования, выход которого через третий элемент задержки соединен с входом регистра состояния счетчика циклов, выходы которого соединены с второй группой входов первого блока сравнения, выход которого через элемент НЕ подключен к второму входу четвертого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, выход генератора импульсов соединен с входом формирователя первого импульса, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого через четвертый элемент задержки подключен к второму входу второго элемента И и к входу пятого элемента задержки, выход которого соединен с вторым входом третьего элемента И, выход третьего элемента ИЛИ соединен с вторым вхоаом первого элемента И, с вторым Входом второго элемента ИЛИ и через шестой элемент задержки с вторым вхо- дом элемента И разрешения копирования, выход которого соединен через седьмой элемент задержки с входом установки нуля счетчика циклов, с первым входом пятого элемента И и первым входом блока счетчиков адреса памяти результата, ИзТ- ходы которого подключены к адресным входам блока памяти результата, второй вход блока счетчиков адреса памяти реаупьтата соединен с выходом третьего элемента И, второй вход пятого элемента И соединен с выходом блока буферной памяти, а выход - с информационным входом блока памяти результата, выходы которого соединены с вторым входом блока умножения и входом блока регистрации, выход первого блока сравнения соединен с первым входом шестого элемента И и третьим входом элемента И разрешения копирования, выходы счетчика переменных соединены с адресными -входами блока памяти переменных и вторым входом шестого элемента И, третий вход которого подключен к выходу генератора, а выход соединен с вторым входом третьего элемента ИЛИ и вычитающим входом счетчика переменных, дополнительно введень второй и третий блок сравнения, причем вход второго блока сравнения соединен с третьим выходом блока памяти результата, выход второго блока сравнения с первым входом третьего блока сравнения, второй выход которого соединен с третьим выходом блока ввода, а выход с входом генератора импульсов.

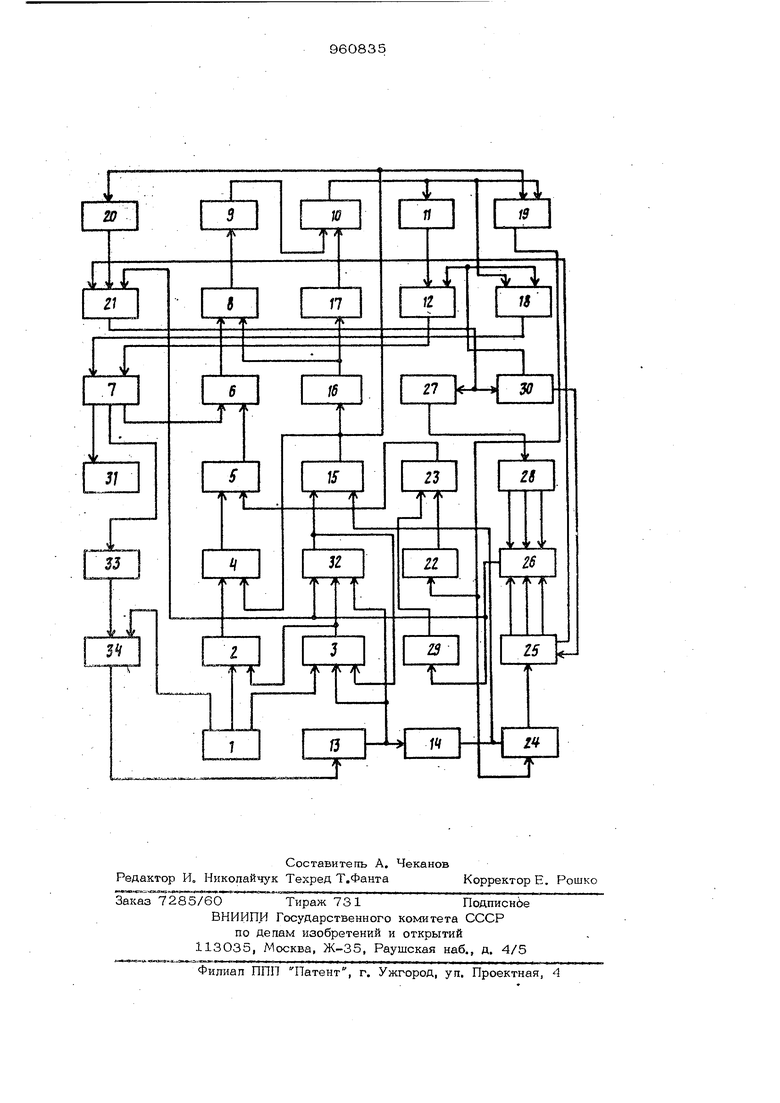

На чертеже дана схема предлагаемого устройства.

Устройство содержит блок 1 ввода, блок 2 памяти переменных, счетчик 3 переменных, первый элемент И 4, первый элемент ИЛИ 5, блок 6 умножения, блок 7 памяти результата, второй элемент И 8, сумматор 9, третий элемент И 10, блок 11 буферной памяти, пятый элемент И 12, генератор- 13 импульсов, формирователь 14 первого . импульса, третий элемент ИЛИ 15, четвертый 16 и пять1й 17 элементы задержки, блок 18 счетчиков адреса памяти результата, второй элемент ИЛИ 19, шестой элемент 20 задержки, элемент И 21 разрешения копирования, первый элемент 22 задержки, четвертый элемент И 23, второй элемент 24 задержки, счетчик- 25 циклов, первый блок 26 сравнения, третий элемент 27 задержки, регистр 28 состояния счетчика циклов, элемент НЕ 29, седьмой элемент 30 задержки, блок 31 регистрации, шестой элемент И 32, второй 33 и третий 34 блоки сравнения.

Блок 1 ввода предназначен для па ралпепьного приема переменных из аппаратуры АСУ и ввода переменных в блок 2 памяти переменных.

Для обеспечения возможности автономной работы устройства в блок 1 ввода введено устройство перевода вводимых значений переменных из Десятичной системы счисления в двоичную. Блок 1 ввода соединен со счетчиком 3 переменных, предназначенным для подсчета введенных переменных. Этот счетчик явтгяется реверсивным т.е. считает от О до и и от VI До О, В Предлагаемом варианте VI 10О.

Блок 2 памяти переменных предназначен для хранения переменных X и ч/ и представляет собой две памяти; память у и память N с устройствами управления.

Блок 2 памяти переменных через элемент И 4 и элемент ИЛИ 5 соединен р.блоком умножения, который предназначен для 79 умножения множимого на все раарядь множителя, начиная со старшего. В качестве множимого берутся переменные ( и j в качестве множителя - содержимое двух ячеек блока 7 памяти резупьтата. Причем бпок 6 предназначен дпя параллельного умножения где и Vi - переменные из блока 2 памяти переменных ,а аJ - значения соответствуюших ячеек блока 7 памяти результатов ( а i|, и Блок 6 умножения соединен через элемент И 8 с сумматором 9 параллельного действия, связанным через элемент И 1О с блоком 11 буферной памяти. Блок 11 буферной памяти выполнен аналогично блоку 7 памяти результатов на регистpax и соединен с ним через элемент И 12, Вь1ход генератора 13 импульсов соединен с узлом 14 формирования первого импульса, представляющим собой триггер, элемент задержки, причем, первый вход элемента И является входом узла 14 формирования первого импульса, второй вход элемента И соединен с единичным выходом триггера, а вход элемента И узла с единичным выходом триггера. Выход элемента И через элемент задержки соединен с нулевым входом триггера и явгшется также выходом узла 14 формирования выдачи первого импульса. Он соединен через элемент ИЛИ 15 и элемент И 4 с блоком 6 умножения, через элемент 16 задержки и элемент И8-с суммато-, ром 9, через элемент 17 задержки и элемент И 1О - с блоком 11 буферной памяти и единичными входами блока 18 счетчиков адреса памяти результатов и первым входом элемента ИЛИ 19. ) Бпок 18 счетчиков адреса памяти результатов предназначен для управления выдачей результатов из двух соседних ячеек блока 7 памяти на блок 6 умножени я н представляет собой два счетчика, один из которых предназначен для определения ячейки для умножения ее содержимого на X, а другой - для определения ячейки дпя умножения ее содержимого на VВторой взсоД элемента ИЛИ 19 соедиией с выходом элемента ИЛИ 15 и через элемент 2О .задержки с первым входом элемента И 21 разрешения копирования, который представляет собой трехвходовый элемент И. Выход элемента ИЛИ 19 соединен через элемент 22 задержки, элемент И 23, элемент ИЛИ 5 с блоком 6 умножения и через элемент 24 задержки с единичным входом счетчика 25 циклов, 358 выходы которого соединены с блоком 26 сравнения и через второй вход элемента И 21 разрешения копирования и элемент 27 задержки срегистром 28 состояния счетчика циклов. Выход блока 26 сравнения соединен с третьим входом элемента 21 разрешения копирования, а также через элемент НЕ 29 с вторым входом элемента И 21. Выход элемента И 21 разрешения копирования, кроме того, соединен через элемент 30 задержки с нулевыми входами счетчика 25 циклов блока 18 счетчиков памяти результатов и вторым входом элемента И 12, Выход блока 7 памяти результатов соединен о блоком 31 регистрации, служащим для сопряжения с аппаратурой АСУ, если информация используется в следующих устройствах, или для отображения информации средствами индикации, выполненнымина элементах ИН-17. обеспечения возможности автономной работы устройства в блок 31 регисгистрации введено устройство перевода результата из двоичной системы счиспе ния в десятичную. Выход генератора 13 соединен также с первым входом элемента И 32 разрешения-прохождения импульсов, второй вход которого соединен с блоком 26 сравнения, а третий вход,- с выходом счетчика 3 переменных. Выход элемента И 32 разрешения прохождения импупьсов соединен с входом элемента ИЛИ 15. Элемент И 32 разрешения прохождения импульсов представляет собой трехвходовую схему И. Третий вход блока 7 памяти резупьта соединен с входом второго блока 33 сравнения, выход которого соединен с первым входом третьего блока 34 сравнения. Второй вход третьей схемы срав)яения соединен с третьим выходом блока ввода. Выход третьей схемы 34 сравнения соединен с входом генератора 13 импульсов. .. Конструктивно устройство вычисления коэффициентов полинома выполнено в виДе элемента АСУ,. а также как автономное устройство, представляющее собой спецвычислитель. Устройство работает следующим образом. Перед началом работы сигналом с синаронизатора АСУ устройство приводится в исходное состояние в блоке 2 памяти переменных, в блоке 11 памяти (результатов 7) во все ячейки записываются нуо96хш, в блоке 7 памяти реэупьтатов во вторую ячейку записывается единица, а во все остальные ячейки - нули, счетчик 25 циклов и счетчик 3 переменных устанавливаются в нуль, в блоке 18 счетчиков адреса памяти результатов счетчик 7 управления блоком памяти результатов, пред назначенный для реализации операции умножения с использованием переменной У устанавливается в нуль, а счетчик 7 управления блоком-памяти результатов, пред назначенный для реализации операции умножения с использованием переменной устанавливается в единицу, в регистр 28 счетчика циклов записываемся цифра 2 и триггер узла 14 формирования первого импульса последовательности устанав ливается в 1. Через блок 1 ввода в блок 2 памяуи переменных вводятся значения X и 5, Од новременно на счетчике 3 переменных устанавливается их число. Через блок 1 ввода в третий блок сравнения уводится заданное значение порога -минимальное отличное от нуля число, По окончании ввода переменных включается генератор 13. Импульсы с герератора 13 поступают на узел 14 формирования первого импульса последовательности. Этот элемент пропускает только один первый импульс, который, проходя через элементы ИЛИ 15, И 4 и ИЛИ 5, копирует состояние первых ячеек блока 2 памяти переменных в блоке G умножения. На блок 6 умножения поступает также информация из первой и второй ячеек блока 7 памяти результатов, после чего выполняются операции умножения и Ct гаеС Л q,2.- содержимое соответствуюших ячеек блока 7 памяти результатов , X., и V., - содержимое первых ячеек блока 2 памяти переменных. Этот же импульс через элемент 16 задержки и элемент И 8 пересылает результат из блока 6 умножения на сумматор 9, где производится сложение результатов, полученных в блоке 6 умножения, и через элемент 17 задержки и элемент И 10 производится копирование результата сум-мирования на блок 1.1 буферной памяти. Этот же импульс поступает на блок 18 счетчиков адреса памяти результатов и через элемент ИЛИ 19 и элемент 24 задержки на счетчик 25 циклов, а через элемент 32 задержки, элементы И 23 и ИЛИ 5 на копирование состояния ячеек на блок 6 умножения, причем с блока 7 памяти результатов поступает информация второй 5lO и третьей ячеек и выполняются операции V/tQ - ® производится суммирование -и запись результата суммирования в блок 11 буферной памяти. Импульс копирования результата сумлдарования на блок 11 буферной памяти добавляет единицу к счетчику 25 циклов. Блок 26 сравнения выдает сигнал сравнения, который разрешает элементу И 32 разрешения прохождения импупьсов пропустить импульс с генератора 13. Этот импульс вычитает из счетчика 3 перемен-. ных единицу, и, проходя через элементы ИЛИ 15 и 19 и элемент 24 задержки, п эибавляет единицу к счетчику 25 циклов, а также через элемент И 21 разрешения копирования,- элемент 27 задержки, а также записывает, новое состояние счетчика 25 циклов на регистр 28 счетчика. Этот же импульс нереп элемент 30 задержки устанавт1вает в нуль счетчик 25 циклов и счетчики 18 блока счетчи- . ка адреса памяти результатов и через элемент И 12 копирует информацию из блока 11 буферной памяти на блок 7 памяти результатов. Тот же импульс со схемы 32 разрешения прохождения -через схему ИЛИ 15 копирует содержимое ячеек 1 и V/j из блока 2 буферной памяти чеР® элементы И 4 и ИЛИ 5 на блок 6 умножения, где выполняются операции умножения Лл О, и х/,.,,Результат умножения пересылается на сумматор 9 и после суммирования в блок 11 буферной памяти. Из блока 7 памяти результата на втоРОЙ блок сравнения 33 поступают значения а и С|,2(в обшем случае Cly, и а, .Л если выполняется условие Ol2 а (в обшем случае (Лцк, СС1,K--f}, то значение .) поступает на третий блок 34 сравнения, где сравнивается с заранее заданной величиной . При а СС1цк.)ретий блок 34 сравнения выдает сигнал на генератор 13 импульсов, останавливаю й работу устройства. Если не выполняются описанные выше условия на блоках 33 и 34 сравнения, то работа устройства продолжается по описанному агаоритму, но число циклов на единицу больше, т.е. три.Затем происходит разрешение прохождения следую-, щего импульса с генератора 13, и рабо-та устройства повторяется, причем при каждом следующем повторении число циклов увеличивается на единицу до тех пор, пока не выполнятся условия второго 33 и третьего 34 блоков сравнения или пока счетчик 3 переменных не установится в нуль.

12960835 ,11

После этого происходит запрещениепась теоретически и методом математипрохожДения импульса с генератора 13ческого моделирования,

и вычисления заканчиваются.Результаты теоретического расчета и

Результат вычисления коэффициентов.математического моделирования сведены

.,,-,i,..,,t,.,-ij 5 в таблицу, на которой показан харак--..тер изменения коэффициентов (

-Ori ,,и 0; CJoo-; 1, 2, .... Vi ) для различных ц при .

l-o,i,...,vT, a.:iO-я/xtv- s0,012...

передается в блок 31 регистрации.Изобретение позволяет сократить вреОценка технико-экономического эффек- мя вычисления коэффициентов полинома та от использования изобретения проводи- на 1О-35%.

значениях вероятностей Р 0,01, 0,011, 1596 Формула изобретения Устройство для вычисления коэффициентов полинома, содержащее блок ввода блок памяти переменных, счетчик переменных, шерть элементов И, элемент И разрешения копирования, три элемента ИЛИ, блок умножения, блок памяти реауль тата, сумматор, блок буферной памяти, , генератор импульсов, формирователь первого импульса, семь элементов задержки, блок счетчиков адреса памяти результата, счетчик циклов, первый блок сравнения, регистр состояния счетчика циклов, элемент НЕ и блок регистрации, причем первый выход блока ввода соединен с установочными входами счетчика переменных, а второй выход - с информационным входом блока йамяти переменных, выход ко- торого соединен с первым входом первого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого подключен к первому входу блока умножения, выход которого соединен с первым входом второго элемента И, выход которого соединен с входом сум матора, выход которого соединен с первым входом третьего элемента И, выход которого соединен с входом блокд буферной памяти и первым входом второго элемента ИЛИ, выход которого через первый элемент задержки подключен к первому входу четвертого элемента И, а через второй элемент задержки к счетному входу счетчика циклов, выходы которого подключены к первой группе входов первого блока сравнения и первому входу элемента И разрешения копирования, выход которого через третий элемент задержки соединен с входом регистра состояния счетчика циклов, выходы которого соединены с Второй группой входов первого блока сравнения, выход которого через элемент НЕ подключен к второму входу четвертого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, выход генератора импульсов соединен с входом форм ирователя перво- по импульса, вьисод которого соединен с nepBbiM входом третьего элемента ИЛИ, выход которого через четвертый элемент задержки подключен к второму входу вто516рого элемента И и к входу пятого элемента задержки, выход которого соединен с вторым входом третьего элемента И, выход третьего элемента ИЛИ соединен с вторым входом первого элемента И, с вторым входом второго элемента ИЛИ и через шестой элемент задержки с вторым входом элемента И разрешения копирова ния, выход которого соединен через седьмой элемент задержки с входом установки нуля счетчика циклов, с первым входом пятого элемента И и первым вхо- дом блока счетчиков адреса памяти результата, выходы которого подключены к адресным входам блока памяти резупътата, второй вход блока счетчиков адреса памяти результата соединен с выходом третьего элемента И, второй вход пятого элемента И соединен с выходом бло- ка буферной памяти, а выход - с информационным входом блока памяти результата, выходы которого соединены с вторым входом блока умножения и входом блока регистрации, выход первого бпока сравнения соединен с первым входом шестого элемента И и третьим входом элемента И разрешения копирования, выходы счетчика переменных соединены с адресными входами блока памяти переменных и вторым входом шестого элемента И, третий вход которого подключен к выходу генератора, а выход соединен с вторым вхоДом третьего элемента ИДИ и вычитаюшим входом счетчика переменных, отличающееся тем, что, с целью повышения производительности, в него введены второй и третий блоки сравнения, причем вход второго бпока сравнения соединен с третьим выходом блока памяти результата, выход второго блока сравнения - с первым входом третьего блока сравнения, второй вход которого соединен с третьим выходом блока ввода, а выход - с входом генератора импульсов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 6О3998, кл. Q Об F 15/31, 1977. 2.Авторское свидетельство СССР Кз 734714, кл. G Об F 15/31, 1978 (прототип).

Авторы

Даты

1982-09-23—Публикация

1980-12-15—Подача