Изобретение относится к вычислительной технике и может быть использовано для обработки массивов данных при поисках новых месторождений нефти и газа.

Цель изобретения - повьшюние производительности устройства.

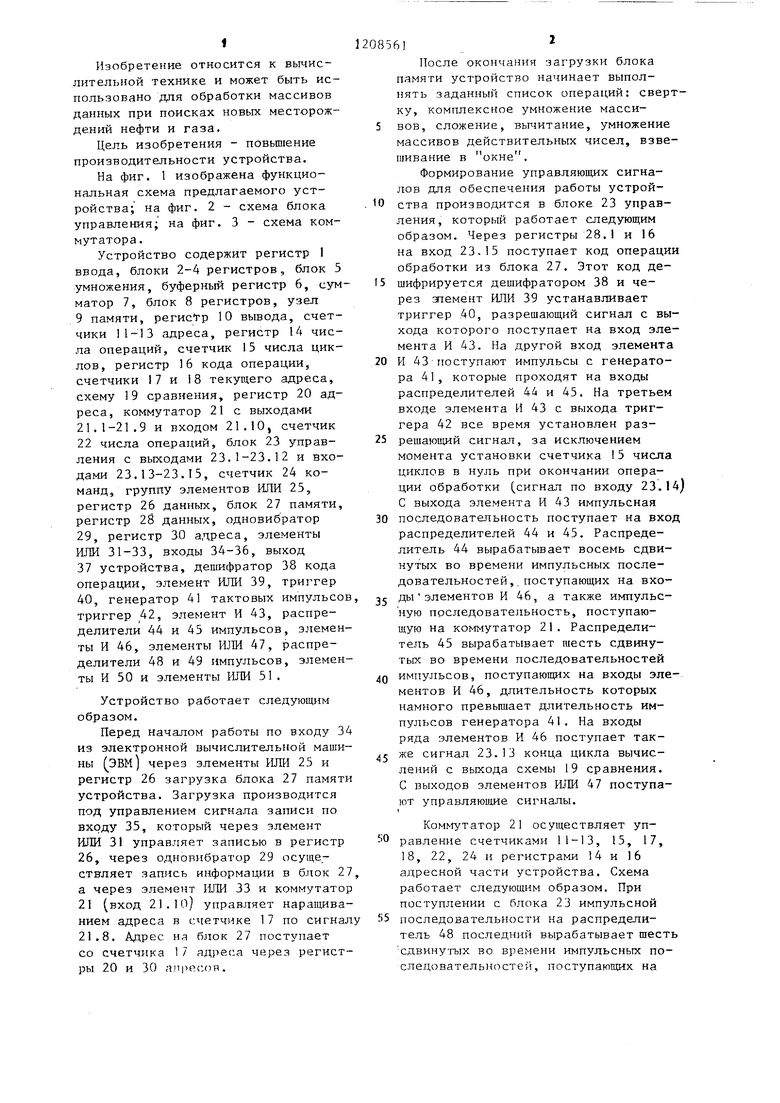

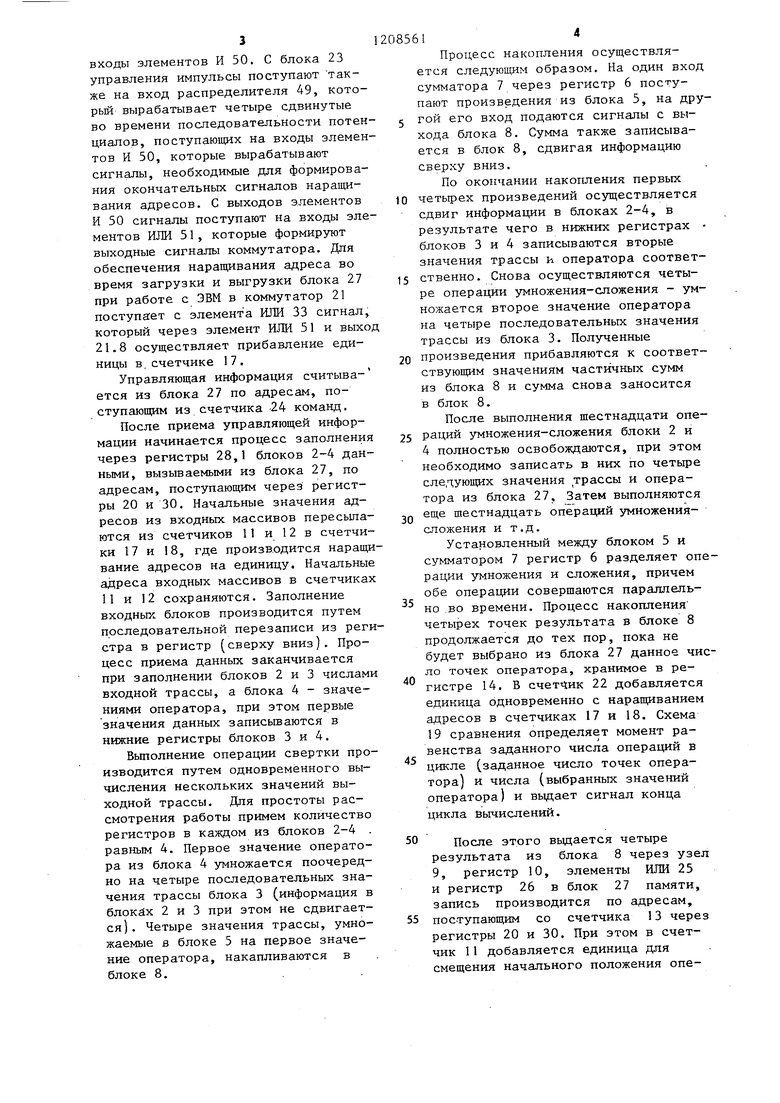

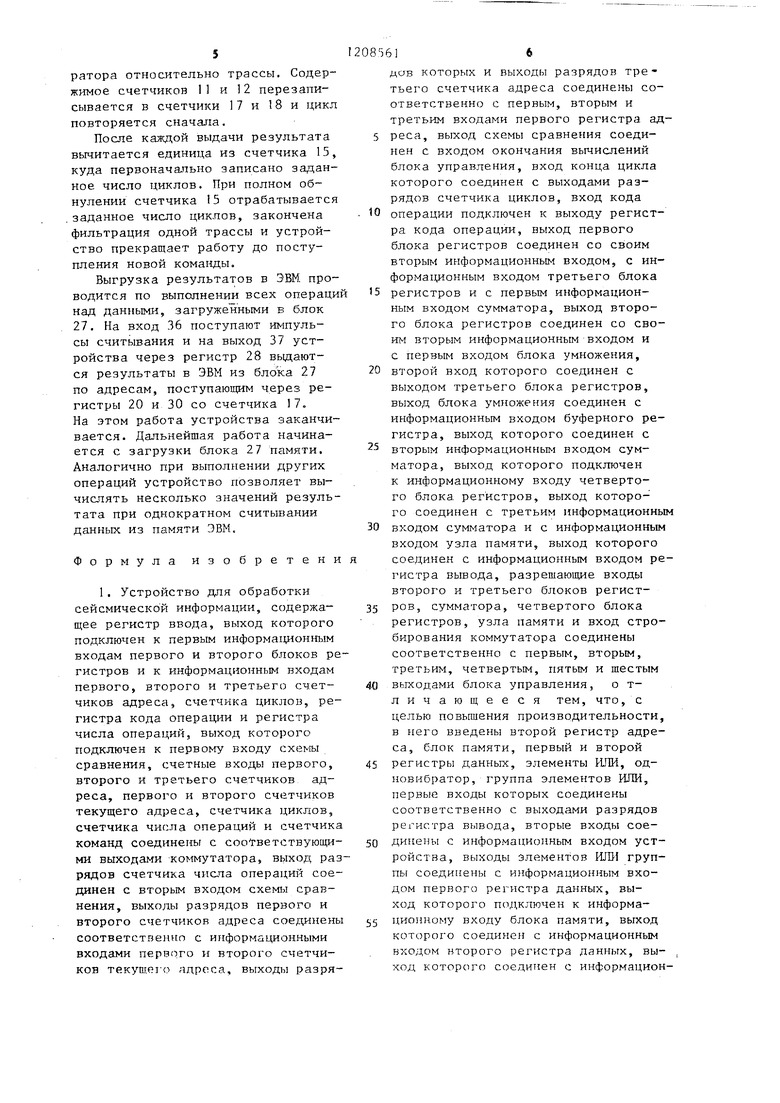

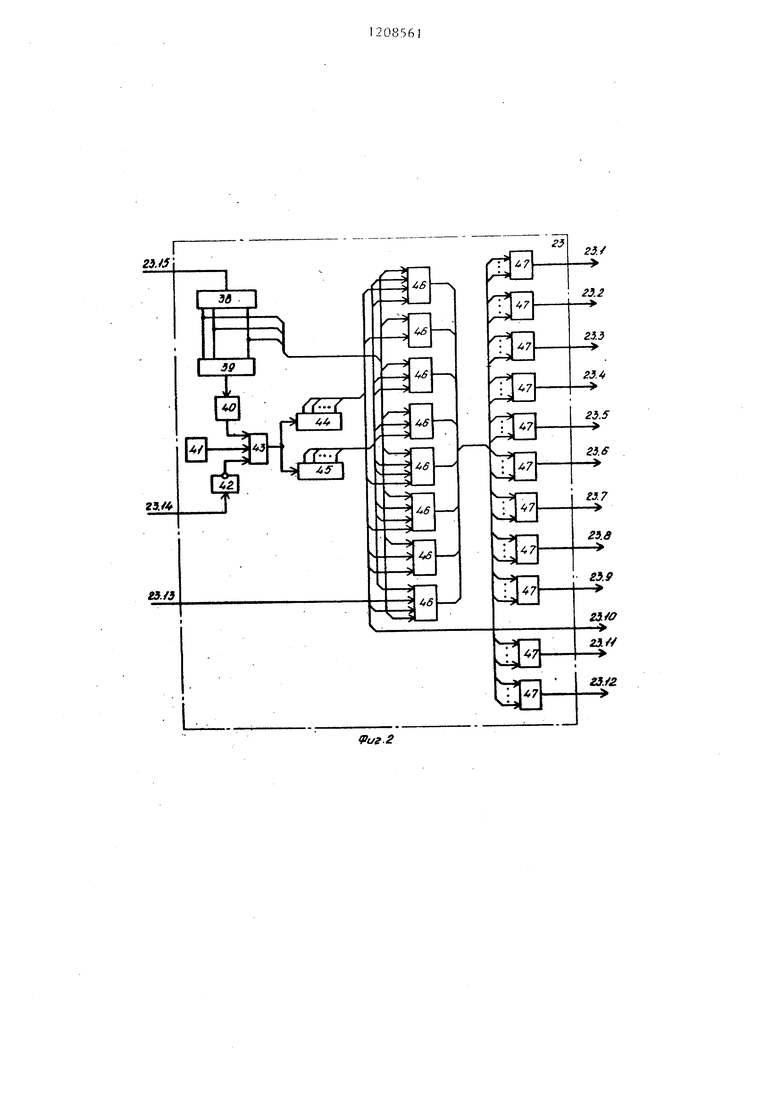

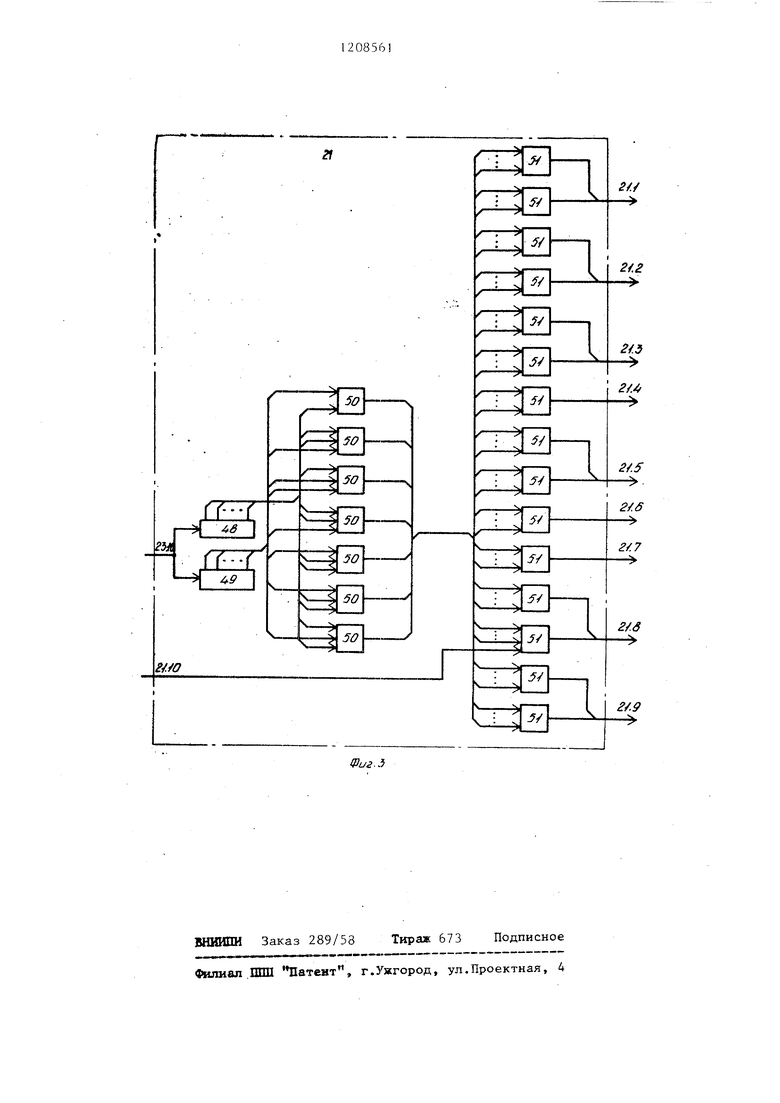

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 - схема блока управления; на фиг. 3 - схема коммутатора.

Устройство содержит регистр I ввода, блоки 2-4 регистров, блок 5 умножения, буферный регистр 6, сумматор 7, блок 8 регистров, узел 9 памяти, регистр 10 вывода, счетчики 11-13 адреса, регистр 14 числа операций, счетчик 15 числа циклов, регистр 16 кода операции, счетчики 17 и 18 текущего адреса, схему 19 сравнения, регистр 20 адреса, коммутатор 21 с выходами 21.1-21.9 и входом 21.10, счетчик 22 числа операций, блок 23 управления с выходами 23.1-23.12 и входами 23.13-23.15, счетчик 24 команд, группу элементов ИЛИ 25 регистр 26 данных, блок 27 памяти, регистр 28 данных, одновибратор 29, регистр 30 адреса, элементы ИЛИ 31-33, входы 34-36, выход 37 устройства, дешифратор 38 кода операции, элемент ИЛИ 39, триггер 40, генератор 41 тактовых импульсов триггер 42, элемент И 43, распределители 44 и 45 импульсов, элементы И 46, элементы ИЛИ 47, распределители 48 и 49 импульсов, элементы И 50 и элементы ИЛИ 51.

Устройство работает следующим образом.

Перед началом работы по входу 34 из электронной вычислительной машины (ЭВМ) через элементы ИЛИ 25 и регистр 26 загрузка блока 27 памяти устройства. Загрузка производится под управлением сигнала записи по входу 35, который через элемент ИЛИ 31 управляет записью в регистр 26, через одновибратор 29 осуществляет запись информации в блок 27 а через элемент ИЛИ 33 и коммутатор 21 (вход 21.1 о) управляет наращиванием адреса в счетчике 17 по сигнал 21.8. Адрес на блок 27 поступает со счетчика 17 адреса через регистры 20 и 30 апресов.

2085612

После окончания загрузки блока памяти устройство начинает выполнять заданный список операций: свертку, комплексное умножение масси5 ВОВ, сложение, вычитание, умножение массивов действительных чисел, взвешивание в окне.

Формирование управляющих сигналов для обеспечения работы устрой- . О ства производится в блоке 23 управления, которьш работает следующим образом. Через регистры 28. и 16 на вход 23,15 поступает код операции обработки из блока 27. Этот код деtS шифрируется дешифратором 38 и через зтемент ИЛИ 39 устанавливает триггер 40, разрешающий сигнал с выхода которого поступает на вход элемента И 43. На другой вход элемента

20 И 43-поступают импульсы с генератора 41, которые проходят на входы распределителей 44 и 45. На третьем входе элемента И 43 с выхода триггера 42 все время установлен раз25 решающий сигнал, за исключением

момента установки счетчика 15 числа циклов в нуль при окончании операции обработки (сигнал по входу 23.14) С вьЕХОда элемента И 43 импульсная

30 последовательность поступает на вход распределителей 44 и 45. Распределитель 44 вырабатывает восемь сдви- нут ых во времени импульсных последовательностей,. поступающих на вхо35 ды элементов И 46, а также импульсную последовательность, поступающую на коммутатор 21. Распределитель 45 вырабатывает шесть сдвинутых во времени последовательностей

40 импульсов, поступающих на входы элементов И 46, длительность которых намного превышает длительность импульсов генератора 41. На входы ряда элементов И 46 поступает же сигнал 23.13 конца цикла вычислений с выхода схемы 19 сравнения. С выходов элементов ИЛИ 47 поступают управляющие сигналы.

Коммутатор 21 осуществляет уп- - 0 равление счетчиками 11-13, 15, 17, 18, 22, 24 и регистрами 14 и 16 адресной части устройства. Схема работает следующим образом. При поступлении с блока 23 импульсной 5 последовательности на распределитель 48 последний вырабатывает шесть сдвинутых во времени импульсных последовательностей, поступающих на

3

входы элементов И 50. С блока 23 управления импульсы поступают также на вход распределителя 49, кото- рьш вырабатывает четыре сдвинутые во времени последовательности потенциалов, поступающих на входы элементов И 50, которые вырабатывают сигналы, необходимые для формирования окончательных сигналов наращивания адресов. С выходов элементов И 50 сигналы поступают на входы элементов ИЛИ 51, которые формируют выходные сигналы коммутатора. Для обеспечения наращивания адреса во время загрузки и выгрузки блока 27 при работе с ЭВМ в коммутатор 21 поступа:ет с элемента ИЛИ 33 сигнал, который через элемент ИЛИ 51 и выхо 21.8 осуществляет прибавление единицы в. счетчике 17.

Управляющая информация считыва- ется из блока 27 по адресам, поступающим из счетчика -24 команд.

После приема управляющей информации начинается процесс заполнения через регистры 28,1 блоков 2-4 данными, вызываемыми из блока 27, по адресам, поступающим через регистры 20 и 30. Начальные значения адресов из входных массивов пересыпаются из счетчиков 11 и 12 в счетчики 17 и 18, где производится наращивание адресов на единицу. Начальные aja;peca входных массивов в счетчиках 11 и 12 сохраняются. Заполнение входньк блоков производится путем последовательной перезаписи из регистра в регистр (сверху вниз). Процесс приема данных заканчивается при заполнении блоков 2 и 3 числами входной трассы, а блока 4 - значениями оператора, при этом первые значения данных записьшаются в нижние регистры блоков 3 и 4.

Вьтолнение операции свертки производится путем одновременного вычисления нескольких значений выходной трассы. Дпя простоты рассмотрения работы примем количество регистров в каждом из блоков 2-4 . равным 4. Первое значение оператора из блока 4 умножается поочередно на четыре последовательных значения трассы блока 3 (информация в блокйх 2 и 3 при этом не сдвигается) . Четыре значения трассы, умножаемые в блоке 5 на первое значение оператора, накапливаются в блоке 8.. .

08561

Процесс накопления осуществляется следующим образом. На один вход сумматора 7 через регистр 6 поступают произведения из блока 5, на дру- 5 гой его вход подаются сигналы с выхода блока 8. Сумма также записывается в блок 8, сдвигая информацию сверху вниз.

По окончании накопления первых

10 четьфех произведений осуществляется сдвиг информации в блоках 2-4, в результате чего в нижних регистрах блоков 3 и 4 записываются вторые значения трассы и оператора соответ15 ственно. Снова осуществляются четыре операции умножения-сложения - умножается второе значение оператора на четыре последовательных значения трассы из блока 3. Полученные

20 произведения прибавляются к соответствующим значениям частичных сумм из блока 8 и сумма снова заносится в блок 8.

После выполнения щестнадцати опе25 раций умножения-сложения блоки 2 и 4 полностью освобождаются, при этом необходимо записать в них по четыре следующих значения трассы и оператора из блока 27, Затем выполняются

2Q еще шестнадцать операций з ножения- сложения и т.д.

Установленный между блоком 5 и сумматором 7 регистр 6 разделяет операции умножения и сложения, причем обе операции совершаются параллельно во времени. Процесс накопления четырех точек результата в блоке 8 продолжается до тех пор, пока не будет выбрано из блока 27 данное число точек оператора, хранимое в регистре 14. В счетчик 22 добавляется единица одновременно с нарапщванием адресов в счетчиках 17 и 18. Схема 19 сравнения определяет момент равенства заданного числа операций в цикле (заданное число точек оператора) и числа (выбранных значений оператора) и выдает сигнал конца цикла Вычислений.

50 После этого выдается четыре

результата из блока 8 через узел 9, регистр 10, элементы ИЛИ 25 и регистр 26 в блок 27 памяти, запись производится по адресам,

55 поступающим со счетчика 13 через регистры 20 и 30. При этом в счетчик 11 добавляется единица для смещения начального положения опе35

40

атора относительно трассы. Содеримое счетчиков 11 и 12 перезапиывается в счетчики 17 и 18 и цикл овторяется сначала.

После каждой выдачи результата ычитается единица из счетчика 15, уда первоначально записано заданое число циклов. При полном обулении счетчика 15 отрабатывается заданное число циклов, закончена ильтрация одной трассы и устройство прекращает работу до поступления новой команды.

Выгрузка результатов в ЭВМ проводится по выполнении всех операций над данными, загруженными в блок 27. На вход 36 поступают импульсы считывания и на выход 37 устройства через регистр 28 выдаются результаты в ЭВМ из блока 27 по адресам, поступающим через регистры 20 и 30 со счетчика 17. На этом работа устройства заканчивается. Дальнейшая работа начинается с загрузки блока 27 пгшяти. Аналогично при выполнении других операций устройство позволяет вычислять несколько значений результата при однократном считывании данных из памяти ЭВМ.

Формула изобретения

1. Устройство для обработки сейсмической информации, содержащее регистр ввода, выход которого подключен к первым информагщонным входам первого и второго блоков регистров и к информационным входам первого, второго и третьего счетчиков адреса, счетчика циклов, регистра кода операции и регистра числа операций, выход которого подключен к первому входу схемы сравнения, счетные входы первого, второго И третьего счетчиков адреса, первого и второго счетчиков текущего адреса, счетчика циклов, счетчика числа операций и счетчика команд соединены с соответствующими выходами коммутатора, выход разрядов счетчика числа операций соединен с вторым входом схемы сравнения, выходы разрядов первого и второго счетчиков адреса соедешены соответственно с информационными входами первого и второго счетчиков текуш,е1 о адреса, выходы разря0

0

.5

0

5

S

дон которых и выходы разрядов третьего счетчика адреса соединены соответственно с первым, вторым и третьим входами первого регистра ад5 реса, выход схемы сравнения соединен с входом окончания вычислений блока управления, вход конца цикла которого соединен с выходами разрядов счетчика циклов, вход кода операции подключен к выходу регистра кода операции, выход первого блока регистров соединен со своим вторым информационным входом, с ин- форма1ц{онным входом третьего блока

5 регистров и с первым информационным входом сумматора, выход второго блока регистров соединен со своим вторым информационным входом и с первым входом блока умножения, второй вход которого соединен с выходом третьего блока регистров, выход блока умножения соединен с информационным входом буферного регистра, выход которого соединен с вторым информационным входом сумматора, выход которого подключен к информационному входу четвертого блока регистров, выход которого соединен с третьим информационным входом сумматора и с информаи ионным входом узла памяти, выход которого соединен с информационным входом регистра вывода, разрешающие входы второго и третьего блоков регистров, сумматора, четвертого блока регистров, узла памяти и вход стро- бирования коммутатора соединены соответственно с первым, вторым, третьим, четвертьгм, пятым и шестым выходами блока управления, о т- личающееся тем, что, с целью повышения производительности, в него введены второй регистр адреса, блок памяти, первый н второй регистры данных, элементы ИЛИ, од- новнбратор, группа элементов ИЛИ, первые входы которых соединены соответственно с выходами разрядов регистра вывода, вторые входы соединены с информационным входом устройства, выходы элементов ШШ группы соединены с информационным входом первого регистра данных, выход которого подключен к информа- ционноь у входу блока памяти, выход которого соединен с информационным входом второго регистра данных, выход; которого соединен с информацион0

5

ным входом регистра ввода и с информационным выходог устройства, первые входы первого и второго элементов ИЛИ соединены с входом раэр шения записи устройства, второй вход второго элемента ИЛИ и первый вход третьего элемента ИЛИ соединены с входом разрешения считьша- ния устройства, выход первого элемента ИЛИ соединен с разрешающим входом первого регистра данных и через одновибратор - с входом разрешения записи блока памяти, вторы входы первого и третьего элементов ИЛИ соединены соответственно с сед мым и восьмым выходами блока управления, выход третьего элемента ИЛИ соединен с разрешающим входом второго регистра данных, выход второго элемента ИЛИ соединен с разрешающим входом второго регистра а реса и с разрешающим входом коммутатора, выходы разрядов первого регистра адреса соединены с информационным входом второго регистра адреса, выходы разрядов которого , подключены к адресному входу блока памяти, разрешающие входы регистра числа операций и регистра кода операции соединены с соответствующими выходами коммутатора, разрешающие входы первого блока регистров, регистра ввода, буферного регистра и регистра вывода соединены соответственно с девятым, десятым, одиннадцатым и двенадцатым выходами блока управления, выходы разрядов счетчика команд соединены с четвертым входом первого регистра адреса.

2. Устройство по п. 1, отличающееся тем, что блок уп2085618

равления содержит генератор тактовых импульсов, два распределителя импульсов, девять элементов И, двенадцать элементов ШШ, два триггера 5 и дешифратор кода операций, вход которого является входом кода операции блока, выходы дешифратора кода операции соединены с входами первого элемента ИЛИ и с первыми 10 входами с первого по восьмой элементов И, выходы которых подключены соответственно к входам элементов ИЛИ с второго по двенадцатый, выходы которых являются с первого

15 по пятый -и с седьмого по двенадцатый выходами блока, выход первого элемента ИЛИ соединен с входом первого триггера, вход второго триггера является входом сигнала 20 конца цикла блока, входы девятого элемента И соединены соответственно с выходами первого триггера, генератора тактовых импульсов и второго триггера, выход девятого эле- 25 мента И подключен к входам первого и второго распределителей импульсов, выходы первого из которых подключены соответственно к вторым входам первого, второго, пятого, шестого, 30 седьмого и восьмого элементов И, к третьему входу седьмого элемента И и к шестому выходу блока, выходы второго распределителя импульсов подключены соответственно к второму 35 и третьему входам третьего и четвертого элементов И, к третьим и четвертым входам первого, пятого и шестого элементов Ник третьему входу восьмого элемента И, четвер- 40 тый вход которого является входом сигнала окончания вычислений бло - ка.

д6

ВНИИПИ Заказ 289/58 Тираж. 673 Подписное Филиал .ШШ Патент, г.Ужгород, ул.Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования управляющей информации при обработке данных сейсмических колебаний | 1981 |

|

SU1000766A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Многофункциональный цифровой коррелометр | 1983 |

|

SU1096656A1 |

| Устройство для отладки программ | 1983 |

|

SU1290334A1 |

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Устройство для моделирования процессов изменения параметров электронных схем | 1980 |

|

SU924712A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство для вывода графической информации | 1989 |

|

SU1644208A1 |

| Устройство для отладки программ | 1983 |

|

SU1322290A2 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

Изобретение относится к вычислительной технике и может использоваться при поиске месторождений нефти и газа. Целью изобретения является повьшение производительности. Устройство содержит регистр ввода, четыре блока регистров, блок умножения, буферный регистр, узел памяти, регистр вывода, счетчики адреса, регистр числа операций, счетчик циклов, регистр кода операции, два счетчика текущего адреса, схему сравне ния, регистры адреса, коммутатор, счетчик числа операций, блок управления, счетчик команд, группу элементов ИЛИ, регистры данных , блок памяти, одновибратор, элементы ШШ. 3 ил. о S (Л

| Устройство для обработки сейсмических данных | 1977 |

|

SU744591A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования управляющей информации при обработке данных сейсмических колебаний | 1981 |

|

SU1000766A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-01-30—Публикация

1984-08-10—Подача