Изобретение относится к дискретной автоматике и вычислительной технике и может быть использовано при разработке арифметических устройств.

. Известен реверсивный регистр сдвига, содержащий ячейки памяти, каждая из которых состоит из триггера, элемента И-ИЛИ-НЕ, и шины управления сдвигом вправо и влево 1.

Недостатком данного регистра является невысокое быстродействие при осуществлении сдвига информации на число разрядов больше одного.

Наиболее близким к изобретению по технической сущности является реверсивный регистр сдвига, который содержит ячейки памяти, два элемента задержки, два элемента ИЛИ, элемент И-ИЛИ, шины управления.Ячейка памяти состоит из триггера и элемента И-ИЛИ-НЕ, выход которого под- , ключен к одному из входов триггера данной ячейки памяти, первый вход элемента И-ИЛИ-НЕ каждой ячейки памяти соединен с выходом триггера предыдущей ячейки памяти, второй -вход элемента И-ИЛИ-НЕ каждой ячейки памяти подк.пючен к выходу триггера последующей ячейки памяти., выход элемента И-ИЛИ подключен к другому

входу триггера каждой ячейки памяти, выходы элементов ИЛИ соединены с третьим и четвертым входами элемента И-ИЛИ-НЕ каждой ячейки памяти, первый и второй входы элемента И-ИЛИ подсоединены к первым выходам элементов задержки, вхо.цы которых соединены с шинами управления сдвигом, вторые ВЫХО.ДЫ элементов задержки

10 подключены соответственно к первым входам элементов ИЛИ, вторые входы которых соединены с третьим и четвертым входами элемента И-ИЛИ и шинами управления сдвигом {2.

15

Недостатком известного реверсивного регистра сдвига является низкое быстродействие при осуществлении сдвига информации на число разрядов больше одного, так как при сдвиге 20 информации на N разрядов необходимо подать последовательно N управляющих сигналов.

Целью изобретения является повышение быстродействия устройства.

25

Поставленная цель достигается тем, то в реверсивный регистр сдвига, содержащий ячейки памяти, каждая из которых состоит из триггера и элемента И-ИЛИ-НЕ, выход которого 30 соединен с первым входом триггера.

первый и второй элементы задержки, входы которых соединены соответственно с шинами управления сдвигом вправо и влево, первый и второй элементы ИЛИ, первые входы которых соединены с первыми выходами элементов задержки, элемент И-ИЛИ, первый и второй входы которого соединены с вторыми выходами элементов задержки, третий вход элемента И-ИЛИ соединен с вторым входом первого элемента ИЛИ и с шиной управления сдвигом вправо, четвертый вход элемента И-ИЛИ соединен с вторым входом второго элемента ИЛИ и с шиной управления сдвигом влево, выход элемента И-ИЛИ соединен с вторыми . входами триггеров ячеек памяти, выход триггера каждой ячейки памяти соединен с первым входом элемента И-ИЛИ-НЕ последующей ячейки памяти, и тактовые шины, введен деищфратор, входы которого соединены с тактовыми шинами, выходы дешифратора подключены к вторым, третьим, четвертым и пятым входам элементов И-ИЛИ-НЕ ячеек памяти, шестые входы элементов И-ИЯИ-НЕ ячеек памяти соединены с выходом первого элемента ИЛИ, выход второго элемента ИЛИ соединен с седьмыми-входами элеМентов И-ИЛИ-НЕ ячеек памяти, выход триггера каждой ячейки памяти соединен с восьмыми входами элементов И-ИЛИ-НЕ ячеек памяти, кроме данной ячейки памяти.. ,

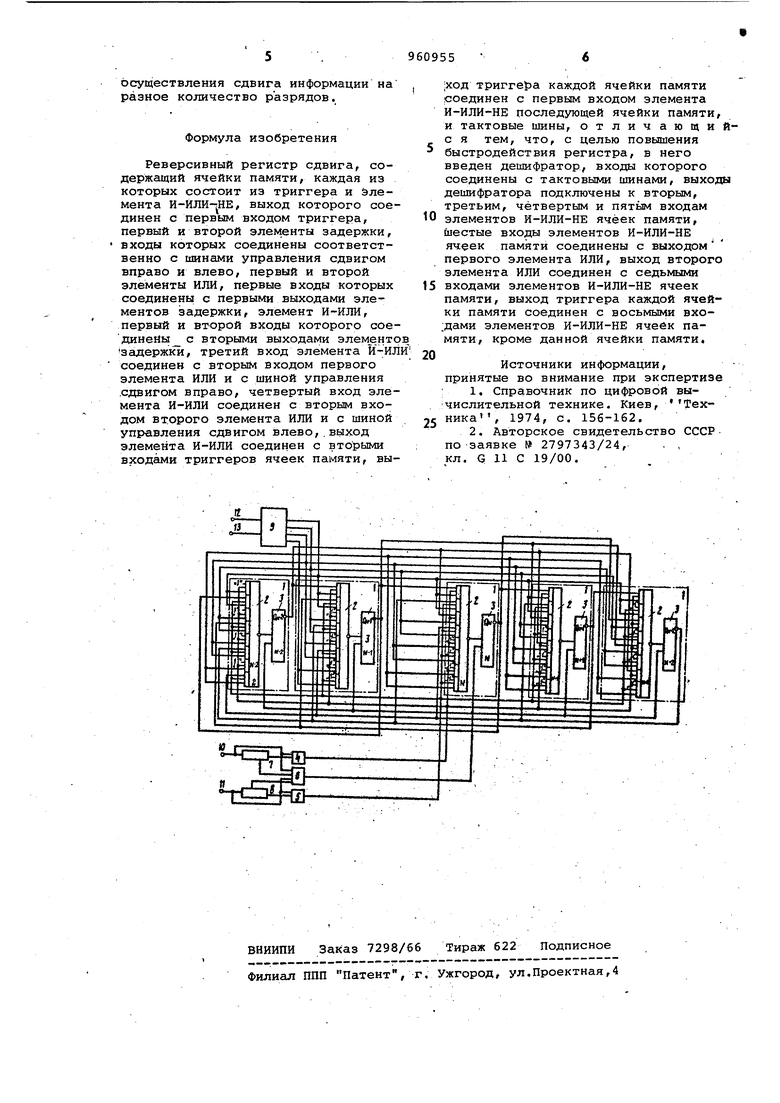

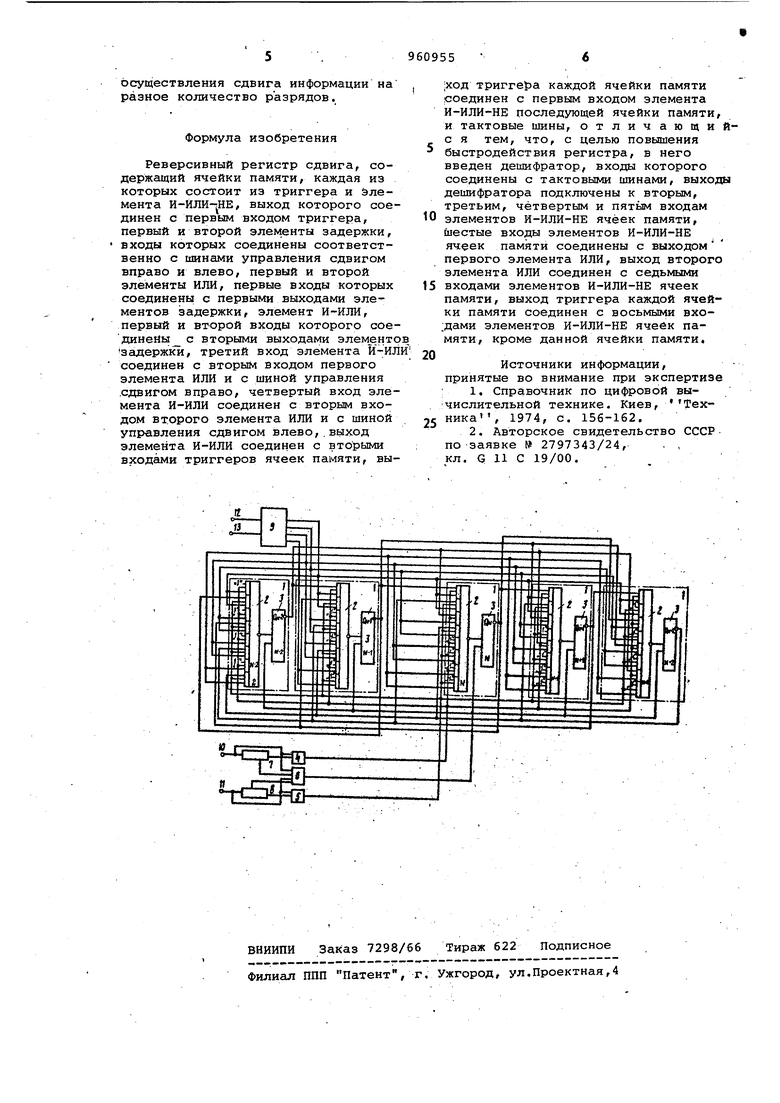

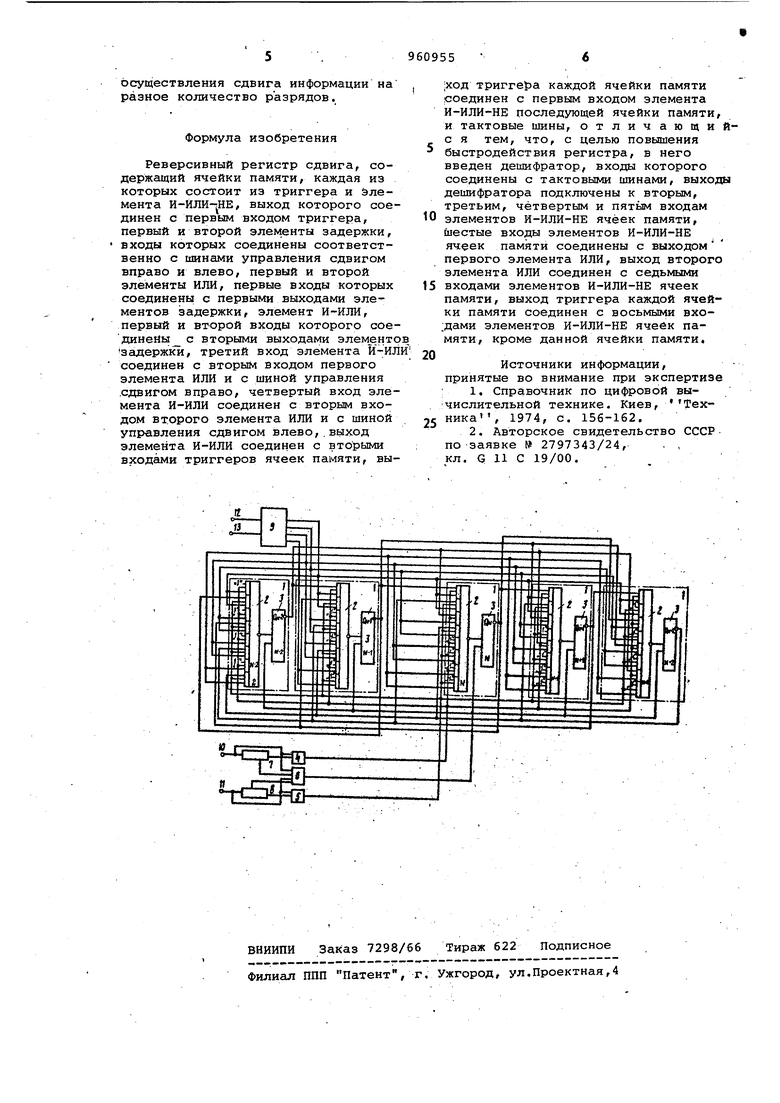

На чертеже изображена функциональная схема предложенного устройства.

Устройство содержит ячейки 1 памяти, каждая из которых состоит из элемента И-ИЛИ-НЕ 2 и триггера 3, элементы ИЛИ 4 и 5, элемент И-ИЛИ б, элементы 7 и .8 задержки, дешифраТор .9, шины 10 и 11 управления сдвигом вправо и влево, тактовые шины 12 и 13.

Предложенный регистр сдвига работает следующим образом.

Сдвиг информации вправо (влево) в реверсивном регистре двига происходит по переднему фронту сигнала, поступающего с выхода элемента И-ИЛИ б при наличии разрешающего (логической единицы) сигнала с выхода элемента ИЛИ 5. Одновременное наличие разрешающего сигнала на выходах элементов ИЛИ 4 и ИЛИ 5 запрещено.

Для того, чтобы информация ретистра не разрушалась по окончанию сдвига информации необходимо чтобы сигнал с выхода элемента И-ИЛИ б оканчивался раньше, чем разрешающий сигнал на выходе элемента ИЛИ 4.

Сдвиг информации вправо (влево) на любое количество разрядов определяется кодом, задаваемым на шинах 12 и.13.

Первый вариант, когда на шинах 12 иДЗ задан код 0000. При этом на первом выходе дешифратора 9 присутствует разрешающий сигнал, поступаюощй йа вторую группу входов элемента И-ИЛИ-НЕ 2 каждой ячейки 1 памяти. На остальных выходах, дешиф-, ратора 9 присутствует запрещающий

0 (логический нуль) сигнал.

При поступлении импульсного сигнала, например, по шине 10 передний ФРОНТ данного сигнала на выходах элемента 7 задержки появлялся бы с

5 задержкой времени t и t. На выходе элемента ИЛИ 4 передний фронт этого сигнала возникал бы без задериски, а на выходе элемента И-ИЛИ б с задержкой t. По окончанию данного импульсного сигнала его задний фронт исчезает с задержкой времени t.и ti. На выходе элемента И-ИЛИ 6 задний фронт такого сигнала исчезает без задержки, а на выходе

элемента ИЛИ 4 - с задержкой t.

Аналогично происходит формирова-ние сигналов при поступлении импульсного сигнала по шине 11.

При задании на шинах 12 и 13 кода 0000 и при поступлении импульсного

0 сигнала на шины 10 (11) информация с предыдущих (последующих) триггеров 3 через элементы ИЛИ-НЕ 2 переписывается в последующие (предыдущие) триггеры 3, что соответствует сдвигу

5 информации в регистре вправо (влево) на один разряд.

При поступлении кода 0100 на шины 12 и 13 на третьем выходе дешифратора 9 присутствует разрешающий

0 сигнал, поступающий на вторую группу входов элемента И-ИЛИ-НЕ 2 каждой ячейки памяти. При поступлении импульсного сигнала; на шины 10 (11) информация в регистре запишется со

5 сдвигом вправо (влево) на три разряда .

Аналогично, при задании на ttffiiHax 12 и 13 кода 1001, 0010 и т.п., осуществляется сдвиг информации на

десять, пять и т.п. разрядов.

Таким образом, введение дешифратора и новые связи между элементами регистра позволяет производить . сдвиг информации в регистре на N разрядов. Информация сдвигается на N разрядов, минуя все промежуточные N-1 разряды путем подачи управляющего кода и при поступлении одного импульсного сигнала на шины сдвига.

9 Тем самым повышается быстродействие сдвига информации в N раз.

Использование изобретения также позволяет повысить кoэф ициeJHT унификации изделия за счет использования однотипных устройств для

осуществления сдвига информации на , разное количество разрядов.

Формула изобретения

Реверсивный регистр сдвига, содержащий ячейки памяти, каждая из которых состоит из триггера и элемента И-ЙЛИ-,НЕ, выход которого соединен с первым входом триггера, первый и второй элементы задержки, входы которых соединены соответственно с шинами управления сдвигом вправо и влево, первый и второй элементы ИЛИ, первые входы которых соединены с первыми выходами элементов задержки, элемент И-ИЛИ, первый и второй входы которого соединеНы с вторыми выходами .нто задержкТ, третий вход элемента И-ИЛ соединен с вторым входом первого элемента ИЛИ и с шиной управления сдвигом вправо, четвертый вход элемента И-ИЛИ соединен с вторым входом второго элемента ИЛИ и с шиной управления сдвигом влево,.выход элемента И-ИЛИ соединен с вторыми входами триггеров ячеек памяти, вы:ход тригге$)а каждой ячейки памяти соединен с первым входом элемента И-ИЛИ-НЕ последующей ячейки памяти, и тактовые шины, отличающийс я тем, что, с целью повышения

5 быстродействия регистра, в него введен дешифратор, входы которого соединены с тактовыми шинами, выходы дешифратора подключены к вторым, третьим, четвертым и пятым входам

10 элементов И-ИЛИ-НЕ ячеек памяти, шестые входы элементов И-ИЛИ-НЕ . ячеек памяти соединены с выходом первого элемента ИЛИ, выход второго элемента ИЛИ соединен с седьмыми

15 входами элементов И-ИЛИ-НЕ ячеек памяти, выход триггера каждой ячейки памяти соединен с восьмыми входами элементов И-ИЛИ-НЕ ячеек памяти, кроме данной ячейки памяти.

Источники информации,

принятые во внимание при экспертизе

1. Справочник по цифровой вы числительной технике. Киев, Гех„ ника, 1974, с. 156-162. 2. Авторское свидетельство CCCi по заявке № 2797343/24, . кл. (3 11 С 19/00.

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный регистр сдвига | 1989 |

|

SU1642527A1 |

| Реверсивный регистр сдвига | 1979 |

|

SU830577A1 |

| Реверсивный регистр сдвига | 1990 |

|

SU1721632A1 |

| Симметричный делитель частоты импульсов | 1982 |

|

SU1089763A2 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037272C1 |

| Устройство для отображения информации | 1987 |

|

SU1437909A1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2522306C1 |

| Запоминающее устройство с замещениемдЕфЕКТНыХ ячЕЕК | 1978 |

|

SU803009A1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2527188C1 |

Авторы

Даты

1982-09-23—Публикация

1980-06-18—Подача