Изобретение относится к вычислительной технике и может быть использовано в устройствах диагностирования и статистической обработки информации.

Целью изобретения является повышение быстродействия регистра в режиме уплотнения информации.

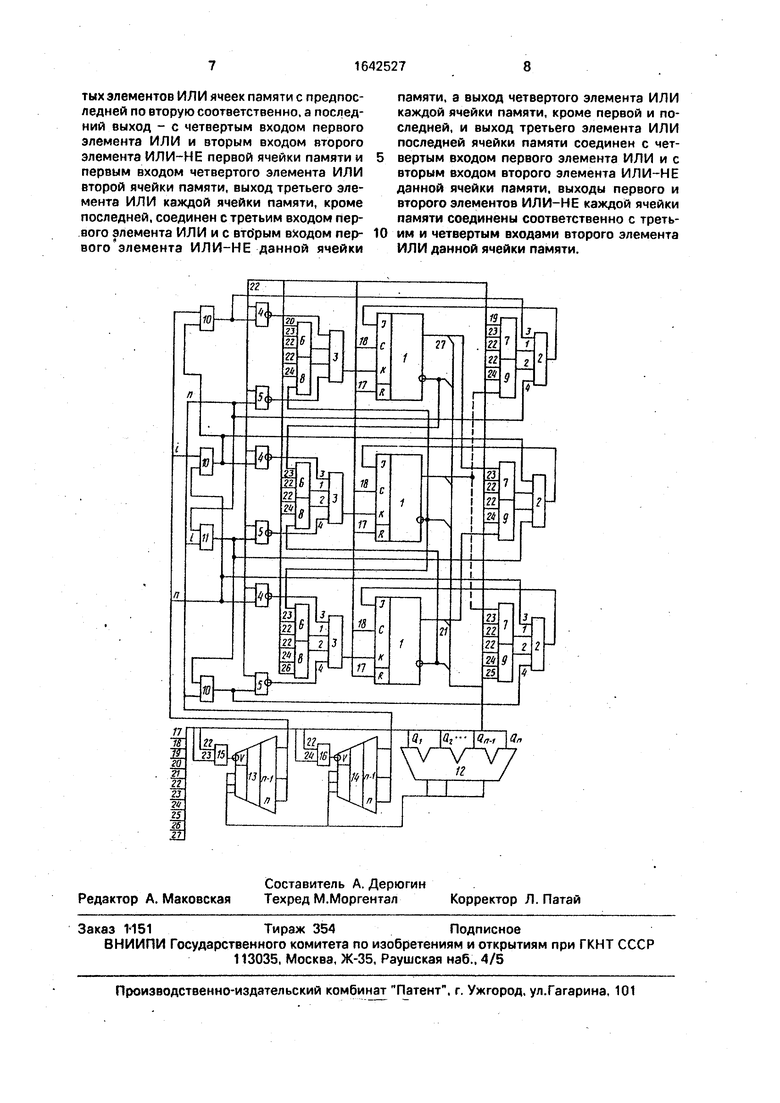

На чертеже представлена схема регистра сдвига.

Регистр содержит в каждой ячейке памяти (К-триггер 1, первый 2 и второй 3 элементы ИЛИ, первый 4 и второй 5 элементы ИЛИ-НЕ, первый 6, второй 7. третий 8 и четвертый 9 элементы И, третий элемент ИЛИ 10, в каждой ячейке (кроме первой и последней) - четвертый элемент ИЛИ 11, сумматор 12,дешифраторы 13 и 14, первый

15 и второй 16 дополнительные элементы ИЛИ, вход 17сброса регистра, вход сдвига, прямой информационный вход 19 при сдвиге вправо, инверсный информационный вход 20 при сдвиге вправо, выход 21 информации в прямом последовательном коде при сдвиге вправо, вход 22 управления режимом работы Сдвиг/уплотнение,-входы управления реверсом вправо 23 и влево 24, прямой информационный вход 25. инверсный информационный вход 26 и прямой информационный выход 27 при сдвиге влево.

Реверсивный регистр сдвига работает следующим образом.

Регистр сдвига в зависимости от сигнала управления, подаваемого на вход 22 упо

-N Ю СЛ ГО

VI

равления режимом, может работать в двух режимах - сдвига кода и уплотнения информации. При единичном значении сигнала управления на входе 22 регистр работает в режиме сдвига кода. При этом на первых входах элементов ИЛИ-НЕ 4 и 5, ИЛИ 15 и 16, на третьих входах элементов И 6-9 и на входах стробирования дешифраторов 13 и 14 устанавливаются единичные значения сигналов. В результате на всех выходах де- шифраторов 13 и 14, на выходах всех элементов ИЛИ 10 и 11 и, следовательно, на третьих и четвертых входах элементов ИЛИ 2 и 4 всех ячеек устанавливаются нулевые значения сигналов. Направление сдвига оп- ределяетсл значением сигналов на входах 23 и 24 управления реверсом.

При подаче единичного сигнала на вход

23и нулевого на вход 24 вследствие наличия единичных сигналов на вторых входах эле- ментов И 6 и 7 и нулевых сигналов на вторых входах элементов И 8 и 9 всех ячеек замкнуты связи между прямыми и инверсными выходами IK-триггера 1 i-й ячейки и, соответственно, I- и К-входами tK-триггера 1 (I + 1)-й ячеек (i 1, п-1), выполняетсся режим сдвига вправо.

Входная информация в виде парафаз- ного последовательного кода при сдвиге вправо поступает на входы 19 и 20 или в виде однофазного - на вход 19. Выходом последнего однофазного кода при сдвиге вправо является выход 21, соединенный с прямым выходом IK-триггера 1 последней ячейки.

При подаче единичного сигнала на вход

24и нулевого - на вход 23 вследствие наличия нулевых сигналов на вторых входах элементов И 6, 7 и единичных сигналов на вторых входах элементов И 8 и 9 всех ячеек замкнуты связи между прямым и инверсным выходами IK-триггера 1 i-й ячейки и, соответственно, 1-й К-входами IK-триггера 1 (1)-й ячейки (I п, 2), выполняется режим сдвига влево. Входная информация в виде парафазного последовательного кода при сдвиге влево поступает на входы 25 и 26 или

в виде одноразрядного - на вход 25. Выходом последовательного однофазного кода при сдвиге влево является выход 27, соеди- ненный с прямым выходом IK-триггера первого разряда.

При нулевом значении сигнала управления на входе 22 регистр работает в режиме уплотнения (сжатия) информации. Направ- ление уплотнения, как и в режиме сдвига, определяется значением сигналов на шинах 23 и 24 реверса.

Код неуплотиенной двоичной комбинации, записанный в регистр, с прямых выходов триггеров 1 всех ячеек поступает на входы сумматора 12 и формирует на его выходах двоичный код суммы числа единиц, что приводит к появлению единичного сигнала на одном из выходов одного из дешифраторов 13 или 14. В режиме уплотнения вправо на вход 22 управления режимом подан нулевой сигнал, на вход 23 - единичный, на вход 24 - нулевой. Соответственно нулевое значение сигнала поступает на первые входы элементов ИЛИ-НЕ 4 и 5 всех ячеек и на вход стробирования дешифратора 14. Единичный сигнал с возбужденного i-ro выхода дешифратора 14 поступает на первый вход элемента ИЛИ 11 соответствующего разряда (считая справа налево от последнего разряда) и проходит далее по цепи элементов ИЛИ 11 включительно до п-го разряда. В результате на четвертых входах элементов ИЛИ 2 и, следовательно, на :входах IK-триггеров 1 ячеек (п - I + 1) п

установятся единичные, а на четвертых входах элементов ИЛИ 2 и на 1-входах триггеров 1 ячеек (п - I) 1 - нулевые сигналы.

На входе К триггера 1 каждой ячейки значение сигнала противоположно значению сигнала на 1-входе триггера 1 этой ячейки. Подача одного импульса сдвига на вход 18 сдвига при нулевом сигнале на входе 22 управления режимом приведет к установке fpnrrepOB 1 ячеек1-(п-) в нулевое, а триггеров 1 ячеек (п - i + 1)п-в единичное

состояния.

При дальнейшей подаче импульсов сдвига состояние регистра не изменяется. При установке единичного сигнала на шине 22 управления режимом сжатая информация выводится из регистра сдвигом вправо.

Время сжатия информации вправо - один такт.

В режиме уплотнения влево на вход 22 управления режимом подается нулевой, на вход 23 - нулевой, на вход 24 - единичный сигналы. Соответственно нулевое значение сигнала поступает на первые входы элементов ИЛИ-НЕ 4 и 5 всех ячеек, на вход стробирования дешифратора 13. Единичный сигнал с входа 24 поступает на вход стробирования дешифратора 14 через элемент ИЛИ 16, запрещая декодирование двоичного кода суммы. В результате на всех выходах дешифратора 14 присутствуют нулевые сигналы, дешифратор 13 в это время открыт нулевым сигналом на входе стробирования. Единичный сигнал с возбужденного 1-го выхода дешифратора 13 поступает на первый вход элемента ИЛИ 10 соответствующего разряда (считая слева направо от первого разряда) и проходит далее по цепи элементов ИЛИ 10 до первого разряда включительно.

В результате на третьих входах элементов ИЛИ 2 и. следовательно, на 1-входах

триггеров 1 ячеек I, i - 1 1 установятся

единичные, а на третьих входах элементов ИЛИ 2 и на 1-входах триггеров 1 ячеек (I + 1),

(I + 2)п - нулевые сигналы. На входе К

триггера 1 каждой ячейки значение сигнала противоположно значению сигнала на I- входе триггера 1 этой ячейки.

Подача одного импульса сдвига на вход 18 сдвига при нулевом сигнале на входе 22 управления режимом приведет к установке триггеров 1 ячеек 1-1 в единичное, а триггеров 1 ячеек (i + 1) - п - в нулевое состояние.

При дальнейшей подаче импульсов сдвига состояние реверсивного регистра не изменяется.

При установке единичного сигнала на входе 22 управления режимом сжатия информация выводится из регистра сдвигом влево.

Время сжатия информации влево - один такт.

Формулаизобретения

Реверсивный регистр сдвига, содержащий ячейки памяти, каждая из которых, кроме первой и последней, состоит из IK-триггера, четырех элементов И и четырех элементов ИЛИ, а первая и последняя ячейки памяти - из IK-триггера, четырех элементов И и трех элементов ИЛИ, и первый и второй дополнительные элементы ИЛИ, причем прямой и инверсный выходы IK- триггеров каждой ячейки памяти, кроме по- следней, соединены с первыми выходами соответственно второго и первого элементов И последующей ячейки памяти, а прямой выход IK-триггера последней ячейки памяти является последовательным инфор- мационным выходом регистра при сдвиге вправо, первые входы второго и первого элементов И первой ячейки памяти являются соответственно прямым и инверсным по- следовательными информационными входами регистра при сдвиге вправо, прямой и инверсный выходы IK-триггеров каж- дрй ячейки памяти, кроме первой, соединены с первыми входами соответственно четвертого и третьего элементов И предыдущей ячейки памяти, а прямой выход IK-триггера первой ячейки памяти является последовательным информационным выходом регистра при сдвиге влево, первые входы четвертого и третьего элементов И последней ячейки памяти являются соответственно прямым и инверсным последовательными информационными входами регистра при сдвиге влево в каждой ячейке памяти, выходы первого и третьего элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен с К-входом IK- триггера, выходы второго и четвертого элементов И соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с 1-входом IK-триггера, вторые входы первого и второго элементов и всех ячеек памяти соединены и являются входом реверса вправо, вторые входы третьего и четвертого элементов И соединены и являются входом реверса влево, входы сброса и тактовые входы IK- триггеров соединены и являются соответственно входом сброса и сдвига регистра, первый вход третьего элемента ИЛИ каждой ячейки, кроме последней и предпоследней, соединен с выходом третьего элемента ИЛИ последующей ячейки памяти, первый вход четвертого элемента ИЛИ каждой ячейки, кроме второй, еоединен с выходом четвертого элемента ИЛИ предыдущей ячейки памяти, а первый вход третьего элемента ИЛИ последней ячейки памяти соединен с выходом четвертого элемента ИЛИ предпоследней ячейки памяти, отличающийся тем, что, с целью повышения быстродействия регистра в режиме уплотнения информации, в него введены сумматор, первый и второй дешифраторы, а в каждую ячейку памяти - первый и второй элементы ИЛИ-НЕ, первые входы которых и третьи входы каждого элемента И каждой ячейки памяти соединены и являются входом управления режимом работы регистра, прямые выходы IK-триггеров всех ячеек памяти соединены с соответствующими входами сумматора, выходы которого соединены с соответствующими информационными входами первого и второго дешифраторов, входы стробирования которых соединены соответственно с выходами первого и второго дополнительных элементов ИЛИ, первые входы которых соединены с первым входом первого элемента ИЛИ - НЕ первой ячейки памяти, а вторые входы являются входами управления реверсом соответственно вправо и влево регистра, каждый выход, кроме последнего, первого дешифратора соединен с вторым входом третьего элемента ИЛИ соответствующей ячейки памяти, а последний - с вторым входом первого элемента ИЛИ-НЕ и третьим входом первого элемента ИЛИ последней ячейки памяти и первым входом третьего элемента ИЛИ предпоследней ячейки памяти, первый выход второго дешифратора соединен с вторым входом третьего элемента ИЛИ последней ячейки памяти, выходы с второго по предпоследний соединены с вторыми входами четвертых элементов ИЛИ ячеек памяти с предпоследней по вторую соответственно, а последний выход - с четвертым входом первого элемента ИЛИ и вторым входом второго элемента ИЛИ-НЕ первой ячейки памяти и первым входом четвертого элемента ИЛИ второй ячейки памяти, выход третьего элемента ИЛИ каждой ячейки памяти, кроме последней, соединен с третьим входом первого элемента ИЛИ и с вто рым входом пер- вого элемента ИЛИ-НЕ данной ячейки

0

памяти, а выход четвертого элемента ИЛИ каждой ячейки памяти, кроме первой и последней, и выход третьего элемента ИЛИ последней ячейки памяти соединен с четвертым входом первого элемента ИЛИ и с вторым входом второго элемента ИЛИ-НЕ данной ячейки памяти, выходы первого и второго элементов ИЛИ-НЕ каждой ячейки памяти соединены соответственно с третьим и четвертым входами второго элемента ИЛИ данной ячейки памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 1991 |

|

RU2022372C1 |

| Реверсивный регистр сдвига | 1989 |

|

SU1817135A1 |

| Регистр сдвига | 1987 |

|

SU1439682A1 |

| Кодовый преобразователь | 1985 |

|

SU1285605A1 |

| Устройство для программного управления автооператором | 1987 |

|

SU1536355A1 |

| Устройство для отображения информации | 1987 |

|

SU1437909A1 |

| Ассоциативное запоминающее устройство | 1984 |

|

SU1234880A1 |

| Реверсивный регистр сдвига | 1980 |

|

SU960955A1 |

| Устройство для обработки изображений | 1986 |

|

SU1316003A1 |

| Устройство для программного управления захватом автооператора | 1982 |

|

SU1233103A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах диагностирования и статистической обработки информации. Цель изобретения - повышение быстродействия реверсивного регистра сдвига в режиме уплотнения информации за счет определения числа единиц в неуплотненной кодовой комбинации и установки регистра в состояние, соответствующее сжатой комбинации, за время одного такта. Реверсивный регистр сдвига содержит в каждой ячейке двухступенчатый IK-триггер, первый и второй элементы ИЛИ, первый и второй элементы ИЛИ-НЕ, четыре элемента И, в каждой ячейке третий элемент ИЛИ, в каждой ячейке, кроме первой и последней, четвертый элемент ИЛИ, первый и второй дополнительные элементы ИЛИ. Введение дополнительных элементов - сумматора числа единиц неуплотненной кодовой комбинации, первого и второго дешифраторов кода суммы - позволяет повысить быстродействие реверсивного регистра сдвига в режиме уплотнения до одного такта. 1 ил. сл с

| Реверсивный регистр сдвига | 1983 |

|

SU1140176A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Авторское свидетельство СССР № 1283856, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-04-15—Публикация

1989-03-15—Подача