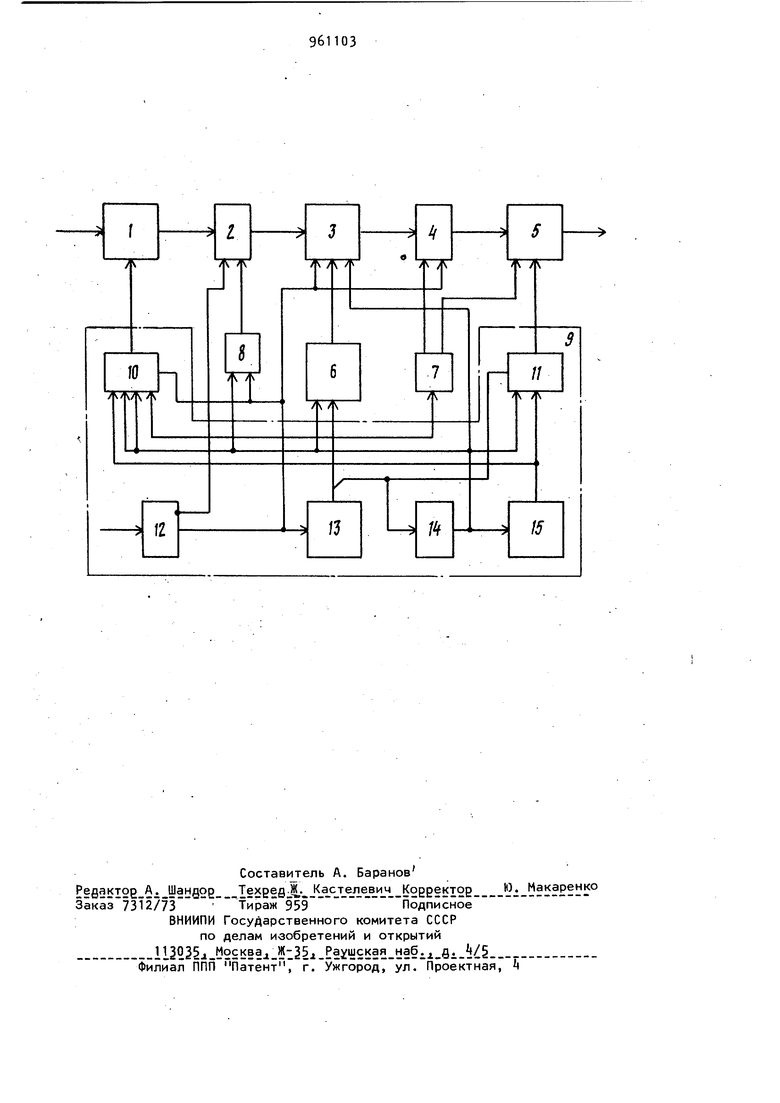

Изобретение относится к вычислительной технике и может быть использовано для вычисления коэффициентов |цифрового фильтра, основанного на ис пользовании алгоритма быстрого преоб разования Фурье, при цифровой обработке сигналов. Известно устройство, содержащее блок памяти коэффициентов фильтра и управляемый квантующий генератор, в котором форма частотной характерис тики изменяется переключением наборов коэффициентов фильтра, заранее записанных в блок памяти коэффициентов, а положение частотной характерис тики фильтра на частотной оси задается изменением частоты управляемого квантующего генератора 1 . Недостаток этого фильтра - низкая точность получения заданной частотной характеристики из-за ограниченного количества наборов коэффициентов, записанных в блоке памяти коэффициентов (Ьильтра. Наиболее близким к предложенному является цифровой фильтр радиолокационной системы со сжатием импульсов, содержащий блок памяти импульсной характеристики (излучаемого сигнала), блок преобразования Фурье, блок умножения и блок памяти коэффициентов. В этом устройстве коэффициенты вычисляются в самом фильтре по заданной импульсной характеристике. Это увеличивает скорость изменения частотной характеристики фильтра 2. Однако и в этом фильтре коэффициенты вычисляются с помощью преобразования Фурье, для вычисления которого необходимо выполнить большое количество арифметических операций, а поэтому затратить большое время. Кроме того, чаще бывает задана не импульсная характеристика 1| ильтра, а его частотная характеристика. Цель изобретения - упрощение и повышение быстродействия устройства. 39 Для достижения этой цели в устройство, содержащее два блока памяти и блок умножения, введены дополнительно первый и второй накапливающие сумматоры- вымитатели , блок постоянной памяти, дешифратор, элемент И, сумматор-оычитатель, буферный регистр,,первый и второй счетчик, первый и вто рой триггер, причем выход первого блока памяти соединен с.входом первого накапливающего еумматора-вычитателя, выход которого подключен к первому входу блока умножения, выход которого соединен с входом второго нака ливащего сумматора-вычитателя, выход которого подключен к информационному входу второго блока памяти, выход коVoporo является выходом устройства, первый выход первого триггера подключен к управляющему входу сумматора-вычитателя, первому входу элемента И, первому управляющему входу блока умножения и второго накапливающего сумматора-вычитателя и ко входу первого счетчика, выход которого соединен с первым информационным входом старших разрядов сумматора-вычитателя, входом старших разрядов адреса блока постоянной памяти, входом дешифратора, управляющим входом буферного регистра и входом второго триггера, выход которого подключен к первому и второму информационным входам младших разрядов сумматора-вычитателя , второму входу элемента И, входу младших разрядов адреса блока постоянной памяти, второму управляющему входу блока умножения, входу младших разрядов буферного регистра и входу второго счетчика, выход которого соединен с вторым информационным входом старших разрядов сумматора-вычита теля и входом старших рязрядов буферного регистра, выход которого подключен к адресному входу второго блока памяти, вход записи которого подключен к первому выходу дешифратора, второй выход которого соединен со вторым управляющим входом второго на капливающего сумматора-вычитателя, выход блока постоянной памяти соедин с вторым входом блока умножения, выход элемента И соединен с первым управляющим входом первого накапливающего сумматора-вычитателя, второй уп равляющий вход которого соединен со вторым выходом первого триггера, вход которого ярляется первым входом устройства, выход сумматора-вы3читателя соединен с адресным входом второго блока памяти, информационный вход которого является вторым входом устройства. На чертеже показана блок-схема устройства. Устройство содержит первый блок 1 памяти, первый накапливающий сумматор- вычитатель 2, блок 3 умножения. второй накапливающий сумматор 4, второй блок 5 памяти, блок 6 постоянной памяти, дешифратор 7, элемент И 8 и адресный блок 9, содержащий комбинационный сумматор-вычитатель 10, буфарный регистр 11 , первый триггер 12, первый счетчик 13, второй триггер Н и второй счетчик 15. Коэффициенты фильтра в предложенном устройстве,вычисляются без выполнения прямого и обратного преобразований Фурье по формулам: (-nrVn)(n) Р((К4П41; Ч.г где и Лл.. коэффициенты фильтра соответственно с четным И нечетным номером; заданная частотная характеристика фильтра.содержащая 2L+1 отсчетов; константа, выбирается в зависимости от используемого сглаживающего окна; последовательность, вычисленная заранее и записанная в ПЗУ. К 0,1,2,...,N-1, Последовательность (Vi) можно получить следующим юбразом: гт)( i) , если i О В m(i)/7. .если i О где rn(i) -последовательность, полученная преобразованием Фурье от сглаживающего окна, дополненного до двойной длины нулевыми отсчетами сглажи ающего окна - U , 1 ,Z,. .. ,/iL Отсчеты t(2n) - действительные числа, а В(2п 1) - мнимые. Устройство работает следующим образом. Предварительно в блок 1 памяти по, второму входу устройства записывают заданную частотную характеристику 596 фильтра. Первый триггер 12 и первый счетмик 1,3 устанавливают в нулевое состояние. Во второй триггер 1 записывается младший разряд номера вычисляемого коэффициента, во второй счетчик 15 число К, представляющее собой старшие разряды номера вычисляемого коэффициента. После этого на счетный вход первого счетного триггера 12, являющийся первым входом устройства, подается сигнал с выхода опорного генератора импульсов. На выходах триггера 12 фор мируются тактовые импульсы (ТИ) такие, что длительность импульса равна длительности интервала между импульсами. По заднему фронту тактовых импульсов пересчитывают последовательно соединенные первый счетчик 13, .второй счетный триггер I и второй счетчик 15Число с выхода первого счетчика п ступает на старшие разряды адресного входа блока 6. На младший разряд вхо да блока 6 поступает 1 или О с выхода второго триггера 1A, Таким об разом, на вход блока 6 поступает адрес 2п при вычислении коэффициентов t четным индексом и 2п+1 при вычисле нии коэффициентов с нечетным индексом В первой половине каждого такта работы устройства, т.е. в интервале между ТИ, комбинационный сумматорвычитатель 10 сигналом на управляющем входе включен в режим сложения На его выходе при вычислении коэффициентов с четным и нечетным индексом формируются числа соответственно 2(k+n) и 2(k+n+l). Во второй половине такта формируется число 2(k-n). На адресный вход первого блока 1 памяти при этом поступают числа k+n, k+n+1 и абсолютное значение разности k-n, так как младший и знаковый разря ды сумматрра-вычитателя 10 к входу блока 1 памяти не подключены. Отсчеты ). Я(.п + ч; или S( заданной частотной характеристики фильтра с выхода первого блока 1 памя ти поступают на информационный вход накапливаюсцего- сумматора-вычитателя 2 При вычислении коэффициентов с четными индексами элемент И 8 закрыт сигналом с выхода второго триггера 14 поэтому на второй управляющий вход ..,. .- . J- , , . . ,-, сумматора 2 поступает нулевой сигнал а на его выходе к окончанию каждого ,ТИ формируется сумма S(k-n)-S(k-Hi- -1) ;При вычислении коэффициентов с нечет34ным индексом элемент И 8 открыт, на его выход и на второй управляющий вход сумматора-вычитателя 2 проходят инвертированные ТИ. Поэтому на выходе сумматора-вычитателя 2 формируется разность S(k-n)-S(k+n+1). С окончанием каждого ТИ по его заднему фронту сумма или разность () или S(-k-nr()i+n-n) поступает на первый информационный вход блока 3 умножения. В это же время на второй вход этого блока записывается число В(2п) или Р(2п+1) из блока 6. Эти числа перемножаются в блоке 3 умножения и по следующему ТИ произведение 5(к-п; ()ji (2п) или 5 ( k-n) S{fe+n-i;/ 1(2п+1) поступает на информационный вход накапливающего сумматора f. В накапливающем сумматоре j суммируются (kfl) произведений с выхода умножителя, затем по одиночному сигналу с первого выхода дешифратора 7 значение вычисленного коэффициента ,.е(1п) (1c-n))J (l..n-.)-S( записывается во второй блок 5 памяти по адресу 2К или , поступающему на его адресный вход с выхода буферного регистра 11. Коэффициент пересмета первого счетчика 13 равен L, + 1, поэтому после вычисления очередного коэффициента фильтра сигналом с выхода этого счетчика увеличивается на единицу суммарное содержимое триггера 1 и счетчика 12 и начинается вычисление следующего коэффициента фильтра. Суммирование нового коэффициента в накапливающем сумматоре f наминается по единичному сигналу с второго выхода дешифратора 7. Время вычисления коэффициентов фильтра определяется количеством выполняемых в устройстве операций умножения. В известных устройствах для вычисления коэффициентов по заданной частотной характеристике необходимо выполнить 3Nlog H+2N операций умно tЖения, а в предложенном --(, что значительно.меньше. Дополнительный оыигрыш в быстродействии получается из-за того, что в предлагаемом 7.96 устройстве можно не вычислять коэффициенты, о которых известно, что они заведомо равны нулю. Таких коэффициентов в низкочастотных фильтрах бывает до 1/2 их общего количества, а в полосовых фильтрах - еще больше. В целом, в зависимости от вида требуемой частотной характеристики фильтра, увеличение быстродействия составляет от десятков до тысяч раз, При этом одновременно упрощается конструкция устройства, так как отпадает необходимость в реализации БПФ. Формула изобретения Устройство для вычисления коэффициентов цифрового фильтра, содержащее два блока памяти и блок умножения, отличающееся тем, что, с целью упрощения устройства и повышения быстродействия, оно содержит первый и второй, накапливающие сумматоры- аычитатели, блок постоянной Памяти, дешифратор, элемент И, сумматор- пычитатель, буферный регистр, пер .вый и второй счетчик, первый и второй триггер, причем выход первого блока памяти соединен с входом liepBOго накапливающего сумматора-вычитателя, выход которого подключен к первому входу блока умножения, выход которого соединен с входом второго накапливающего сумматора-вычитателя, выход которого подключен к информационному входу второго блока памяти, выхо которого является выходом устройства, первый выход первого триггера подключен к управляющему входу сумматоравычитателя, первому входу элемента И, первому управляющему входу блока умно жения и второго накапливающего сумматора-вычитателя и к входу первого счетчика, выход которого соединен с З8 первым информационным входом старших рязрядов сумматора-вычитателя, входом старших разрядов адреса блока постоянной памяти, входом дешифратора, управляющим входом буферного регистра и входом второго триггера, выход ко(горого подключен к первому и второму информационным входам младших разрядов сумматора-вычитателя, второму входу элемента И, входу младших разрядов адреса блока постоянной памяти, второму управляющему входу блока умножения, входу младших разрядов буферного регистра и входу второго счетчика, выход которого соединен с вторым информационным входом старших разрядов сумматора-вычитателя и входом старших разрядов буферного регистра, выход которого подключен к адресному входу второго блока памяти, вход записи которого подключен к первому вь1ходу дешифратора, второй выход которого соединен с вторым управляющим входом второго накапливающего сумматора-вычитателя, выход блока постоянной памяти соединен с вторым входом блока умножения, выход элемента И соединен с первым управляющим входом первого накапливающего сумматора-вычитателя, второй управляющий вход которого соединен со вторым выходом первого триггера, вход которого является первым входом устройства, выход сумматора-вычитателя соединен с адресным входом второго блока памяти, информационный вход которого является вторым входом устройства. Источники информации, принятые во внимание.при экспертизе 1. Рабинер Л., Гоулд Б. Теория и применение цифровой обработки сигналов. М., Мир, 1978. . 2. Патент США № 3680105, кл. G Об F 15/3, опублик. 1972 (пpoтofип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления коэффициентов цифрового фильтра | 1981 |

|

SU987804A1 |

| Устройство для формирования случайных процессов с заданным спектром | 1981 |

|

SU1027723A1 |

| Устройство для решения систем алгебраических уравнений | 1983 |

|

SU1226427A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Устройство для определения амплитудно-частотных характеристик объектов | 1989 |

|

SU1689876A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1003078A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Цифровой рекурсивный фильтр | 1985 |

|

SU1328925A1 |

| Устройство для решения систем линейных дифференциальных уравнений | 1988 |

|

SU1525714A2 |

Авторы

Даты

1982-09-23—Публикация

1980-06-05—Подача