1

Изобретение относится к вычисли-, тельной технике и может быть использовано для вычисления коэффициентов цифрового фильтра, основанного на использовании алгоритма быстрого преобразования Фурье (БПФ) при цифровой обработке сигналов.

Известен цифровой фильтр радиолокационной системы со сжатием импульсов, содержащий блок памяти импульсной характеристики (излучаемого сигнала), блок преобразования Фурье, блок умножения и блок памяти коэффициентов СОВ этом устройстве коэффициенты вычисляются в самом фильтре по заданной импульсной характеристике. Это обеспечивает получение заданной импульсной характеристики фильтра, однако в этом устройстве коэффициенты вычисляются с помощью преобразования Фурье, для выполнения которого необходимо выполнить большое количество арифметических операций.

а следовательно затратить большое время и сложное оборудование. Кроме того, чаще бывает задана не импульсная характеристика фильтра, а его частотная характеристика.

Известно также устройство для вычисления коэффициентов фильтров, сО держащее два блока памяти, блок ум ножения, блок постоянной памяти ком бинационнОй сумматор-вычитатель, два накапливающих сумматора-вычитателя, регистр, два счетных триггера, два двоичных счетчика, элемент И и дешифратор, в котором коэффициенты вычисляются по заданной частотной ха рактеристике без выполнения преобразования Фурье и с уменьшенным количеством выполняемых арифметических операций 2 J.

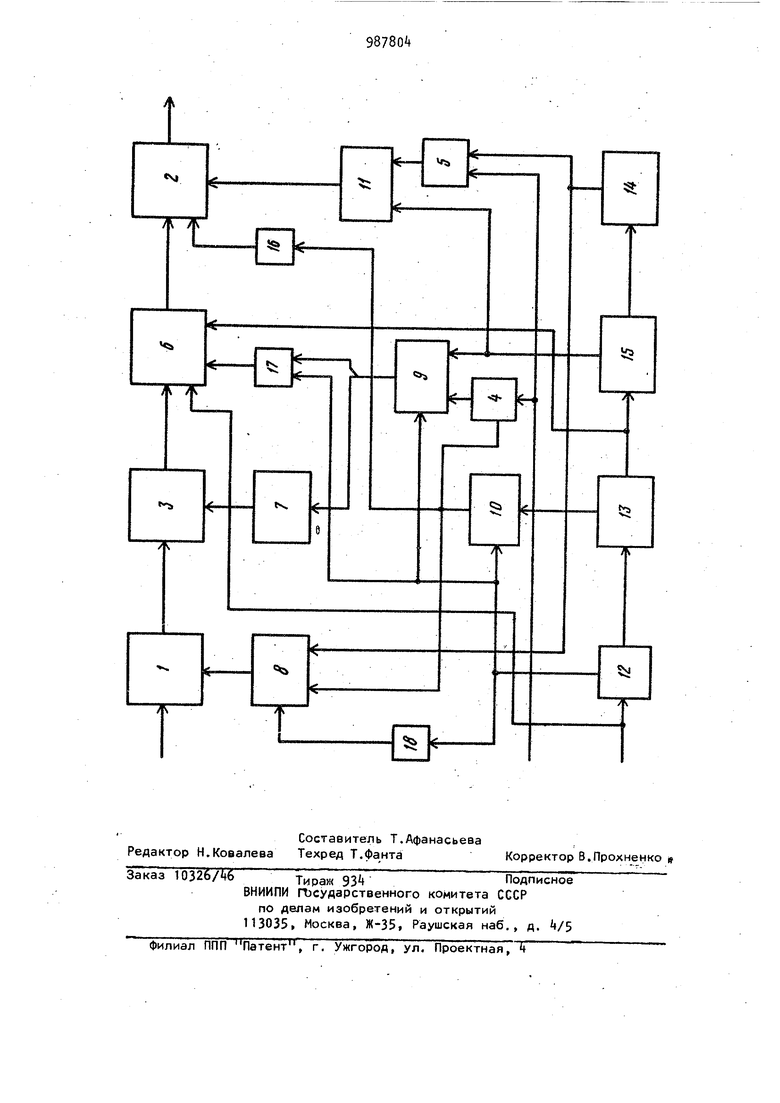

Недостаток известного устройства заключается в том, что размер преобразования Фурье N при выполнении цифровой фильтрации должен быть равным удвоенной длине импульсной характеристики фильтра L, в то время как оптимальная величина N приблизительно равна , Это приводит к то му, что количество вычислений, необходимых для выполнения фильтрации, возрастает по сравнению с минимально возможным и может привести к значительному усложнению с минимально возможным и может привести к значительному усложнения конструкции цифрового фильтра. Цель изобретения - расширение .функциональных возможностей устройства за счет вычисления коэффициентов для фильтров, использующих быстрое преобразование Фурье с размером преобразования Lц, где W(j - про извольное число; L - длина импульсной характеристики .фильтра. Поставленная цель достигается тем что в устройство для вы иcлeния кодффициентов цифрового фильтра, содержащее первый блок памяти, информа ционный вход которого является первым входом устройства, а адресный вход соединен с выходом комбинационного сумматрра-вычитателя, последова тельно соединенные блок постоянной памяти, блок умножения, накапливаюсумматрр-вычитатель и второй бло щий памяти, вход записи которого подключен к выходу дешифратора, вход которого объединен с первым информационным входом комбинационного сумматора вычитателя, счетный триггер, вход которого является вторым входом устройства, первый выход соединен с пер вым входом элемента И, а второй вы ход - с входом первого счетчика импульсов, и второй счетчик импульсов, выход которого подключен ко второму информационному входу комбинационного сумматора-вычитателя, введены сум маторы, дополнительный комбинационный сумматор-вычитатель, дополнитель ный счетчик импульсов, дополнительны блоки умножения и инвертор, при этом выход первого блока памяти подключен к другому входу блока умножения, пер вый выход счетного триггера соединен с управляющим входом дополнительного koмбинaциoннoro сумматора-вычитателя, с первым входом первого сумматора и через инвертор с управляющим входом комбинационного . сумматора-вы . читателя, информационный выход первого счетчика импульсов подключен к второму входу первого сумматора, выход которого соединен с входом дешиф ратора и первым входом первого Дополнительного блока умножения, а вы- ход переноса - к первому управляющему входу накалпивающего сумматоравычитателя и к входу дополнительного счетчика импульсов, выход переноса которого соединен с входом второго счетчика импульсов, а информационный выход - с первым информационным входом дополнительного комбинационного сумматора-вычитателя и с первым входом второго сумматора, выход которого подключен к адресному входу второго блока памяти, а второй вход - к ВЫХОДУ второго допол « нительного блока умножения, первый вход которого соединен с выходом второго счетчика, а второй вход объединен со вторым входом первого дополнительного блока умножения и является третьим входом устройства,,причем выход первого дополнительного блока умножения соединен со вторым информационным входом дополнительного комбинационного сумматора-вычитателя, выход которого подключен к адресному входу блока постоянной памяти и к второму входу элемента И, выход которого подключен к второму I управляющему входу накапливающего сумматора-вычитателя, вход синхронизации которого объединен с входом счетного триггера. На чертеже представлена структурная электрическая схема предлагаемого устройства. Устройство содержит первый и второй блоки 1 и 2 памяти, блок 3 Умножения, дополнительные блоки и 5 умножения, накапливающий сумматорвычитатель 6, блок 7 постоянной памяти, комбинационный сумматор-вычитатель 8, дополнительный комбинационный сумматор-вычитатель 9, первый и второй сумматоры 10 и 11, счетный триггер 12, первый и второй счетчики 13 и Т импульсов, дополнительный счетчик 15 импульсов, дешифратор 16, элемент И 17 и инвертор 18. В качестве блоков 1 и 2 памяти используют полупроводниковые статические запоминающие устройства. Единичный сигнал на входе Запись блоков памяти включает их в режим записи. Счетный триггер 12 и счетчики 13-15 импульсов в предлагаемом устройстве построены с использованием 5 только входа прямого счета. В качестве счетного триггера 12 используют любой D-триггер. В этом случае в качестве его второго выхода необходимо использовать инверсный выход триггера. Пересчет триггера и счетчиков происходит по переднему фрон ту сигнала. В качестве сумматоров 10 и 11 и комбинационных сумматоров-вычитателей 8 и 9 используют любые комбинационные устройства соответствующего назначения. Единичный сигнал на управляющем входе сумматора-вычитателя включает его в режим вычитания. Ком бинационный сумматор-вычитатель 8 работает в дополнительном коде, а до полнительный комбинационный суммато вычитатель 9 - в прямом, В качестве блока 3 умножения используется матричное устройство умножения комплексных чисел, а в каче стве блоков умножения и 5 устрой ство умножения действительных чисел . причем один из сомножителей, посту.. пающих на блоки 4 и 3 умножения выби рается обычно равным целой степени двух, вследствие чего операция умно жения сводится к сдвигу другого сомн жителя на фиксированное количество разрядов. Дешифратор 16 представляет собой обычную комбинационную логическую схему, при подаче на вход которой числа L+1 на выходе вырабатывается единичный уровень. Коэффициенты, фильтра вычисляются в предлагаемом устройстве по формут1е А iKN(v+) - 21 S tK.-ViU еМ( ) hto (K.v - iKi:M(c«H)-i«ir где A(i) вычисляемые коэффициенты цифрового фильтра; S(i) заданная частотная характеристика;константа, выбираемая в зависимости от используемого сглаживающего окна и Ng; отношение размера алгорит ма БПФ N в цифровом филь тре к длине импульсной ха рактеристики фильтра Ly,, целое числоi 4 t(i) - последовательность, вычисляемая заранее и .записанная в блок постоянной памяти 71 ,1,2,...,|m; ,1 ,2,...,Mg-t. Устройство работает сл едующин образом. Предварительно в первый блок 1 памяти по первому входу устройства заносится заданная частотная характеристика фильтра S(i). Счетный триггер 12, первый счетчик 13 импульсов и регистр накаляйвапцего сумматоравычитателя 6 устанавливают в нулевое состояние. В счетчики Т и 15 импульсов записывают числа соответственно k и т, определяющие номер вычисляемого коэффициента kNg+m. На третий вход устройства подается число Ng, После этого на выходе комбинационного сумматора-вычитателя .8, включенного сигналом с выхода счетного триггера 12 в режим вычитания, сформируется число kln, причем чис/Ю п, поступающее с выхода счетчика 13 инпульсов в первом такте равно нулю. С выхода первого блока 1 памяти на вход блока 3 умножения поступает число S(k-n). На вход блоке 7 постоянной памяти поступает адрес Ng-n+m, сформированный в комбинационном сумматоре-вычитателе 9 и блоке k умножения, а с выхода блока 7 постоянной памяти на первый вход блока 3 умножения поступает число {n-Ng+m). На выходе блока 3 умножения формируется произведение S(k-n) {n-Ng+m), которое поступает на вход накапливающего сумматора-вычитателя 6. Далее на второй вход устройства подают тактовые импульсы (ТИ). По первсжу ТИ пересчитывает счетный триггер 12, сигналом с его выхода, комбинационный сумматор-вычитатеяь 8 включается в режим сложнен)), а комбинационный сумматор-вычитатель Э в режим вычитания. На выходе первого сумматора 10формируется число ; гн-1, так как счетный триггер 12 находится в единичном состоянии, на адресные входы первого блока 1 памяти и .блока 7 постоянной памяти поступают адреса соответственно , и I4g(n+1)-ra. На второй управляющий вход накапливающего сумматора-вычитатеяя 6.через элемент И 17 открытый еди

ничным уровнем с выхода счетного триггера 12, поступает сигнал с выхода младшего разряда комбинационного сумматора-вычитателя Э- Если число на выходе комбинационного сумматора -вычитателя 9 нечетное, то на второй управляющий вход накапливающего сумматора-вычитателя 6 поступает единичный уровень и включает режи.м вычитания. Таким образом обеспечивается умножение на (-1 По второму ТИ счетный триггер 12 переходит снова а нулевое состояние, в счетчике 13 импульсов устанавливается число , и продолжается вычисления коэффициента A(k«Ng-HD),

В процессе вычисления коэффициента разность k-n на выходе комбинационного сумматора-вычитателя может при малых значениях k получится от-, рицательной, однако запи ыаать в блок памяти значения частотной характеристики фильтра S(t) для отрицательного аргумента нет необходимости, Эти значения можно получить различными способами, используя, например, свойство периодичности функции S{i). Для этого, в частности, достаточно выбрать комбинационный сумматор-вычитатель работающим в дополнительном коде, и не подключать выход его знакового разряда к адресному входу первого блока 1 памяти.

Вычисление коэффициента завершается, когда число п на выходе счетчика 13 импульсов станет равным L, а счетный триггер 12 установится в единичное состояние. При этом на выходе первого сумматора 10 сформируется число L4-1, которое вызывает формирование единичного уровня сигнала Запись на выходе дешифратора 16, и вычисленное значение коэффициента с выхода накапливающего сумматора-вычитателя 6 запишется во второй блок 2 памяти по адресу k-Ng-fm, который формируется в блоке 5 умножения S и втором сумматоре 11.

Коэффициенты пересчета счетчиков 13 и 15 импульсов равны соответственно 1+1 и Ng, и поэтому после Записи вычисленного коэффициента, по очередному ТИ в счетчике 13 импульсо вырабатывается сигнал переноса, по KOJTOромув счетчиках Н и 15 импульсов устанавливаются числа k и т, определяющие номер следующего по порядку коэффициента.

Сигнал с выхода переноса счетчика 13 импульсов поступает также на второй управляющий вход накапливающего сумматора-вычитателя 6 и устанаеливает его регистр в нулевое состояние подготавливая его к вычислению нового коэффициента.

При определении быстродействия устройства необходимо учитывать, что

число Ng практически принимает значения не более 2 8, причем его обычно можно выбрать равным целой степени двух.

Количество операций умножения, выполняемых в блоке 3 умножения при вычислении N коэффициентов фильтра составляет в предлагаемом устройстве около 2LN умножений комплексного числа на действительное или мнимое, против примерно 2N-Ng(3 Ipg N+N9+9) операций умножения действительных чисел при использовании устройств,, реализующих вычисления по известному алгоритму с использованием БПФ. В

зависимости от вида частотной характеристики и размера преобразования Фурье выигрыш по быстродействию может составлять примерно от 10 раз в случае широкополосных фильтров и до

нескольких тысяч раз в случае узкополосной фильтрации.

формула изобретения

Устройство для вычисления коэффициентов цифрового фильтра, содержащее первый блок памяти, информационный вход которого является пер. вым входом устройства, а адресный вход соединен с выходом комбинационного сумматора-вычитателя, последовательно соединенные блок постоянной памяти, блок умножения, накапливающий cyMMatop-вычитатель и второй блок памяти, вход записи которого подключен к выходу дешифратора, вход которого объединен с первым информационным входом комбинационного сумматора - вычитателя, счетный триггер, вход которого является вторым входом устройства, первый выход соединен с первым входом элемента И, а второй выход - с входом первого счетчика импульсов, и второй счет.чик импульсов, выход которого подключен к второму информационному входу комбинационного сумматора-вычитателя, отличающееся

тем, что, с целью расширения функциональных возможностей за счет вычисления коэффициентов для фильтров использущих быстрое преобразование Фурье с размером преобразования М Ng-L, где Ng - произвольное число 1ц - длина импульсной характеристики фильтра, введены сумматор), дополнительный комбинационный сумматорвычитатель; дополнительный счетчик импульсов, дополнительные блоки умножения и инвертор, при этом выход первого блока памяти подключен к другому входу блока умножения, первый выход счетного триггера соединен с управляющим входом дополнительного комбинационного сумматора-вычитателя, с первым входом первого сумматора и через инвертор с управляющим входом комбинационного сумматора-вычитателя, информационный выход первого счетчика импульсов подключен к второму входу первого сумматора i выход которого соединен с входом дешифратора и первым входом первого дополнительного блока умножения, а выход переноса - к первому управляющему входу накапливающего cj«4Maтора - вычитателя и к входу дополнительного счетчика импульсов, выход переноса которого соединен с входом второго счетчика импульсов, а информационный выход - с первым информационешм входом дополнительного комбинационного сумматора-вычнтзтеля и с первым входом второго сумматора , выход которого подключен к адресному входу второго блока памяти, а второй вход - к выхоАУ второго дополниteльнoro блока уиножения, первый вход которого соеда|нен с выходом второго счетчика импульсов, а второй вход объединен с вторым входом первого дополнительного блока ум(;1ожения и является третьим входом устройства, причем «hixoA первого дополнительного блока умножения соединен с вторым информационным входом дополнительного комбинационного сумматора-вычитателя, выход которого подключен к адресному входу блока постоянной памяти и к второму входу элемента И, выход которого подключен к второму управлякяцему входу накапливаощего сумматора-вычитателя, вход синхронизации которого объединен с входом счетного т01ГГера.

Источники информации, принятые во внимание при экспертизе

1.Патент ША tf 3680105, кл. G 01 S 9/02, 1972.

2.Авторское свидетельство СССР

№ 2938695/24, кл.Н 03 Н 17/04, (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления коэффициентов цифрового фильтра | 1980 |

|

SU961103A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Фурье-Чебышеву | 1983 |

|

SU1136181A1 |

| Устройство для формирования случайных процессов с заданным спектром | 1981 |

|

SU1027723A1 |

| УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2000 |

|

RU2182358C2 |

| УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2000 |

|

RU2182724C2 |

| Устройство для выполнения преобразования Фурье | 1987 |

|

SU1418747A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для вычисления коэффициентов обобщенных дискретных функций | 1978 |

|

SU752347A1 |

| Устройство для вычисления суммы произведений двух массивов чисел | 1980 |

|

SU985782A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1256044A1 |

Авторы

Даты

1983-01-07—Публикация

1981-07-07—Подача