Изобретение относится к вычисли- тельной технике и может быть исполь- - зовано при построении цифровых интегрирующих машин и специализированных процессоров, предназначенных для решения систем линейных диМэеренциаль- ных уравнений вида

у А + В; у(0) у„,

где А и В - матрица и вектор коэффициентов соответственно.

Цель изобретения - повышение быстродействия устройства.

На фиг,1 приведена схема устройства;, на фиг,2 - схема блока управления; на фиг,3 - схема блока анализа; на фиг,4 - схема блока суммирования.

Устройство содержит с первого по п-й блоки li-ln памяти, с первого по

п-й блоки 2,-2f, сдвига, с первой по п-ю группы накапливающих сумматоров 3,-Зп, с первой по п-ю группы элементов И , с первой по п-ю группы сумматоров ,,, с первого по п-й кодирующие элементы ,, вьвделення старшего значащего разряда, с (и+1)й по 2п-ю группы сумматоров , с первого п о п-й дешифраторы 8,-8п, с (п+1)-й по 2п-ю группы накапливающих сумматоров 9,-9„, с (п+)-й по 2п-ю группы элементов И , счетчик 11, блок 12 элементов И, регистр. 13 шага интегрирования, коммутатор 14 . приращений и знаков, элемент РШИ 15, блок 16 анализа, блок 17 управления, вход 18 сигнала начала работы, выходы результата устройства, входы 20 шага интегрирования устройства, с первого по п-й блоки

N

суммирования, с третьей по (2+п)-ю группы элементов И ,5 с (3.+п)й по (2h+2)-io группы элементов И 23,- 23 и с (2п+3)-й по (Зп+2)-ю группы элементов И ,

Блок 17 управления образзтат генератор 25 импульсов, с первого по восьмой элементы И 26-33, первый 34 и второй 35 дешифраторы, с первого по шестой элементы ИЛИ 36-41 с.первого по четвертый счетчики 42-45, первый 46 и второй 47 триггеры, вход 48 режима интегрирования блока управления, . элемент НЕ 49, блок 50 эле- ментов НЕ, сумматор 515 блок 52 элементов задержки, с первого по девятый выходы 53-6, выход 62 сигнала окончания интегрирования, вход 63 запуска блока управления, вход 64 признака.окончания работы блока управления, третий триггер-65, десятый 66 и одиннадцатый 67 выходы блока управления.

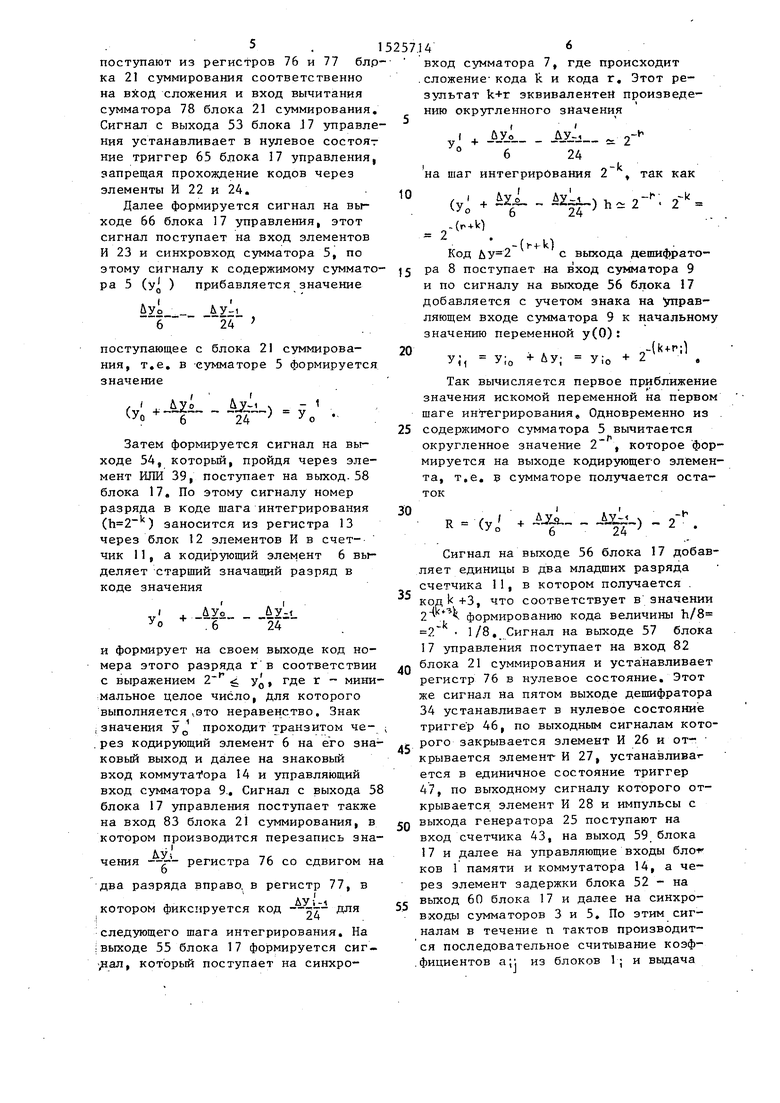

Блок 16.анализа включает сумматор 68 невязки, регистр 69 значения точности интегрирования, информационный вход 70, управляющий вход 71 и выход 72 блока анализа.

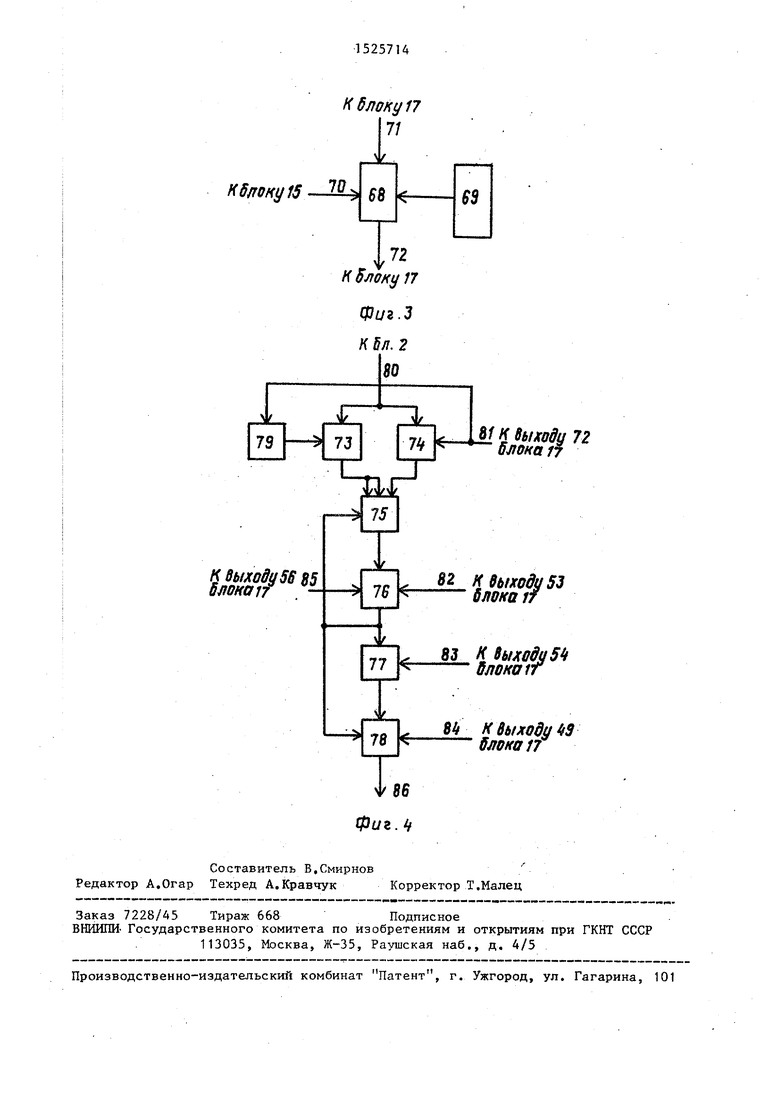

Блок 21 суммирования содержит пер вую и вторую группы 73 и 74 элементов И, первый с умматор 75 первый 76 и второй 77 регистры,.второй сумматор 78, элемент НЕ 79, информационный вход 80, с первого по четвертый управляющие входы 81-84, вход 85 cиIixpoнизaции и выход 86 блока 21 суммирования.

Устройство работает следующим образом.

50

Перед началом работы в блоки 1 па- яти заносятся соответствующие коэфициенты (1, j l 5,. „ ,п) матрицы А дз решаемой системы дифференциальных уравнений у Ау+В,в сумматоры 3 заносятся начальные значения производhНОЙ у (0)b. + У (0) , а в сум

маторы 9| - начальные значения переменной у j (О) В счетчик 43 заносится значение порядка решаемой системы (в дополнительном коде), на вход 48 подается значение интервала интег- рироваьшя, В регистр 13 заносит-, ся код шага интегрирования в виде значения номера разряда k, в котором содержится значащая единица. Сумматор 5 и счетчик 11 обнуляются,

Б регистр 76 блока 21 суммирования заносится код приращения производной на начальном шаге интегрирот вания, умноженный на константу 1/6, в регистр 77 блока 21 суммирования заносится код приращения производной на предыдущем шаге, умноженный на константу 1/24, Эти значения приращений производных вычисляются перед началом работы устройства по формулам:

ЛУо Т

(0)y() ;

Ajy- 24

24

А y(0-h)y(0-2h) ,

т.е. чтобы начать вычисления по методу Адамса, необходимо иметь значения искомой функции в двух предыдущих и текущей точках интегрирования,

В качестве начальных условий в регистр 69 блока 16 анализа заносится значение кода заданной точности искомого решения Е, Счетчики 42-45 блока 17 управления обнуляются.

Устройство начинает работать при поступлении сигнала на вход 18 устройства. Этот сигнал поступает на вход 63 блока 17 управления, проходит через элемент ИЛИ 36, устанавливает триггер 46 в единичное состояние.и запускает генератор 25 импульсов, с выхода которого импульсы проходят че- ,рез элемент И 26, открытый по второму входу от единичного выхода триггера 46, на вход счетчика 42,

В зависимости от кода в счетчике 42 дешифратор 34 формирует сигнал на соответствующем выходе. Так, по первому импульсу генератора 25 дешифратор 34 формирует сигнал на первом выходе, который поступает на выход 53 блока 17 и далее на вход группы элементов И 4; и синхровход сумматора 5, По этому сигналу содержимое сумматора 3 (начальное значение производной у) заносится в сумматор 5, По этому же сигналу, поступающему на вход 84 блока 21 суммирования, в сумматоре .78 формируется значение выражения

ЛУо

Ау-1

6 - 24 составляющие значения

5 .

поступают из регистров 76 и 77 блр- ка 21 суммирования соответственно на вход сложения и вход вычитания сумматора 78 блока 21 суммирования. Сигнал с выхода 53 блока J 7 управле ния устанавливает в нулевое состоят ние триггер 65 блока 17 управления, запрещая прохождение кодов через элементы И 22 и 24.

Далее формируется сигнал на выходе 66 блока 17 управления, этот сигнал поступает на вход элементов И 23 и синхровход сумматора 5, по этому сигналу к содержимому сумматора 5 (у ) прибавляется значение ( (

йУо

.

&У-1

-24

поступающее с блока 21 суммирования, т.е. в сумматоре 5 формируется значение

6

Лу-1 24

-) У о

Затем формируется сигнал на выходе 54, который, пройдя через элемент ИЛИ 39, поступает на выход.58 блока 17, По этому сигналу номер разряда в коде шага интегрирования ) заносится из регистра 13 через блок 12 элементов И в счетчик 11, а кодирующий элемент 6 вьг- деляет старший значащий разряд в коде значения

,; ..4ь.

йу-

и формирует на своем выходе код номера этого разряда г в соответствии с выражением 2 у, где г - минимальное целое число, для которого выполняется кэто неравенство. Знак

.значения yj проходит транзитом че-

.рез кодирующий элемент 6 на его зна- ковьй выход и далее на знаковый вход коммутатора 14 и управляющий вход сумматора 9., Сигнал с выхода 58 блока 17 управления поступает также на вход 83 блока 21 суммирования, в котором производится перезапись значения --г-- регистра 76 со сдвигом на два разряда вправо, в регистр 77, в котором фиксируется код - для

следующего шага интегрирования. На i выходе 55 блока 17 формируется сиг- , который поступает на синхро

5257.

вход сумматора 7, где происходит .сложение-кода k и кода г. Этот результат k+r эквиваленте произведению округленного значения

5

10

йу1

АУ. 24

/ о

,-k

-Y

2

15

20

25

на шаг интегрирования 2 , так как

(). 2-. -(-.Ч

/ 1 л

Код Лу-2 с выхода дешифратора 8 поступает на вход сумматора 9 и по сигналу на выходе 56 блока 17 добавляется с етом знака на управляющем входе сумматора 9 к начальному значению переменной у(0):

У,-, У;о + &У; у;о + 2 .

Так вычисляется первое приближение значения искомой переменной на первом шаге интегрированияе Одновременно из . содержимого сумматора 5 вычитается округленное значение 2 , которое формируется на выходе кодирующего элемента, т.е. в сумматоре получается остаток

I

R (у / + , J.I 2 У° 6 24 Л

-h

0

5

Сигнал на выходе 56 блока 17 добавляет единицы в два младших разряда счетчика 11, в котором получается . код k +3, что соответствует в значении 2 формированию кода величины h/8 2 1/8, Сигнал на выходе 57 блока 17 управления поступает на вход 82 блока 21 суммирования и устанавливает регистр 76 в нулевое состояние. Этот же сигнал на пятом выходе дешифратора 34 устанавливает в нулевое состояние триггер 46, по выходным сигналам которого закрывается элемент И 26 и от- крывается элемент- И 27, устанавливаг- ется в единичное состояние триггер 47, по выходному сигналу которого открывается элемент И 28 и импульсы с выхода генератора 25 поступают на вход счетчика 43, на выход 59, блока 17 и далее на управляющие входы бло-р ков 1 памяти и коммутатора 14, а через элемент задержки блока 52 - на выход 60 блока 17 и далее на синхро- входы сумматоров 3 и 5, По этим сигналам в течение п тактов производится последовательное считывание коэффициентов а;; из блоков 1 ; и выдача

0

5

Их на входы блоков 2 , на управляю- входы которых поступают последовательно с. коммутатора 14 коды прира- прений .1, знаки которых коммутато- lioM 14 по знаковому входу и выходу Коммутируются на управляющие входы сумматоров 3 и 5. Сдвиг коэффици- 61НТОВ ajl на блоках 2 сдвига на k-t-r разрядов вправо эквивалентен их Умножению на приращение Ду;, а на- йопление этих результатов в сумматорах 3 и 5 эквивалентно вычислению но- 1рьгх значений производных Ч . п

у ;, Yi

10

;j

ji значений прира щений производных n

I

: i

I.

Соответственно,

j Поскольку триггер 65 блока 17 управления находится в нулевом состоянии, то нулевой сигнал на выходе 67 блока 17 управления., поступая, на вход 81 блока 21 суммирова- ния, закрывает элементы И 74 и через элемент НЕ 79 открьшает эле- |менты И 73, разрешая прохождение 1кодов значений а|:&У| с выхода бло 1ка 2 сдвига на входы сумматора 75, где они складьшаются с предьщз тцим : значением S, поступающей с ;выхода регистра 76 При этом коды ;-значений подаются на входы сумматора 75 непосредственно, и со подвигом на 3,5, 7 ,,,, (2i-f 1) , где i ; 1,253,,,.,п, разрядов, , в сумматоре 75 вычисляются суммы S -f 7 (lisy-) причем фиксация этого

кода осуществляется синхросигналом, поступающим с выхода 60 блока 17 управления на вход 85 блока 21 суммирования, а умножение на константу 1/6 происходит за счет сдвигов на (2i+l) разрядов кода а;- й.у . К концу цикла считьшания коэффициентов а;; из блока 1 памяти в регистре 76 формируется значение суммы

5 к Z-a; , У у .

.

представляюп1ее собой приращение производной У,, умноженное на константу. 1/6, которое используется на следующем шаге интегрирования.

После сложения п импульсов счетчик 43 вырабатьшает сигнал переполнения, который сбрасывает триггер 47 в нулевое состояние, закрывая прохождение импульсов через элемент

И 28 и открывая элемент И 29, с выхода которого сигналы поступают на счетчик 44, Сигнал переполнения счетчика 43 устанавливает триггер 65 в единичное состояние, разрешая сигналом на выходе 67 блока 17 управления прохождение кодов через элементы И 22 с блоков 2 сдвига на входы сумматоров 3 и 5, а также прохождение кодов через элементы И 24 с выхода дешифратора 8 на вход сумматора 9, Кроме того, сигнал переполнения, пройдя через элемент ИЛИ 39 на выход 58 блока 17, разрешает кодирующему элементу 6 выделить и зашифровать

старший значащий разряд из кода приращения производной ДУ- . Вьзделенный номер старшего разряда г складьтает- ся с кодом k+3 с выхода.счетчика 11 . по сигналу на выходе 55, сформированнону дешифратором 35 блока J7 управ- . ления. Эта операция эквивалентна умножению округленного значения на величину h/8, т.е.

, h -( + S)

hy.

а поскольку с учетом интерполяционной формулы .Адамса прираццения искомых переменных вычисляются в виде

у; ь

то на выходе кодирующего элемента 6; формируется округленное значение

1 (

о которое используется для

J 7 ,i: .:

. . к

формирования значений &.у ; и - ,,

о. I

Этот код с выхода дешифратора 8| по- ступает на вход сумматора 9j и по сигналу на выходе 56, сформированному -дешифратором 35, добавляется непосредственно и со сдвигом влево на 2 разряда с учетом знака на управляющем входе сумматора 9 к предыдущему значению переменной у, т,е, вычисляет3ся новое значение у У| + о ЬДУ|.

Одновременно из содержимого суъшатора 5 вычитается значение Вьщеленного разряда 2 и формируется новый остаток от округления приращения производной „

Кроме того, вблоке 21 суммирования производитсявычисление приращения производной,умноженного на константу 1/6, т.е.значение S / k

1 А ( д.

+ 7 Z 3|juy. формируется путем Ь j, ) )

добавления к предыдущему значению суммы sj (содержимое регистра 76)

1 (s+«)

значения кодов ;: Д. у . , посту -J J J

пающих с выхода блока 2, сдвига на вход 80 блока 21 суммирования.и далее через злементы И 74, открытые сигналом с выхода 67 блока 17 управления (триггер 65.находится в единичном состоянии), на вход сумматора 75 со сдвигом на один разряд вправо

В этом же такте по сигналу на выходе 61 блока 17 с помощью блока 16 проверяется достижение заданной точности решения на каждом шаге интегрирования. Для этого коды приращений . с выходов дешифраторов 8: через

.элемент ИЛИ 15 поступают на входы сумматора 68 блока 16, в котором из сформированного максимального кода приращения У вычитается код задан- ной точности (Е) из регистра 69,- и знак результата выдается на выход 72 блока 16 и далее на вход 64 блока 17, где он открывает элемент И 31 (если знак отрицательный, , удовлетворяется заданная точность Е) или через эл1)мент НЕ 49

элемент И 30 (если Е) последнем случае сигнал с выхода элемента И 30 устанавливает триггер 47 в единичное состояние, переключая выходные сигналы генератора 25 через элемент И 28 на вход счетчика 43 и на выход 59 блока 17,

Затем аналогично производится вы-

.числение последующих значений прира- щения переменных у и приращения производных При этом триггер 65

блока 17 управления находится в единичном состоянии и разрешает прохождение сигнала с .выхода блока 4в через элемент И 22 и 24, через которые коды с выходов блоков 2 сдвига поступают , со сдвигом на один разряд влево на входы сумматоров 3 и 5, а коды с выходов дешифраторов 8 поступают со сдвигом на один разряд влево на входы сумматоров 9, Накапливающие сумматоры 3 и 9 и сумматоры 5 содержат комбинационную часть на

два внешних входа, для вьтолнения операции сложения кодов на их входах непосредственно и со на один разряд влево.с содержимым этих сумматоров, что аналогично умножению входного кода на коэффициент, 3, т.е. к содержимому суммато

ров 9 добавляется код

содержимому сумматоров 3

|-h Ау;

ляются

коды g h

И

J

ЛУ.

а к 5 добав- Если

удовлетворяется заданная точность

то сигнал с третьего выхода дешифратора 35.проходит через элемент И 31 на вход счётчика 45, добавляя к его содержимому единицу. На последующем такте в сумматоре 51 осуществляется вычитание из содержимого счетчика 45 (в котором формируется текущее значение количества обработанных шагов интегрирования Р решаемой системы уравнений) кода заданного числа шагов Pj. Знак результата этого вычитания поступает на вход элемента И 32 или через блок 50 на вход элемента И 33, Если разность . отрицательна, т,е, еще не закончено интегрирование системы урав- нений, сигнал с выхода дешифратора 35 проходит через элемент И 32 и далее через.элемент ИЛИ 36 на вход триггера 46, устанавливая его в единичное состояние, в результате соз-. даются условия для продолжения интегрирования на следующем шаге,

Если разность РТ положительна, т,е, интегрирование на заданном интервале закончено, то открьшается элемент И 33 и сигнал поступает на выход 62 блока.17 и далее на входы элементов И 10, через которые результат решения вьщается на выходы 19

устройства, а генератор 25 .импуль.сов прекращает свою работу.

На каждом (1+1)-м шаге интегрирования в устройстве в течение первых шести тактов находится первое приближение к решению по экстраполяци- онной формуле

У;,...Ь(У;, .Аж„А.).

55

.- 2

(k.n;:

причем производится округление прира. W U/ I

щения , h(

ili-j.-)

24

1

с точностью до старшего значащего разряда, а затем в последующие (п+3) I такта, повторенные несколько раз, i чтобы удовлетворить заданной точнос- I ти, производится уточнение решения по интерполяционной формуле

о П

j i

а:

,(s) -(bs+n)

у;;е:г2

причем остаток от округления R используется на следующей итерации вычис- ; лений по интерполяционной формуле.

На каждом шаге может выполняться равления подключен к выходу третьего

А12

сятый выход блока управления подключен к вторым входам элементов И групп с (3+п)-й по (2+2п)-ю, одиннадцатый выход блока управления подключен к вторым входам элементов И групп с третьей по (2+п)-ю и к вторым входам элементов И групп с С3+2п)-й по (2+Зп)-ю, при этом блок управления дополнительно содержит третий триг гер, причем в блоке управления десятый выход блока управления подключен к шестому выходу первого дешифратора, одиннадцатый выход блока уп

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения систем линейных дифференциальных уравнений | 1985 |

|

SU1252792A1 |

| Интерполятор | 1987 |

|

SU1413602A1 |

| Устройство для решения интегральных уравнений Фредгольма второго порядка | 1985 |

|

SU1295413A1 |

| Цифровой интегратор | 1975 |

|

SU661572A1 |

| Интерполятор | 1988 |

|

SU1541557A1 |

| Вычислительный блок матричного устройства для решения дифференциальных уравнений в частных производных | 1989 |

|

SU1605253A1 |

| Интегрирующая вычислительная структура | 1981 |

|

SU1257672A1 |

| Интегрирующее устройство | 1990 |

|

SU1727122A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| Вычислительный узел цифровой сетки | 1987 |

|

SU1501053A1 |

Изобретение относится к вычислительной технике и может быть использовано для решения систем дифференциальных уравнений, предназначено для работы в системах реального времени в составе специализированных процессоров или цифровых интегрирующих машин. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что устройство для решения систем линейных дифференциальных уравнений по авт. св. N 1252792 содержит с третьей по (3N+2) - ю группы элементов И (где N - порядок матрицы системы уравнений) и с первого по N - й блоки суммирования. Интегрирование решаемых уравнений в устройстве производится по модифицированному алгоритму экстраполяционно-интерполяционного метода Адамса. 1 з.п. ф-лы, 4 ил.

симум m и минимум одна итерация по интерполяционной формуле и в среднем требуется не более т/2 итераций

Формула изобретения

1, Устройство для решения систем линейных дифференциальных уравнений по автссв, № 1252792. отличающееся тем, чтр, с целью повышения быстродействия, оно содержит п блоков сзлммирования (где п - порядок матрицы коэффициентов решаемой сис- темы )и с третьей по (2+Зп)т-ю группы элементов И, причем седьмой, восьмой, шестой, пятый и первый выходы блока управления подключены соответственно к входам синхронизации, к первым, вторым, третьим и четвер- , тым управляющим входам блоков суммирования с первого по п-й, выход i-ro блока сдвига (где ,.„.,п) подклю- ч ен к информационному входу i-ro блока суммирования и к первым входам элементов И (2+1)-и группы, выход i-ro блока суммирования подключен к первым входам элементов И (2+п+ -|-1)-й группы, выходы которых подклю - чены соответственно к третьим информационным входам сумматоров i-й группы, выходы элементов И (2+i)-й группы подключены соответственно к входам синхронизации сумматоров i-й группы и к входам синхронизации накапливающих сумматоров i-й группы, выходы i-ro де1Ш1фратора подключены соответственно к первым входам элементов И (2+2п- i)-й группы, выходы , которых подключены соответственно к входам синхронизации накапливающих сумматоров ()-й группы, детриггера, вход установки в О и вход установки в 1 которого подключены соответственно к первому выходу первого дешифратора и к выходу переноса третьего счетчика,

2, Устройство по п, 1, о т л и - чающееся тем, что,каждьй блок суммирования содержит первую и вторую группы элементов И элемент

НЕ, первый и второй сумматоры, первый и второй регистры, причем в каж- дом блоке суммирования информационный вход блока суммирования подключен к первым входам элементов И первой и второй групп, выходы которых подключены соответственно к первому и второму информационным входам пер вого сумматора, выход которого подключен к информационному входу пер-

вого регистра, выход которого подключен к третьему информационному входу первого сумматора, к первому .информационному.входу второго сумматора и к информационному входу

второго регистра, выход которого .подключен к второму информационному входу второго сумматора, выход которого подключен к выходу блока суммирования, первый управляющий .вход

которого подключен ,к вторым входам элементов И.первой группы и к входу элемента НЕ, выход которого подклю- ,, чен к вторым входам элементов И второй группы, второй управляющий вход,

третий управляющий вход, четвертый управляющий вход и вход синхронизации блока суммирования подключены соответственно к ВХОДУ установки в О первого регистра, к входу записи-считывания второго регистра,к входу синхронизации второго сумматора и к входу записи-садтывания первого регистра.

«

кбя1,,5,И r.Sn.$ 23

./l,IZ

,9

.tf,2l

KSn. l-J б,Я

Ндлоку17 71

I

К5локу15

Н локу 17

Фиг.З Кбл.2

1

ок

К выходу 72 в л он а 17

| Устройство для решения систем линейных дифференциальных уравнений | 1985 |

|

SU1252792A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-30—Публикация

1988-04-29—Подача