соединен через элемент задержки с первым входом седьмого элемента И, с входом установки в О триггера состояния и с входом установки в 1 первого триггера управления, единичный и нулевой выходы которого соединены соответственно с вторым входом седьмого элемента И и с вторыми входами элементов И третьей группы, выходы которых соединены с тактовыми входами регистра маски, выход седьмо го элемента И соединен с единичным входом второго триггера управления, (единичный выход которого подключен к третьим входам второго и третьего эле-г ментов И, выход первого элемента ИЛИ

соединен с вторым входом первого элемента И и инверсным входом пятого элементами, прямой вход которого соединен с входом тактовых импульсов устройства, выход первого элемента И соединен с тактовым входом триггера состояния, единичный выход триггера режима соединен с четвертым входом второго элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, вход задания режима устройства соединен со счетным входом триггера режима,нулевой выход которого соединен с четвертым входом третьего элемента И,выходы группы элементов ИЛИ соединены с входами первого элемента ИЛИ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля параллельного двоичного кода на четность | 1981 |

|

SU999057A1 |

| Устройство для контроля параллельного кода на четность | 1983 |

|

SU1100626A1 |

| Устройство для контроля двоичного кода на четность | 1981 |

|

SU989558A1 |

| Устройство для прерывания программ | 1982 |

|

SU1072045A1 |

| Устройство для контроля кода на четность | 1988 |

|

SU1529224A1 |

| Устройство для контроля двоичного кода на четность | 1981 |

|

SU962955A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1233155A1 |

| Устройство для контроля последовательного двоичного кода | 1989 |

|

SU1644146A1 |

| Устройство для контроля параллельного кода на четность | 1981 |

|

SU1015387A2 |

Изобретение относится к вычислительной технике и может быть использовано для проверки на четность инфо мации, используемой при работе цифро вых вычислительных машин и систем Известно устройство для контроля параллельного двоичного кода на четность, содержащее элементы И, регист ры и счетный триггер Недостатком известного устройства является низкое быстродействие, обус |ловленное учетом положения единицы старшего разряда о Известно также устройство контроля двоичных кодов на четность, содержащее регистр, элементы И, ИЛИ и счетный триггер z ., Недостатками известного устройства являются его сложность и низкое быстродействие, обусловленное необходимостью опроса всех разрядов, которые находятся в единичном состоянии, а также необходимость специального обнуления соответствующих разрядов после окончания процесс контроля кода на четность, что в сво очередь замедляет готовность устройства к контролю следующей кодовой ко бинациИо Наиболее близким по технической сущности и достигаемому положительному эффекту к предлагаемому является устройство, содержащее регистр кода, регистр маски, первую, вторую, третью группы элементов И, группу элементов ИЛИ, первый, второй и третий элементы ИЛИ, триггер состояния, первый, второй, третий, четвертый, пятый, шестой и седьмой элементы И, элемент задержки, причем ()-ый выход регистра кода, где 1 Ifm, а m равно количеству разрядов контролируемого кода соединен с первым входом (2i-1)-ro элемента И первой группы элементов И, 21-ый выход регистра кода соединен с первым входом 2i-ro элемента И первой группы элементов И, выходы (21-1)-го и 2i-ro элементов И этой группы соединены с входами i-ro элемента ИЛИ группы элементов ИЛИ и соответственно с первыми входами (21-1)-го и 2i-ro элементов И второй группы элементов И, выходы которых соединены соответственно с входом установки в О и входом установки в 1 i-ro триггера регистра кодов, информационный выход I-го триггера регистра масок соединен с вторым инверсным входом (2i-l)-ro элемента И первой группы.элементов И и с вторым входом 2i-ro элемента И этой группы, выход j-ro элемента ИЛИ группы элементов ИЛИ, где j l-(m-l) соединен с (j+2)-MH инверсными входами элементов И первой группы элементов И, от ()-ro и до 2т-го, вход тактовых импульсов соединен с первым входом первого элемента И, выход которого соединен с вторыми входами элементов И второй группы элементов И, выход первого элемента ИЛИ соединен с счетным входом триггера состояния, единичный выход которого соединен с первым входом вт рого элемента И, а нулевой - с первым входом третьего элемента И, выхо третьего элемента И соединен с входом рторого элемента ИЛИ, выход ко- торого является контрольным выходом устройства з Недостатком известного устройства является низкое быстродействие, обус ловленное возможностью работы только с четной маской. Значение разрядов кода маски М для пакета кодов К выбирается из условия ,есАи| ef. а VCfei.eVie.miM. М 3 О.еаи I еТ: - , у, . где Cji - значение j -го разряда i -го кода пакета К; m - число разрядов в коде; J - длина nakcTa; 1 . причем VCfM.e Л .Q... Поэтому в ряде случае оптимальная маска М(.|,для пакетов кодов не удовлетворяет условию (2.), а является б нечетной, т,ер 53 ЛЛ. .( Для того, чтобы организовать конт роль на четность таких пакетов кодов (т.е. пакетов, у которых Мд,, является нечетной), необходимо преобразова оптимальную маску в четную, а именно изменить значение какого-либо разряда, чтобы эта маска стала четной. Эт ведет к увеличению общего числа единиц в таком пакете кодов после маски рования его модифицированной маской, Причем увеличение числа единиц тем больше, чем больше ассимметрия числа единиц и нулей в одноименных разряда кодов пакета (т„е, где чисаЮ нулей и единиц не приближается к 50) и за мена значения какого-либо разряда на противоположное в значительной степени не удовлетворяет условию (1), Следовательно, увеличение числа единиц ведет к уменьшению быстродействия устройства, так как быстродействие известного устройства определя ется числом единиц в контролируемом коде после маскирования. Цель изобретения повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для контроля параллельного двоичного кода на четность, содержащее регистр кода, регистр маски, первую, вторую и третью группы элементов И, группу элементов ИЛИ, первый, второй и третий элементы .ИЛИ, триггер состояния, первый; второй, третий, четвертый, пятый, шестой и седьмой элементы И и элемент задержки, причем (2(-1)-ый выход регистра кода {где1 - 1 -т, а m равно количеству разрядов контролируемого кода) соединен с прямым входом (Zi-lJ-ro элемента И первой группы, выход регистра кода соединен с первым входом 2 -го элемента И первой группы, выходы -го и элементов И первой группы соединены соответственно с первым и вторым входами -го элемента ИЛИ группы и с первыми входами соответственно (.i-l)-ro и ,2i,-ro элементов И второй группы,выходыкоторых соединены соответственно с входами установки в О и 1 -го разряда регистра кодов, выход -го разряда регистра масок соединен с первым инверсным входом (.i-l)-ro элемента И первой группы и с вторым уходом 2i-го элемента И первой группы, выход -го элемента ИЛИ группы (где) - 1 -(w-l) соединен с ( j +1 -ми инверсными входами элементов И первой группы, от (.j+1)-ro до 2Ш-ГО, вход тактовых импульсов устройства соединен с первым входом первого элемента И, выход которого соединен с вторыми входами элементов И второй группы, выход первого элемента ИЛИ соединен со счетным входом триггера состояния, единичный и нулевой выходы которого соединены с первыми входами соответственно второго и третьего элементов И, выход третьего элемента И соединен с первым входом второго элемента ИЛИ,выход которого является контрольным выходом устройства, введены триггер ремима, первый и второй триггеры управления, причем информационный вход устройства соединен с информационными входами регистров кодов и маски и с входами третьего элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И, выход пятого элемента И соединен с тактовый входом регистра кодоо, с первыми входами элементов И третьей группы, с вторыми входами второго, третьего и четвертого элементов И и с первым входом шестого элемента И, второй вход которого соединен с входом Конец пакета устройства, выход шестого элемента И соединен с входом установки в О первого и второго триггеров управления, выход четвертого элемента И соединен через элемент задержки с первым входом седьмого элемента И, с входом установки в О триггера состояния и с входом установки в 1 первого триггера управления, единичный и нулевой выходы которого соединены соответственно с вторым входом седьмого элемента И и с вторыми входами элементов И третьей группы,выходы которых соединены с тактовыми входами регистра маски, выход седьмого элемента И соединен с единичным входом второго триггера управления, единичный выход которого подключен к третьим входам второго и третьего элементов И, выход первого элемента ИЛИ соединен с вторым входом первого элемента И и инверсным входом ;пятого элемента И, прямой вход которого соединен с входом тактовых импульсов устройства, выход первого элемента И соединен с тактовым входом триггера состояния, единичный выход триггера режима соединен с четвертым входом второго элемента И, выход которого соединен с вторым входом вто рого элемента ИЛИ, вход задания режима устройства соединен со счетным входом триггера режима, нулевой выход которого соединен с четвертым вхо дом третьего элемента И, выходы груп пы элементов ИЛИ соединены с входами первого элемента ИЛИ,. Сущность изобретения состоит в по вышении быстродействия устройства пу тем обеспечения возможности обработк пакетов кодов, у которых оптимальной может быть как четная, так и нечетна маска Четной называется маска, у которой сумма числа единиц четна, а нечетной, соответственно, - у которой сумма числа единиц нечетна„ В зависимости от вероятностных характеристик пакета обрабатываемых кодов (числ единиц и нулей в одноименных разрядах кодов пакета) маска, являющаяся оптимальной для данного пакета, может оказаться нечетной Значение разрядов оптимальной мас ки Мрд вычисляется по формуле (О без ограничения накладываемого выражением (2) , Полученная таким образом маска М и хранимая в специальном регистре после поступления каждого контролируемого кода К складывается поразрядно с поступившим кодом по модулю два, В формируемом коде число единиц будет существенно меньше, чем в исходном коде, а, следовательно, определение четности кодов будет происходить За меньшее число тактов Использование оптимальной маски Мдр(как четной, так и нечетной) для каждого пакета кодов позволяет для подсчета числа единиц получать коды, содержащие минимально возможное число единиц, что позволяет повысить быстродействие устройства и исключить влияние некоторых вероятностных характеристик пакетов кодов на быстродействие устройства о Введение триггера режима и подключение его единичного выхода к входу второго элемента И, его выхода - к входу второго элемента ИЛИ и подключе ние нулевого выхода триггера режима к входу третьего элемента И позволяет управлять выдачей результата контроля на выход устройства Состояние триггера контроля зависит от контролируемого кода„ Если число единиц в коде нечетно, то в конце контроля |триггер контроля остается в единичном состоянии и наоборот,. Это при условии использования четной маски, так как при сложении ее с четным кодом по модулю два на выходе сумматора сигнал равен нулю. Если используется нечетная маска, то при сложении ее с четным кодом по модулю два триггер контроля окажется в единичном состояний. Поэтому путем изменения состояния гера режима в зависимости от используемой маски (четная, нечетная комму тируются соответствующие выходы три1- гера контроля и на контрольном выходе устройства формируется результат контроля: 1 - проверяемый код нечетный, О - проверяемый код четный Введение первого триггера управления и подключение его нулевого выхода к управляющим входам третьей группы элементов И позволяет осуществлять управление записью информации в регистр маски с, Введение второго триггера контроля и подключение его единичного выхода к соответствующим входам второго и третьего элементов И разрешает выд чу информации с триггера контроля после записи в регистр кодов первого проверяемого кода пакета, а также за прещает выдачу информации с триггера контроля до поступления в регистр кодов первогр кода очередного -контро лируемого пакета кодов, Подключение входной шины устройства к информационным входам 1)-три1- геров регистра, подключение выхода первого элемента ИЛИ и генератора та товых импульсов к входам пятого элемента И, а выхода этого элемента И к управляющим входам триггеров обоих регистров позволяет осуществить информацию записи маски в регистр масок и записи контролируемых кодов в устройство. Подключение выхода пятого элемента И через четвертый элемент И, элемент задержки к входу установки в О триггера контроля позволяет устанавливать этот триггер в исходное состо яние после контроля очередного кода. Подключение выхода пятого элемента И через четвертый элемент И и эле мент задержки к входу установки в 1 первого триггера управления и дополнительно через седьмой элемент И к входу установки в 1 второго тригге ра управления, а через шестой элемент И к входам установки в О обоих триггеров позволяет управлять записью информации в регистр масок, сч тыванием результата контроля и установкой триггеров контроля в исходное состояние после контроля очередно го пакета кодов„ Таким образом, введение вышеописанных элементов и связей позволяет повысить быстродействие устройства путем уменьшения числа единиц в коде маскированием поступающих кодов оптимальной для каждого пакета кодов мае кой как четной, так и нечетной , На чертеже представлена функционал ная схема устройства для контроля параллельных двоичных кодов на четность Устройство содержит вход 1 информации устройства, регистр 2 кода, пер вую труппу 3 элементов И, вторую группу элементов И, группу 5 элемен тов ИЛИ, первый элемент ИЛИ 6, триггер 7 состояния, второй элемент И 8, третий элемент И 9, второй элемент ИЛИ 10, триггер 11 режима, третью группу 12 элементов И, регистр 13 маски, первый элемент И 1А, пятый элемент И 15, третий элемент ИЛИ 16, четвертый элемент И 17, шестой элемент И 18, элемент 19 задержки, пе вый триггер 20 управления, седьмой элемент И 21, второй триггер 22 управления, вход 23 Конец пакета устройства, выход 2 контроля устройства, вход 25 тактовых импульсов и вход 26 задания режима о Регистр 2 предназначен для хранения кодов, контролируемых на четность и поступающих из информационного канала, регистр 13 - для хранения кода маски проверяемого пакета кодов. Запись информации в регистры осуществляется только при наличии очередного тактового сигнала с выхода пятого элемента И на тактовых С-входах1) -триггеро.в регистра Это позволяет устранить влияние помех на входе и на работу устройства в целом , Тактовые сигналы поступают на входы ре гистра масок через третью группу элементов И 12, которая управляется первым триггером 20 управления. После записи маски в регистр 13 этим же тактовым импульсом триггер 20 переводится в единичное состояние и запирает группу элементов И 12, Таким образом, в регистре 13 в течение всего цикла проверки предлагаемого пакета кодов хранится маска И данного пакета. Только при наличии информации на входе возможна установка в единичное состояние триггеров управления и установка в исходное состояние триггера 7 так как при отсутствии информации закрыт четвертый элемент И 17 Выходы регистра 2 кодов соединены с входами соответствующих элементов И первой группы элементов И 3 вторые входы которых соединены с аналогичными выходами регистра 2 и входами регистра 13 маски Первая группа элементов И 3 и груп па элементов ИЛИ 5 представляют собой сумматор по модулю два, все выходы которого объединены с помощью первого элемента ИПИ 6. Если после сложения по модулю два каких-либо разрядов кода на выходе элементов ИЛИ группы элементов ИЛИ 5 появится единичный сигнал, то он через первый элемент ИЛИ 6 запишется в триггер 7 при наличии на его С-входе управляющего сигнала. Этот же сигнал пройдет и на вьход группы элементов И 4 и поступит на соответствующий вход регистра 2 кодов, состояния триггеров регистра 2 меняются таким образом, чтобы на выходе элементов И группы элементов И 3, которым соответствует единичная информация, появился О. Выходы элементов ИЛИ группы элементов ИЛИ 5 соединены с инверсными входами группы элементов ИЗ, нто позволяет проводить последователь-ное поразрядное сравнение разрядов кода и маски и последовательно менять состояние триггера 7. После проверки всех разрядов кода на выходе элемента ИЛИ 6 появляется нулевой сигнал, который коммутирует поступление тактовых импульсов в схему, закрывая первый элемент И 1 и открывая пятый элемент И IS Триггер 1.1 режима находится в состоянии, соответствующем маске данного пакета, единичном, если маска четная, и нуле вом - в противном случае, Сигнал с выхода триггера 11 открывает (закрывает) элементы И 8 и 9 С выхода второго триггера 22 управления поступают на элементы И 8 и 9 разрешающие сигналы После окончания контроля кода очередной тактовый импульс открывает оба элемента И 8 и 9 и в зависимости от состояния триггера 11 режима на вхо устройства поступает соответствующая информация с триггера 7 Если маска четная и код четный, то открыт элемент И 8 и на выходе 2 устройства появляется нулевой сигнаЛо Если код нечетный, - появляется Т„ Если маска нечетная, т открыт элемент И 9 и на выходе устройства сигнал равен нулю, если код четный, и единица,- если-нечетный. Сигнал, разрешающий считывание результата, проходит одновременно и на управляющие входы регистра 2 кодов и разрешает запись очередного кода контролируемого пакета. По окончании контроля всех кодов пакета на входе 23 устройства появля ется сигнал, которым триггеры 20 и 2 управления устанавливаются в исходно состояние о Открывается группа элемен то.в И 12 и очередным тактовым импуль сом в регистры 2 и 13 устройства зап сывается код маски очередного пакета Предлагаемое устройство работает следующим образом В исходном состоянии триггеры обо их регистров 2 и 13, триггер 7 состояния, первый и второй триггеры 20 1 9 . 10 и 22 управления находятся в единичном состоянии, если маска четная и в нулевом - при нечетной маске, третья группа элементов И 12 открыта разрешающим сигналом с нулевого выхода первого триггера 20 управления, элемент И 15 открыт и с его выхода тактовые импульсы поступают в устройство, элементы И 8 и 9 закрыты. Устройство готово к приему пакета кодов. После включения устройства на вход поступают тактовые импульсы, которые проходят на выход элемента И 15f так как сигнал на выходе первого элемента ИЛИ 6 равен нулю, и поступает на управляющие входы триггеров регистра кодов, через открытую группу элементой И на управляющие входы триггеров регистра маски, на второй вход четвертого элемента И 17, первый вход шестого элемента И 18 и вторые управ ляющие входы второго и третьего элементов И 8 и 9о До тех пор, пока информация на входе 1 устройства отсутствует, в регистры 2 и 13 ничего не записывается. Первым в пакете кодов передается код маски„ Он поступает на входы информации обоих регистров 2 и 13 и записывается в них после поступления очередного тактового импульса на управляюи4ие входы регистров 2 и 13 П5явление информации на входе фиксируется третьим элементом ИЛИ 16, на выходе которого появляется единичный сигнал, который поступает на первый вход четвертого элемента И 17 и открывает его для прохождения того же тактового импульса, который осуществляет запись информации в регистры 2 и 13. Единичный сигнал с выхода этого элемента И 17 проходит через элемент 19 задерх ки и поступает на вход установки в О триггера 7 состояния, подтверждая его нулевое состояние на вход седьмого элемента И 21 и устанавливает в единичное состояние первый триггер 20 управления. Длительность задержки сигнала элементом 19 задержки выбирается исходя из времени, необходимого для надежной записи кода маски & регистры 2 и 13, а длительность этого сигнала выбирается меньшей, чем время переключения в единичное состояние первого три1- гера 20 управления. Следовательно, сигнал, поступивший на вход седьмого элемента И 21, на его выход не пройдет, и второй триггер управления останется в исходном нулевом состоянии В результате изменения состояния первого триггера управления на противоположное закрывается третья группа элементов И 12, Так как в регистрах 2 и 13 .записана одинаковая- информация - код маски, то в результате поразрядного сравнения этого кода по модулю два, которое осуществляется элементами И 3 l 3o2fti и ИЛИ формируется нулевой кодо. Этот код поступает на входы первого элемента ИЛИ 6 и выходной сигнал этого элемента по-прежнему остается нулевым, В результате этого очередной второй тактовый импульс проходит на выход элемента И 15 и поступает на управляющие входы только регистра 2 кодов, так как третья группа элементов И 12 закрыта нулевым сигналом с выхода первого триггера 20 управления, записывая в него очередной код пакета, поступивший на вход 1 устройства В регистре 2 кодов теперь за писан первый код пакета кодов, а в(регистре 13 масок осталась записанной |маска пакета Одновременно второй тактовый импульс проходит через откры тый четвертый элемент И 17, элемент 19 задержки, открытый к этому времени седьмой элемент И 21 и устанавливает в единичное состояние второй триггер 22 управления, который своим единичнымсигналом, поступающим на входы элементов-И 8 и 9, готовит цепи прохождения сигналов контроля с выхода триггера 7 состояния на выход устройства 2k контроля. После записи контролируемого кода в регистр 2 просходит его поразрядное сравнение с -кодом маски на элементах И и ИЛИ 5о1-5от. Если проверяемый i -ый разряд поступившего кода не совпадает с одноименным разрядом кода маски, то на выходе элемента.ИЛИ группы элементов ИЛИ 5 появляется единичный сигнал который поступает на соответствующий /(-ый вход первого элемента ИЛИ 6 и запрещает поразрядное сравнение следующих за -ым разрядом кода. Единичный выходной сигнал с первого элемента ИЛИ 6 закрывает пятый элемент И 15 и открывает первый элемент И Поэтому очередной тактовый импульс (третий) проходит на выход первого элемента И , устанавли109912 вает триггер 7 состояния в единичное состояние и открывает элементы И второй группы элементов И А, На выходе элементов И ) и .,2,1 второй группы элементов И 4 появляются соответствующие сигналы, которые поступают HaRS-входы f -го триггера регистра 2 кодов соответственно и устанавливают этот i -ый триггер в состояние, совпадающее с состоянием л -го триггера регистра 13 масок, в котором записан одноименный разряд кода маски, В результате этого выходной сигнал элемента ИЛИ 5 становится равным О и, воздействуя на соответствующие входы элементов И 3.(24+1), 3-(2i+2) разрешает поразрядно е сравнение по модулю два {4+1)-ых разрядов кода и маски „ Если состояния этих различны, то на выходе элемента ИЛИ 5 (+1) появляется единичный сигнал, что приводит к поступлению единичного сигнала на вход Т-триггера 7 состояния о После поступления очередного тактового импульса триггер 7 состояния переключится в противоположное состояние, а триггер 2(4+1)-го регистра 2 кодов - в состояние, совпадающее с триггером 13(+1)-го регистра 13 кода маски В противном случае /при совпадении ( разрядов единичный сигнал на выходе элемента ИЛИ 5(+1) группы элементов ИЛИ 5 не формируетел и разрешается сравнение значений (+2}-ьлк разрядов контролируемого кода и маски, процесс протекает в схеме ДО тех пор, пока состояние всех разрядов регистра 2 кодов не совпадает с соответствующими разрядами регистра 13 масоко Необходимое для этого число тактов равно числу несовпадающих разрядов регистров 2 и 13 или, другими словами, числу единиц в коде, полученном в результате сложения по модулю два поступившего в регистр кодов кода пакета и кода маски. После окончания процесса сравнения кодов на выходе первого элемента ИЛИ 6 появится нулевой сигнал, в результате чего очередной тактовый импульс пройдет через пятый элемент И 15 и поступит на входы элементов И 8 и 9, которые управляются триггером 11 режимаJ.Если при обработке рассматриваемого пакета кодов используется четная маска,,то триггер 11 режима установлен в единичное состояние, и, следовательно, единичный сигнал поступит на вход второго элемента И 8, а нулевой - на вход элемента И 9 Если после окончания (сонт роля триггер 7 состояния окажется в нулевом состоянии, то его единичный выход будет равен О и на выход 2 устройства единичный сигнал /очередной тактовый импульс с выхода элемсн та И 15) не пройдет, что свидетельствует о четности поступившего кода. В противном случае на выходе 2k устройства появится единичный сигнал Если же при обработке пакета кодов используется нечетная маска, то триггер режима 11 устанавливается в нулевое,состояние и откроется элемент И 9о В этом случае по окончании контроля, если, поступивший код четный, триггер 7 состояния должен оказаться в единичном состоянии, и, следовательно, единичный сигнал с вы хода триггера 7 на выход 2k устройства не пройдет, так как элемент И 8 закрыт нулевым сигналом с единичного выхода триггера 11 . В противном случае код нечетныйj на всех входах третьего элемента И 9 окажется единичный сигнал, что приведет к появлению единичного сигнала и на выходе второго элемента ИЛИ.10, т.е на выходе 2k контроля устройствао В предлагаемом устройстве такт выдачи результата совмещен с тактом приема очередного кода пакета, что позволяет еще больше повысить быстро действие устройства Поэтому тот же тактовый импульс с выхода пятого эле мента И 15 которым управляется выдача результата контроля предыдущего проверяемого кода, поступает на управляющие входы регистра кодов и осу ществляет запись очередного кода в р гистр 2., Кроме того, пройдя через элемент И 17 и элемент 19 задержки, этот импульс устанавливает в исходное нулевое) состояние триггер 7, готовя его к следующему циклу работы. При совпадении кода пакета с кодом маски первым тактовым импульсом он записывается в регистр 2 кодов. Так как содержимое регистров 2 и 13 одинаково, на выходе первого элемента ИЛИ 6 единичный сигнал не появится и очередной тактовый импульс пройдет на выход пятого элемента И 15 и/запишет очередной код пакета в регистр кодово При этом, если используется четмая маска, на выходе 2k устройства информация отсутствует. Если же используется нечетная маска, то третий элемент И 9 будет открыт и следующий тактовый импульс, который запишет о редной код пакета в регистр 2, пройдет на выход элемента И 9, и на выходе 2k устройства появится единичный сигнал, свидетельствующий о нечетности проверенного кода В дальнейшем устройство работает аналогично вышеописанному, После обработки пакета кодов на вход 23 устройства поступает сигнал Конец пакета, по которому очередной тактовый импульс с выхода элемента И 15 установит триггеры 20 и 22 управления в исходное (нулевое) состояние, подготавливая тем самым устройство к обработке очередного пакета кодов. Так как регистры 2 и 13 состоят из управляемых II -триггеров, нет необходимости устанавливать эти регистры в исходное состояние ибо предыдущее состояние триггеров регистра не влияет на запись последующей информации. В таблице показан пакет контролируемых кодов.

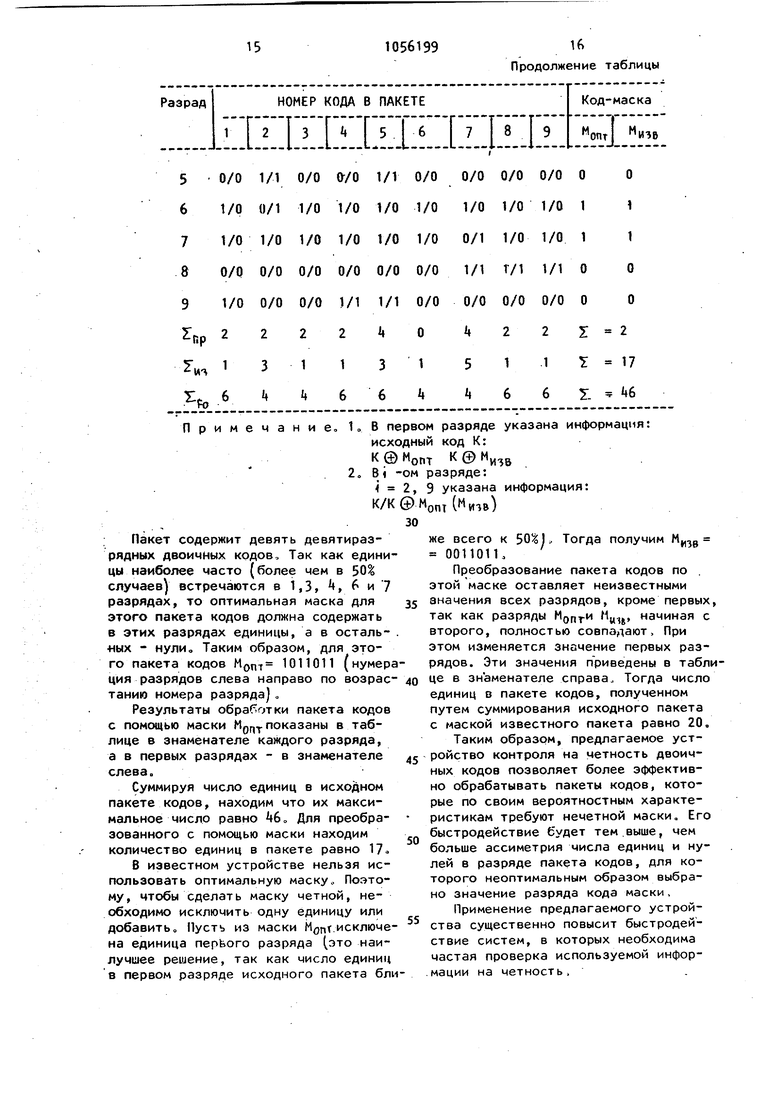

О/О1/1О/Оа/о1/1о/оо/оо/оо/ооо

1/00/11/01/01/01/01/01/01/011

1/01/01/01/01/01/00/11/01/011

о/оо/оо/оо/оо/оо/о1/1г/11/1оо

1/0о/оо/о1/11/1о/оо/оо/оо/ооо Пакет содержит девять девятиразрядных двоичных кодово Так как едини цы наиболее часто (более чем в 50% случаев) встречаются в 1,3, , 6 и 7 разрядах, то оптимальная маска для этого пакета кодов должна содержать в этих разрядах единицы, а в остальных - нули. Таким образом, для этого пакета кодов MQj,7 1011011 (нумер ция разрядов слева направо по возрас танию номера разряда), Результаты обработки пакета кодов с помощью маски HQ показаны в таблице в знаменателе каждого разряда, а в первых разрядах - в знаменателе слева. Суммируя число единиц в исходном пакете кодов, находим что их максимальное число равно 46 о Для преобразованного с помощью маски находим количество единиц в пакете равно 17 В известном устройстве нельзя использовать оптимальную маску о Поэтому, чтобы сделать маску четной, необходимо исключить одну единицу или добавить. Пусть из маски Мдпг.исключе на единица первого разряда (это наилучшее решение, так как число единиц в первом разряде исходного пакета бл

исходный код К:

к ® MQOT к @ My,g

Bi -ом разряде:

2, 9 указана информация:

К/К©МопДМи,в) 50 „ Тогда получим М же всего к 0011011. Преобразование пакета кодов по этой маске оставляет неизвестными значения всех разрядов, кроме первых, так как разряды uu начиная с второго, полностью совпа,1ают, При этом изменяется значение первых разрядов. Эти значения приведены в таблице в знаменателе справа. Тогда число единиц в пакете кодов, полученном путем суммирования исходного пакета с маской известного пакета равно 20, Таким образом, предлагаемое устройство контроля на четность двоичных кодов позволяет более эффективно обрабатывать пакеты кодов, которые по своим вероятностным характеристикам требуют нечетной маски. Его быстродействие будет тем.выше, чем больше ассиметрия числа единиц и нулей в разряде пакета кодов, для которого неоптимальным образом выбрано значение разряда кода маски, Применение предлагаемого устройства существенно повысит быстродействие систем, в которых необходима частая проверка используемой информации на четность.

Авторы

Даты

1983-11-23—Публикация

1982-07-09—Подача