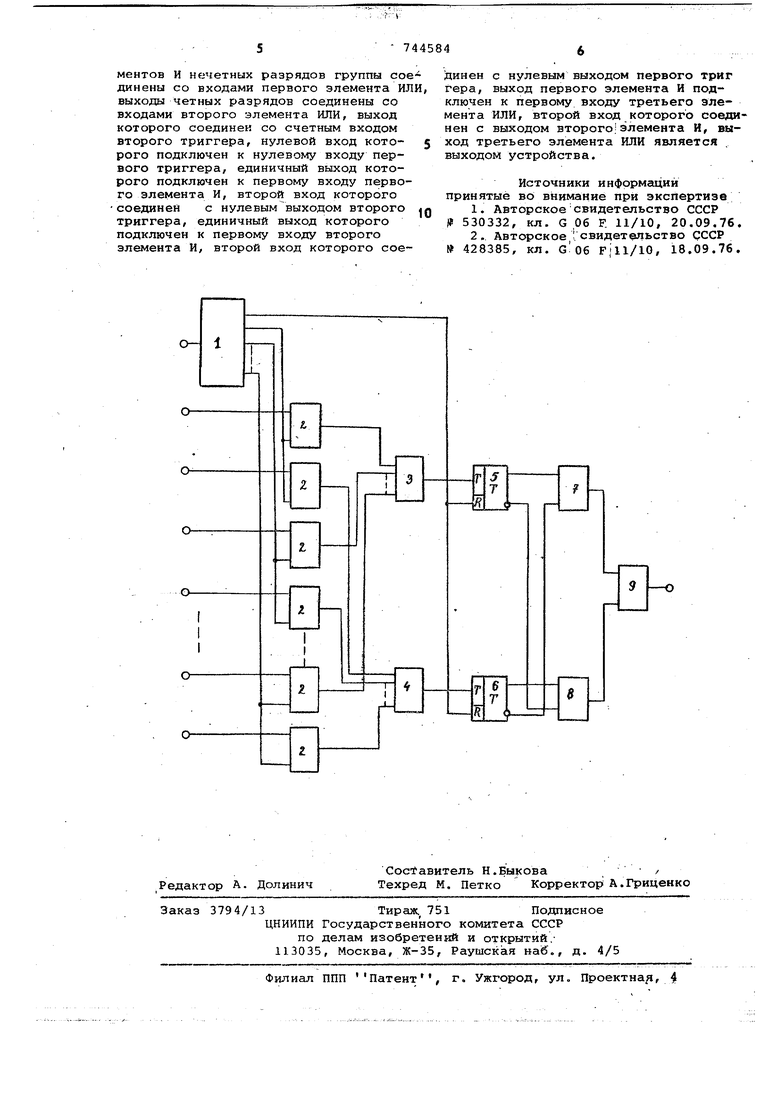

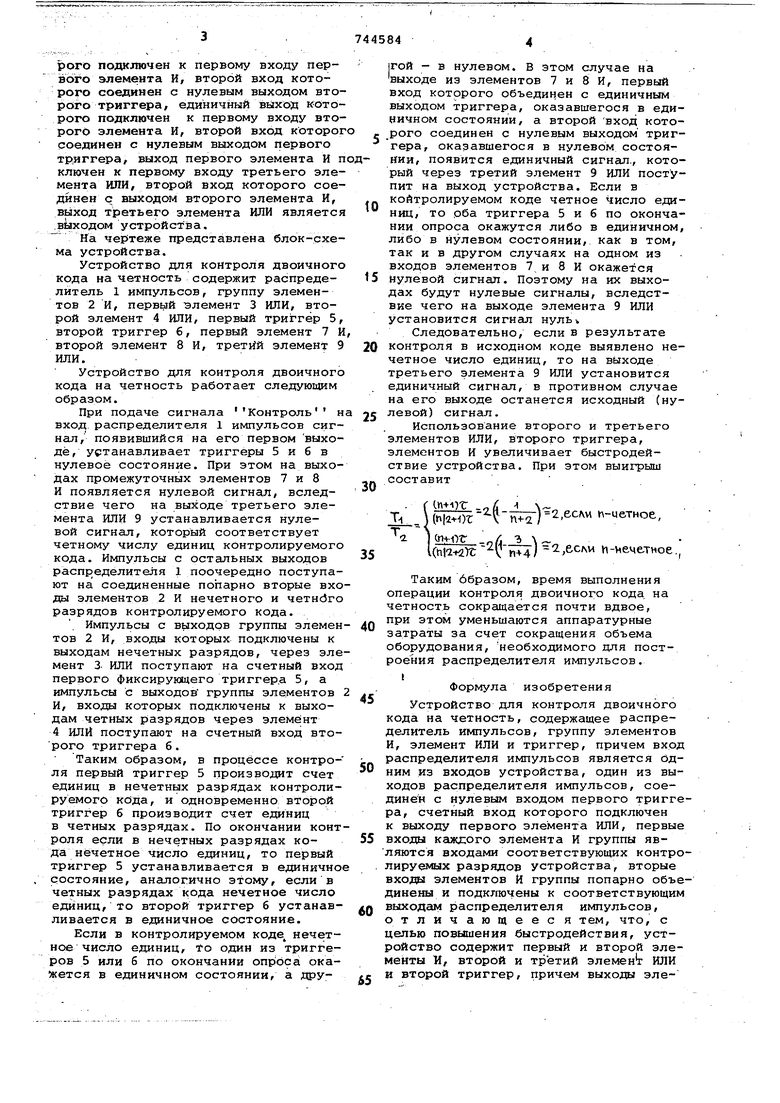

рого подключен к первому входу первого элемента И, второй вход которого соединен с нулевым выходом вто рого триггера, единичный выход кото рого подключен к первому входу вто рого элемента И, второй вход которо соединен с нулевым выходом первого триггера, выход первого элемента И ключен к первому входу третьего эле мента ИЛИ, второй вход которого сое динен с выходом второго элемента И, вьзход третьего элемента ИЛИ являетс .выходом устройства. На чертеже представлена блок-схе ма устройства. Устройство для контроля двоичног кода на четность содержит распределитель 1 импульсов, группу элементов 2 И, первый элемент 3 ИЛИ, второй элемент 4 ИЛИ, первый триггер 5 второй триггер б, первый элемент 7 второй элемент 8 И, третий элемент ИЛИ. Устройство для контроля двоичног кода на четность работает следующим образом. При подаче сигнала Контроль вход распределителя 1 импульсов сигнал/ появившийся на его первом выходе, устанавливает триггеры 5 и 6 в нулевое состояние. При этом на выходах промежуточных элементов 7 и 8 И появляется нулевой сигнал, вследствие чего на выходе третьего элемента ИЛИ 9 устанавливается нулевой сигнал, который соответствует четному числу единиц контролируемого кода. Импульсы с остальных выходов распределителя 1 поочередно поступают на соединенные попарно вторые вхо ды элементов 2 И нечетного и четнсЗго разрядов контролируемого кода. Импульсы с выходов группы элемен тов 2 И, входы которых подключены к выходам нечетных разрядов, через эле мент 3- ИЛИ поступают на счетный вход первого фиксирующего триггер.а 5, а импульсы с выходов группы элементов И, входы которых подключены к выходам четных разрядов через элеме нт 4 ИЛИ поступают на счетный вход второго триггера 6. Таким образом, в процессе контроля первый триггер 5 производит счет единиц в нечетных разрядах контролируемого кода, и одновременно второй триггер б производит счет единиц в четных разрядах. По окончании конт роля если в нечетных разрядах кода нечетное число единиц, то первый триггер 5 устанавливается в единично состояние, аналогично этому, если в четных разрядах кода нечетное число единиц, то второй триггер б устанавливается в единичное состояние. Если в контролируемом коде нечетное число единиц, to один из триггеров 5 или 6 по окончании опрос окажется в единичном состоянии, а Другой - в нулевом. В этом случае на выходе из элементов 7 и В И, первый вход которого объединен с единичным выходом триггера, оказавшегося в единичном состоянии, а второй вход кото рого соединен с нулевым выходом триггера, оказавшегося в нулевом состоянии, появится единичный сигнал., который через третий элемент 9 ИЛИ поступит на выход устройства. Если в коАтролируемом коде четное число единиц, то оба триггера 5 и б по окончании опроса окажутся либо в единичном, либо в нулевом состоянии, как в том, так и в другом случаях на одном из входов элементов 7 и 8 И окажется нулевой сигнал. Поэтому на их выходах будут нулевые сигналы, вследствие чего на выходе элемента 9 ИЛИ установится сигнал нуль Следовательно, если в результате контроля в исходном коде выявлено нечетное число единиц, то на выходе третьего элемента 9 ИЛИ установится единичный сигнал, в противном случае на его выходе останется исходный (нулевой) сигнал. Использование второго и третьего элементов ИЛИ, второго триггера, элементов И увеличивает быстродействие устройства. При этом выигрыш составит ( ч7Т 0/1 -1 NЛ±. ( ri) 1 -цетное, 2. ) ()Г /. 5 „ (( Тнч/ -.ьсли и-иеметмое,, Таким ббразом, время выполнения операции контроля двоичного кода на четность сокргицается почти вдвое, при этом уменьшаются аппаратурные затраты за счет сокращения объема оборудования, необходимого для построения распределителя импульсов. Формула изобретения Устройство для контроля двоичного кода на четность, содержащее распределитель импульсов, группу элементов И, элемент ИЛИ и триггер, причем вход распределителя импульсов является бдним из входов устройства, один из выходов распределителя импульсов, соединен с нулевым входом первого триггера, счетный вход которого подключен к выходу первого элемента ИЛИ, первые входы каждого элемента И группы являются входами соответствующих контролируемых разрядов устройства, вторые входы элементов И группы попарно объединены и подключены к соответствующим выходам распределителя импульсов, отличающееся тем, что, с целью повышения быстродействия, устройство содержит первый и второй элементы И, второй и третий элемент ИЛИ и второй триггер, причем выходы элементов И нечетных разрядов группы соединены со входами первого элемента ИЛИ, выходы четных разрядов соединены со входами второго элемента ИЛИ, выход которого соединен со счетным входом второго триггера, нулевой вход кото- § рого подключен к нулевому входу первого триггера, единичный выход которого подключен к первому входу первого элемента И, второй вход которого соединен с нулевым выходом второго IQ триггера, единичный выход которого подключен к первому входу второго элемента И, второй вход которого соединен с нулевым выходом первого триг гера, выход первого элемента И подключен к первому входу третьего элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, выход третьего элемента ИЛИ является выходом устройства.

Источники информации принятые во внимание при экспертизе

1.Авторскоесвидетельство СССР

if 530332, кл. G Об F. 11/10, 20.09.76.

2,Авторское tсвидетельство СССР

№ 428385, кл. G Q6 FJll/lO, 18.09.76,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля двоичного кода на четность | 1981 |

|

SU962955A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1056199A1 |

| Устройство для контроля параллельного кода на четность | 1979 |

|

SU883910A1 |

| Датчик сообщений | 1985 |

|

SU1282348A1 |

| Устройство для контроля двоичного кода на четность | 1981 |

|

SU989558A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1981 |

|

SU999057A1 |

| Устройство для контроля параллельного кода на четность | 1987 |

|

SU1413632A1 |

| Устройство для контроля кода на четность | 1988 |

|

SU1529224A1 |

| Устройство для сравнения числа единиц в двоичных кодах | 1988 |

|

SU1509867A2 |

| Устройство для обнаружения и исправления ошибок | 1980 |

|

SU938415A1 |

О

Авторы

Даты

1980-06-30—Публикация

1978-04-10—Подача