Изобретение относится к вычисли тельной технике и может использова ся для Обнаружения ошибок нечетной кратности при передаче и хранении данных в двоичном коде. Известно устройство для контроля четности информации, содержащее три гер, два элемента И, регистр сдвига, группу элементов ИЛИ, число которых равно половине количества раз рядов контролируемого кода, группу двухвходовых элементов и, группу трехвходовых элементов ИЛИ и элемент задержки Г1. Недостатком устройства является .очень низкое быстродействие. Наиболее близким по технической сущности к предлагаемому является . асинхронное устройство для определе ния четности.информации, содержащее регистр, разрядные входы которого являются входами устройства, эле. мент ИЛИ, выходом соединенный со счетным входом триггера, выходы которого соединены с первыми выходами двух элементов И, выходы которых являются выходами устройства, второ и третий элементы ИЛИ, элементы И, второй триггер и элемент задержки, причем входы устройства соединены со-входами второго элемента ИЛИ, выход которого соединен со входом элемента задержки и с установочным входом второго триггера,, единичный выход которого и выход элемента задержки соединены со входами третьег элемента И, выход которого соединен с одним из входов второго элемента ИЛИ и с первыми входами дополнитель ных элементов И, вторые входы которых соединены с выходами дополнител ного триггера, установочный вход ко торого соединен, с выходом пороговог блока, входами соединенного со входами устройства, а вход сброса - с выходом дополнительного элемента за держки, входом подсоединенного к вы ходу первого дополнительного элемен Ник объединенным вторым входам до полнительных элементов ИЛИ, к выходам которых подключены счетные вход триггеров регистра, причем первые и третьи.входы дополнительных элементов ИЛИ соответственно подключены к входам первого и второго элементов ИЛИ, выход второго дополнительного элемента И подключен к первым входам четвертого и пятого элементов И, вторые входы которых соединены с выходами первого разряда регистра выходы пятого и. последующих нечетных элементов И соединены с первыми входами двух последующих элементов И, вторые входы которых соединены с выходами следующего разряда регистра, выходы четвертого и последующих четных элемен-Гов И соединены со входами первого элемента ИЛИ, выход последнего нечетного элемента И соединен с входами первых двух элементов И, выходы которых соединены со входами третьего элемента ИЛИ, выход которого соединен со входами сброса первого и второго триггеров 2. Недостатками устройства являются . большой объем оборудования вследствие применения достаточно сложного порогового блокаj особенно при большой разрядности контролируемого кода, и необходимость применения по два двухвходовых элементов И на каждый разряд регистра, а также невысокое быстродействие, обусловленное тем, что последовательно анализируются все п разрядов регистра. Целью изобретения является упрощение устройства и увеличение его быстродействия за счет сокращения вдвое длины анализируемого кода путем предварительного попарного суммирования по модулю 2 содержимого соседних разрядов-,, и совмещения по времени опроса первых двух разрядов с суммированием в- остальных. Поставленная цель достигается тем, что в устройство для определения четности информации, содержащее регистр, первый и второй элементы ИЛИ, первый и второй элементы задержки, первый, второй, третий, четвертый и пятый элементы И, группу пар элементов И первый, второй и третий триггеры, причем выход первого элемента ИЛИ соединен со счетным входом первого триггера, единичный и нулевой вы-, ходы которого соединены с первыми входами первого и второго элементов И, разрядные входы регистра являются входами устройства и соединены с группой входов второго элемента ИЛИ, выход,которого соединен с единичнЕлм входом второго триггера и через первый элемент задержки - с первым входом третьего элемента И, выходы первого и второго элементов И являются выходами устройства и соединены со входами третьего элемента ИЛИ, выход которого соединен с нулевым входом первого триггера и нулевым входом второго триггера, единичный вьаход которого соединен со вторым входом третьего элемента И, выход третьего элемента И соединен со входом второго элемента ИЛИ и с первыми входами четвертого и пятого элементов И, выход четвертого элемента И через второй элемент задержки соединен с единичным входом третьего i триггера, нулевой и единичный выходы которого соединены соответственно со вторыми входами четвертого и пятого элементов И, выход пятого элемента И соединен с первыми входами первой пары элементов И группы, выход первого и второго элементов И ь аждой пары группы соединены соответственно с соответствующим входом первого элемента,ИЛИ и первыми входами следующей пары элементов И группы, единичный и нулевые выходы каждого нечетного триггера регистра, начиная с третьего, соединены со вторыми входами соответствующей пары элементов И группы, введена дополнительная пара элементов И и группа элементов И, причем выход четвертого элемента И соединен с первыми входами элемё.нтрв И дополнительной пары и с первыми входами элементов И группы, единичный выход первого и нулевой выход второго триггеров регистра соединены со вторым и третьим входом первого элемента Идополнительной пары, нулевой выход первого и единичный выход второго триггеров регистра соединены соответственно со вторым и третьим входами второго элемента И дополнительной пары, выхода пары дополнительных элементов И соединены с соответствующими входами первого элемента ИЛИ, единичные выходы четных триггеров регистра, начиная с четвертого, соединены со вторыми входами соответствующих элементов И группы, выход каждого элемента И группы соединен со счетным входом каждого нечётного .триггера регистра, начиная с третьего,-выход третьего элемента ИЛИ соединен с нулевым входом третьего триггера и нулевьми входами перг вого, второго и всех четных триггеров регистра, выход первого элемента И каждой пары группы соединены с нулевым7:входом соответствующего триггера рег истра.

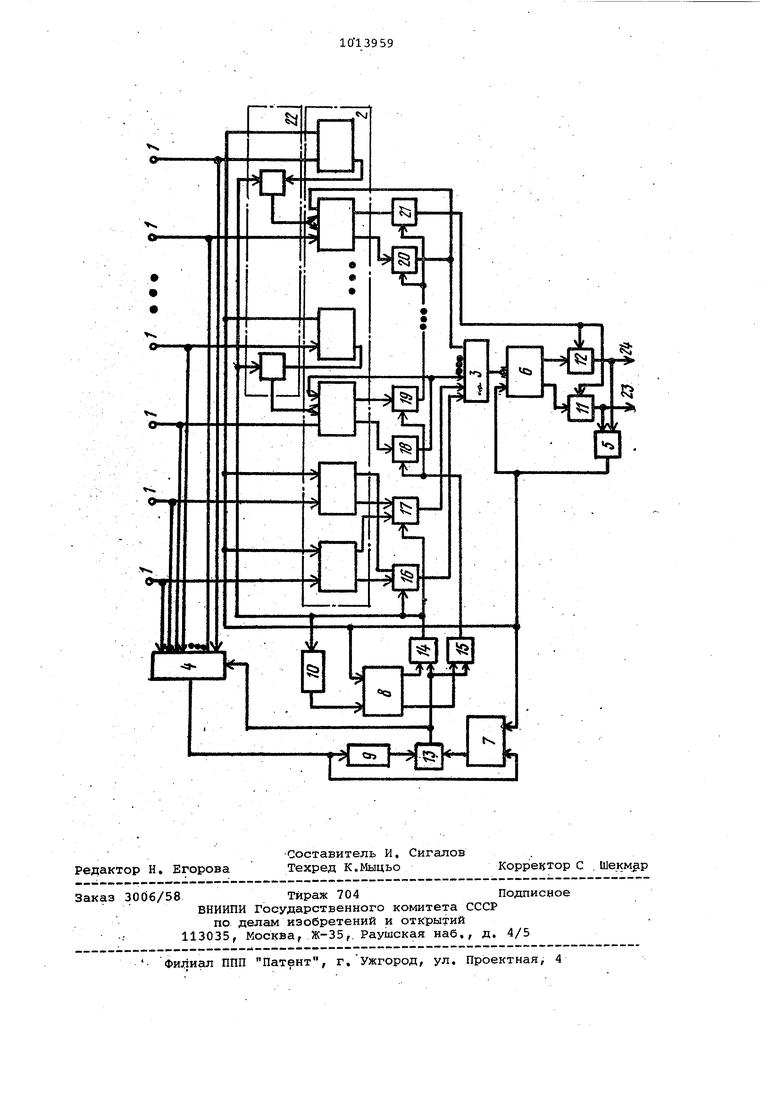

На чертеже приведена функциональная схема предлагаемого устройства,

В состав устройства входят информационные входы 1, реглстр 2, элементы ИЛИ 3-5, триггеры 6-8, элементы 9 и 10 задержки, элементы И ll-2i группа дополнительных элементов И 22 и выходы 23 и 24,

Устройство работает следующим образом, .

В исходном состоянии триггеры 6-8 и регистр Нс1ходятся в нулевом состоянии. Входная п-разрядная кодовая комбинация поступает в параллель ном коде на входы устройства 1 и записывается в регистр 2, Одновременно

входные импульсы входного кода подаются на элемент ИЛИ 4, С выхода элемента ИЛИ 4 импульс, соответствующий моменту записи, поступает на вход элемента задержки 9 и на установочный вход триггера 7, Последний устанавливается в единичное состояние и открывает элемент И 13, Через . время -у , соответствующее времени задержки 9, импульс через Открытый

0 элемент И 13 поступает на вход элемента ИЛИ 4 и входы элементов И 14 и 15, Так как триггер 8 первоначально находится в нулевом состоянии, то от-. крыт элемент И 14, поэтому первый

5 импульс пройдет на входы группы дополнительных элементов И и вызовет суммирование по mod 2 содержимого каждой пары соседних -разрядов 21+1 и 2 i + 2 ( для всех t-i li 7/ 7/1)1

0 ,причем результат этого суммирования окажется в 2 + 1 разрядах.

Одновременно первый .импульс прой|Дет через элемент И 16 либо 17, элемент ИЛИ 3 на счетный триггер 6/

5 .если значение двух первых разрядов регистра будет 10 либо 01 соответственно. Спустя время -гГа CCi.Ci} с выхода элемента задержки 10 триггер 8 будет установлен в единичное состояние и откроет элемент И 15 для всех

0 последующих импульсов. Второй импульс поступает на элементы И 18 и 19, Если триггер третьего разряда находится , то импульс пройдет через элементы И 18, ИЛИ 3 на счет5ный триггер 6 и одновременно.- на вход сброса 3 разряда, К приходу третьего импульса третий разряд триггера будет сброшен и импульс пройдет через элемент И 19. на опрос пятого

0 разряда и т,д. Если же содержимое третьего разряда равно нулю, то уже второй и мпульс пройдет на опрос пяjToro разряда регистра. С выхода последнего И 21 импульс про5ходит на входа элементов И 11 и 12, Если число единиц в кодовой комбинации нетно, то импульс появится на выходе 23, если нечетно - то на вьаходе 24, Через элемент ИЛИ 5 любой

0 из этих импульсов проходит на входал сброса триггеров 6-8, первого и всех четных разрядов регистра. Это при- . водит схему в исходное состояние, -,

Таким образом, изобретение позволит значительно повысить быстродей5ствие и упростить устройство.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1056199A1 |

| Устройство для контроля двоичного кода на четность | 1981 |

|

SU962955A1 |

| Устройство для перебора перестановок | 1986 |

|

SU1397933A1 |

| Устройство для определения максимальной гармоники спектра Уолша | 1984 |

|

SU1211751A1 |

| Устройство для управления реконфигурацией резервированной вычислительной системы | 1991 |

|

SU1837296A1 |

| Устройство для возведения в квадрат чисел,представленных в унитарном коде | 1976 |

|

SU660045A1 |

| Устройство для обхода сеточной области | 1982 |

|

SU1084806A1 |

| Медианный рекурсивный фильтр | 1988 |

|

SU1654837A1 |

| Устройство для обнаружения и исправления ошибок | 1980 |

|

SU938415A1 |

| Асинхронное устройство для определения четности информации | 1978 |

|

SU767765A2 |

УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЧЕТНОСТИ ИНФОРМАЦИИ, содержащее регистр, первый и второй элемент ИЛИ, первый и второй элементы задержки, первый, второй, третий, четвертый . и пятый элементы И, группу пар элементов И, первый второй и третий триггеры, причем выход первого элемента ИЛИ соединен со счетным вхо дом первого триггера, единичный и ;нулевой выходы которого соединены с первыми входами первого и второго . элементов И, разрядные входы регистра являются входами устройства и соединены с группой входов второго элемента или, выход которого соединен с единичным входом второго триггера и через первый элемент задержки с первым входом третьего элемента И выходы первого и второго элементов И являются выходами устройства и соединены с входами третьего элемента ИЛИ., выход которого соединен с нулевым входом первого триггера и ну- левым входом второго триггера, еди.ничный выход которого соединен с втоpbGM ВХОДОМ третьего элементга И,выхрд третьего элемента И соединен с входом второго элемента ИЛИ и с первыми входами четвертого и пятого элементов И, выход четвертого элемента И через второй элемент задержки соединен с единичным входом третьего триггера, . нулевой и единичный выходад которого соединены соответственно с вторь1ми входами четвертого и пятого, элементов И, выход пятого элемента И соединен с первыми входами первой пары элемен.тов И группы, выход первого и второго элементов И каждой пары группы, соединены соответственно с соответствующим входом первого элемента ИЛИ и первьши входами хшедующей пары элементов И группы единичный и нулевые выг ходы каждого счетного триггера регистра, начиная с третьего, соединены с вторыми входами соответствующей пары элементов И группы, о т л ич а ю щ еес я тем, чт.о, с целью повышения быстродействия и упрощения устройства, введена дополнительная пара элементов И и группа элементов И, причем выход четвертого элемента О) ,И соединен с первыми входсши элементов И дополнительной пары и с первыми входами элементов И группы, единичный выход первого и нулевой выход второго триггеров регистра сое-; динены с вторым и третьим входом первого элемента И дополнительной пары, нулевой выход первого и единичный выход второго триггеров регистра соединены соответственно с вторым и третьим входами второго элемента И дополнительной пары, вы00 ходы пары дополнительных элементов . со сд И соединены с соответствующими входа ми первого элемента ИЛИ, единичные выходы четных триггеров регистра, о начиная с четвертого, соединены с вторыми входами -соответствующих элементов И группы, выход каждого эле- мента И группы соединен со счетным входом каждого нечетного триггерарегистра, начиная с третьего, выход третьего элемента ИЛИ соединен с нулевым входом третьего триггера и нулевыми входами первого и всех четных триггеров регистра, выход первого элемента И каждой пары группы соединен сГнулевым.. входом соответстЪующего триггера регистра.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1978 |

|

SU746530A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-04-23—Публикация

1981-11-13—Подача