Изобретение относится к вычислительной технике,и может быть использовано в многомашинных системах для осуществлен 1я автоматического запуска и перезапуска вычислительного комплекса.

Известно устройство повторного запуска ЭВМ, содержащее три управляющих триггера, блок управления состоянием первого и второго управляющих триггеров по заданной программе, блок повторного запуска ЭВМ без возвращения ЭВМ в исходное состояние, блок возвращения ЭВМ в исходное состояние перед повторным запускам, блок взведения третьего управляющего триггера после повторного запуска ЭВМ, блок детектирования временного останова ЭВМ fl.

Однако известное устройство невозможно использовать в многомашинных системах, необходимо иметь заданную программу для управления устройством, нет обратной связи с ЭВМ, что пр.иводит к тому, что невозможно оценить осуществлен повторный запуск ЭВМ или нет, не предусмотрена возможность осуществления автоматической реконфигурации системы, а также возможность автоматического обновления

исходной информации с внешнего носителя.

Известна система обработки данных, автоматически возобновляющая работу входящих в нее ЭВМ после сбоя которая включает в себя несколько ЭВП, периферийные устройства, блок, обнаруживающий сбой в ЭВМ, блок управляющий возобновлением работы ЭВМ. V Система позволяет, обнаружив сбой в работе ЭВМ, произвести останов ЭВМ, стирание содержимого памяти, загрузку nporpaMNSJ и возобновление работы ЭВМ 2.

Однако в данной системе для автоматического возобновления работы входящих в нее ЭВМ необходимо, чтобы после сбоя осталась работоспособной одна или несколько ЭВМ. В случае сбоя всея входящих в систему ЭВМ автоматическое возобновление работы невозможно. Данная система не позволяет также осуществить автоматическую реконфигурацию системы, что также понижает надежность работы системы.

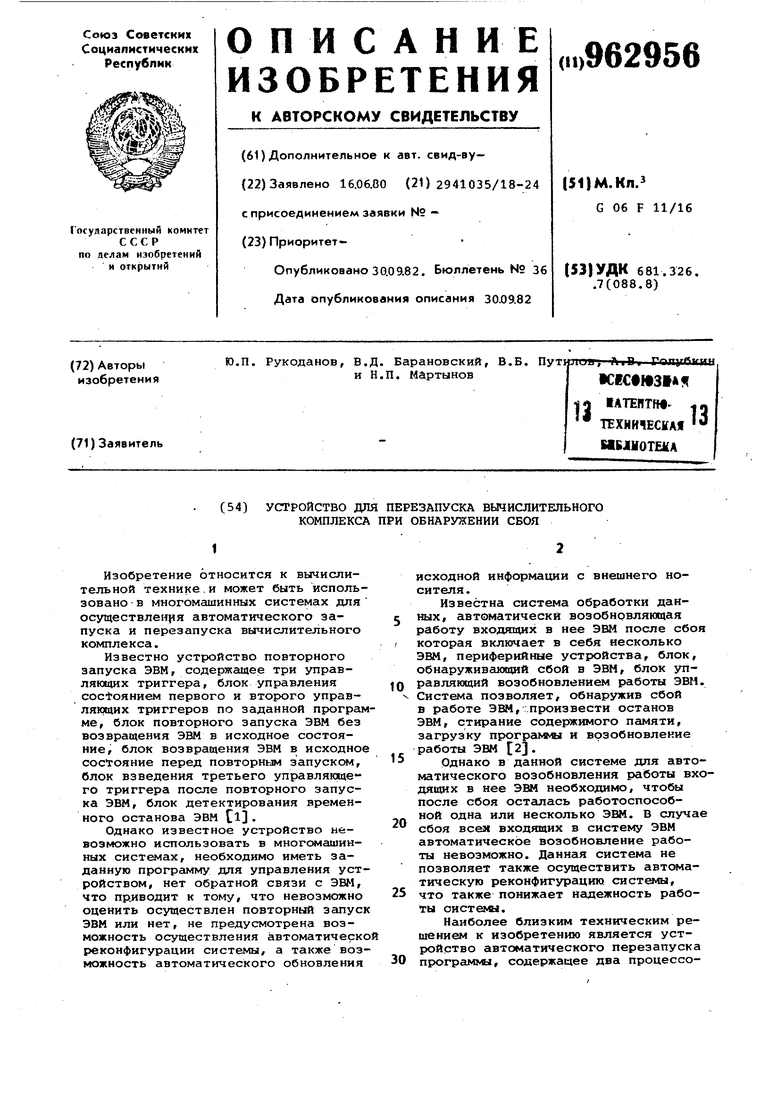

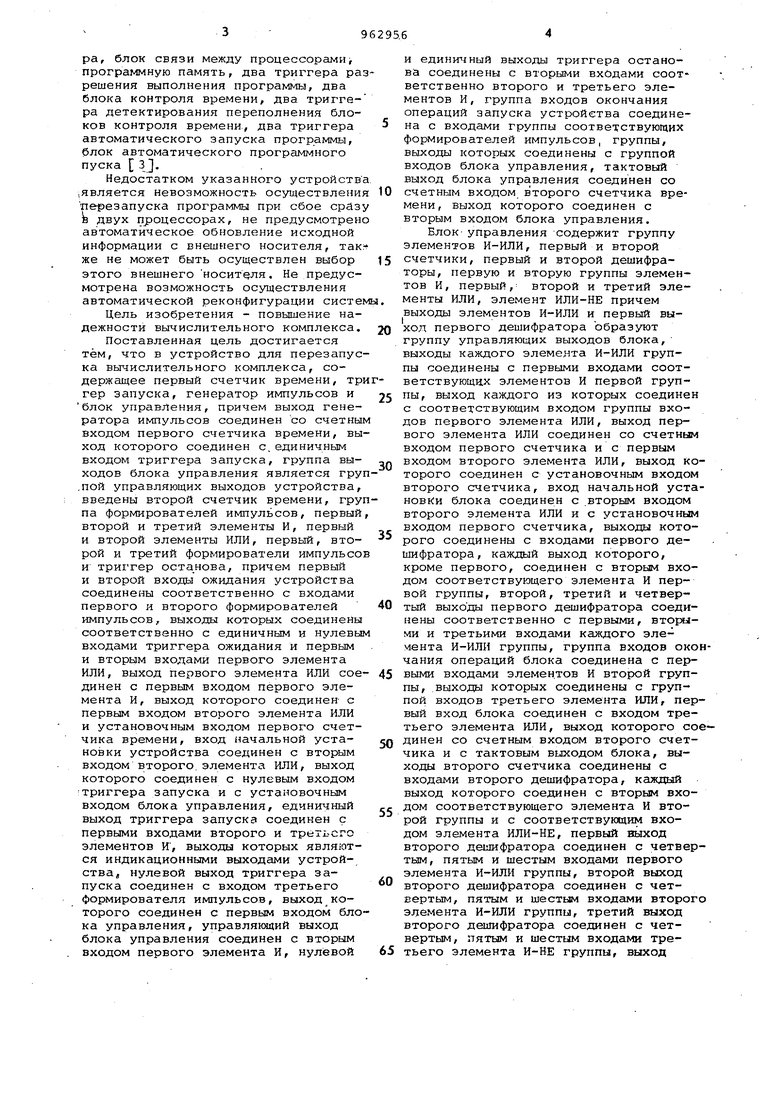

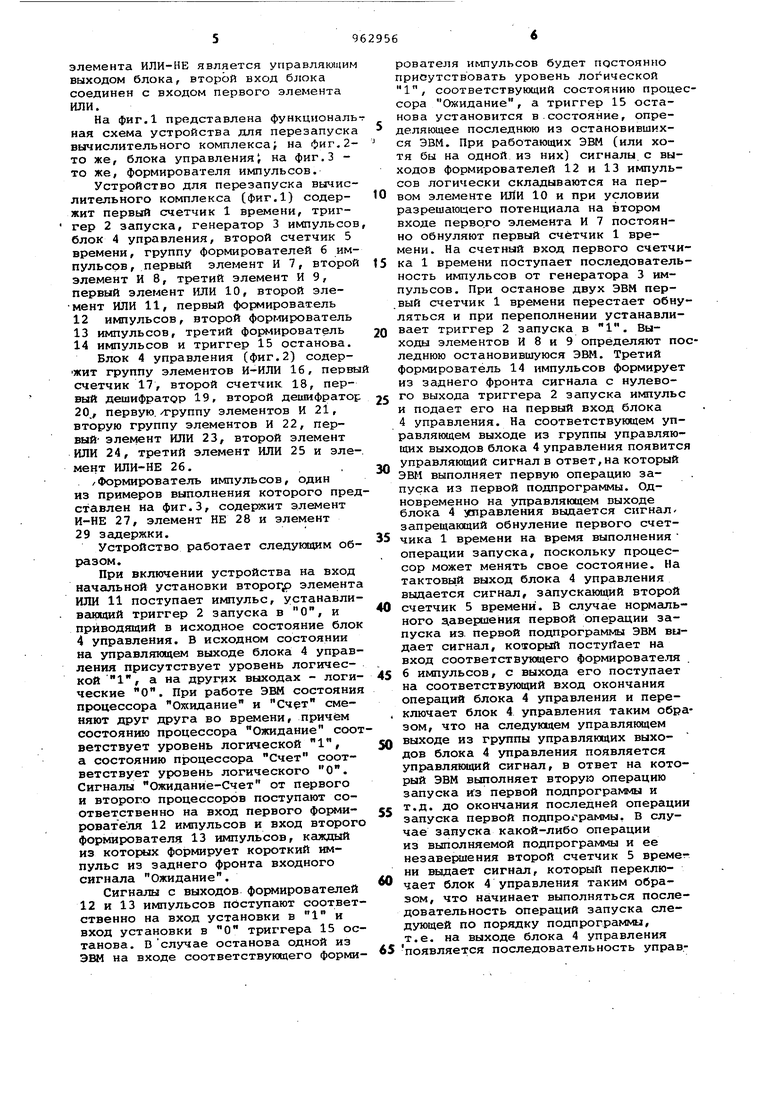

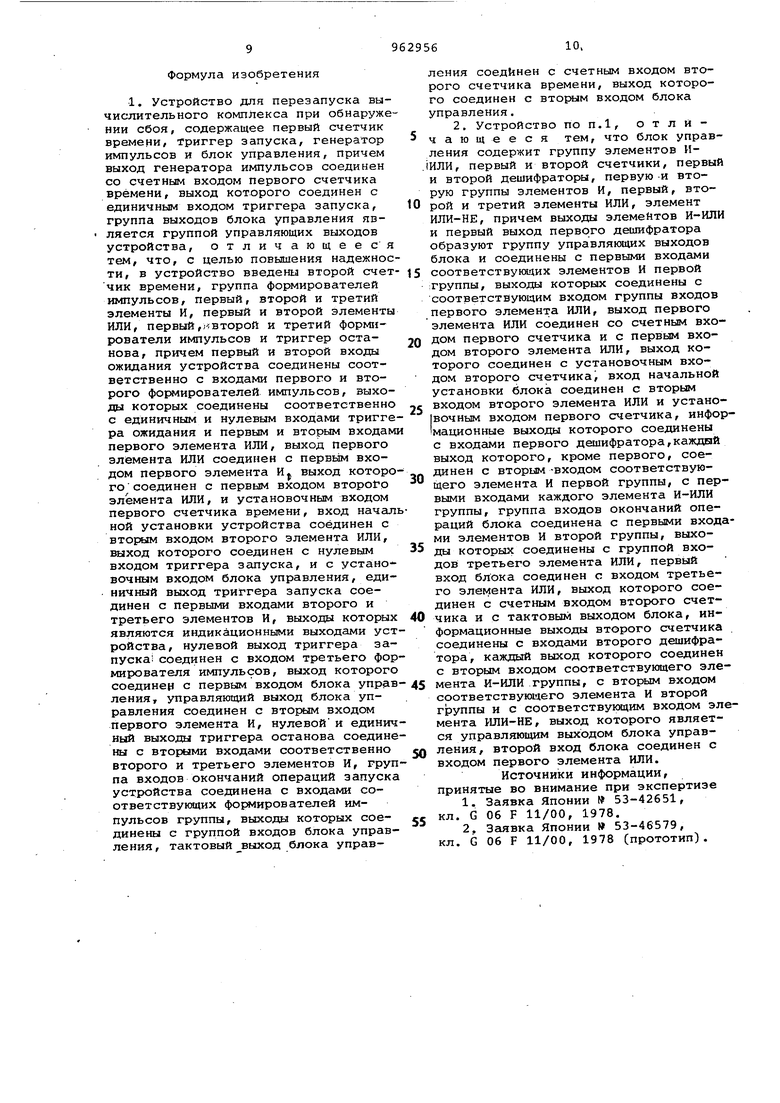

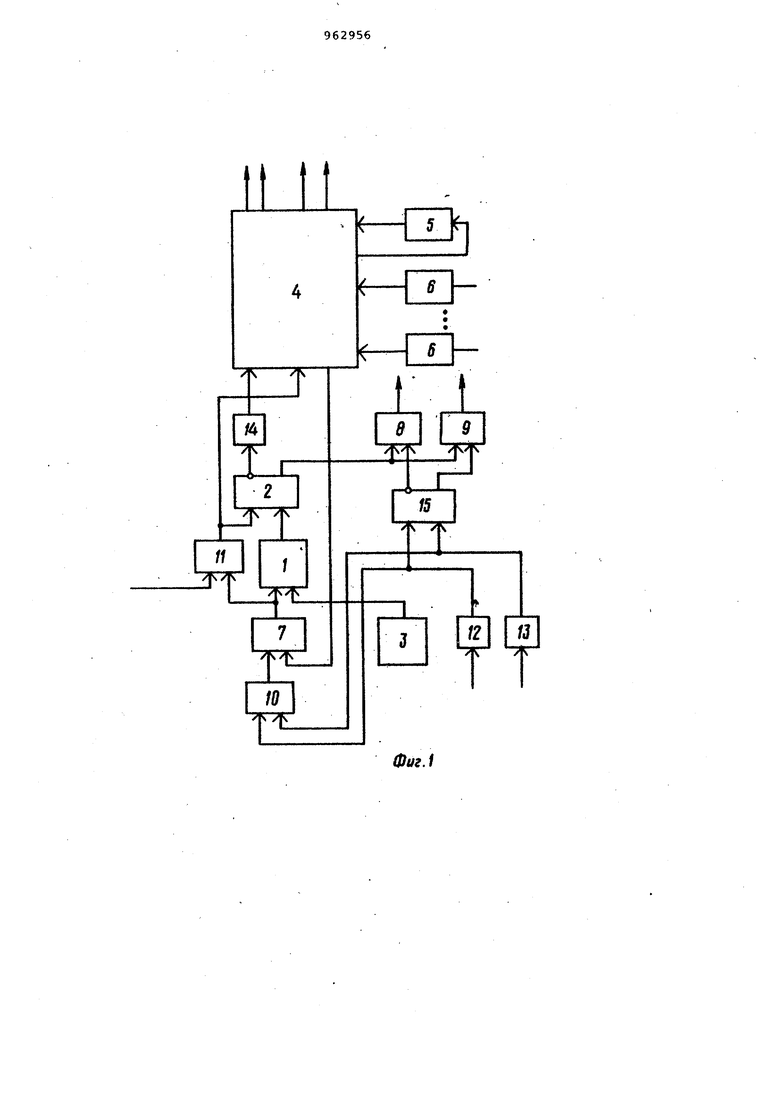

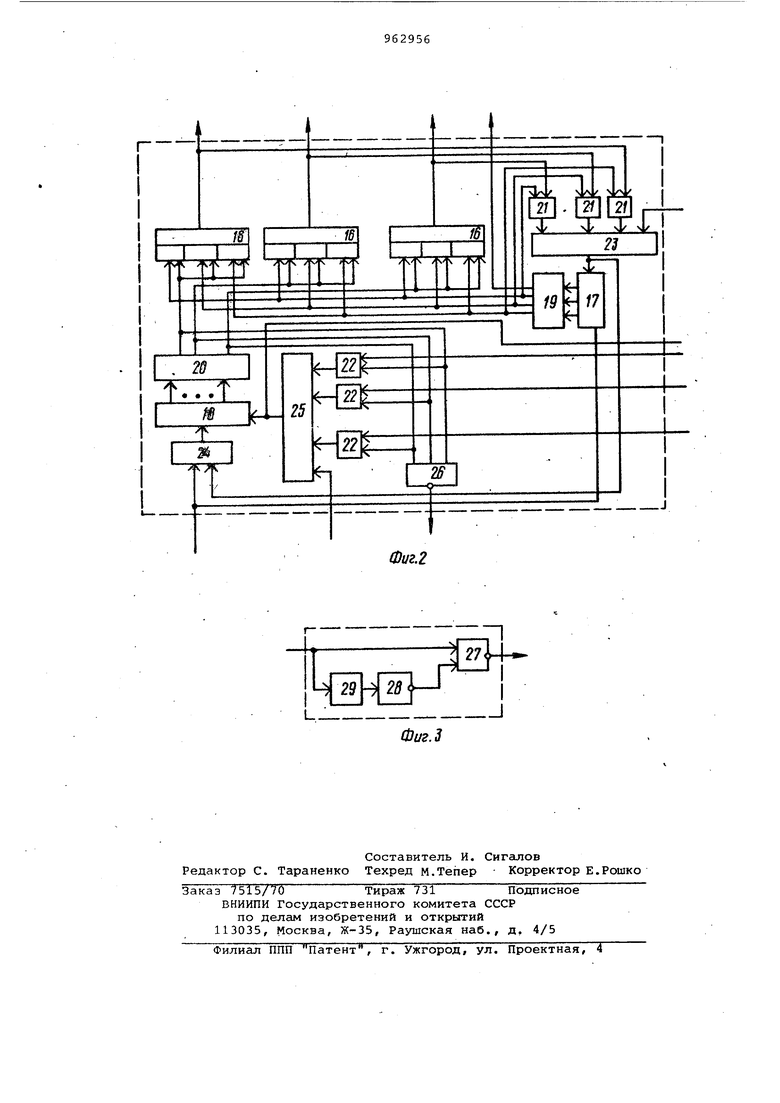

Наиболее близким техническим решением к изобретению является устройство автоматического перезапуска програмуы, содержащее два процессоpa, блок связи между процессорами программную память, два триггера ра решения выполнения программы, два блока контроля времени, два триггера детектирования переполнения блоков контроля времени, два триггера автоматического запуска программы, блок автоматического программного пуска 3. Недостатком указанного устройств .является невозможность осуществлени перезапуска программы при сбое сраз fe двух процессорах, не предусмотрен автоматическое обновление исходной информации с внешнего носителя, так же не может быть осуществлен выбор этого внешнего носителя. Не предусмотрена возможность осуществления автоматической реконфигурации систе Цель изобретения - повышение надежности вычислительного комплекса. Поставленная цель достигается тем, что в устройство для перезапус ка вычислительного комплекса, содержащее первый счетчик времени, тр гер запуска, генератор импульсов и блок управления, причем выход генератора импульсов соединен со счетны входом первого счетчика времени, вы ход которого соединен с,единичным входом триггера запуска, группа выходов блока управления является гру ,пой управляющих выходов устройства, введены второй счетчик времени, гру па формирователей импульсов, первый второй и третий элементы И, первый и второй элементы ИЛИ, первый, второй и третий формирователи импульсо и триггер , причем первый и второй входы ожидания устройства соединены соответственно с входами первого и второго формирователей импульсов, выходы которых соединены соответственно с единичным и нулевы входами триггера ожидания и первым и вторым входами первого элемента ИЛИ, выход первого элемента ИЛИ сое динен с первым входом первого элемента И, выход которого соединен- с первым входом второго элемента ИЛИ и установочным входом первого счетчика времени, вход начальной установки устройства соединен с вторым входом второго.элемента ИЛИ, выход которого соединен с нулевым входом Триггера запуска и с установочным входом блока управления, единичный выход триггера запуска соединен с первыми входами второго и третьего элементов И , выходы которых являются индикационными выходами устройства, нулевой выход триггера запуска соединен с входом третьего формирователя импульсов, выход которого соединен с первым входом бло ка управления, управлякяций выход блока управления соединен с вторнлм входом первого элемента И, нулевой и единичный выходы триггера останова соединены с вторыми входами соответственно второго и третьего элементов И, группа входов окончания операций запуска устройства соединена с входами группы соответствующих формирователей импульсов, группы, выходы которых соединены с группой входов блока управления, тактовый выход блока управления соединен со счетным входом второго счетчика времени, выход которого соединен с вторым входом блока управления. Блок управления содержит группу элементов И-ИЛИ, первый и второй счетчики, первый и второй дешифраторы, первую и вторую группы элементов И, первый, второй и третий элементы ИЛИ, элемент ИЛИ-НЕ причем выходы элементов И-ИЛИ и первый выход первого дешифратора образуют группу управляющих выходов блока, выходы каждого элеме.1та И-ИЛИ группы соединены с первыми входами соответствующих элементов И первой группы, выход каждого из которых соединен с соответствующим входом группы входов первого элемента ИЛИ, выход первого элемента ИЛИ соединен со счетным входом первого счетчика и с первым входом второго элемента ИЛИ, выход которого соединен с установочным входом второго счетчика, вход начальной установки блока соединен с .вторым входом второго элемента ИЛИ и с установочным входом первого счетчика, выходы которого соединены с входами первого дешифратора, каждый выход которого, кроме первого, соединен с вторым входом соответствующего элемента И первой группы, второй, третий и четвертый выходы первого дешифратора соединены соответственно с первыми, вторыми и третьими входами каждого элемента И-ИЛИ группы, группа входов окончания операций блока соединена с первыми входами элементов И второй группы, выходы которых соединены с группой входов третьего элемента ИЛИ, первый вход блока соединен с входом третьего элемента ИЛИ, выход которого соединен со счетным входом второго счетчика и с тактовым ВЕЯХОДОМ блока, выходы второго счетчика соединены с входами второго дешифратора, каждый выход которого соединен с вторым входом соответствующего элемента И второй группы и с соответствующим входом элемента ИЛИ-НЕ, первый выход второго дешифратора соединен с четвертым, пятым и шестым входами первого элемента И-ИЛИ группы, второй выход второго дешифратора соединен с четвертым, пятым и шестым входами второго элемента И-ИЛИ группы, третий выход второго дешифратора соединен с четвертым, пятым и шестым входами третьего элемента И-НЕ группы, выход элемента ИЛИ-НЕ является управляющим выходом блока, второй вход блока соединен с входом первого элемента ИЛИ. На фиг.1 представлена функциональ ная схема устройства для перезапуска вычислительного комплекса; на фиг.2то же, блока управленияJ на фиг.З то же, формирователя импульсов. Устройство для перезапуска вычислительного комплекса (фиг.1) содержит первый счетчик 1 времени, триггер 2 запуска, генератор 3 импульсо блок 4 управления, второй счетчик 5 времени, группу формирователей 6 импульсов, первый элемент И 7, второй элемент И 8, третий элемент И 9, первый элемент ИЛИ 10, второй элемент ИЛИ 11, первый формирователь 12импульсов, второй форглирователь 13импульсов, третий формирователь 14импульсов и триггер 15 останова. Блок 4 управления (фиг.2) содержит группу элементов И-ИЛИ 16, первы счетчик 17, второй счетчик 18, первый дешифратор 19, второй дешифратор 20., первую./группу элементов И 21, вторую группу элементов И 22, первый- элемент ИЛИ 23, второй элемент ИЛИ 24, третий элемент ИЛИ 25 и элемент ИЛИ-НЕ 26. /Формирователь импульсов, один из примеров выполнения которого пред ставлен на фиг.З, содержит элемент И-НЕ 27, элемент НЕ 28 и элемент 29 задержки. Устройство работает следукадим образом. При включении устройства на вход начальной установки второгр элемента ИЛИ 11 поступает импульс, устанавлива1рвдий триггер 2 запуска в О, и приводящий в исходное состояние блок 4 управления. В исходном состоянии на управляющем выходе блока 4 управления присутствует уровень логической 1, а на других выходах - логические О. При работе ЭНИ состояния процессора Ожидание и Счет сменяют друг друга во времени, причём состоянию процессора Ожидание соот ветствует уровень логической 1, а состоянию процессора Счет соответствует уровень логического О. Сигналы Ожидание-Счет от первого и второго процессоров поступают соответственно на вход первого фоЕ 1ирователя 12 импульсов и вход второго формирователя 13 импульсов, каждый из которых формирует короткий импульс из заднего фронта входного сигнала Ожидание. Сигналы с выходов формирователей 12 и 13 импульсов поступают соответственно на вход установки в 1 и триггера 15 освход установки в танова. D случае останова одной из ЭВМ на входе соответствующего формирователя импульсов будет постоянно присутствовать уровень логической 1, соответствующий состоянию процессора Ожидание, а триггер 15 останова установится в.состояние, определяющее последнюю из остановившихся ЭВМ. При работающих ЭВМ (или хотя бы на одной из них) сигналы с выходов формирователей 12 и 13 импульсов логически складываются на первом элементе ИЛИ 10 и при условии разрешающего потенциала на втором входе первого элемента И 7 постоянно обнуляют первый счётчик 1 времени. На счетный вход первого счетчика 1 времени поступает последовательность импульсов от генератора 3 импульсов. При останове двух ЭВМ первый счетчик 1 времени перестает обнуляться и при переполнении устанавливает триггер 2 запуска в 1. Выходы элементов И 8 и 9 определяют последнюю остановившуюся ЭВМ. Третий формирователь 14 импульсов формирует из заднего фронта сигнгша с нулевого выхода триггера 2 запуска импульс и подает его на первый вход блока 4 управления. На соответствующем управляющем выходе из группы управляющих выходов блока 4 управления появится управляющий сигнал в ответ,на который ЭВМ выполняет первую операцию запуска из первой подпрограммы. Одновременно на управляющем выходе блока 4 управления выдается сигнал/ запрещающий обнуление первого счетчика 1 времени на время выполнения операции запуска, поскольку процессор может менять свое состояние. На тактовый выход блока 4 управления вьадается сигнал, запускающий второй счетчик 5 времени. В случае нормального завершения первой операции запуска из. первой подпрограммы ЭВМ выдает сигнал, который постугГает на вход соответствующего формирователя 6 импульсов, с выхода его поступает на соответствующий вход окончания операций блока 4 управления и переключает блок 4 управления таким образом, что на следующем управляющем выходе из группы управляющих выходов блока 4 управления появляется управляющий сигнал, в ответ на который ЭВМ выполняет вторую операцию запуска из первой подпрограммы и т.д. до окончания последней операции запуска первой подпрограммы. В случае запуска какой-либо операции из выполняемой подпрограммы и ее незавершения второй счетчик 5 времетни выдает сигнал, который переключает блок 4 управления таким образом, что начинает выполняться последовательность операций запуска следующей по порядку подпрограммы, т.е. на выходе блока 4 управления появляется последовательность управляющих сигналов, в ответ на которые ЭВМ будет производить последовательность операций запуска следукядей по порядку подпрограммы и т.д. Так продолжается до тех пор, jiOKaустройство не осуществит :запуск вычислительного комплекса с помощью операций запуска какой-либо подпрограммы. Блок 4 управления позволяет осуществить несколько вариантов запуска вычислительного комплекса. Каждый вариант запуска определяется соответствующей подпрограммой с входящими в нее операциями. Запуск вычислительного комплекса начинает осуществляться с подпрограммы , охватывающей минимальное количество ресурсов. В случае невозможности запуска вычислительного ко1 тлекса по первой подпрограмме (т.е. невыполнения какойлибо операции, входящей в состав данной подпрограммы). Блок 4 управления переключается на выполнение следующей по порядку подпрограммы, охватывающей большее количество ресурсов. В последующих подпрограммах включены ог1ерации запуска, осуществляющие автоматическую реконфигура-. цию системы, перепись исходной информации с различных внешних носителей информации. Если ни одна подпрограмма запуска не осуществилась, блок 4 управления выдает управляющий сиг|нал, сообщающий о том, что -автоматический запуск вычислительного комплекса невозможен.

В блоке 4 управления (фиг.2) первый счетчик 17 и первый дешифратор 19 определяют выполняемую подпрограмму, второй счетчик 18 и второй дешифратор 20 определяют выполняемую операцию из выполняемой .подпрограммы. Если Е какой-либо подпрограмме не должны выполняться некоторые операции, тоосоответствующие входы элементов И-ИЛИ 16 соединяются с корпусом. При включении устройства на вход начальной установки блока 4 управления поступает импульс, который устанавливает в О счетчики 17 и 18, приведя в исходное состояние блок 4 управления. В этом состоянии на управляющем выходе блока 4 управления присутствует уровень логической l, а на всех других выходах - уровень логического О. Поступающий на первый вход блока 4 управления импульс через третий элемен ИЛИ 25 записывает единицу во второй счетчик 18 и выдаётся на тактовый выход, начиная счет времени, отпущенного на выполнение данной операции. Второй дешифратор 20 в зависимости от числа, записанного во второй счетчик 18, выдает кодовую комбинацию ка элементы И-ИЛИ 16, и на одном из выходов группы управляющих выходов блока 4 управления появляется

управляющий сигнал, осуществляющий запуск первой операции первой подпрограммы. При нормальном завершении данной операции на соответствующий вход окончания операции блока 4 упрал ния поступает импульс, который открывает соответствующий элемент И 22 и, пройдя элемент ИЛИ 25, добавляет единицу в счетчик 18. Дешифратор 20 выдает следующую кодовуюкомбинацию на элементы И-ИЛИ 16, и на другом выходе из группы у правляющих выходов блока 4 управления появляется управляющий сигнал, осуществляющий выполнение следующей по порядку операции из первой подпрограммы. Аналогично выполняются последующие операции первой подпрограммы. Если после выдачи последнего управляющего сигнала из первой подпрограммы не произошло запуска вычислительного комплекса, то этот управлякяций сигнал открывает соответствующий элемент И 21 и через элемент ИЛИ 23 добавляет единицу в счетчик 17 и на выходе дешифратора 19 появляется кодовая комбинация, определяющая следующую по порядку подпрограмму и начинают выполняться операции следующей подпрограммы. Если какаялибо операция выполняемой подпрограммы нормально не завершилась, то последующая операция данной подпрограммы не начинается, а сигнал с первого входа блока 4 управления через элемент ИЛИ 23 добавляет в счетчик 17 единицу и начинают выполняться операции следующей по порядку подпрограммы. После завершения каждой пoдпpoгpaм Iы производится установка в О счетчика 18. После завершения какой-либо подпрограммы запуска и запуска вычислительного комплекса блок 4 управления приводится в исходное состояние сигналом, поступающим на вход начальной установки блока 4 управления. ..

Таким образом, предлагаемое устройство позволяет осуществить автоматический запуск вычислительного комплекса при сбое всех ЭВМ, входящих в состав вычислительного комплекса. Устройство осуществляет автсяи атическую перепись исходной информации с различных внешних носителей информации, а также позволяет производить автоматическую конфигурацию вычислительной системы, что позволяет осуществить автоматический запуск вычислительного комплекса при отказе части устройства, входящи в состав вычислительного комплек- . са, а также при частичной потере исходной информации в оперативном запоминающем устройстве или на внаиних носителях. Формула изобретения 1. Устройство для перезапуска вычислительного комплекса при обнаруже нии сбоя, содержащее первый счетчик времени, триггер запуска, генератор импульсов и блок управления, причем выход генератора импульсов соединен со счетным входом первого счетчика времени, выход которого соединен с единичным входом триггера запуска, группа выходов блока управления является группой управляющих выходов устройства, отличающееся тем, что, с целью повышения надежнос ти, в устройство введены второй счет чик времени, группа формирователей импульсов, первый, второй и третий элементы И, первый и второй элементы ИЛИ, первый,ивторой и третий формирователи импульсов и триггер останова, причем первый и второй входы ожидания устройства соединены соответственно с входами первого и второго формирователей импульсов, выходы которых соединены соответственно с единичным и нулевым входами тригге ра ожидания и первым и вторым входам первого элемента ИЛИ, выход первого элемента ИЛИ соединен с первым входом первого элемента К выход которо госоединен с первым входом BTOpoto элемента ИЛИ, и установочным входом первого счетчика времени, вход начал ной установки устройства соединен с вторым входом второго элемента ИЛИ, выход которого соединен с нулевым входом триггера згшуска, и с установочным входом блока управления, единичный выход триггера запуска соединен с первыми входами второго и третьего элементов И, выходы которых являются индикационньоми выходами уст ройства, нулевой выход триггера заnycKai соединен с входом третьего фор мирователя импульсов, выход которого соединен с первым входом блока управ ления, управляющий выход блока управления соединен с вторалм входом первого элемента И, нулевой и единич ный выходы триггера останова соедине ны с вторыми входами соответственно второго и третьего элементов И, груп па входов окончаний операций запуска устройства соединена с входами соответствующих формирователей импульсов группы, выходы которых соединены с группой входов блока управления, тактовый выход блока управления соединен с счетным входом второго счетчика времени, выход которого соединен с вторым входом блока управления. 2. Устройство по П.1, отличающееся тем, что блок управления содержит группу элементов ИИЛИ, первый и второй счетчики, первый и второй дешифраторы, первую -и вторую группы элементов И, первый, второй и третий элементы ИЛИ, элемент ИЛИ-НЕ, причем выходы элементов И-ИЛИ и первый выход первого дешифратора образуют группу управляющих выходов блока и соединены с первыми входами соответствующих элементов И первой ;Группы, выходы которых соединены с соответствующим входом группы входов первого элемента ИЛИ, выход первого элемента ИЛИ соединен со счетным входом первого счетчика и с первым входом второго элемента ИЛИ, выход которого соединен с установочным входом второго счетчика, вход начальной установки блока соединен с вторым входом второго элемента ИЛИ и устано(вочннм входом первого счетчика, информационные выходы которого соединены с входами первого дешифратора,кажднй выход которого, кроме первого, соединен с вторым-входом соответствующего элемента И первой группы, с первыми входами каждого элемента И-ИЛИ группы, группа входов окончаний операций блока соединена с первыми входами элементов И второй группы, выходы которых соединены с группой входов третьего элемента ИЛИ, первый вход блока соединен с входом третьего элемента ИЛИ, выход которого соединен с счетным входом второго счетчика и с тактовым выходом блока, информационные выходы второго счетчика соединены с входами второго дешифратора, каждый выход которого соединен с вторым входом соответствующего элемента И-ИЛИ группы, с вторым входом соответствующего элемента И второй группы и с соответствукицим входом элемента ИЛИ-НЕ, выход которого является управляющим выходом блока управления, второй вход блока соединен с входом первого элемента ИЛИ. Источники информации, принятые во внимание при экспертизе 1.Заявка Японии № 53-42651, кл. G 06 F 11/00, 1978, 2,Заявка Японии 53-46579, кл. G 06 F 11/00, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для перезапуска вычислительного комплекса при обнаружении сбоя | 1984 |

|

SU1211734A1 |

| Устройство для перезапуска вычислительного комплекса при обнаружении сбоя | 1988 |

|

SU1594543A1 |

| Устройство для перезапуска вычислительного комплекса при обнаружении сбоя | 1988 |

|

SU1541608A1 |

| Устройство для контроля хода программы и перезапуска ЭВМ | 1985 |

|

SU1337901A1 |

| Устройство для контроля хода программы и перезапуска ЭВМ | 1987 |

|

SU1501066A2 |

| Устройство для отладки программ | 1988 |

|

SU1661771A1 |

| Устройство для тестовой проверки узлов контроля каналов ввода-вывода | 1979 |

|

SU922752A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для сопряжения магистрали ЭВМ с магистралью внешних устройств | 1984 |

|

SU1246105A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1168950A1 |

Фиг.1

Фиг.З

Авторы

Даты

1982-09-30—Публикация

1980-06-16—Подача