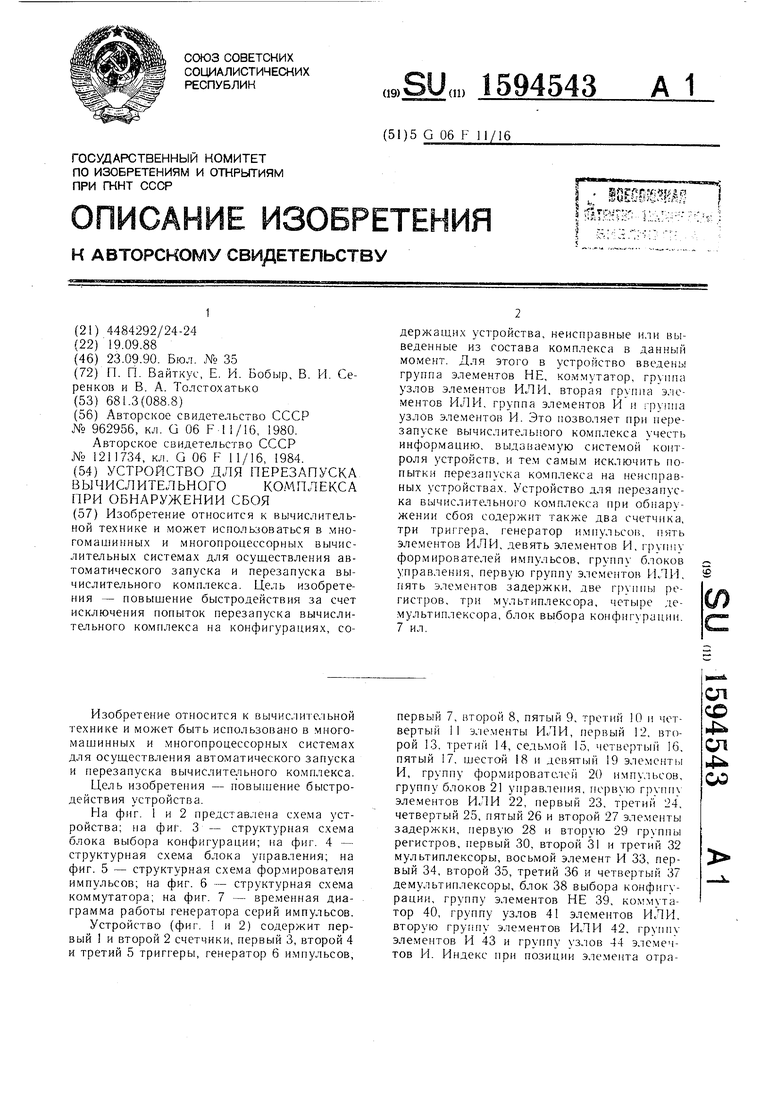

Изобретение относится к вычислительной технике и может быть использовано в многомашинных и многопроцессорных системах для осуществления автоматического запуска и перезапуска вычислите.пьного комплекса.

Цель изобретения - повып ение быстродействия устройства.

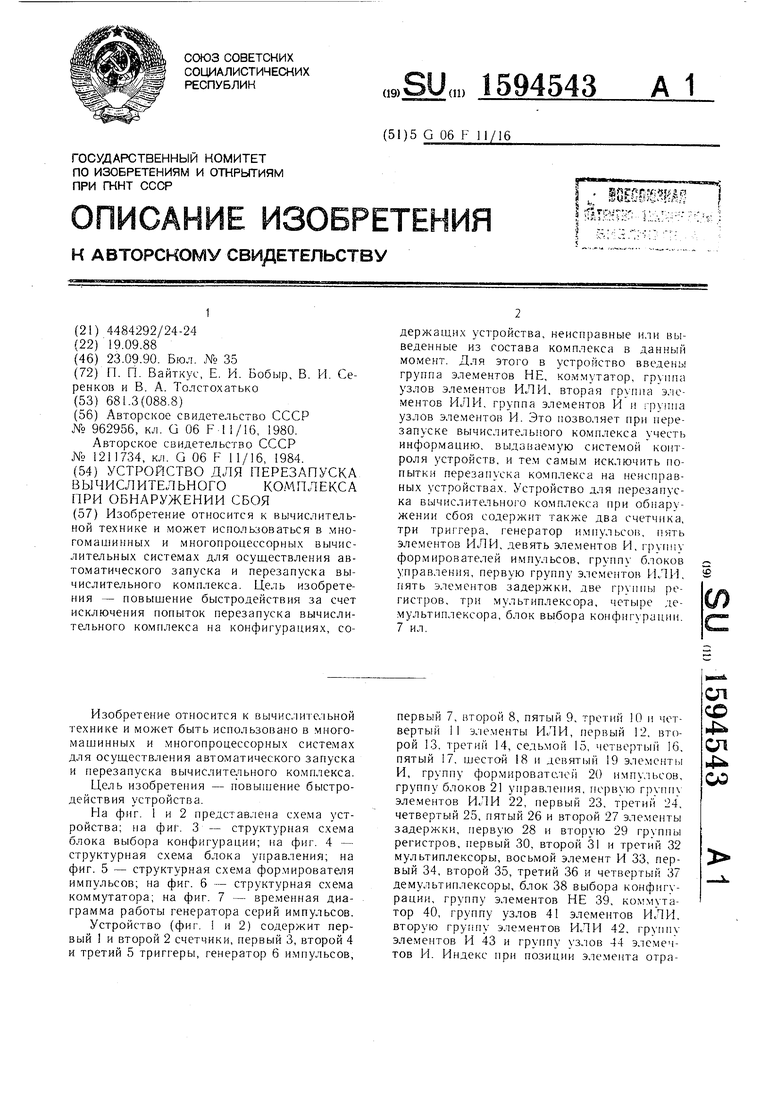

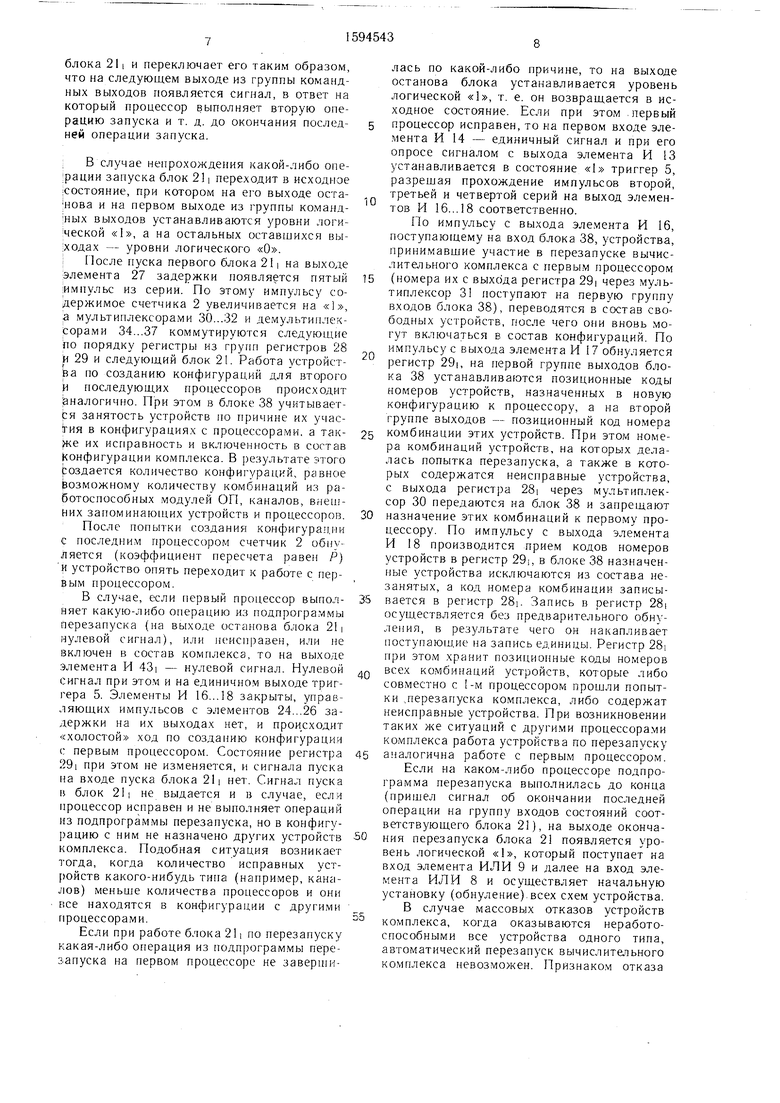

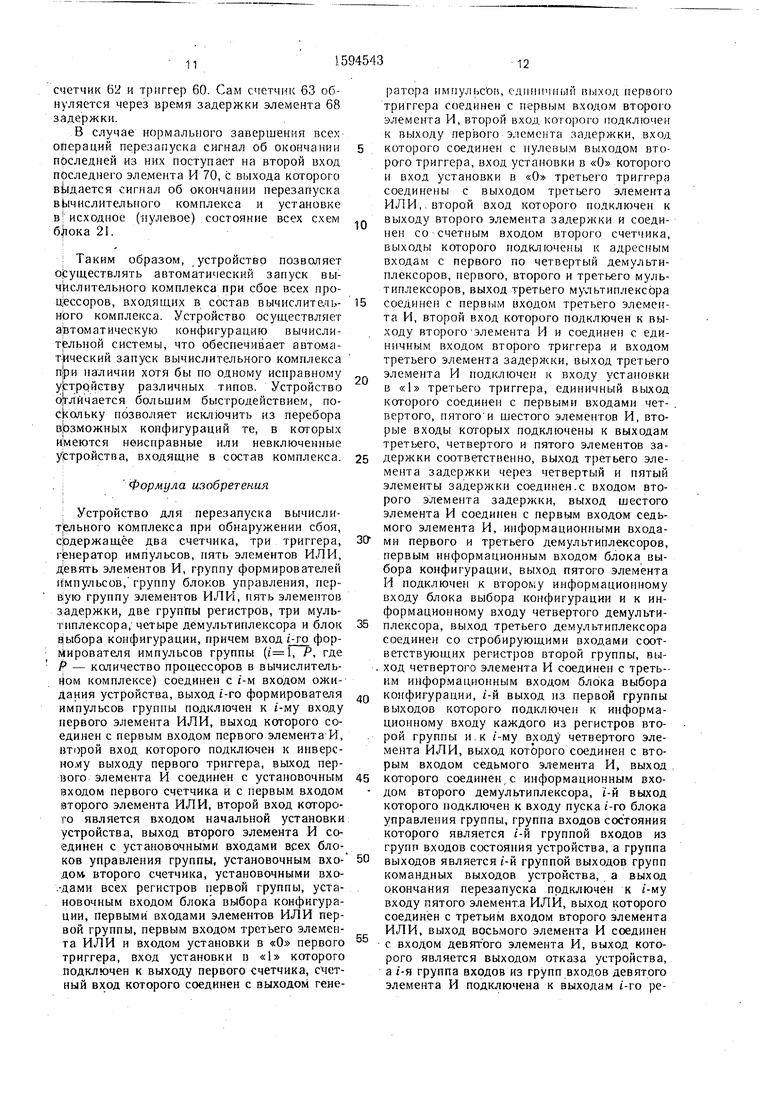

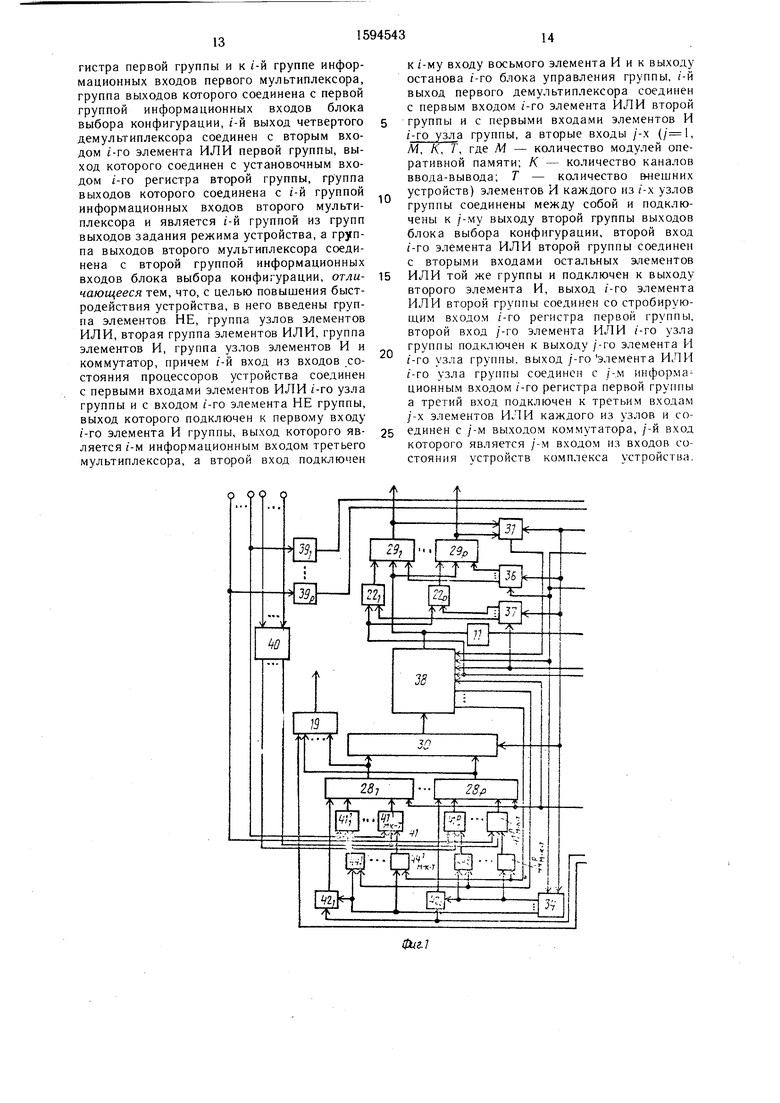

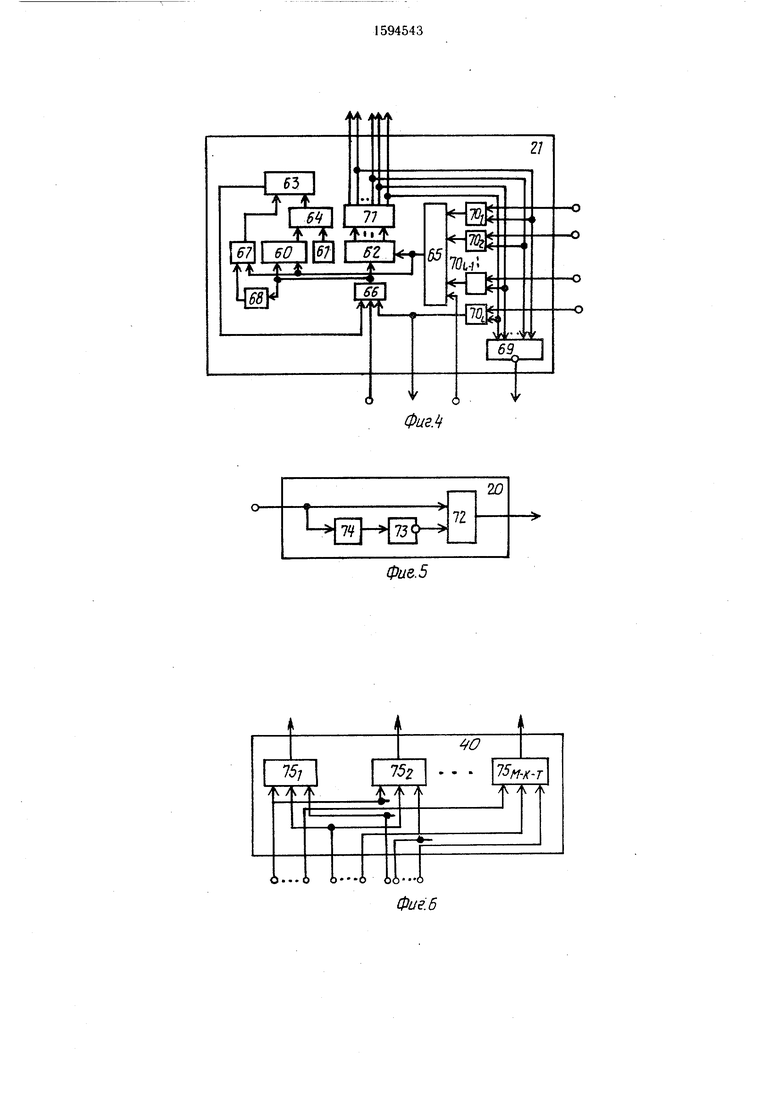

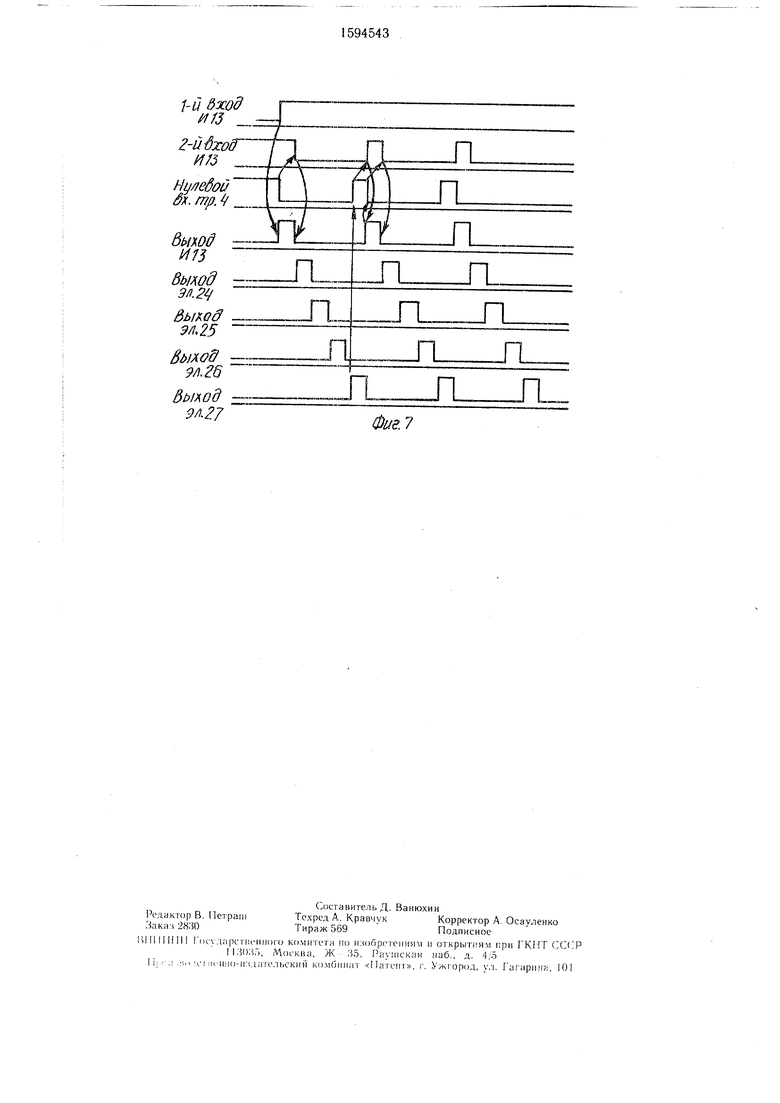

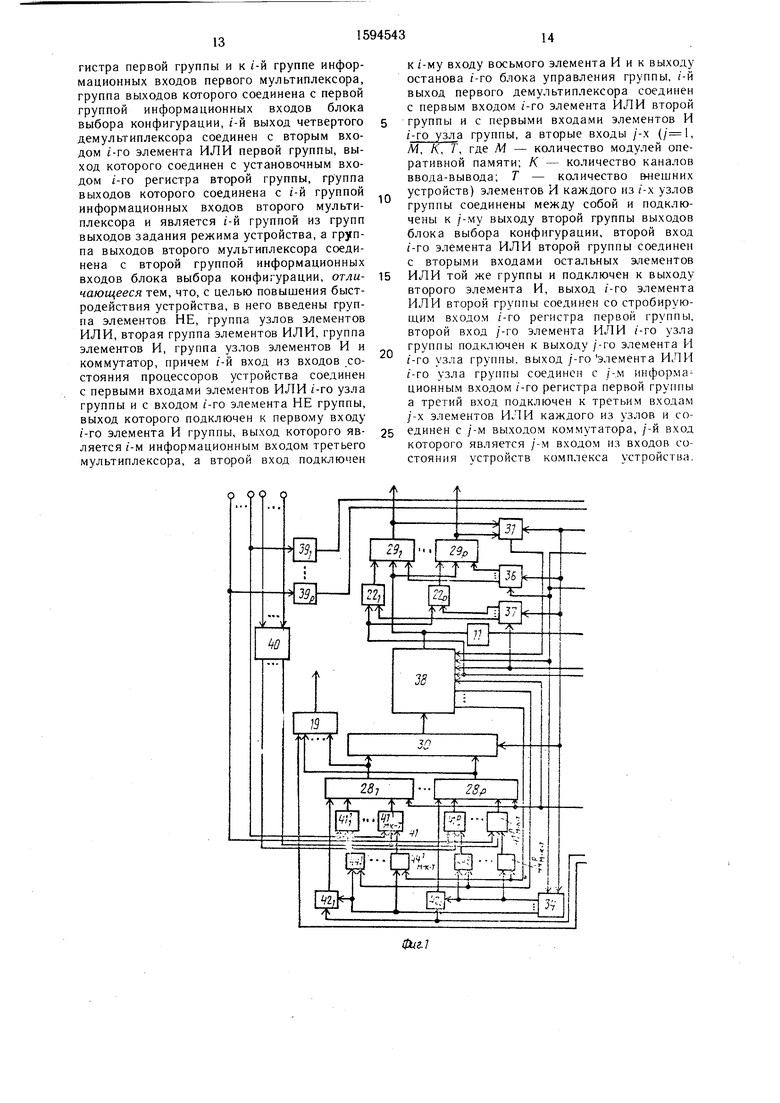

Fla фиг. 1 и 2 представлена схема устройства; на фиг. 3 - структурная схема блока выбора конфигурации; на фиг. 4 - структурная схема блока управления; на фиг. 5 - структурная схема формирователя импульсов; на фиг. 6 - структурная схема коммутатора; на фиг. 7 - временная диаграмма работы генератора серий импульсов.

Устройство (фиг. 1 и 2) содержит первый 1 и второй 2 счетчики, первый 3, второй 4 и третий 5 триггеры, генератор 6 импульсов.

первый 7, второй 8, пятый 9, третий 10 и четвертый 11 элементы ИЛИ, первый 12, второй 13, третий 14, седьмой 15, четвертый 16, пятый 17, шестой 18 и девятый 19 элемент1 1 И, группу формирователей 20 импульсов, группу блоков 21 управления, первую группу элементов ИЛИ 22, первый 23, третий 24, четвертый 25, пятый 26 и второй 27 элементы задержки, первую 28 и вторую 29 группы регистров, первый 30, второй 31 и третий 32 мультиплексоры, восьмой элемент И 33, первый 34, второй 35, третий 36 и четвертый 37 демультиплексоры, блок 38 выбора конфигурации, группу элементов НЕ 39, коммутатор 40, группу узлов 41 элементов ИЛИ, вторую группу элементов ИЛИ 42, группу элементов И 43 и группу узлов 44 элемеч- тов И. Индекс при позиции элемента отрасл со

4

сд

и

оо

жает количество этих элементов в названных узлах или группах, при этом Р - количество процессоров вычислительного комплекса; М - количество модулей оперативной памяти; К - количество каналов ввода-вывода; Т - катичество внешних устройств.

Блок 38 выбора конфигурации (фиг. 3), содержит первую 45 и вторую 46 группы узлов элементов И, первую 47 и вторую 48 группы элементов И, группу узлов 49 элемен- тов ИЛИ, узлы 50...52 элементов ИЛИ, узлы 53...55 триггеров, группы 56 и 57 э. емен- тов НЕ, элемент ИЛИ 58 и регистр 59. Триггеры 53 хранят состояние каждого из М модулей оперативной памяти, триггеры 54 - каждого из К каналов, а триггернэ 55 -- каж- дого из Т внешних устройств.

Каждый блок 21 управления группы (фиг. 4) содержит триггер 60, генератор 61 импул1гсов, счетчики 62 и 63, элемент И 64, элементы ИЛИ 65...67, элемент 68 задержки, элемент ИЛИ-НЕ 69, группу элементов И 70 и дешифратор 71.

Каждый формирователь 20 импульсов группы (фиг. 5) содержит элемент И 72, элемент НЕ 73 и элемент 74 задержки

Коммутатор 40 (фиг. 6) содержит группу элементов ИЛИ 75.

Устройство работает следующим образом.

При включении устройства через вход начальной установки на вход второго эле- мента ИЛИ 8 поступает положительный импульс. Появившись на выходе ИЛИ 8, импульс устанавливает в нулевое состояние

первый триггер 3, через элемент ИЛИ 10

второй 4 и третий 5 три1теры, второй счетчик 2 и регистры 28|...28, через элементы ИЛИ 22i...22p - регистры 29i...29p и приводит в исходное состояние блок 38 и блоки 211...21р. Е5 исходном состоянии на первых из командных выходов каждого блока 211... присутствуют уровни логической «1, а на остальных - уровни логического «О. Наличие единичных сигналов на первых командных выходах блоков 21|...21,, управления дает возможность каждому процессору вести вычисления по програ.мме.

При нормальной работе процессора его состояния «Ожидание и «Счет сменяют одно другое во времени, причем состоянию процессора «Ожидание соответствует уровень логической «1, а состоянию процессора «Счет - Уровень логического «О. Сигналы «Ожидание и «Счет от всех процессоров поступают на входы соответствующих формирователей 20|...20,,, каждый из которых формирует короткий положительный импульс при переходе процессора из состояния «Счет (логического «О) в состояние «Ожидание (логической «1). При работающих процессорах (или хотя бы одного из них) сигналы с выходов формирователей 20|...20p логически складываются на первом элементе

,

5

0

5 Q

5 0

5

ИЛИ 7, и при наличии разрешающего потенциала на втором входе первого элемента И 12 с пулевого выхода триггера 3 постоянно обнуляют счетчик 1. На счетный вход счетчика 1 постоянно поступает последовательность импульсов от генератора 6.

При останове всех процессов на входах формирователей 20i...20p присутствуют уровни логической «1 (останов процессора соответствует состоянию «Ожидание). Счетчик 1 перестает обнуляться и сигналом «Переполнение устанавливает триггер 3 в единичное состояние. Единичный сигнал с единичного выхода триггера 3, пройдя второй элемент И 13 (так как триггер 4 находится в нулево.м состоянии и на его нулевом выходе, а соответственно, и на выходе элемента 23 задержки имеет место единичный сигнал), запускает генератор серии импульсов, собранный на элементах 23...27 задержки, элементе ИЛИ 10, элементе И 13 и триггере 4. Генератор непрерывно вырабатывает пять серий импульсов, сдвинутых один относитепь- но другого (фиг. 7). Одновременно нулевым сигналом с нулевого выхода триггера 3, поступающим на второй вход первого элемента И 12, блокируется прохождение сигналов «Ожидание и «Счет на время выполнения операций запуска, поскольку процессоры при выполнении этих операций меняют свое состояние. И.мпульсы, вырабатываемые генератором, управляют устройство.м в режиме запуска.

Работа с каждым процессором в этом режи.ме осуществляется поочередно. Но.мер процессора, с которым з данный момент ведется работа, находится в счетчике 2. Код номера процессора со счетчика 2 поступает на адресные входы мультиплексоров 30...32 и демультиплексороз 34...37, которые производят коммутацию соответствующих коду процессора регистров из групп регистров 28i...28p и 29i...29p к блока управления из блоков 21...21,,. В /-М регистре 28, (, Р) в позиционном коде хранятся номера комбинаций устройств оперативной памяти (ОП) каналов и впецгних запоминающих устройств, которые с (-м процессором (, Р) уже принимали участие в попытке перезапуска вычислительного комплекса либо имеют в своем составе неисправное или выключенное устройство. Разрядность каждого регистра равна М-К-Т (где М - количество модулей ОП; К. - количество каналов; Т - количество внешних запоминающих устройств). В регистре 29,- (i, Р) в позиционном коде хранятся номера устройств ОП, кана.ча и внешнего запоминающего устройства, которые с i -M процессором образуют текущую конфигурацию, на которой осуществляется попытка перезапуска вычисли- те чьного комплекса. Разрядность регистра 29,- равна М- гК+Т.

В случае неисправности любого устройства ОП, капала, внешнего запоминающего

устройства или процессора или невключения их в рабочую конфигурацию комплекса на входе состояния, соответствующего этому устройству, присутствует потенциал логической «Ь. В этом случае на выходах комму- татора 40, соответствующих комбинациям устройств, в составе которых имеется неисправное или не включенное в состав отмеченное устройство, имеются потенциалы логической «Ь. По поступающему с выхода элемента И 13 первому импульсу из серии импульсов производится запись в регистры 28|...28р позиционных кодов номеров комбинаций устройств, которые не могут участвовать в перезапуске комплекса по причине наличия в них неисправных или не включен- ных в конфигурацию комплекса устройств. Запись в регистры 28|...28p позиционных кодов осуществляется через элементы ИЛИ 411...41и.к.ткаждой из групп. При наличии неисправного или не включенного в состав конфигурации комплекса t-ro процессора (1 р) разряды регистра 28,- полностью будут заполнены единицами, так как пи одна из комбинаций устройств с этим процессором может участвовать в перезапуске вычислительного компле са. Таким образом, при- нятые меры позволяют не делать попыток запуска вычислительного комплекса с комбинациями устройств, в которых имеются неисправные или не включенные в состав конфигурации устройства.

В начальный момент запуска вычисли- тельного комплекса счетчик 2, как было отмечено, находится в нулевом состоянии. Нулевой код с его выхода поступает на адрест ные входы мультиплексоров 30...32 и демуль- типлексоров 34...37, которые коммутируют первые регистры 28, и 29i, а также первый блок 211. С помощью элемента И 43i произ- водится анализ на. возможность участия в перезапуске комплекса с первого процессора, код которого равен нулю. Для этого первый процессор должен быть исправным, что определяется наличием сигнала «О на первом входе состояния, и на выходе соответствующего-ему блока 211 должен присутствовать сигнал «Останов. Наличие логической «1 на выходе останова блока 211 свидетельствует о том, что блок не участвует в перезапуске вычислительного процессора. Если блок 211 оказывается не запущенным на управление перезапуском и первый процессор исправен, то на выходе мультиплексора 32, а соответственно, и на первом входе элемента И 14 появляется единичный сигнал - сигнал участия. Проверка присутствия сигнала участия на первом входе И 14 осуществляется первым импульсом из серии, снимаемым с выхода элемента И 13. При его наличии устанавливается в единичное со- стояние триггер 5, который единичным сигналом с единичного выхода разрещает прохождение импульсов второго, третьего и четвертого из серии на выходы элементов И

16...18 соотвегственно. По импульсу с выхода пятого элемента И 17 на первом выходе де- мультиплексора 37 появляется единичный сигнал, устанавливающий (через элемент ИЛИ 22:) в нулевое состояние первый регистр 29|. Одновременно импульс с выхода элемента И 17 поступает на управляющий вход блока 38 и устанавливает на первой группе выходов номера устройств, назначенных в конфигурацию к первому процессору, а на второй группе выходов - позиционный номер комбинации этнх устройств. Причем в конфигурацию к первому процессору назначаются только исправные и включенные в конфигурацию комплекса устрой- ства. Это осуществляется блокированием единичными сигналами регистра 28i через мультиплексор 30 в блоке 38 (через 2-ю группу входов) тех комбинаций устройств, в которых имеется неработоспособное устройство по отмеченным причинам. При наличии способных участвовать в перезапуске комбинаций устройств по импульсу с выхода элемента И 18, поступаю- ц;ему на вход демультиплексора 36 и через него на вход стробирования приема регистра 291, производится прием кодов номерон устройств в этот регистр. Кроме того, импульс с выхода элемента И 18 поступает на вход демультиплексора 34, сигналом с первого выхода которого, поступаюплим через элемент ИЛИ 42i на стробнрующий вход регистра 28i, обеспечивается прием в этот регистр кода номера комбинации устройств, с которыми работает первый.процессор.

Запись в регистр 28i кода номера комбинации устройств осуществляется через элементы И 44ь..И 44«.к.гпервой группы. Импульс с выхода элемента И 18, поступая на вход блока 38, исключает из состав а незанятых, но работоспособных устройств те, которые назначены в конфигурацию с первым процессором. При этом на первой группе выходов блока 38 - не нулевой код, в результате чего на выходе элемента ИЛИ II, а соответственно, и на первом входе элемента И 15 появляется единичный сигнал. Пройг дя элемент И 15, этот единичный сигнал ключает первый выход демультпплексора 35 на вход пуска первого блока 211.

По этому сигналу блок запускается на управление программой перезапуска вычислительного комплекса. На выходе оста.- нова блока 211 устанавливается уровень логического-«О. При этом, на первом выходе из группы командных выходов блока 211 тоже появляется уровень логического «О, а на втором выходе устанавливается уровень логической «1. В ответ на этот единичный сигнал первый процессор в;.июлняет первую операцию запуска. В случае нормального завершения первой операции запуска процессор выдает сигнал, который поступает на первый вход группы входов состояния

блока 211 и переключает его таким образом, что на следующем выходе из группы командных выходов появляется сигнал, в ответ на который процессор выполняет вторую операцию запуска и т. д. до окончания последней операции запуска.

: В случае непрохождения какой-либо опе- :рации запуска блок 211 переходит в исходное :состояние, при котором на его выходе оста- нова и на первом выходе из группы ко.манд- :ных выходов устанавливаются уровни логи- :ческой «1, а на остальных оставшихся вы- :ходах - уровни логического «О. : После пуска первого блока 211 на выходе элемента 27 задержки появляется пятый :импульс из серии. По этому импульсу содержимое счетчика 2 увеличивается на «1, а мультиплексорами 30...32 и демультиплек- сорами 34...37 коммутируются следующие по порядку регистры из групп регистров 28 и 29 и следующий блок 21. Работа устройства по созданию конфигураций для второго И носледующих процессоров происходит аналогично. При этом в блоке 38 учитывается занятость устройств но причине их участия в конфигурациях с процессорами, а также их исправность и включенность в состав Конфигурации комплекса. В результате этого создается количество конфигураций, равное Возможному количеству комбинаций из работоспособных модулей ОП, каналов, внешних запоминающих устройств и процессоров.

После попытки создания конфигурации с последним процессором счетчик 2 обнуляется (коэффициент пересчета равен Р) и устройство опять переходит к работе с первым процессором.

В случае, если первый процессор выполняет какую-либо операцию из подпрограммы перезапуска (на выходе останова блока 21: нулевой сигнал), или неисправен, или не включен в состав комплекса, то на выходе элемента И 43i нулевой сигнал. Нулевой сигнал при этом и на единичном выходе триггера 5. Элементы И 16...18 закрыты, упрае.- ляющих импульсов с элементов 24...26 задержки на их выходах нет, и прои сходит «холостой ход по созданию конфигурации с первым процессором. Состояние регистра 29i при этом не изменяется, и сигнала пуска на входе пуска блока 211 нет. Сигнал пуска в блок 21I не выдается и в случае, если процессор исправен и не выполняет операций из подпрограммы перезапуска, но в конфигурацию с ним не назначено других устройств комплекса. Подобная ситуация возникает тогда, когда количество исправных уст- )ойств какого-нибудь типа (например, каналов) меньше количества процессоров и они Eice находятся в конфигурации с другими процессорами.

Если при работе блока 211 по перезапуску какая-либо операция из подпрограммы перезапуска на первом процессоре не заверши15

20

25

-30

5

0

5

0

лась по какой-либо причине, то на выходе останова блока устанавливается уровень логической «1, т. е. он возвращается в исходное состояние. Если при этом .первый процессор исправен, то на первом входе эле- .мента И 14 -- единичный сигнал и при его опросе сигналом с выхода элемента И 13 устанавливается в состояние «1 триггер 5, разрешая прохождение импульсов второй, третьей и четвертой серий на выход элементов И 16... 18 соответственно.

По импульсу с выхода элемента И 16, поступающему на вход блока 38, устройства принимавшие участие в перезапуске вычислительного комплекса с первым процессором (номера их с выхода регистра 29i через мультиплексор 31 поступают на первую группу входов блока 38), переводятся в с остав сво бодных устройств, после чего они вновь могут включаться в состав конфигураций. По импульсу с выхода элемента И 17 обнуляется регистр 29|, на первой группе выходов блока 38 устанавливаются позиционные коды номеров устройств, назначенных в новую конфигурацию к процессору, а на второй группе выходов -- позиционный код номера комбинации этих устройств. При этом номера комбинаций устройств, на которых делалась попытка перезапуска, а также в которых содержатся неисправные устройства, с выхода регистра 28i через м ультиплек- сор 30 передаются на блок 38 и з апрещают назначение этих комбинаций к первому процессору. По импульсу с выхода эле мента И 18 производится прием кодов номеров устройств в регистр 29i, в блоке 38 назначенные устройства исключаются из состава не- занятых, а код номера комбинации записывается в регистр 28i. Запись в регистр 28i осущ,ествляется без предварительного обнуления, в результате чего он накапливает поступающие на запись единицы. Регистр 28i при этом хранит позиционные коды номеров всех комбинаций устройств, которые либо совместно с -м процессором прошли попытки .перезапуска комплекса, либо содержат неисправные устройства. При возникновении таких же ситуаций с другими процессорами комплекса работа устройства по перезапуску аналогична работе с первым процессором. Если на каком-либо процессоре подпрограмма перезапуска выполнилась до конца (пришел сигнал об окончании последней операции на группу входов состояний соответствующего блока 21), на выходе окончания перезапуска блока 21 появляется уровень логической «1, который поступает на вход элемента ИЛИ 9 и далее на вход элемента ИЛИ 8 и осуществляет начальную установку (обнуление),всех схем устройства. В случае массовых отказов устройств комплекса, когда оказываются неработоспособными все устройства одного типа, автоматический перезапуск вычислительного комплекса невозможен. Признаком отказа

вычислительного комплекса служит единичное состояние всех выход9в всех peгиctpoв 28i...28p (исчерпание всех возможных комбинаций исправных устройств комплекса) и единичное состояние выходов останова блоков 21 (ни один из процессоров не выполняет операций по перезапуску вычислительного комплекса). При выполнении этих условий на выходе элемента И 19 устанавливается единичный потенциал, свидетельствующий о том, что автоматический запуск вычислительного комплекса невозможен.

В блоке 38 (фиг. 3) триггеры узла 53 являются триггерами занятости модулей оперативной памяти. По сигналу начальной установки, поступающему на установочный вход блока и далее на первые входы элементов ИЛИ узла 49, триггеры устанавливаются в единичное состояние. Единичное состояние каждого триггера узла 53 соответствует незанятости одноименного модуля оператив-- ной памяти. Аналогично триггеры узлов 54 и 55 являются триггерами занятости модулей каналов и внешних запоминающих устройств. Элементы И 47 выполняют роль шиф- раторов номеров комбинаций устройств оперативной памяти, каналов и внещних запоминающих устройств. Для этого на входы элементов И 47 заведены все возможные комбинации номеров этих устройств. В начальный момент, когда все устройства свободны, на выходах всех элементов И 47 устанавливается потенциал логической «1. Это свидетатьствует о том, что любая комбинация устройств оперативной памяти, канала и внещнего запоминающего устройства может быть назначена в конфигурацию к процессору для осуществления перезапуска вычислительного комплекса. На элементах ,И 48 и элементах НЕ 56 осуществляется выбор одной комбинации устройств из всех возможных. При этом комбинации устройств уже участвовавшие в перезапуске и хранящиеся на регистрах 28, через мультиплек- сор 30 поступают на элементы НЕ 57 и далее на входы соответствующих элементов И 48, чем запрещается повторное назначение комбинации устройств. Код выбранной комбинации устройств с выходов элементов И 48 заносится и хранится в регистре 59. Код выбранной комбинации с выхода регистра 59 поступает на вторую группу выходов блока 38 и далее на регистры 28 для запоминания в соответствующем регистре. Кроме того, код с выхода регистра 59 поступает на входы элементов ИЛИ узлов 50...52, где осуществ- ляется обратное преобразование кода номера комбинации устройств в коды номеров устройств.

Коды номеров устройств поступают на входы соответствующих элементов И 46 и по сигналу с третьего управляющего входа блока 38 устанавливают в нулевое состояние триггеры узлов 53...55 тех устройств, которые назначены в конфигурацию. Кроме того.

10

5

15.25 3035 „45 50

10

номера устройств с выхода элементов ИЛИ узлов 50...52 поступают на первую группу выходов блока 38 и далее на регистры 29. При переводе устройств конфигурации из занятого состояния в свободное, номера этих устройств с группы выходов соответствующего регистра 29 через мультиплексор 31 поступают на первую группу входов блока 38, далее на входы элементов И 45 и по сигналу на первом управляющем входе блока 38 устанавливают в единичное состояние соответствующие триггеры узлов 53...55. По сигналу с первого управляющего входа блока 38, поступающему на первый вход элемента ИЛИ 58, производится обнуление перед приемом регистра 59.

В каждом блоке 21 (фиг. 4) счетчик 62 и дешифратор 71 определяют выполняемую операцию из подпрограммы перезапуска вычислительного комплекса. При включении устройства на установочный вход блока 21 поступает импульс начальной установки, который поступает на вход элемента ИЛИ 66 и устанавливает в исходные (нулевые) состояния счетчики 62 и 63 и триггер 60. На первом выходе дешифратора 71 устанавливается уровень логической «1, а на остальных - логического «О, при этом на выходе элемента ИЛИ-НЕ 69 (выход останова устанавливается также уровень логической «1. При поступлении сигнала пуска на вход блока 21 он поступает через элемент ИЛИ 65 на счетный вход счетчика 62 и изменяет его состояние на единицу. При этом единичный уровень на первом выходе де1иифратор;1 пропадает и появляется единичный уровень на втором выходе дещифратора, который осуществляет запуск первой операции подпрограммы перезапуска. Сигналом с выхода элемента ИЛИ 66 осуществляется также обнуление счетчика 63 и установка в единичное состояние триггера 60, разрешающего прохождение импульсов с генератора 61 импульсов через элемент И 64 на счетный вход счетчика 63.

При нормальном завершении операции перезапуска на соответствующий вход окончания операции блока 21 поступает импульс, который открывает соответствующий элемент И 70 и, пройдя элемент ИЛИ 65, ляет единицу в счетчик 62. Деп1ифратор 71 выдает следующую кодовую комбинацию на выходы блока 21, и осуществляется запуск следующей операции подпрограммы перезапуска. Одновременно с запуском операции сигналом с выхода элемента ИЛИ 65 осуществляется обнуление счетчика 63, который начинает подсчет импульсов с нулевого состояния. Если после запуска какой- либо операции не приходит сигнал о ее окончании в течение интервала времени, определяемого временем пересчета счетчика 63, с выхода переполнения счетчика 63 выдается сигнал, переводящий в нулевое состояние

счетчик 62 и триггер 60. Сам счетчик 63 обнуляется через время задержки элемента 68 задержки.

В случае нормального завершения всех операций перезапуска сигнал об окончании последней из них поступает на второй вход последнего элемента И 70, с выхода которого выдается сигнал об окончании перезапуска вычислительного комплекса и установке

в исходное (нулевое) состояние всех схем 21.

; Таким образом, устройство позволяет осуществлять автоматический запуск вычислительного комплекса при сбое всех процессоров, входящих в состав вычислитель- нЬго комплекса. Устройство осуществляет автоматическую конфигурацию вычисли- т|ельной системы, что обеспечи зает автома- т-йческий запуск вычислительного комплекса п|ри наличии хотя бы по одному исправному устройству различных типов. Устройство 6|глйчается большим быстродействием, постольку позволяет исключить из перебора в|озможных конфигураций те, в которых и1меются неисправные или невключенные устройства, входящие в состав комплекса.

. : Формула изобретения

Устройство для перезапуска вычисли- т ельного комплекса при обнаружении сбоя, содержащее два счетчика, три триггера, г|енератор импульсов, пять элементов ИЛИ, Девять элементов И, группу формирователей и;мпульсов, группу блоков управления, пер- BJyro группу элементов ИЛИ, пять элементов задержки, две группы регистров, три мультиплексора, четыре демультиплексора и блок щыбора конфигурации, причем вход г -гр фор- Мирователя импульсов группы (, Р, где Р - количество процессоров в вычислитель- йом комплексе) соединен с i-м входом ожидания устройства, выход t -ro формирователя импульсов группы подключен к /-му входу первого элемента ИЛИ, выход которого соединен с первым входом первого элемента И, Второй вход которого подключен к инверсному выходу первого триггера, выход первого элемента И соединен с установочным йходом первого счетчика и с первым входом второго элемента ИЛИ, второй вход которого является входом начальной установки устройства, выход второго элемента И cct- единен с установочными входами всех блоков управления группы, установочным входом второго счетчика, установочными вхо- .-дами всех регистров первой группы, установочным входом блока выбора конфигурации, первыми входами элементов ИЛИ первой группы, первым входом третьего элемента ИЛИ и входом установки в «О первого триггера, вход установки в «1 которого подключен к выходу первого счетчика, счетный вход которого соединен с выходом гене5

0

5 5

О 5 Q 5 0

ратора импульс ов, единичный выход первого триггера соединен с первым входом второго элемента И, второй вход которого подключен к выходу первого элемента задержки, вход которого соединен с нулевы.м выходом второго триггера, вход установки в «О которого и вход установки в «О третьего триггера соединены с выходом третьего элемента ИЛИ,-второй вход которого подключен к выходу второго элемента задержки и соединен со счетным входом второго счетчика, выходы которого подключены к адресным входам с первого по четвертый демульти- плексоров, первого, второго и третьего мультиплексоров, выход третьего мультиплексора соединен с перв1 1м входом третьего элемента И, второй вход которого подключен к выходу второго элемента И и соединен с единичным входом второго триггера и входом третьего элемента задержки, выход третьего элемента И подключен к входу установки в «1 третьего триггера, единичный выход которого соединен с первыми входами четвертого, ПЯТОГО и шестого элементов И, вторые входы которых подключены к выходам третьего, четвертого и пятого элементов задержки соответственно, выход третьего элемента задержки через четвертый и пятый элементы задержки соединен.с входом второго элемента задержки, выход шестого элемента И соединен с первым входом седьмого элемента И, информационными входами первого и третьего демультиплексоров, первым информационным входом блока выбора конфигурации, выход пятого элемента И подключен к второму информационному входу блока выбора конфигурации и к информационному входу четвертого демультиплексора, выход третьего демультиплексора соединен со стробирующими входами соответствующих регистров второй группы, выход четвертого элемента И соединен с треть-- им информационным входом блока выбора конфигурации, /-и выход из первой группы выходов которого подключен к информационному входу каждого из регистров второй группы и. к /-му входу четвертого элемента ИЛИ, выход которого соединен с вторым входом седьмого элемента И, выход , которого соединение информационным входом второго демультиплексора, t-й выход которого подключен к входу пуска г -го блока управления группы, группа входов состояния которого является /-Й группой входов из групп входов состояния устройства, а группа выходов является г-й группой выходов групп командных выходов устройства, а выход окончания перезапуска подключен к i-му входу пятого элемент.а ИЛИ, выход которого соединен с третьим входом второго элемента ИЛИ, выход восьмого элемента И соединен с входом девятого элемента И, выход которого является выходом отказа устройства, а /-Я группа входов из групп входов девятого элемента И подключена к выходам i-ro ре13

гистра первой группы и к /-и группе информационных входов первого мультиплексора, группа выходов которого соединена с первой группой информационных входов блока выбора конфигурации, г-й выход четвертого демультиплексора соединен с вторым входом t-ro элемента ИЛИ первой группы, выход которого соединен с установочным входом /-го регистра второй группы, группа выходов которого соединена с /-и группой информационных входов второго мультиплексора и является г -й группой из групп выходов задания режима устройства, а группа выходов второго мультиплексора соединена с второй группой информационных входов блока выбора конфигурации, отли- чающееся тем, что, с целью повышения быстродействия устройства, в него введены группа элементов НЕ, группа узлов элементов ИЛИ, вторая группа элементов ИЛИ, группа элементов И, группа узлов элементов И и коммутатор, причем (-и вход из входов .состояния процессоров устройства соединен с первыми входами элементов ИЛИ i -ro узла группы и с входом /-ГО элемента НЕ группы, выход которого подключен к первому входу г-го элемента И группы, выход которого яв- ляется г-м информационным входом третьего мультиплексора, а второй вход подключен

5 15 25

454314

к /-МУ входу восьмого элемента И и к выходу останова г-го блока управления группы, (-и выход первого демультиплексора соединен с первым входом / -го элемента ИЛИ второй группы и с первыми входами элементов И /-ГО узла группы, а вторые входы /-х (, М, К,, Т, где М - количество модулей оперативной памяти; К - количество каналов ввода-вывода; Т - количество в+1ешних устройств) элементов И каждого из /-х узлов группы соединены между собой и подключены к /-МУ выходу второй группы выходов блока выбора конфигурации, второй вход (-ГО элемента ИЛИ второй группы соединен с вторыми входами остальных элементов ИЛИ той же группы и подключен к выходу второго элемента И, выход /-го элемента ИЛИ второй группы соединен со стробирую- дим входом /-ГО регистра первой группы, второй вход /-ГО элемента ИЛИ /-го узла группы подключен к выходу /-го элемента И /-ГО узла группы, выход/-го элемента ИЛИ /-ГО узла группы соединен с /-.м информационным входом /-ГО регистра первой группы а третий вход подключен к третьим входам /-Х элементов ИЛИ каждого из узлов и соединен с /-М выходом коммутатора, /-и вход которого является /-м входом из входов состояния устройств комплекса устройства.

20

9 С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для перезапуска вычислительного комплекса при обнаружении сбоя | 1984 |

|

SU1211734A1 |

| Устройство для перезапуска вычислительного комплекса при обнаружении сбоя | 1988 |

|

SU1541608A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1441399A1 |

| Устройство управления | 1989 |

|

SU1654820A1 |

| Канал обмена многомашинного комплекса | 1984 |

|

SU1236492A1 |

| Многоканальное устройство для распределения задачи процессорам | 1987 |

|

SU1444769A1 |

| Устройство для арбитража запросов | 1988 |

|

SU1596329A1 |

| Устройство для формирования очереди | 1986 |

|

SU1446626A1 |

| Устройство для анализа частоты использования блоков информации в вычислительных комплексах | 1990 |

|

SU1793442A1 |

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

Изобретение относится к вычислительной технике и может использоваться в многомашинных и многопроцессорных вычислительных системах для осуществления автоматического запуска и перезапуска вычислительного комплекса. Цель изобретения - повышение быстродействия за счет исключения попыток перезапуска вычислительного комплекса на конфигурациях, содержащих устройства, неисправные или выведенные из состава комплекса в данный момент. Для этого в устройство введены группа элементов НЕ, коммутатор, группа узлов элементов ИЛИ, вторая группа элементов ИЛИ, группа элементов И и группа узлов элементов И. Это позволяет при перезапуске вычислительного комплекса учесть информацию, выдаваемую системой контроля устройств, и тем самым исключить попытки перезапуска комплекса на неисправных устройствах. Устройство для перезапуска вычислительного комплекса при обнаружении сбоя содержит также два счетчика, три триггера, генератор импульсов, пять элементов ИЛИ, девять элементов И, группу формирователей импульсов, группу блоков управления, первую группу элементов ИЛИ, пять элементов задержки, две группы регистров, три мультиплексора, четыре демультиплексора, блок выбора конфигурации. 7 ил.

t t/ L JA k

ГтГ / 11

&

6

70w .

feOtt

Ш

ЧЭ

-о

Фа5,.5

Фие.б

/-W б ход

/y/J

г-идход

///J

Hy/iedoi/ гиг. тр. .„

дшод

дщод

Э/1.2

дым э/1,25

Вмлод

9Л,26

дм)(од 9/,27

Фие.7

| Устройство для перезапуска вычислительного комплекса при обнаружении сбоя | 1980 |

|

SU962956A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для перезапуска вычислительного комплекса при обнаружении сбоя | 1984 |

|

SU1211734A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-09-23—Публикация

1988-09-19—Подача