Изобретение относится к вычислительной технике и может быть использовано для обеспечения отладки и исследования рабочих программ (РП) пользователя как специализированных, так и универсальных вычислительных уст- . ройств, а также в системах обработки цифровой информации.

Цель изобретения - расширение функциональных возможностей устройства за счет формирования сигнала Останов по заданной команде на заданном цикле ее выполнения.

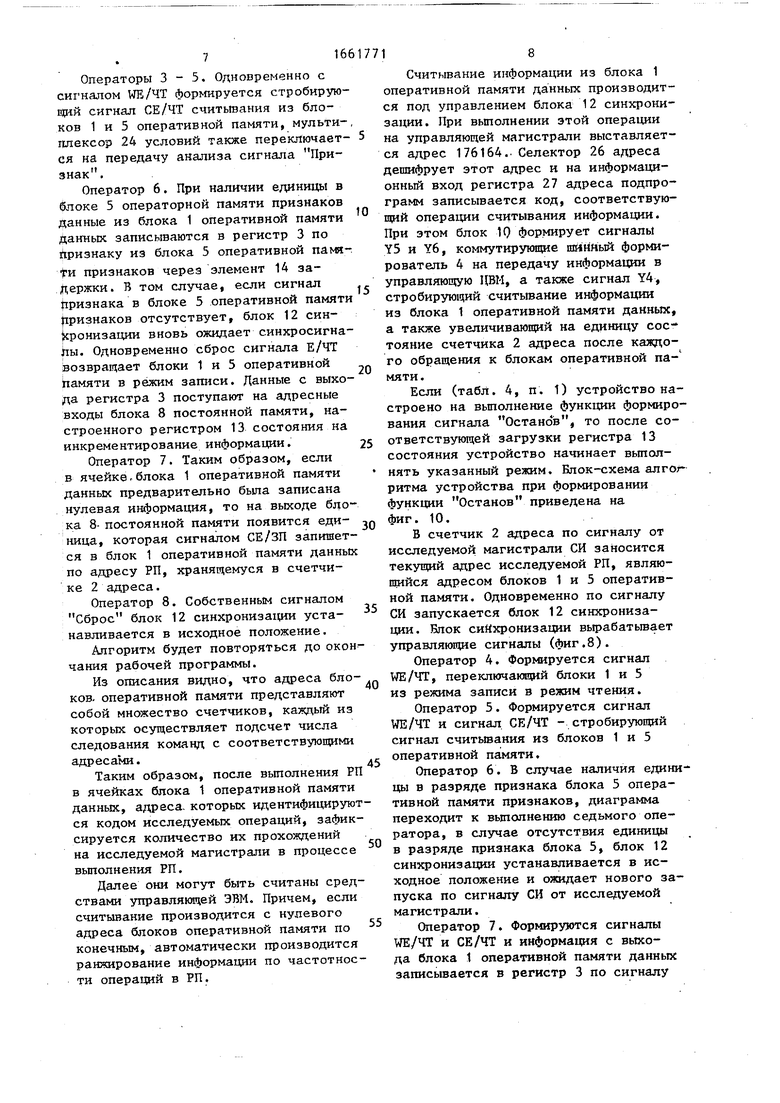

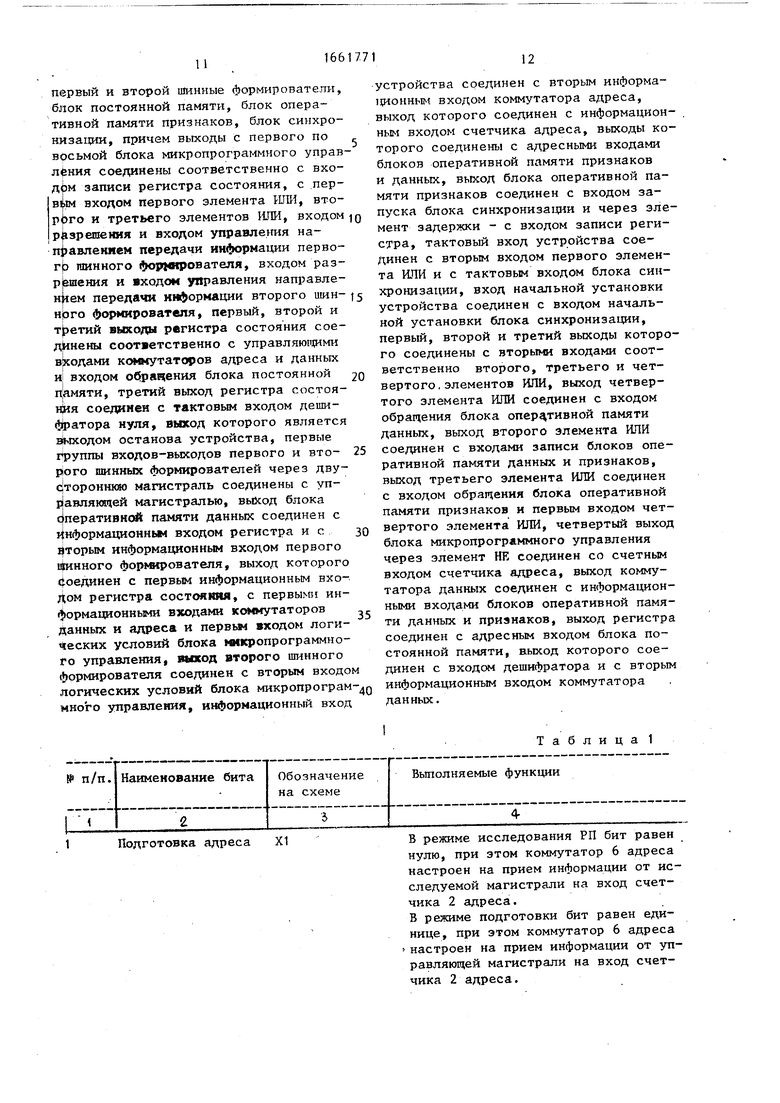

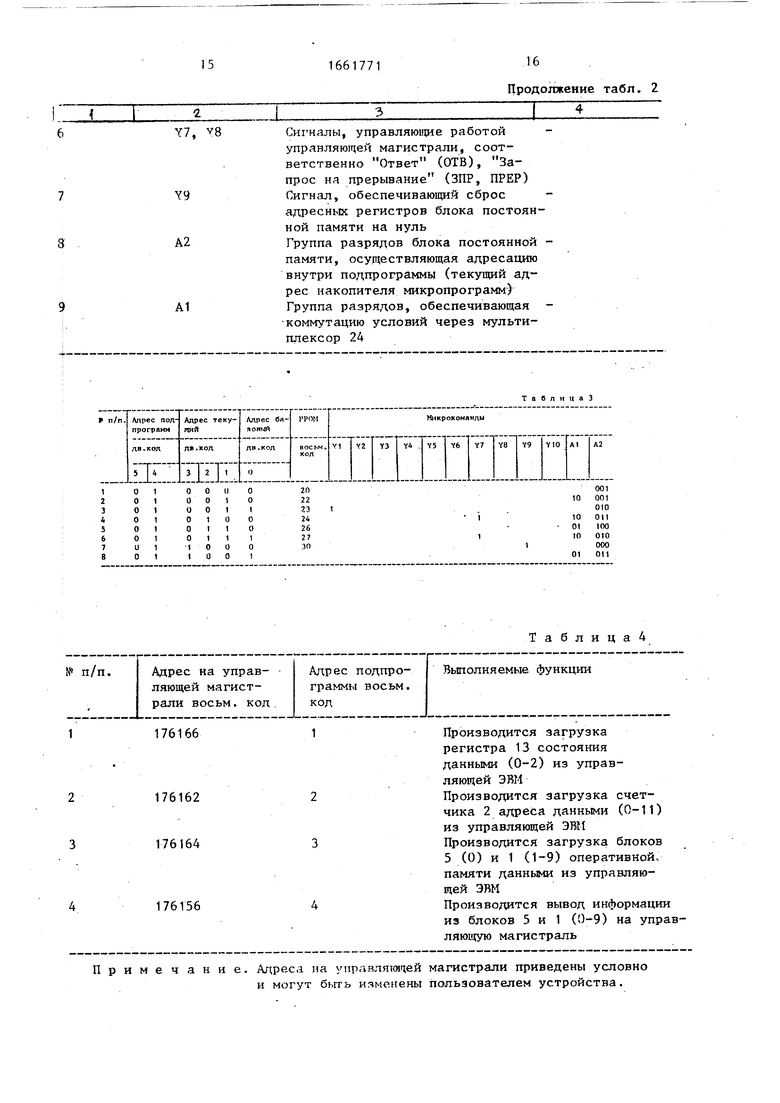

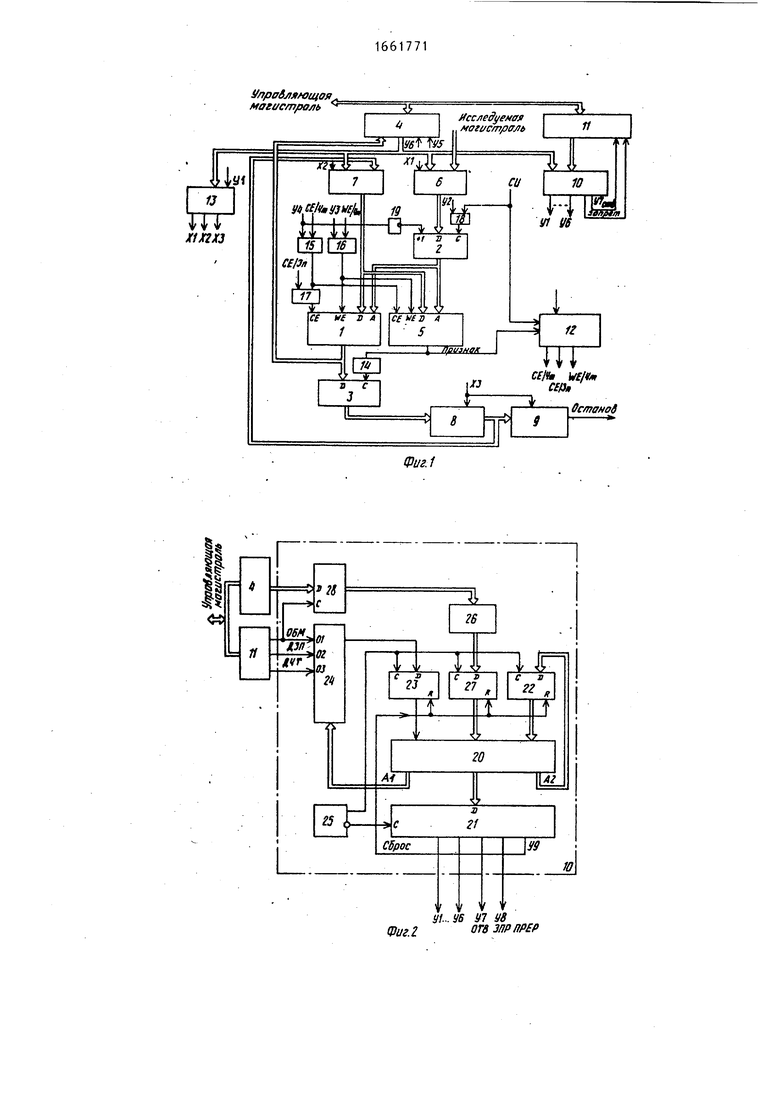

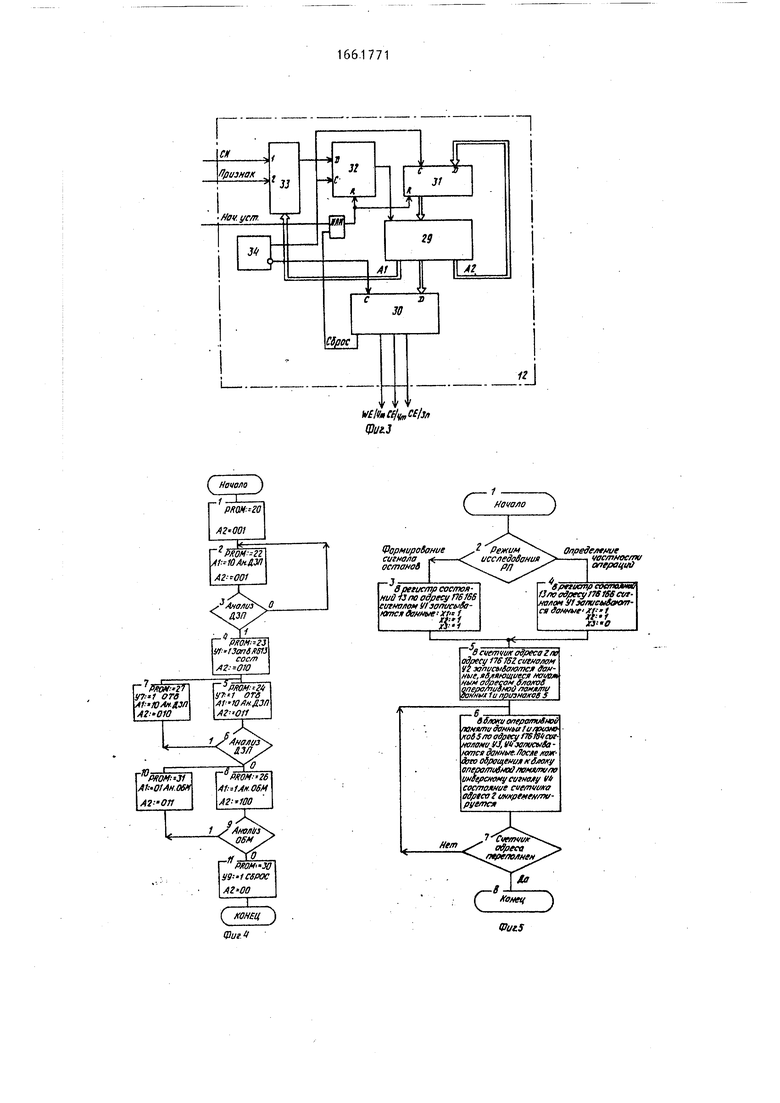

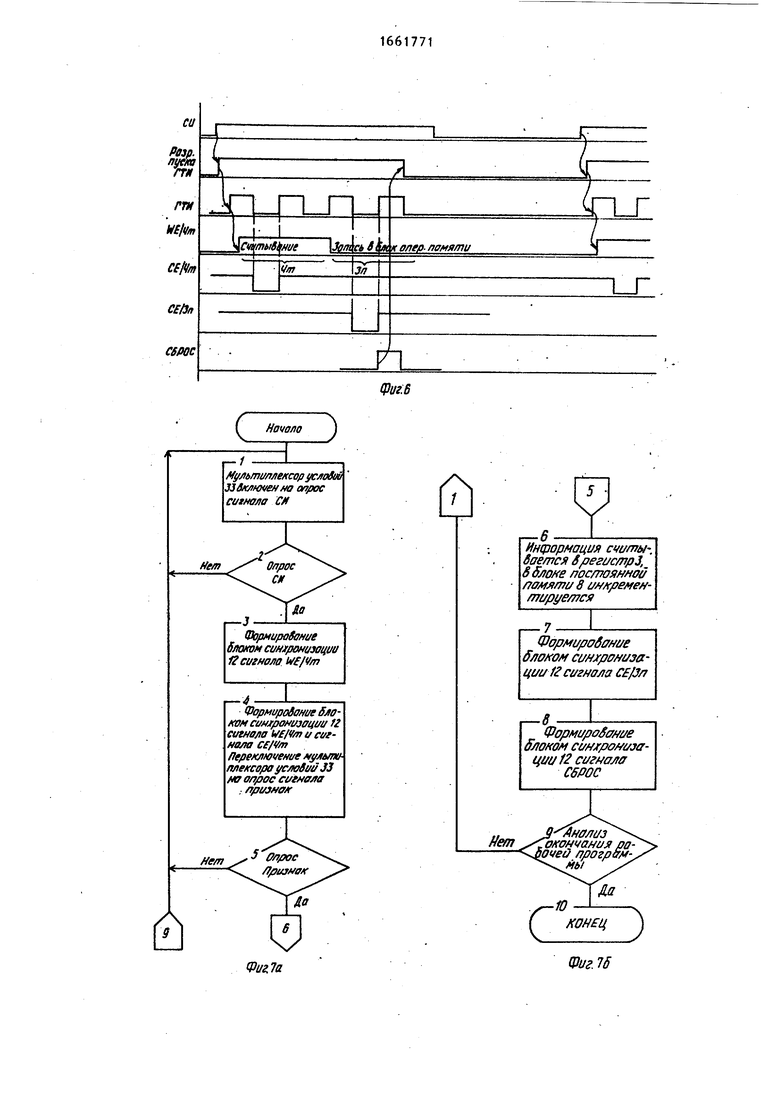

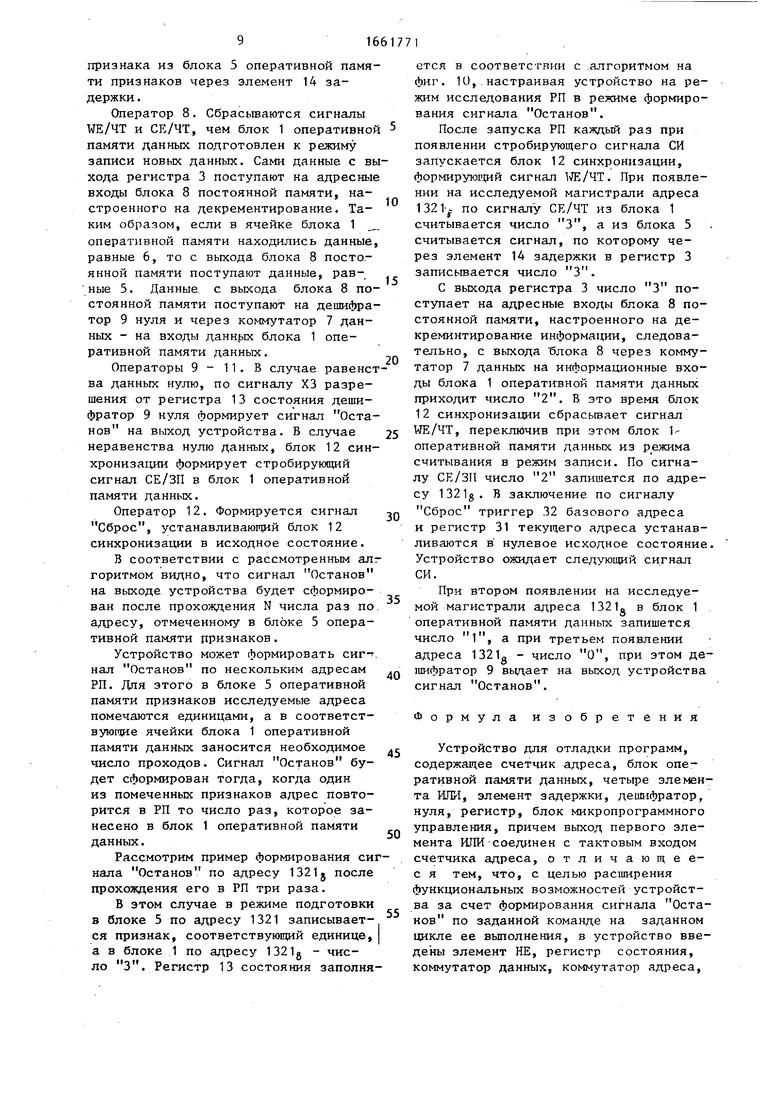

На фиг. 1 изображена функциональная схема устройства; на фиг, 2 - то же, блока микропрограммного управления; на фиг. 3 - то же, блока синхронизации; на фиг. 4 - алгоритм записи информации в регистр состояния; на ,фиг. 5 - алгоритм работы устройства в режиме подготовки блоков оперативной памяти; на фиг. 6 - временная диаграмма формирования сигналов синхрониза-т ции блоком синхронизации; на фиг.7а,б- алгоритм формирования сигналов блоком

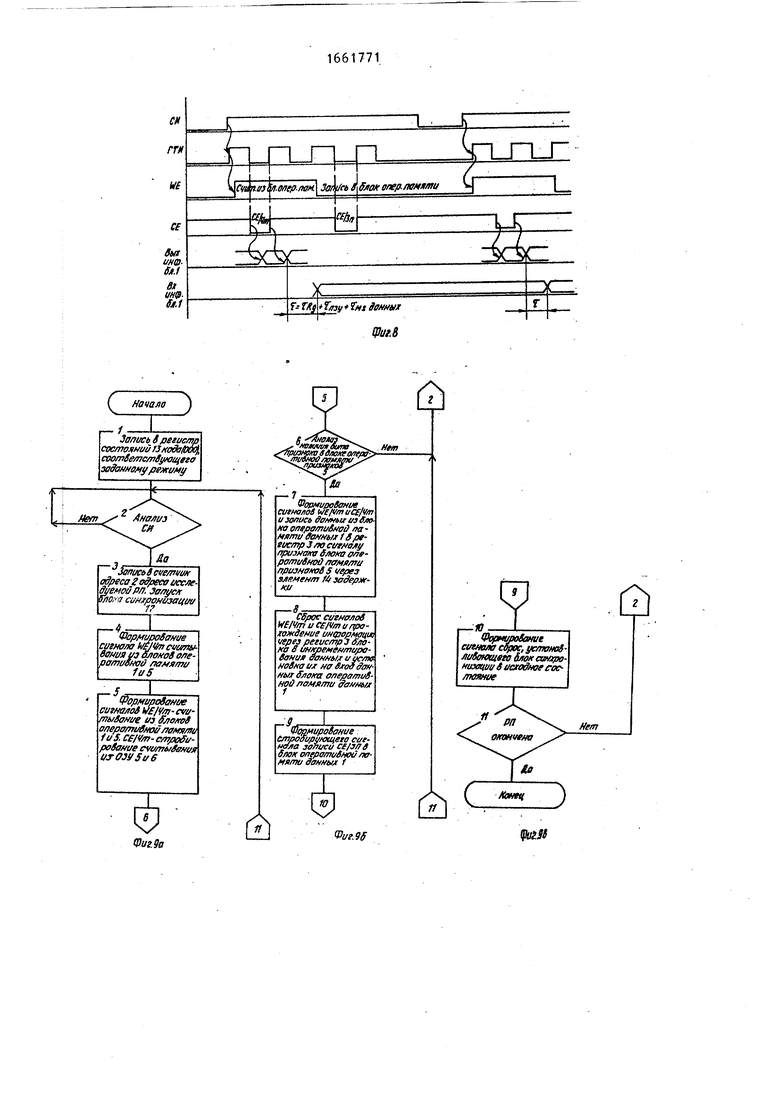

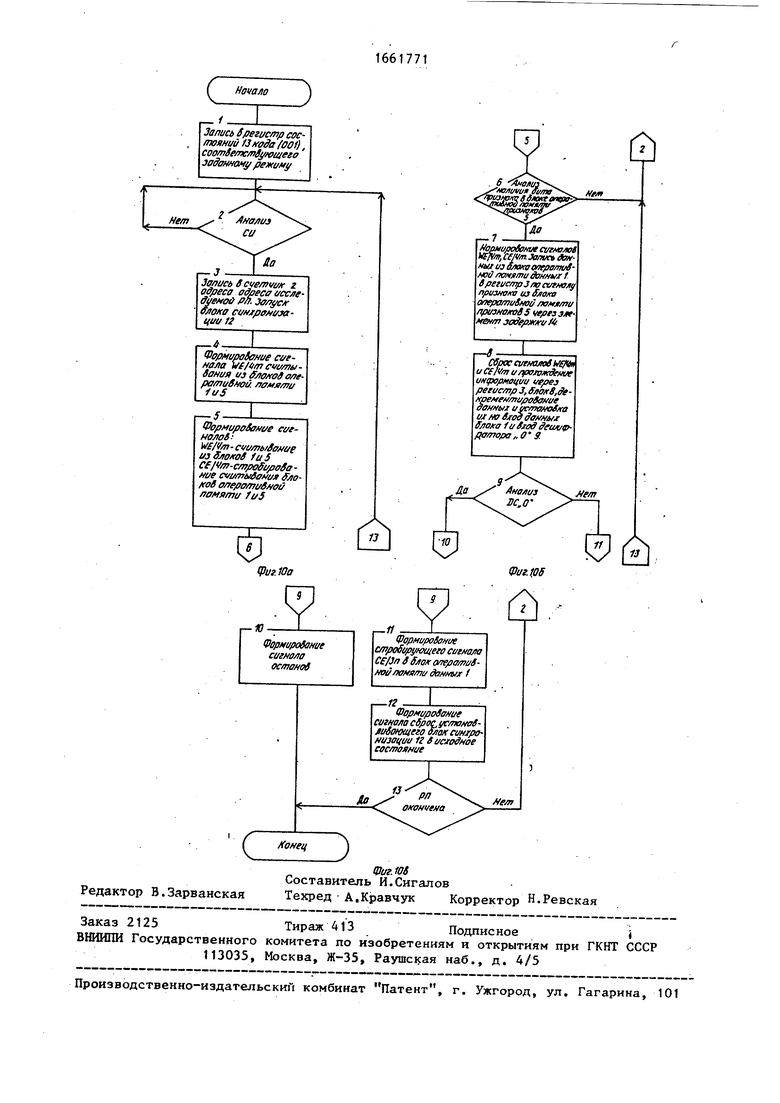

синхронизации; на фиг. 8 - временная диаграмма записи в блок оперативной памяти данных новой информации; на фиг. 9а,в - алгоритм работы устройства в режиме определения частотности , операций; на фиг. - то же, в режиме формирования сигнала Останов.

Устройство содержит (фиг. 1) блок 1 оперативной памяти данных, счетчик 2 адреса, регистр 3, первый шинный формирователь 4, блок 5 оперативной памяти признаков, коммутаторы адреса 6 и данных 7, блок 8 постоянной памяти, дешифратор 9 нуля, блок 10 микропрограммного управления, второй шинный формирователь 11, блок 12 синхронизации, регистр 13 состояния, элемент 14 задержки, четыре элемента ИЛИ 15-18, элемент НЕ 19.

Элемент ИЛИ 18 зяписывает информацию в счетчик 2 адреса по сигналу Y2 в режиме подготовки блоков оперативной памяти или по стробирую ему сигналу СИ от исследуемой магистрали.

i

(Л С

0

О5

sl

J

1

Элемент НЕ 19 обеспечивает наращива- ние значения счетчика 2 адреса по заданному фронту сигнала Y4 в режиме подготовки блоков оперативной памяти. Блок 10 микропрограммного управления (фиг. 2) содержит блок 20 постоянной памяти, регистр 21 микрокоманд, регистр 22 текущего адреса, триггер 23 базового адреса, мультиплексор 24 условий, генератор 25 тактовых импульсов, селектор 26 адреса, регистр 27 и 28 адреса.

Блок 12 синхронизации (фиг. 3) содержит блок 29 постоянной памяти, регистр 30 микрокоманд, регистр 31 текущего адреса, триггер 32 базового адреса, мультиплексор 33 условий, генератор 34 тактовых импульсов.

Устройство для отладки программ paботает в двух режимах: в режиме подготовки данных (загрузка блоков оперативной памяти) и в режиме исследования РП.

В режиме подготовки данных коммута торы адреса 6 и данных. 7 переключаются на прием информации от управляющей магистрали. В качестве устройства управления может быть использована управляющая ЦВМ или пульт оператора, обеспечивающий загрузку блоков оперативной памяти данных 1 и признаков 5. Переключение коммутаторов 6 и 7 на прием от соответствующего входа производится сигналами соответственно XI и Х2, формируемыми от регистра 13 состояния.

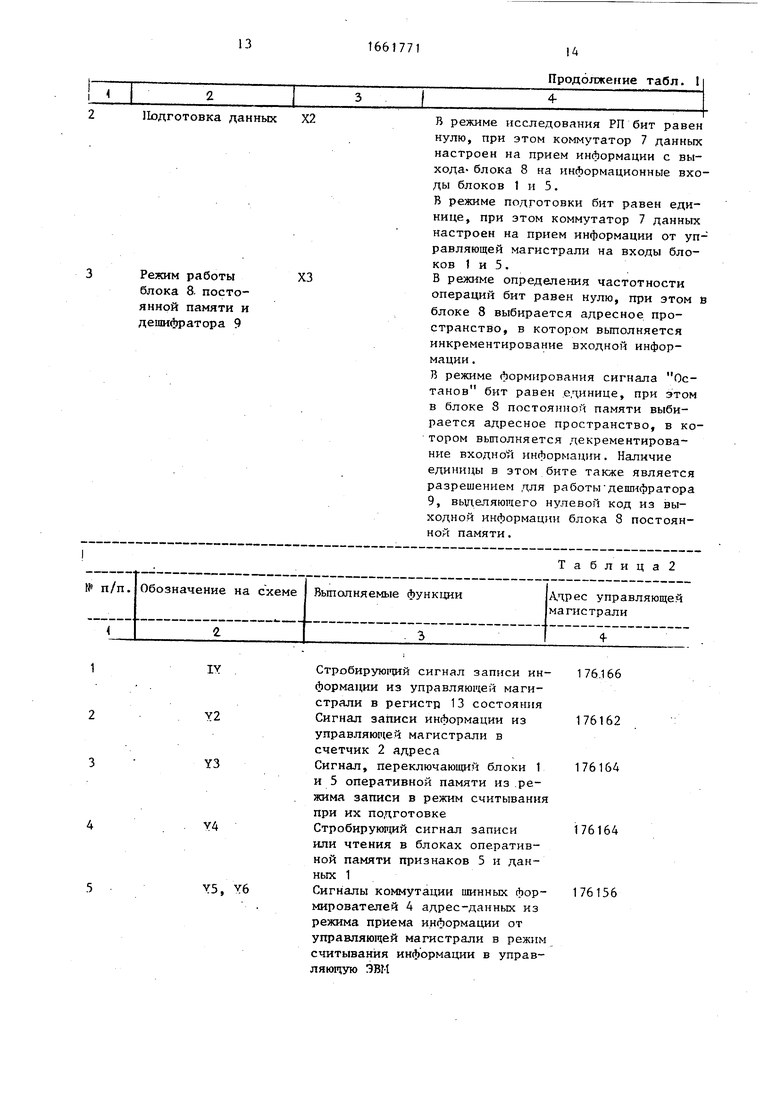

Состав и назначение, а также интерпретация битов регистра 13 состояния приведены в табл. 1.

Загрузка регистра 13 состояния производится данными, поступающими от управляющей магистрали при помощи и под управлением блока 10 микропрограммного управления (фиг.2).

Назначение микрокоманд блока 10 микропрограммного управления, интерпретация и соответствие адресному пространству на управляющей магистрали приведено в табл. 2.

Подпрограмма записи информации в регистр 13 состояния приведена в табл. 3.

Работу блока 10 рассмотрим на примере операции загрузки информации в регистр 13 состояния.

Из табл. 2 и фиг. 2 следует, что адрес 176166, соответствующий этой операции, сигналом ОВМ фиксируется

3

5

5

0

Q

5 п о

5

50

55

на регистре 28 адреса и поступает на вход селектора 26 адреса, откуда считывается код 01g, который поступает на информационный вход регистра 27 адреса подпрограмм.

Далее выполнение операции рассмотрим в объеме ее выполнения на каждом шаге оператора (фиг.4).

Оператор 1, Селектор 26 адреса, получив из управляющей ЭВМ адрес 176166, выдает код 01 на регистр 27 адреса подпрограмм. При наличии текущего адреса, равного нулю, и базового адреса, равного нулю, организуется адрес (табл. 3) блока 20 постоянной памяти, где по текущему адресу подпрограмма переходит к выполнению второго оператора.

Операторы 2 и 3. Формируется код на мультиплексор 24 условий для анализа сигнала ДЗП с управляющей магистрали. При условии наличия этого сигнала, т.е. лог. 1, на базовом входе и текущего адреса 001 подпрограмма переходит к выполнению четвертого оператора. При условии отсутствия сигнала на базовом входе подпрограмма повторяет второй и третий операторы.

Оператор 4. Формируется стробирую- щий сигнал Y1 записи в регистр 13 состояния. По текущему адресу под- пррграмма переходит к выполнению пятого оператора.

I

Оператор 5. Формируется сигнал -Y7 ,

в управляющую магистраль ОТВ о приеме информации. Одновременно формируется код А1 10 для анализа сигнала ДЗП с управляющей магистрали. По текущему адресу 011 подпрограмма переходит к выполнению шестого оператора.

Операторы 6 и 7. При условии наличия лог. 1 на базовом входе подпрограмма повторяет действие пятого оператора, так как происходит подготовка ожидания сброса сигнала ДЗП. При условии сброса этого сигнала, т.е. наличии на базовом входе лог. О, подпрограмма переходит к выполнению восьмого оператора.

Операторы 8 и 9. Формируется код для анализа сигнала ОВМ с управляющей магистрали. При условии наличия этого сигнала (базовый адрес ра- вей единице) через оператор 10 происходит зацикливание ожидания сброса сигнала ОБМ.

При условии сброса сигнала ОБМ (базовый адрес равен нулю) подпрограмма переходит к выполнению 11 оператора.

Оператор 11, Формируется сигнал Y9 сброса, устанавливающий регистры 27, 22 и триггер 23 в нулевое исходное положение.

Таким образом, после установки регистра 13 состояния в соответствующее состояние выполняется режим подготовки устройства к работе.

Устройство в режиме исследования рабочих программ может выполнять два подрежима: определение частотности операций при реализации РП; формирование сигнала Останов на выходе устройства после прохождения заданного числа раз через исследуемую команду, поэтому подготовка устройства, заключающаяся в заполнении блоков 1 и 5 оперативной памяти, для этих режимов тоже ведется по разному.

Подготовка блоков 1 и 5 оперативной памяти для выполнения подрежима определения частотности заключается в обнулении всех ячеек блока 1 оперативной памяти данных и записи единиц

При появлении на магистрали адреса 176164 блоков 1 и 5 оперативной памяти блок 10 управления формирует последовательно сигнал Y3, переключающий блоки 1 и 5 из режима считывания в режим записи, а в следующем такте кроме сигнала Y3 формирует стробирующий сигнал Y4 записи данных (3) в блок 1 оперативной памяти данных к записи данных (1) в блок 5 оперативной памяти признаков. После записи информа- ции в блоки 1 и 5 по заднему фронту сигнала Y4 значение счетчика 2 адреса инкрементируется.

Алгоритм работы устройства в режиме подготовки блоков оперативной . памяти представлен на фиг. 5.

Возможные операции (идентификация

0 функций обслуживания устройства, подпрограмм микропрограммного управления и адресного пространства управляющей магистрали), выполняемые устройством в режиме подготовки блоков оператив5 ной памяти, приведены в табл.4.

После окончания режима подготовки блоков оперативной памяти устройство готово к режиму исследования рабочих программ. В этом режиме устройством

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для контроля за ходом вычислительного процесса | 1987 |

|

SU1539780A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

Изобретение может быть применено в вычислительной технике. Цель изобретения - расширение функциональных возможностей за счет формирования сигнала "Останов" по заданной команде на заданном цикле ее выполнения. Устройство вырабатывает сигналы останова по заданным N адресам одновременно, при реализации программы на I-цикле

- формирует показатели частотности по каждой из N команд исследуемой рабочей программы

- обеспечивает ранжирование величин частотности каждой из исследуемых команд. 4 табл., 10 ил.

во все ячейки блока 5 оперативной па- 30 управляет блок 12 синхронизации

мяти признаков из управляющей магистрали, т.е. от управляющей ЦВМ.

Подготовка блоков 1 и 5 оперативной памяти для выполнения режима фор(фиг. 3). Кодом А1 с регистра 30 рокоманд мультиплексор 33 услови настроен на прием синхросигнала от исследуемой магистрали. В сче

мирования сигнала Останов заключает-,5 2 адреса по сигналу СИ заносится

ся в занесении в блок 1 оперативной памяти данных информации , соответствующей числу прохождения РП через исследуемый адрес. В эти же адреса в блоке 5 оперативной памяти признаков заносятся единицы.

В качестве примера рассмотрим заполнение блоков 1 и 5 оперативной памяти для режима формирования сигнала Останов по любому, допустим 13218, адресу из всего адресного пространства, допустим от 0 до 4К, после прохождения по этом адресу N, допустим 3, число раз.

В этом случае в регистр 13 состояния по адресу 176166 и по сигналу Yt записываются данные , , , переключающие коммутаторы адреса 6 и данных 7 на прием информации от управляющей магистрали.

В счетчик 2 адреса по адресу 176162 по сигналу Y2 записываются данные (1321g), являющиеся адресом блоков 1 и 5 оперативной памяти ОЗУ.

адрес исследуемой РП, являющийся ресом блоков 1 и 5 оперативной па ти. Одновременно по сигналу СИ за пускается блок 12 синхронизации. 40 менная диаграмма работы блока 12 хронизации представлена на фиг. 6

45

50

55

Стробирующий сигнал СИ по так вым импульсам от генератора 34 т вых импульсов записывается в три гер 32 базового адреса, начиная, самым, формирование последовател ности стробирующих сигналов WE/4 СЕ/ЧТ, СЕ/ЗП. Переход к новым ад вам блока 29 постоянной памяти о ствляется по коду А2 через регис 31 текущего адреса.

Алгоритм работы блока 12 синх низации приведен на фиг. 7.

Операторы 1 и 2. Получив синх сигнал СИ исследуемой магистрали блок 12 синхронизации формирует нал WE/ЧТ, переключающий блоки 1 из режима записи в режим считыва

(фиг. 3). Кодом А1 с регистра 30 микрокоманд мультиплексор 33 условий настроен на прием синхросигнала СИ от исследуемой магистрали. В счетчик

,5 2 адреса по сигналу СИ заносится

адрес исследуемой РП, являющийся адресом блоков 1 и 5 оперативной памяти. Одновременно по сигналу СИ запускается блок 12 синхронизации. Вре- 40 менная диаграмма работы блока 12 синхронизации представлена на фиг. 6.

5

0

5

Стробирующий сигнал СИ по тактовым импульсам от генератора 34 тактовых импульсов записывается в триггер 32 базового адреса, начиная, тем самым, формирование последовательности стробирующих сигналов WE/4T, СЕ/ЧТ, СЕ/ЗП. Переход к новым адре- вам блока 29 постоянной памяти осуществляется по коду А2 через регистр 31 текущего адреса.

Алгоритм работы блока 12 синхронизации приведен на фиг. 7.

Операторы 1 и 2. Получив синхросигнал СИ исследуемой магистрали, блок 12 синхронизации формирует сигнал WE/ЧТ, переключающий блоки 1 и 5 из режима записи в режим считывания.

Операторы 3-5. Одновременно с сигналом WE/ЧТ формируется стробирующий сигнал СЕ/ЧТ считывания из блоков 1 и 5 оперативной памяти, мультиплексор 24 условий также переключает- ся на передачу анализа сигнала Признак.

Оператор 6. При наличии единицы в блоке 5 операторной памяти признаков данные из блока 1 оперативной памяти данных записываются в регистр 3 по признаку из блока 5 оперативной памя- tH признаков через элемент 14 задержки. В том случае, если сигнал Признака в блоке 5 оперативной памяти Признаков отсутствует, блок 12 син- (кронизации вновь ожидает синхросигналы. Одновременно сброс сигнала Е/ЧТ возвращает блоки 1 и 5 оперативной памяти в режим записи. Данные с выхода регистра 3 поступают на адресные входы блока 8 постоянной памяти, настроенного регистром 13 состояния на инкрементирование информации.

Оператор 7. Таким образом, если в ячейке.блока 1 оперативной памяти данных предварительно была записана нулевая информация, то на выходе блока 8- постоянной памяти появится еди- ница, которая сигналом СЕ/ЗП запишется в блок 1 оперативной памяти данных по адресу РП, хранящемуся в счетчике 2 адреса.

Оператор 8. Собственным сигналом Сброс блок 12 синхронизации устанавливается в исходное положение.

Алгоритм будет повторяться до окончания рабочей программы.

Из описания видно, что адреса бло- ков. оперативной памяти представляют собой множество счетчиков, каждый из которых осуществляет подсчет числа следования команд с соответствующими адресами.

Таким образом, после выполнения РП в ячейках блока 1 оперативной памяти данных, адреса которых идентифицируются кодом исследуемых операций, зафиксируется количество их прохождений на исследуемой магистрали в процессе выполнения РП.

Далее они могут быть считаны средствами управляющей ЭВМ. Причем, если считывание производится с нулевого адреса блоков оперативной памяти по конечным, автоматически производится ранжирование информации по частотности операций в РП.

, т- 5 16617718

Считывание информации

0

0

5

, 5

. 5

50

оперативной памяти данных производится под управлением блока 12 синхронизации. При выполнении этой операции на управляющей магистрали выставляется адрес 176164. Селектор 26 адреса дешифрует этот адрес и на информационный вход регистра 27 адреса подпрограмм записывается код, соответствующий операции считывания информации. При этом блок 1Q формирует сигналы Y5 и Y6, коммутирующие шинный формирователь 4 на передачу информации в управляющую ЦВМ, а также сигнал Y4, стробирующий считывание информации из блока 1 оперативной памяти данных, а также увеличивающий на единицу состояние счетчика 2 адреса после каждого обращения к блокам оперативной па- мяти.

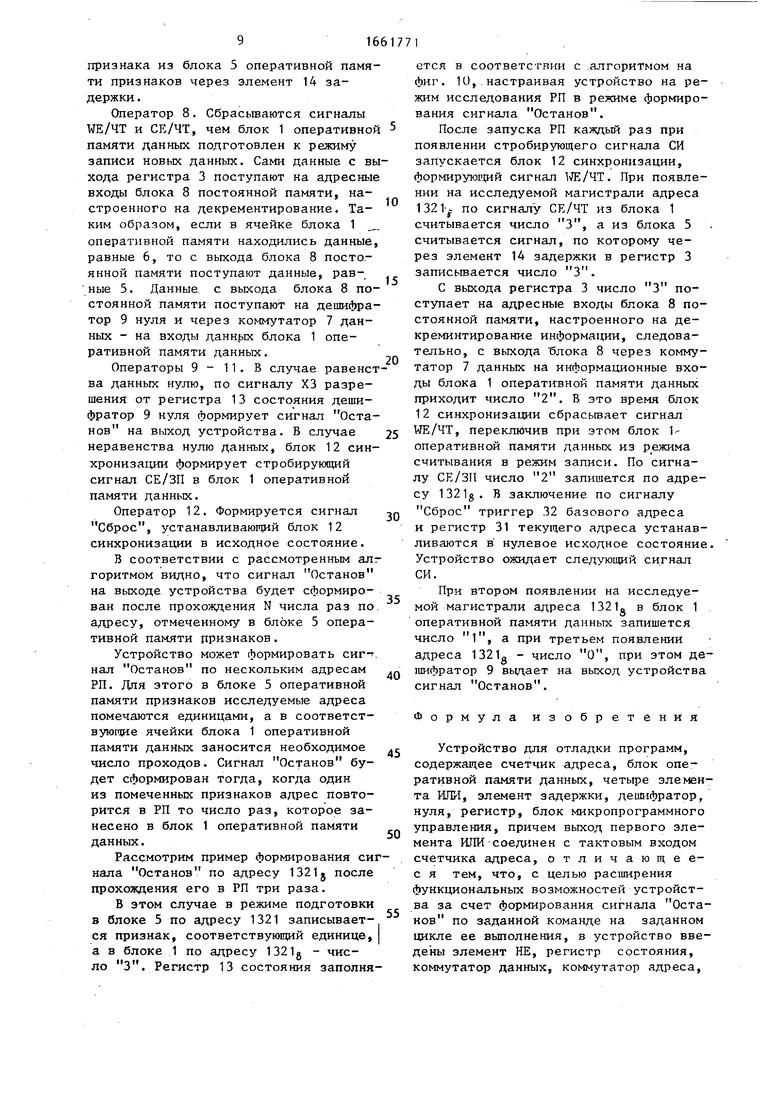

Если (табл. 4, п. 1) устройство настроено на выполнение функции формирования сигнала Останов, то после соответствующей загрузки регистра 13 состояния устройство начинает выполнять указанный режим. Блок-схема алгог- ритма устройства при формировании функции Останов приведена на фиг. 10.

В счетчик 2 адреса по сигналу от исследуемой магистрали СИ заносится текущий адрес исследуемой РП, являющийся адресом блоков 1 и 5 оперативной памяти. Одновременно по сигналу СИ запускается блок 12 синхронизации. Блок синхронизации вырабатывает управляющие сигналы (фиг.8).

Оператор 4. Формируется сигнал WE/ЧТ, переключающий блоки 1 и 5 из режима записи в режим чтения.

Оператор 5. Формируется сигнал WE/ЧТ и сигнал СЕ/ЧТ - стробирующий сигнал считывания из блоков 1 и 5 оперативной памяти.

Оператор 6. В случае наличия единицы в разряде признака блока 5 оперативной памяти признаков, диаграмма переходит к выполнению седьмого оператора, в случае отсутствия единицы в разряде признака блока 5, блок 12 синхронизации устанавливается в исходное положение и ожидает нового запуска по сигналу СИ от исследуемой магистрали.

Оператор 7. Формируются сигналы WE/ЧТ и СЕ/ЧТ и информация с выхода блока 1 оперативной памяти данных записывается в регистр 3 по сигналу

признака из блока 5 оперативной памяти признаков через элемент 14 задержки .

Оператор 8. Сбрасываются сигналы WE/ЧТ и СЕ/ЧТ, чем блок 1 оперативной памяти данных подготовлен к режиму записи новых данных. Сами данные с выхода регистра 3 поступают на адресные входы блока 8 постоянной памяти, настроенного на декрементирование. Таким образом, если в ячейке блока 1 оперативной памяти находились данные, равные 6, то с выхода блока 8 постоянной памяти поступают данные, равные 5. Данные с выхода блока 8 постоянной памяти поступают на дешифратор 9 нуля и через коммутатор 7 данных - на входы данных блока 1 оперативной памяти данных.

Операторы 9 - 11. В случае равенства данных нулю, по сигналу ХЗ разрешения от регистра 13 состояния дешифратор 9 нуля формирует сигнал Останов на выход устройства. В случае неравенства нулю данных, блок 12 синхронизации формирует стробирующий сигнал СЕ/ЗП в блок 1 оперативной памяти данных.

Оператор 12. Формируется сигнал Сброс, устанавливающий блок 12 синхронизации в исходное состояние.

В соответствии с рассмотренным алг горитмом видно, что сигнал Останов на выходе устройства будет сформирован после прохождения N числа раз по адресу, отмеченному в блоке 5 оперативной памяти признаков.

Устройство может формировать сигнал Останов по нескольким адресам РП. Для этого в блоке 5 оперативной памяти признаков исследуемые адреса помечаются единицами, а в соответствующие ячейки блока 1 оперативной памяти данных заносится необходимое число проходов. Сигнал Останов будет сформирован тогда, когда один из помеченных признаков адрес повторится в РП то число раз, которое занесено в блок 1 оперативной памяти данных.

Рассмотрим пример формирования сиг нала Останов по адресу 1321j после прохождения его в РП три раза.

В этом случае в режиме подготовки в блоке 5 по адресу 1321 записывается признак, соответствующий единице, а в блоке 1 по адресу 1321g - число 3. Регистр 13 состояния заполня

ется в соответствии с алгоритмом на фиг. 10, настраивая устройство на режим исследования РП в режиме формирования сигнала Останов.

После запуска РП каждый раз при появлении стробирующего сигнала СИ запускается блок 12 синхронизации, формирующий сигнал WE/ЧТ. При появлении на исследуемой магистрали адреса 1321- по сигналу СЕ/ЧТ из блока 1

считывается число

а из блока 5

5

0

5

0

5

0

45

50

55

считывается сигнал, по которому через элемент 14 задержки в регистр 3 записывается число 3.

С выхода регистра 3 число 3 поступает на адресные входы блока 8 постоянной памяти, настроенного на де- креминтирование информации, следовательно, с выхода блока 8 через коммутатор 7 данных на информационные входы блока 1 оперативной памяти данных приходит число 2. В это время блок 12 синхронизации сбрасывает сигнал WE/ЧТ, переключив при этом блок 1- оперативной памяти данных из режима считывания в режим записи. По сигналу СЕ/ЗП число 2м запишется по адресу 1321g. В заключение по сигналу Сброс триггер 32 базового адреса и регистр 31 текущего адреса устанавливаются в нулевое исходное состояние. Устройство ожидает следующий сигнал СИ.

При втором появлении на исследуемой магистрали адреса 1321 в блок 1 оперативной памяти данных запишется число 1, а при третьем появлении адреса 1321g - число О, при этом дешифратор 9 выдает на выход устройства сигнал Останов.

Формула изобретения

Устройство для отладки программ, содержащее счетчик адреса, блок оперативной памяти данных, четыре элемента ИЛИ, элемент задержки, дешифратор, нуля, регистр, блок микропрограммного управления, причем выход первого элемента ИЛИ соединен с тактовым входом счетчика адреса, отличающее- с я тем, что, с целью расширения функциональных возможностей устройства за счет формирования сигнала Останов по заданной команде на заданном цикле ее выполнения, в устройство введены элемент НЕ, регистр состояния, коммутатор данных, коммутатор адреса,

первый и второй шинные формирователи, блок постоянной памяти, блок оперативной памяти признаков, блок синхронизации, причем выходы с первого по восьмой блока микропрограммного управления соединены соответственно с вхо- записи регистра состояния, с пер- siiM входом первого элемента ИЛИ, второго и третьего элементов ИЛИ, входом разрешения и входом управления направлением передачи информации перво- г(э шинного формирователя, входом разрешения и входом управления направле- щсем передачи информации второго шин- ного формирователя, первый, второй и третий выходы регистра состояния соединены соответственно с управляющими вводами коммутаторов адреса и данных и входом обращения блока постоянной памяти, третий выход регистра состояния соединен с тактовым входом дешифратора нуля, выход которого является выходом останова устройства, первые группы входов-выходов первого и вто- рого шинных формирователей через двустороннюю магистраль соединены с управляющей магистралью, выход блока оперативной памяти данных соединен с Информационным входом регистра и с вторым информационным входом первого Йинного формирователя, выход которого Соединен с первым информационным входом регистра состояния, с первыми информационными входами коммутаторов Данных и адреса и первым входом логических условий блока микропрограммного управления, выход второго шинного формирователя соединен с вторым входо логических условий блока микропрограм много управления, информационный вход

Подготовка адреса Х1

устройства соединен с вторым информационным входом коммутатора адреса, выход которого соединен с информационным входом счетчика адреса, выходы которого соединены с адресными входами блоков оперативной памяти признаков и данных, выход блока оперативной памяти признаков соединен с входом запуска блока синхронизации и через элемент задержки - с входом записи регистра, тактовый вход устройства соединен с вторым входом первого элемента ИЛИ и с тактовым входом блока синхронизации, вход начальной установки устройства соединен с входом начальной установки блока синхронизации, первый, второй и третий выходы которого соединены с вторыми входами соответственно второго, третьего и четвертого, элементов ИЛИ, выход четвертого элемента ИЛИ соединен с входом обращения блока оперативной памяти данных, выход второго элемента ИЛИ соединен с входами записи блоков оперативной памяти данных и признаков, выход третьего элемента ИЛИ соединен с входом обращения блока оперативной памяти признаков и первым входом четвертого элемента ИЛИ, четвертый выход блока микропрограммного управления через элемент НЕ соединен со счетным входом счетчика адреса, выход коммутатора данных соединен с информационными входами блоков оперативной памяти данных и признаков, выход регистра соединен с адресным входом блока постоянной памяти, выход которого соединен с входом дешифратора и с вторым информационным входом коммутатора данных.

В режиме исследования РП бит равен нулю, при этом коммутатор 6 адреса настроен на прием информации от исследуемой магистрали на вход счетчика 2 адреса.

В режиме подготовки бит равен единице, при этом коммутатор 6 адреса настроен на прием информации от управляющей магистрали на вход счетчика 2 адреса.

Подготовка данных Х2

Режим работы блока 8. постоянной памяти и дешифратора 9

V6

Стробирующий сигнал записи ин- 176166 формации из управляющей магистрали в регистр 13 состояния Сигнал записи информации из 176162 управляющей магистрали в счетчик 2 адреса

Сигнал, переключающий блоки 1 176164 и 5 оперативной памяти из режима записи в режим считывания при их подготовке

Стробирующий сигнал записи 176164 или чтения в блоках оперативной памяти признаков 5 и данных 1

Сигналы коммутации шинных фор- 176156 мирователеч 4 адрес-данных из режима приема информации от управляющей магистрали в режим считывания информации в управляющую ЭВМ

В режиме исследования РП бит равен нулю, при этом коммутатор 7 данных настроен на прием информации с выхода- блока 8 на информационные входы блоков 1 и 5.

В режиме подготовки бит равен единице, при этом коммутатор 7 данных настроен на прием информации от управляющей магистрали на входы блоков 1 и 5.

В режиме определения частотности операций бит равен нулю, при этом блоке 8 выбирается адресное пространство, в котором выполняется инкрементирование входной информации .

В режиме формирования сигнала Останов бит равен единице, при этом в блоке 8 постоянной памяти выбирается адресное пространство, в котором выполняется декрементирова- ние входной информации. Наличие единицы в этом бите также является разрешением для работы дешифратора 9, выделяющего нулевой код из выходной информации блока 8 постоянной памяти.

Таблица2

vs

Сигналы, управляющие работой управляющей магистрали, соответственно Ответ (ОТВ), Запрос на прерывание (ЗПР, ПРЕР) Сигнал, обеспечивающий сброс адресных регистров блока постоянной памяти на нуль Группа разрядов блока постоянной - памяти, осуществляющая адресацию внутри подпрограммы (текущий адрес накопителя микропрограмм) Группа разрядов, обеспечивающая коммутацию условий через мультиплексор 24

176166

176162

176164

176156

Примечание. Адреса на управляющей магистрали приведены условно

и могут быть изменены пользователем устройства.

Продолжение табл. 2

ТаблицаЗ

Производится загрузка регистра 13 состояния данными (0-2) из управляющей ЭВМ

Производится загрузка счетчика 2 адреса данными (0-11) из управляющей ЭВМ Производится загрузка блоков 5 (0) и 1 (1-9) оперативной памяти данными из управляющей ЭВМ

Производится вывод информации из блоков 5 и 1 (0-9) на упраляющую магистраль

)1/ОС/ШЭЛЗОН

xotn(H ifyoc/i//i

уд:-1С5Рос

AZ-OO

Mf/fcflfo,«/Jfr

фиг.3

-% Режим исследования РЛ

Определение

частности операций

врпоапрсоапш&Я (Зло адресу 1761S6 cot- налом У1 записываются донные хЈ 1

ecutmvuKofffleceZao адресу пекгсиенолом У г эаписыйтолкя ванные,являющиеся тиал ным адресом lepofnuSHou ломят/ Унт fa признаков 5

е .

Плохи оперативной пошила донниг t if Ogata- /raSS/roa&iecytJSiSt/a/r- малами Vf,W xnucttta - нхпся данные ffoc/ie каждою обращения к блоху onfpa/nulHoutiofwnt/no инверсному сигналу VI состояние cuemvma oSplca г UN/tptMe/tmtr- руется

QlutS

CSPOC

С

Начало

)

-1

Мультиплексор условно ЗЗбключенна спрос сигнала СИ

-3

Формирование блоком синхронизации 12 сигнала Wf/Vm

I

- 4ФормироЙоние 5ло- ком синхронизации Л сигнала VЈ/Vm и согнала Cf/Vm Переключение культи тексора условий 33 но опрос сигнала : /fpt/зна

фиг.6

Т

-6

Информация счи/лы-. бается брегис/прЗ, 85локе постоянной памяти 8 инкрементируе/яся

- 71

Формирование блоком синхронизации К сигнала CЈ/J/7

г-В -

Формиробание 5локом синхронизации f 2 сигналя С6РОС

Щи г. 7S

T nj +fiay fat iofwta Put 8

Начало

3

11

ФигИп

Pc/f.9f

U)

№Sl

С

Начало

)

,- .

Запись 6регистр состояний (Зтда fool), coomSemanSytoutefo заданному режиму

г-3

Запись всчелн/и г адреса адреса исследуемой flfi. залусг слона сумрониза- ции tl

Форм/радение сигнала Vf/t/mcvt/mtt- вания из ff/юяов оперативной, памяти iuS

- 51

IPopMupoSawe ct/e- налоЯ

считывание из8лояо8 fu5 Cf/v/n-c/npoSi/paSa - we считывания f/io- ков олеро/m/Swu ламя/ntf ft/5

w

фигЮа

таттв

1 яа

Нормирование сигналов Wffm, ff/vm Jamtn Aw- нш t/j а/юкаоаеротгв- tau ломят/ Агнмнг f

tpetVCmp3/X С1ЯНвЛ1/

признака из fjtom оаератиВнои помяли/ лризноюв5 через нент задержга /4

Сброс сугномй м&ь и Cf/v/ir ифот/кдгние инфорноции vepej регистр 3, йюк8,де- ярементиробоние еанн&1 uKynaffoixa ш на Йхоо данных ffjiotea 1 и txod деил/ip- Д(т/гюрапО 9

г-#

Формиро60н1/е апробирующего сигнала Cf/Jfr S fjiax опера/лав- ноу понята данных 1

й-1

Формирование сигнала c6poc,ycfno#ot- лабокхцего олок синхронизации п St/ctadnoe состояние

| Устройство для отладки программ | 1984 |

|

SU1166122A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для определения частот обращения к программам | 1985 |

|

SU1357963A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-07—Публикация

1988-08-22—Подача