pa, единичный выход которого соединен с вторыми входами второго, -третьего и четвертого элементов И, а единичный вход подключен к выходу пятого элемента И, второй вход которого соединен с выходом третьего мультиплексора, группа информационных входов которого подключена к группе -входов седьмого элемента И и входам останова блоков управления группы, входы пуска которых соединены с группой выходов второго демуль- типйексора, информационный вход ко- торого подключен к вькоду восьмого элемента И, первьй вход которого подключен к информационному входу тре- % тьего демультиплексора, к первому входу блока выбора конфигурации, к вьтоду второго элемента И и к информационному входу первого демультиплексора, группа выходов которого соединена с входами стробирования приема регистров первой группы, второй вход восьмого элемента И соединен с выходом четвертого элемента ИЛИ, группа входов которого соединена с первой группой выходов блока выбора конфигурации и с группами информационных входов регистров второй группы группы выходов регистров второй группы являются группой выходов задания режима устройства и соединена с группой информационных входов второго мультиплексора, группа выходов которого соединена с первой группой входов блока выбора конфигурации, вторая группа выходов которого соединена с группами информационных входов регистров первой группы, группы выходов регистров первой группы подключены к группе информационных входов первого мультиплексора и группе входов девятого элемента И, вход которого подключен к выходу седьмого элемента И, а выход является выходом отказа устройства, группа выходов первого мультиплексора подключена к второй группе входов блока выбора конфигурации, второй вход которого соединен с выходом четвертого элемента И, а третий вход соединен с выходом третьего элемента И и с информационным входом четвертого демультиплексора, группа выходов которого подключена к вторым входам элементов ИЛИ первой группы, выходы которых соединены с установочными входами регистров второй группы, выходы окончания перезапуска блоков управления группы соединены с группой входов пятого элемента ИЛИ, выход которого подключен к третьему входу второго элемента ИЛИ, группы входов состояния блоков управления группы являются группами входов состояния устройства, а группы выходов - группами командных выходов устройства, грзшпа выхода третьего демультиплексора соединена с входами стробирования приема регистров второй группы, нулевой выход первого триггера подключен к второму входу первого элемента И, причем блок выбора конфигурации содержит две группы узлов элементов И, две группы элементов И, группу узлов элементов ИЛИ, регистр три узла элементов ИЛИ, элемент ИЛИ две группы элементов НЕ и три узла триггеров, причем группы входов узлов элементов И первой группы соединены с первой группой входов блока, входы - с вторым входом блока, а группы выходов подключены к группам входов соответствующих узлов элементов ИЛИ группы, входы которых соединены с установочным входом блока, а группы выходов - с первьпчи группами входов первого, второго и третьего узлов триггеров, вторьге группы входов которых подключены к группам выходов соответствующих узлов элементов И второй группы, входы которых соединены с первым входом блока, а группы входов - с группами выходом первого, второго и третьего узлов элементов ИЛИ и первой группой выходов блока, группа выходов регистра является второй группой выходов блока и подключена к группам входов первого, второго и третьего узлов элементов ИЛИ, группы выходов первого, второго и третьего узлов триггеров соединены с группами входов элементов И -первой группы, выходы которых подключень к первым входам соот- ветствуняцих элементов И второй группы, выходы которых соединены с- группой входов регистра и входами элементов НЕ первой группы, а вторые входы через элементы НЕ Е(торой группы - с второй группой входов блока, выход каждого элемента НЕ первой группы подключен к группам входов последукяцих элементов И второй группы, управляющий вход и вход сброса регистра соединены соответственно с третьим входом блока и выходом элемента ИЛИ, первый и второй входы ко торого подключены соответственно к установочному и второму входам блока, при этом блок управления группы содержит группу элементов И, два счетчика, дешифратор, генератор импульсов, элемент И, триггер, три элемента ИЛИ, элемент задержки и элемент ИЛИ-НЕ, причем группа выходов дешифратора является группой командных выходов блока и соединена с группой входов элемента ИЛИ-НЕ и первыми входами элементов И группы, вторые входы которых подключены к группе входов состояния блока, группы входов дешифратора соединены с группой выходов первого счетчика, счетный вход и вход сброса которого подключены соответственно к выходам первого и второго элементов ШШ и к ер нкчяо- му и нулевому входам триггера, выход которого и выход генератора импуль. 1

Изобретение относится к вычнсли- тельной технике и может быть использовано в многомашинных и многопроцессорных системах для осуществления автоматического запуска и перезапуска вычислительного комплекса.

Целью изобретения является повьш1е- ние быстродействия устройства.

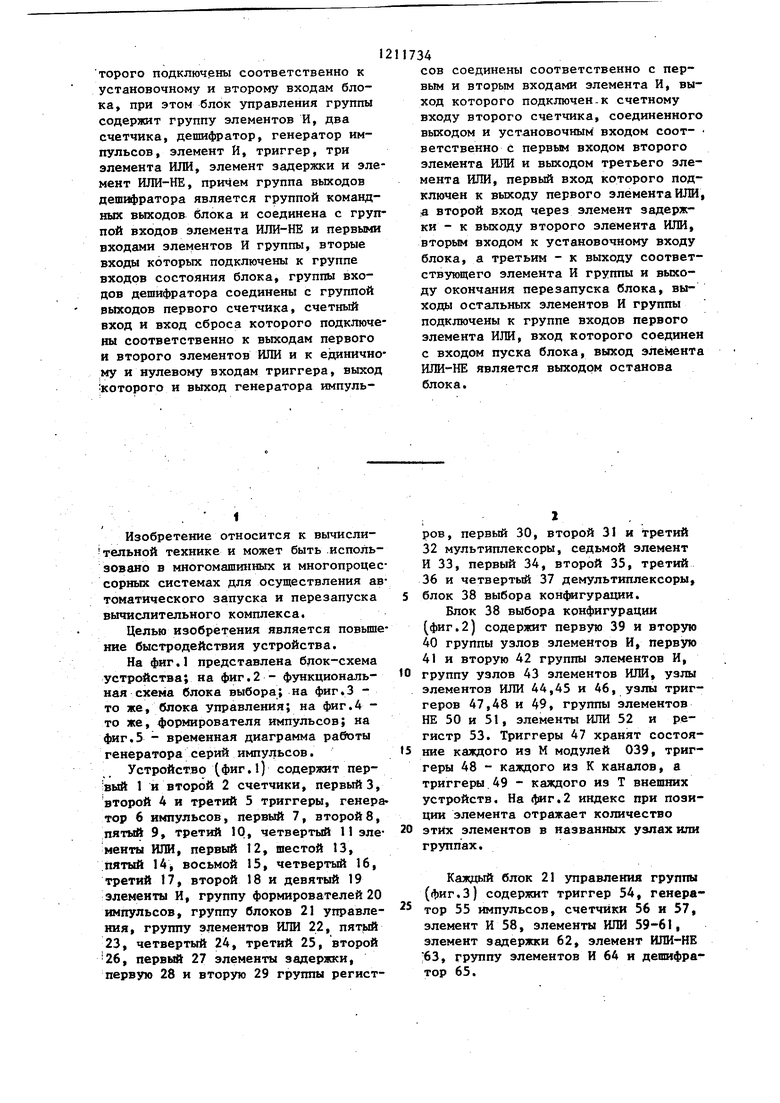

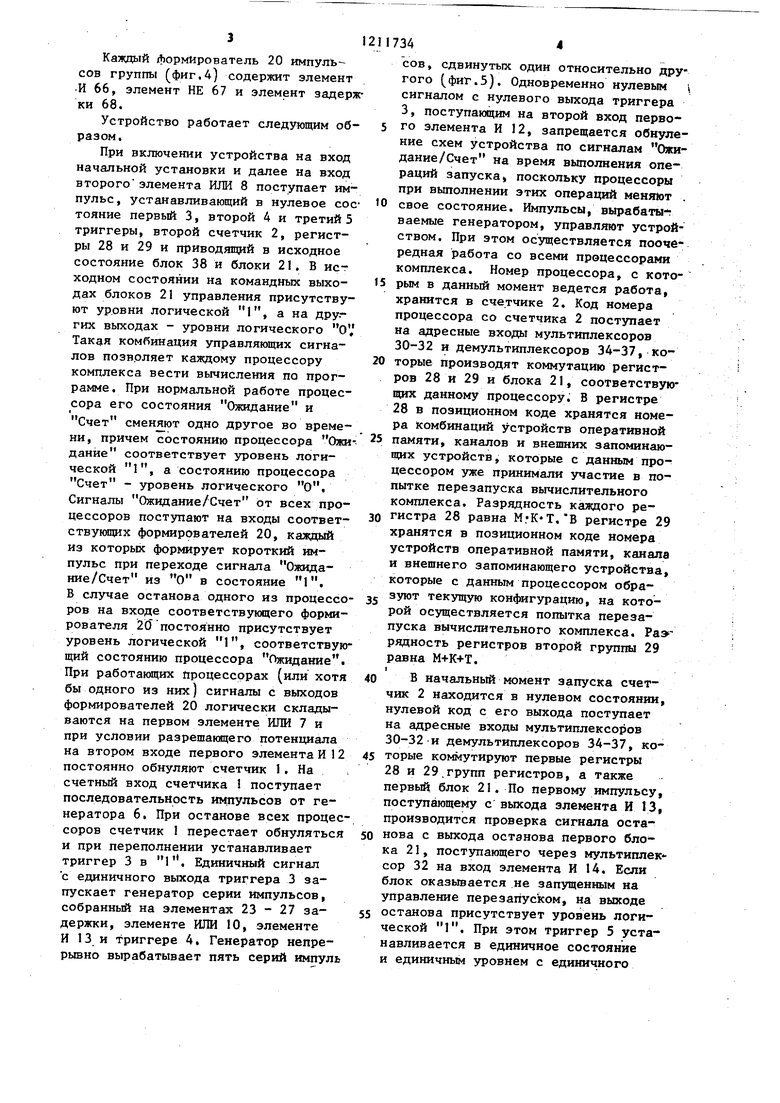

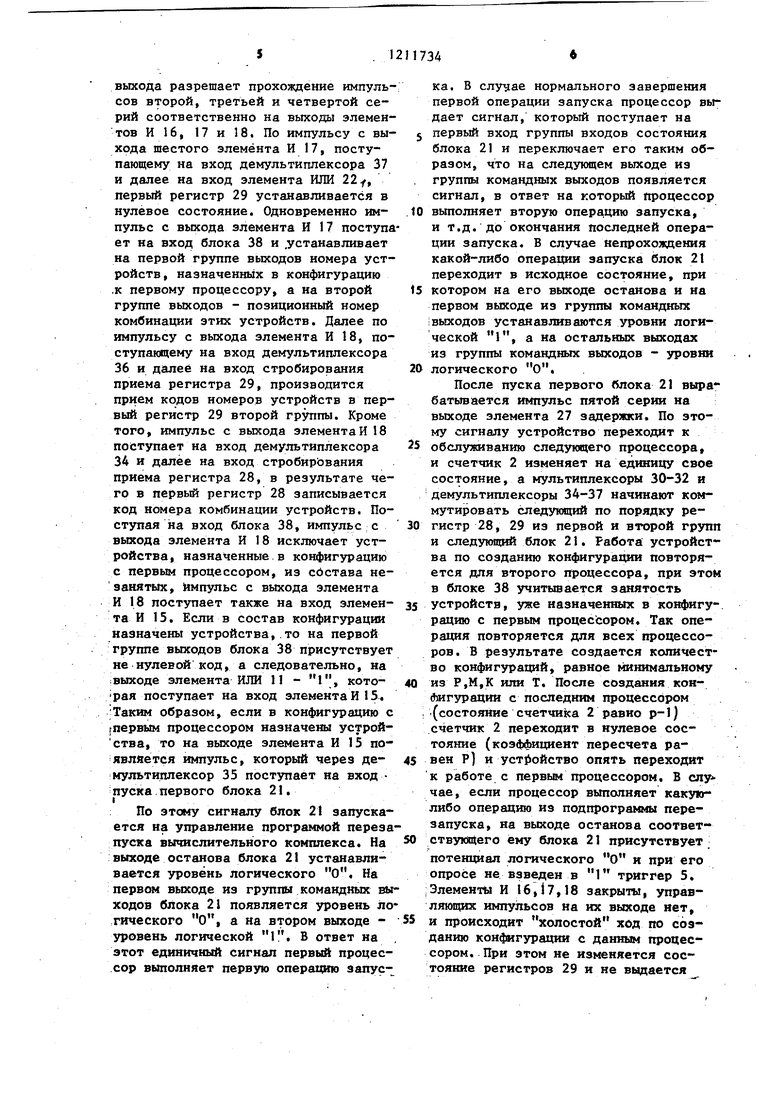

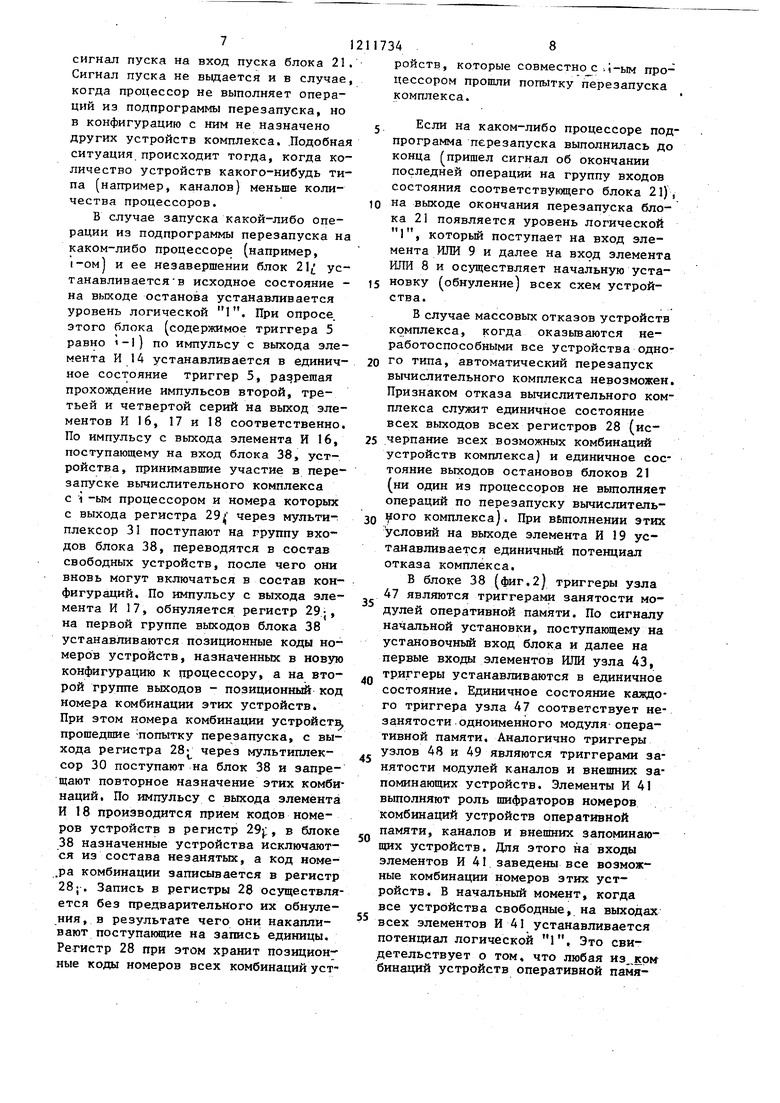

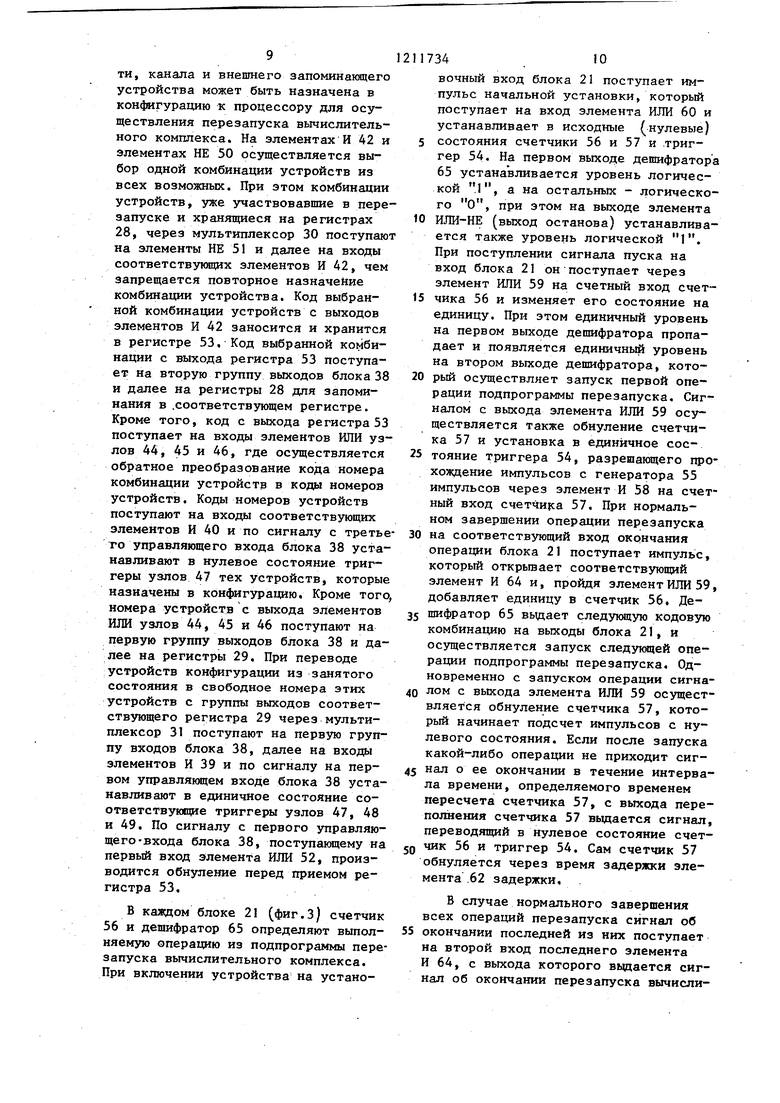

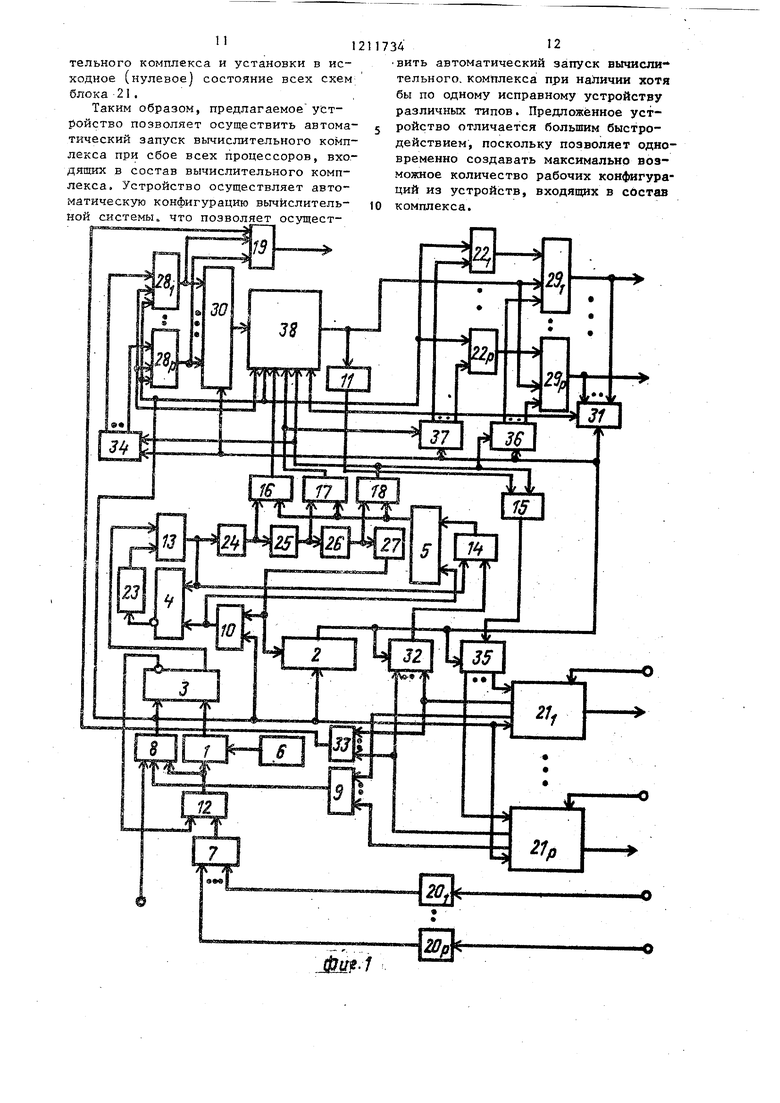

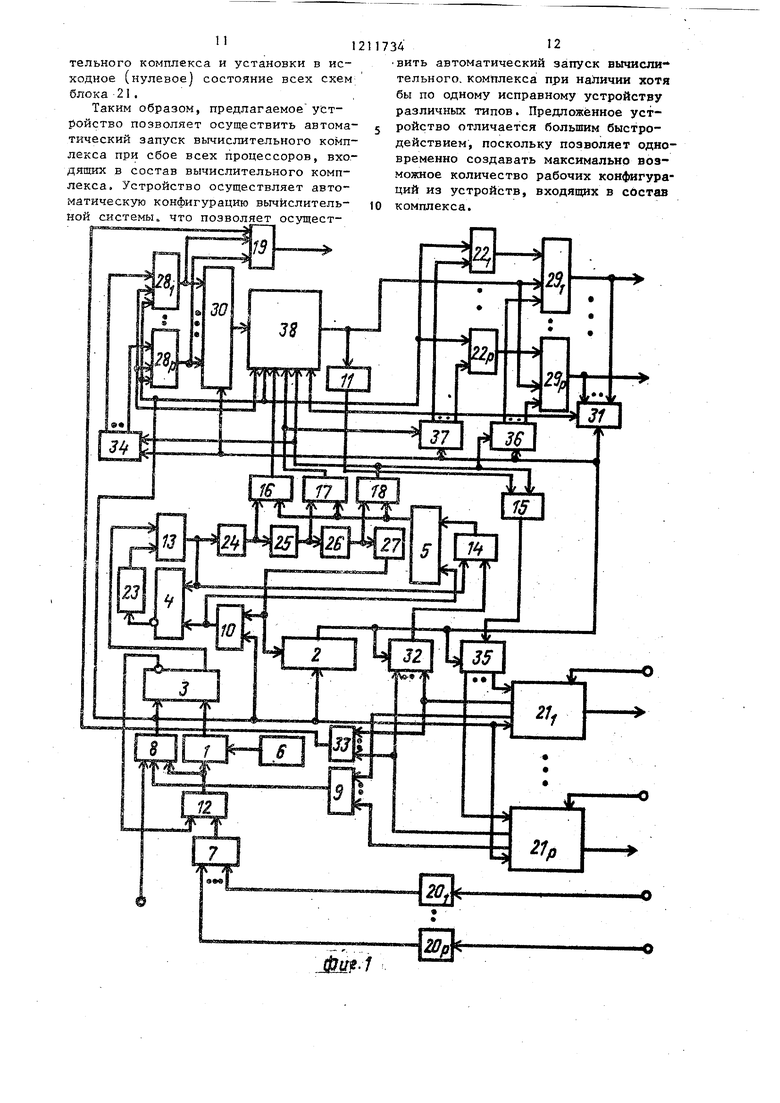

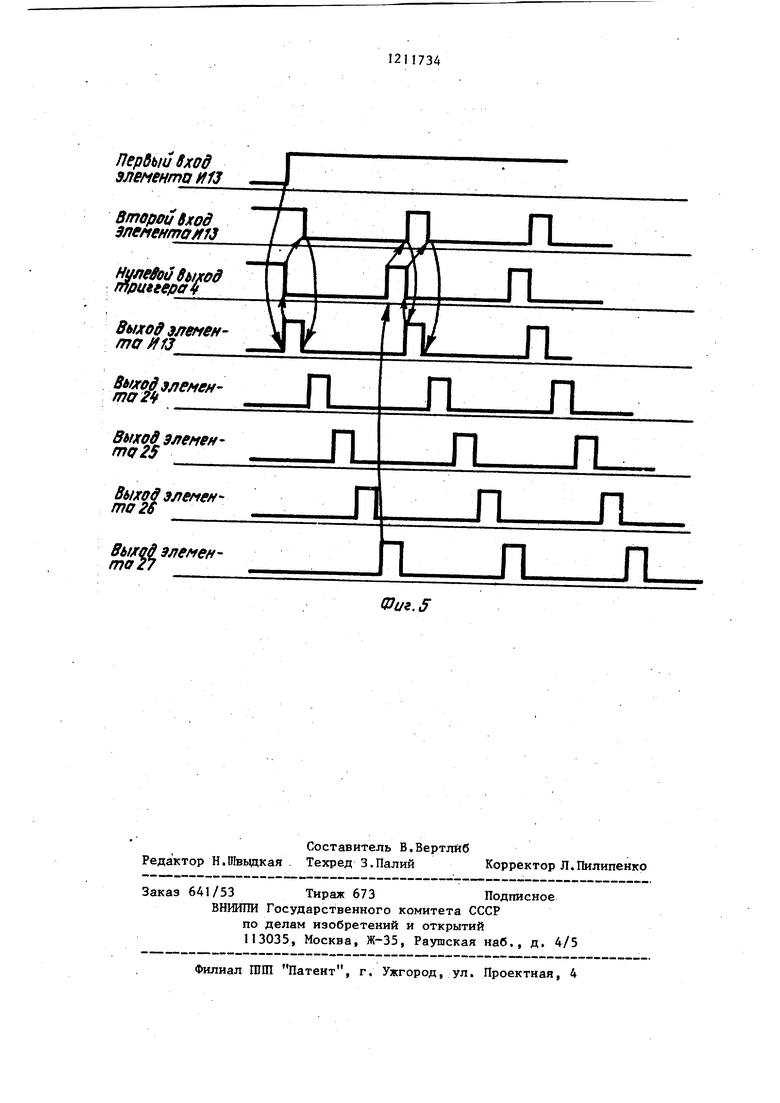

На фиг.1 представлена блок-схема устройства; на фиг.2 - функциональная схема блока выбора; на фиг.З - то же, блока управления; на фиг.4 - то же, формирователя импульсов; на фиг.5 - временная диаграмма работы генератора серий импульсов.

Устройство (фиг.1) содержит пер- :вый 1 и второй 2 счетчики, первый 3, второй 4 и третий 5 триггеры, генератор б импульсов, первый 7, второй8, пятый 9, третий 10, четвертый 11 элементы ИЛИ, первый 12, шестой 13, ;пятый 14 восьмой 15, четвертый 16, третий 17, второй 18 и девятый 19 элементы И, группу формирователей 20 импульсов, группу блоков 21 управления, группу элементов ШШ 22, пят|йй 23, четвертый 24, третий 25, второй 26, первый 27 элементы задержки, первую 28 и вторую 29 группы регист

1734

сов соединены соответственно с первым и вторым входами элемента И, выход которого подключен-К счетному входу второго счетчика, соединенного

выходом и установочным входом COOT-

ветственно с первым входом второго элемента ИЛИ и выходом третьего элемента ИЛИ, первый вход которого подключен к выходу первого элемента ИЛИ, д второй вход через элемент задержки - к выходу второго элемента ИЛИ, вторым входом к установочному входу блока, а третьим - к выходу соответствующего элемента И группы и выхо ду окончания перезапуска блока, выходы остальных элементов И группы подключены к группе входов первого элемента ИЛИ, вход которого соединен с входом пуска блока, выход элемента ИЛИ-НЕ является выходом останова блока.

ров, первый 30, второй 31 и третий 32 мультиплексоры, седьмой элемент И 33, первый 34, второй 35, третий 36 и четвертый 37 демультиплексоры, блок 38 выбора кон гурадии.

Блок 38 выбора конфигурации (фиг.2) содержит первую 39 и вторую

40группы узлов элементов И, первую

41и вторую 42 группы элементов И, группу узлов 43 элементов ИЛИ, узлы

элементов ИЛИ 44,45 и 46, узлы триггеров 47,48 и 49, группы элементов НЕ 50 и 51, элементы ИЛИ 52 и регистр 53. Триггеры 47 хранят состояние каждого из М модулей 039, триггеры 48 - каждого из К каналов, а триггеры 49 - каждого из Т внешних устройств. На фиг.2 индекс при позиции элемента отражает количество

этих элементов в названных узлах или группах.

Каждый блок 21 управления группы (фиг.З) содержит триггер 54, генера- тор 55 импульсов, счетчики 56 и 57, элемент И 58, элементы ИЛИ 59-61, элемент задержки 62, элемент НЛИ-НЕ 63, группу элементов И 64 и дешифратор 65.

OV

Казадый формирователь 20 импульсов группы (фиг.4) содержит элемент И 66, элемеит НЕ 67 и элемент задержки 68.

Устройство работает следующим образом.

При включении устройства на вход начальной установки и далее на вход второго элемента ИЛИ 8 поступает импульс, устанавливающий в нулевое состояние первый 3, второй 4 и третий 5 триггеры, второй счетчик 2, регистры 28 и 29 и приводяпщй в исходное состояние блок 38 и блоки 21. В ист ходном состоянии на командных выходах блоков 21 управления присутствуют уровни логической 1, а на других выходах - уровни логического Такая комбинация управляющих сигналов позволяет каждому процессору комплекса вести вычисления по программе. При нормальной работе процессора его состояния Ожидание и Счет сменяют одно другое во времени, причем состоянию процессора Ожидание соответствует уровень логической 1, а состоянию процессора Счет - уровень логического О, Сигналы Ожидание/Счет от всех процессоров поступают на входы соответствующих формирователей 20, каждый из которых формирует короткий импульс при переходе сигнала Ожидание/Счет из О в состояние 1. В случае останова одного из процессоров на входе соответствующего формирователя 2() постоянно присутствует уровень логической 1, соответствующий состоянию процессора Ожидание. При работающих процессорах (или хотя бы одного из них) сигналы с выходов формирователей 20 логически складываются на первом элементе ИЛИ 7 и при условии разрешакяцего потенциала на втором входе первого элемента И 12 постоянно обнуляют счетчик 1. На счетный вход счетчика 1 поступает последовательность импульсов от генератора 6, При останове всех процессоров счетчик I перестает обнуляться и при переполнении устанавливает триггер 3 в . Единичный сигнал с единичного выхода триггера 3 запускает генератор серии импульсов, собранный на элементах 23-27 задержки, элементе ИЛИ 10, элементе И 13 и триггере 4. Генератор непрерывно вьфабатывает пять серий импуль

сов, сдвинутых один относительно другого (фиг.5). Одновременно нулевым сигналом с нулевого выхода триггера 3, поступающим на второй вход первого элемента И 12, запрещается обнуление схем устройства по сигналам Ожидание/Счет на время выполнения операций запуска поскольку процессоры при выполнении этих операций меняют .

свое состояние. Импульсы, вырабаты- ваемые генератором, управляют устройством. При этом осуществляется поочередная работа со всеми процессорами комплекса. Номер процессора, с которым в данньй момент ведется работа, хранится в счетчике 2. Код номера процессора со счетчика 2 поступает на адресные входы мультиплексоров 30-32 и демультиплексоров 34-37, которые производят коммутацию регистров 28 и 29 и блока 21, соответствующих данному процессору. В регистре 28 в позиционном коде хранятся номера комбинаций устройств оперативной

памяти, каналов и внешних запоминающих устройств, которые с данным процессором принимали участие в попытке перезапуска вычислительного комплекса. Разрядность каждого регистра 28 равна М.-К Т. В регистре 29 хранятся в позиционном коде номера устройств оперативной памяти, канала и внешнего запоминающего устройства, которые с данным процессором обра

зуют текущую кон гурацию, на которой осуществляется попытка перезапуска вычислительного комплекса. Разрядность регистров второй группы 29 равна М+К+Т.

В начальный момент запуска счетчик 2 находится в нулевом состоянии, нулевой код с его выхода поступает на адресные входы мультиплексоров 30-32 и демультиплексоров 34-37, которые коммутируют первые регистры 28 и 29,групп регистров, а также первый блок 21. По первому импульсу, поступающему с выхода элемента И 13, производится проверка сигнала останова с выхода останова первого блока 21, поступающего через мультиплек - сор 32 на вход элемента И 14. Если блок оказывается не запущенным на управление перезапуском, на выходе

останова присутствует уровень логической 1. При этом триггер 5 устанавливается в единичное состояние и единичным уровнем с единичного

выхода разрешает прохождение импульсов второй, третьей и четвертой серий соответственно на выходы элементов И 16, 17 и 18. По импульсу с вы- хода шестого элемента И 17, поступающему на вход демультиплексора 37 и далее на вход элемента ИЛИ 22, первый регистр 29 устанавливается в нулевое состояние. Одновременно им- пульс с выхода элемента И 17 поступает на вход блока 38 и .устанавливает на первой группе выходов номера устройств, назначенных в конфигурацию ,к первому процессору, а на второй группе выходов - позиционный номер комбинации этих устройств. Далее по импульсу с выхода элемента И 18, поступающему на вход демультиплексора 36 и далее на вход стробирования приема регистра 29, производится прием кодов номеров устройств в первый регистр 29 второй группы. Кроме того, импульс с выхода элемента И 18 поступает на вход демультиплексора 34 и далее на вход стробирЬвания приема регистра 28, в результате чего в первый регистр 28 записывается код номера комбинации устройств. Поступая на вход блока 38, импульс с выхода элемента И 18 исключает устройства, назначенные в конфигурацию с первым процессором, из сбстава незанятых, импульс с выхода элемента И 18 поступает также на вход элемен- та И 15. Если в состав конфигурации назначены устройства,.то на первой группе выходов блока 38 присутствует не нулевой код, а следовательно, на выходе элемента ИЛИ 11 - 1, кото- рая поступает на вход элемента И 15. Таким образом, если в конфигурацию с гпервым процессором назначены устрой- ства, то на выходе элемента И 15 появляется импульс, который через де- мультиплексор 35 поступает на вход пуска первого блока 21.

: По этому сигналу блок 21 запускается на управление программой перезапуска вычислительного комплекса. На выходе останова блока 21 устанавливается уровень логического О. На первом выходе из группы командных вы ходов блока 21 появляется уровень ло гического О, а на втором выхода - уровень логической 1. В ответ на этот единичный сигнал первый процессор выполняет первую операщпо запуска. В случае нормального завершения первой операции запуска процессор вы дает сигнал, который поступает на первый вход группы входов состояния блока 21 и переключает его таким образом, что на следующем выходе из группы командных выходов появляется сигнал, в ответ на который гфоцессор выполняет вторую операцию запуска, и т.д. до окончания последней операции запуска. В случае непрохождения какой-либо операции запуска блок 21 переходит в исходное состояние, при котором на его выходе останова и на первом выходе из группы командных :выходов устанавливаются уровни логической 1, а на остальных выходах из группы командных выходов - уровни логического О.

После пуска первого блока 21 вырабатывается импульс пятой серии на выходе элемента 27 задержки. По этому сигналу устройство переходит к обслуживанию следующего процессора, и счетчик 2 изменяет на единицу свое состояние, а мультиплексоры 30-32 и демультиплексоры 34-37 начинают коммутировать следующий по порядку регистр 28, 29 из первой и второй групп и следующий блок 21. Работа устройства по созданию конфигурации повторяется для второго процессора, при этом в блоке 38 учитывается занятость устройств, уже назначенных в конфигу рацию с первым процессором. Так операция повторяется для всех процессоров. В результате создается количество конфигураций, равное Минимальному из Р,М,К или Т. После создания кон- (5мгурация с последним процессором .(состояние счетчика 2 равно р-1) счетчик 2 переходит в кулевое состояние (коэффициент пересчета равен Р и уст14ойство опять переходит к работе с первым процессором. В слу чае, если процессор выполняет какую- либо операцию из подпрограммы перезапуска, на выходе останова соответ- ствукя его ему блока 21 присутствует потенциал логического О и при его опросе не взведен в 1 триггер 5. Элементы И 16,17,18 закрыты, управляющих импульсов на их выходе нет, и происходит холостой ход по созданию конфигурации с данным процессором. При этом не изменяется состояние регистров 29 и не выдается

71

сигнал пуска на вход пуска блока 21, Сигнал пуска не выдается и в случае, когда процессор не выполняет операций из подпрограммы перезапуска, но в конфигурацию с ним не назначено других устройств комплекса. .Подобная ситуация происходит тогда, когда количество устройств какого-нибудь типа (например, каналов) меньше количества процессоров.

В случае запуска какой-либо операции из подпрограммы перезапуска на каком-либо процессоре (например, 1-ом и ее незавершении блок 21 устанавливается в исходное состояние - на выходе останова устанавливается уровень логической 1. При опросе, этого блока (содержимое триггера 5 равно -) по импульсу с выхода элемента И 14 устанавливается в единичное состояние триггер 5, разрешая прохождение импульсов второй, третьей и четвертой серий на выход элементов И 16, 17 и 18 соответственно. По импульсу с выхода элемента И 16, поступающему на вход блока 38, устройства, принимавшие участие в перезапуске вычислительного комплекса с i-ым процессором и номера которых с выхода регистра 29 через мульти- плексор 31 поступают на группу входов блока 38, переводятся в состав свободных устройств, после чего они вновь могут включаться в состав кон- фигурации. По импульсу с выхода элемента И 17, обнуляется регистр 29j, на первой группе выходов блока 38 устанавливаются позиционные коды номеров устройств, назначенных в новую конфигурацию к процессору, а на второй группе выходов - позиционный код номера комбинации этих устройств. При этом номера комбинации устройств, прошедшие -попытку перезапуска, с выхода регистра 28j через мультиплексор 30 поступают на блок 38 и запрещают повторное назначение этих комбинаций. По импульсу с выхода элемента И 18 производится прием кодов номеров устройств в регистр 29j:, в блоке 38 назначенные устройства исключаются из состава незанятых, а код номе- .ра комбинации записывается в регистр 28;, Запись в регистры 28 осуществляется без предварительного их обнуления , в результате чего они накапливают поступающие на запись единицы. Регистр 28 при этом хранит позицион;- ные коды номеров всех комбинаций уст17348

ройств, которые совместно с .i-ым процессором прошли попытку перезапуска комплекса,

5 Если на каком-либо процессоре подпрограмма перезапуска выполнилась до конца (пришел сигнал об окончании последней операции на группу входов состояния соответствующего блока 21) ,

10 на выходе окончания перезапуска блока 21 появляется уровень логической 1, который поступает на вход элемента ИЛИ 9 и далее на вход элемента ИЛИ 8 и осуществляет начальную уста15 новку (обнуление) всех схем устройства,

В случае массовых отказов устройств комплекса, когда оказьгоаются неработоспособными все устройства одно20 го типа, автоматический перезапуск вычислительного комплекса невозможен. Признаком отказа вычислительного комплекса служит единичное состояние всех выходов всех регистров 28 (ис5 черпание всех возможных комбинаций устройств комготекса) и единичное состояние выходов остановов блоков 21 (ни один из процессоров не выполняет операций по перезапуску вьтислительQ комплекса). При выполнении этих условий на выходе элемента И 19 устанавливается единичный потенциал отказа комплекса,

В блоке 38 (фиг.2) триггеры узла 47 являются триггерами занятости модулей оперативной памяти. По сигналу начальной установки, поступающему на установочный вход блока и далее на первые входы элементов ИЛИ узла 43, триггеры устанавливаются в единичное состояние. Единичное состояние каждого триггера узла 47 соответствует незанятости одноименного модуля оперативной памяти. Аналогично триггеры узлов 48 и 49 являются триггерами занятости модулей каналов и внешних запоминающих устройств. Элементы И 41 вьтолняют роль шифраторов номеров комбинаций устройств оперативной памяти, каналов и внешних запоминающих устройств. Для этого на входы элементов И 41 заведены все возможные комбинации номеров этих устройств, В начальный момент, когда все устройства свободные, на выходах

всех элементов И 41 устанавливается потенциал логической 1, Это свидетельствует о том, что любая бинаций устройств оперативной памя0

5

0

9

ти, канала и внешнего запоминающего устройства может быть назначена в конфигурацию к процессору для осуществления перезапуска вычислительного комплекса. На элементах И 42 и элементах НЕ 50 осуществляется выбор одной комбинации устройств из всех возможных. При этом комбинации устройств, уже участвовавшие в перезапуске и хранящиеся на регистрах 28, через мультиплексор 30 поступают на элементы НЕ 51 и далее на входы соответствующих элементов И 42, чем запрещается повторное назначение комбинации устройства. Код выбранной комбинации устройств с выходов элементов И 42 заносится и хранится в регистре 53. Код выбранной комбинации с выхода регистра 53 поступает на вторую группу выходов блока 38 и далее на регистры 28 для запоминания в .соответствующем регистре. Кроме того, код с выхода регистра 53 поступает на входы элементов ИЛИ узлов 44, 45 и 46, где осуществляется обратное преобразование кода номера комбинации устройств в коды номеров устройств. Коды номеров устройств поступают на входы соответствующих элементов И 40 и по сигналу с третье то управляющего входа блока 38 устанавливают в нулевое состояние триггеры узлов 47 тех устройств, которые назначены в конфигурацию. Кроме того номера устройств с выхода элементов ИЛИ узлов 44, 45 и 46 поступают на первую группу выходов блока 38 и далее на регистры 29. При переводе устройств конфигурации из занятого состояния в свободное номера этих устройств с группы выходов соответствующего регистра 29 через мультиплексор 31 поступают на первую группу входов блока 38, далее на входы элементов И 39 и по сигналу на первом управляющем входе блока 38 устанавливают в единичное состояние соответствующие триггеры узлов 47, 48 и 49. По сигналу с первого управляющего-входа блока 38, поступающему на первый вход элемента ИЛИ 52, производится обнуление перед приемом регистра 53.

В каждом блоке 21 (фиг.З) счетчик 56 и дешифратор 65 определяют выполняемую операцию из подпрограммы перезапуска вычислительного комплекса. При включении устройства на устано11734 . 10

вочный вход блока 21 поступает импульс начальной установки, который поступает на вход элемента ИЛИ 60 и устанавливает в исходные (нулевые) 5 состояния счетчики 56 и 57 и .триггер 54. На первом выходе дешифратора 65 устана вливается уровень логической 1, а на остальных - логического О, при этом на выходе элемента

10 ИЛИ-НЕ (выход останова) устанавливается также уровень логической 1. При поступлении сигнала пуска на вход блока 21 он поступает через элемент ИЛИ 59 на счетный вход счет15 чика 56 и изменяет его состояние на единицу. При этом единичный уровень на первом выходе дешифратора пропадает и появляется единичный уровень на втором выходе дешифратора, кото20 рый осзтцествляет запуск первой операции подпрограммы перезапуска. Сигналом с выхода элемента ИЛИ 59 осуществляется также обнуление счетчика 57 и установка в единичное сос25 тояние триггера 54, разрешающего прохождение импульсов с генератора 55 импульсов через элемент И 58 на счетный вход счетчика 57. При нормальном завершении операции перезапуска

30 на соответствующий вход окончания операции блока 21 поступает импульс, который открьшает соответствующий элемент И 64 и, пройдя элемент ИЛИ 59, добавляет единицу в счетчик 56. Де35 шифратор 65 вьщает следующую кодовую комбинацию на выходы блока 21, и ос1га1ествляется запуск следукяцей операции подпрограммы перезапуска. Одновременно с запуском операции сигна40 лом с выхода элемента ИЛИ 59 осуществляется обнуление счетчика 57, который начинает подсчет импульсов с нулевого состояния. Если после запуска какой-либо операции не приходит сиг45 нал о ее окончании в течение интервала времени, определяемого временем пересчета счетчика 57, с выхода переполнения счетчика 57 вьщается сигнал, переводящий в нулевое состояние счетчик 56 и триггер 54. Сам счетчик 57 обнуляется через время задержки элемента .62 задержки.

В случае нормального завершения всех операций перезапуска сигнал об 55 окончании последней из них поступает на второй вход последнего элемента И 64, с выхода которого выдается сигнал об окончании перезапуска вычисли50

тельного комплекса и установки в исходное (нулевое состояние всех схем

блока -21.

Таким образом, предлагаемое устройство позволяет осуществить автоматический запуск вычислительного комплекса при сбое всех процессоров, входящих в состав вычислительного комплекса. Устройство осуществляет автоматическую конфигурацию вычислительной системы, что позволяет осущест©

.Mf-1

вить автоматический запуск вычисли тельного, комплекса при наличии хотя бы по одному исправному устройству различных типов. Предложенное устройство отличается большим быстродействием, поскольку позволяет одновременно создавать максимально возможное количество рабочих конфигураций из устройств, входящих в состав комплекса.

О

ф jt ф

II 1 1 I ™ Т fЯШ 111Я1 ™ - 1-

.. П t рг 7

I I ««/ II « I-I «5.; II W, |..| tfr I

f±za

т

QzD

//уг.7-л1 w/rr I

±

I

±г

I Г

фиеЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для перезапуска вычислительного комплекса при обнаружении сбоя | 1988 |

|

SU1541608A1 |

| Устройство для перезапуска вычислительного комплекса при обнаружении сбоя | 1988 |

|

SU1594543A1 |

| Устройство управления | 1989 |

|

SU1654820A1 |

| Цифровой оптический уровнемер | 1988 |

|

SU1624262A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1441399A1 |

| Устройство для обмена данными в распределенной вычислительной системе | 1988 |

|

SU1580382A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1282121A1 |

| Параллельный логический мультиконтроллер | 2016 |

|

RU2634199C1 |

| Устройство для арбитража запросов | 1988 |

|

SU1596329A1 |

fpus.

| Устройство для блокировки и перезапускаВычиСлиТЕльНОй СиСТЕМы пРи СбОяХ пиТАНия | 1978 |

|

SU824214A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для перезапуска вычислительного комплекса при обнаружении сбоя | 1980 |

|

SU962956A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-02-15—Публикация

1984-07-09—Подача