Изобретение относится к запоминающим устройствам.

Извес-тно устройство для извлечения многозначного ответа из ассоциативного накопителя, в котором слова, образующие многозначный ответ, считываются в порядке возрастания (убывания) номера ячейки ассоциативного запоминающего устройства, определяемом цепью очередности .

Недостатком этого устройства является низкое быстродействие.

Наиболее близким техническим решением к изобретению является устройство для извлечения многозначного ответа из ассоциативного накопителя, содержащее входные, выходные и дополнительные МДП-транзисторы и блок выработки признака ответа на МДП-.транзисторах, причем истоки входных транзисторов, стоки выходных транзисторов, затворы дополнительных транзисторов и входы блока выработки признака ответа соединены с соответствующими словарными линиями, затворы выходных транзисторов и стоки дополнительных транзисторов подключены к соответствующим адресным линиям, а истоки дополнительных транзисторов соединены с одноименными адресными

линиями опроса, истоки выходных транзисторов подключены к линии нулевого потенциала f2j.

Недостатком известного устройства является огра.ичение области его применения вследствие отсутствия возможности коммутации ассоциативных накопителей фиксированной емкости с целью создания блочной структуры ас10социативных накопителей большой емкости.

Цель изобретения - расширение области применения устройства за счет обеспечения возможности коммутации 5 ассоциативных накопителей фиксированной емкости.

Поставленная цель достигается тем, что л устройство для извлечения многозначного ответа из ассоциативно20го накопителя, содержащее входные, выходные, адресные и информационные МДП-транзисторы, причем истоки первого и второго адресных транзисторов объединены и являются первым адресг

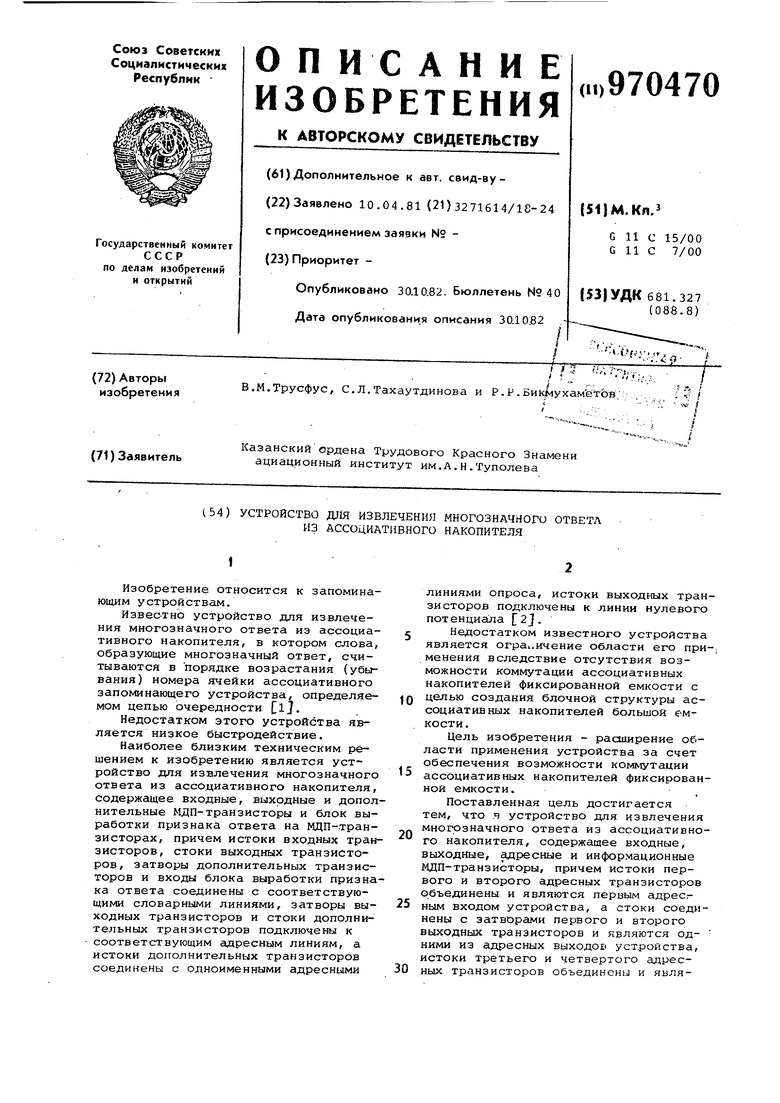

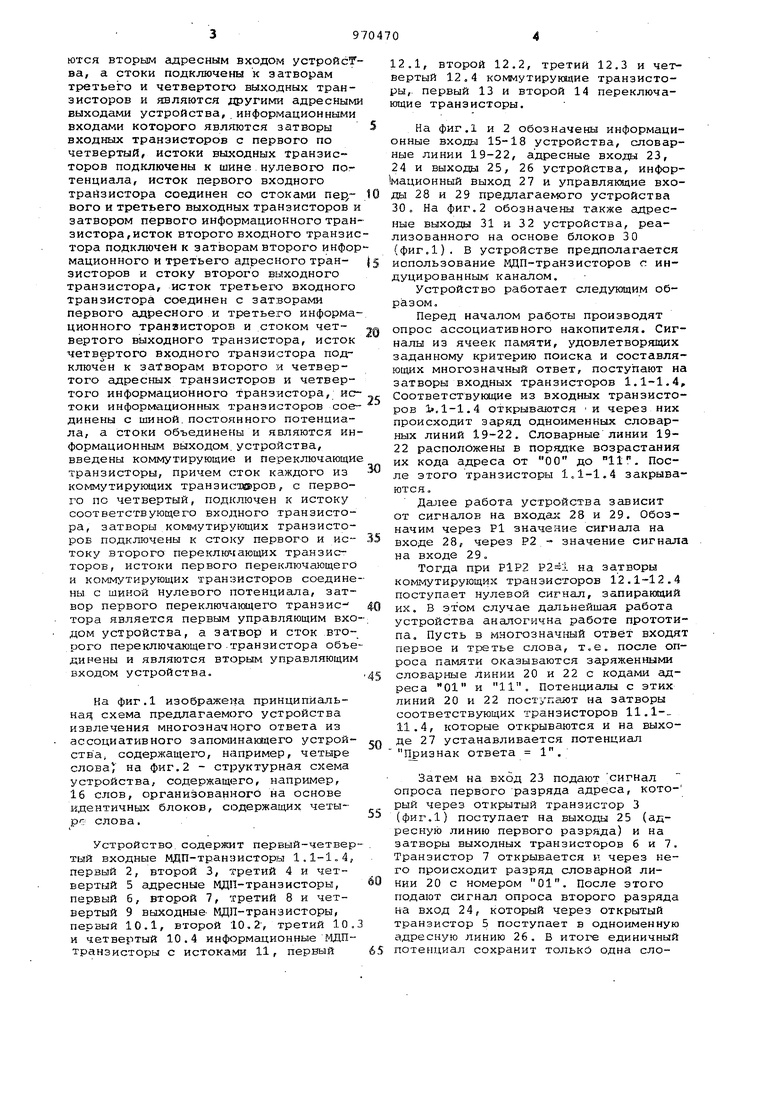

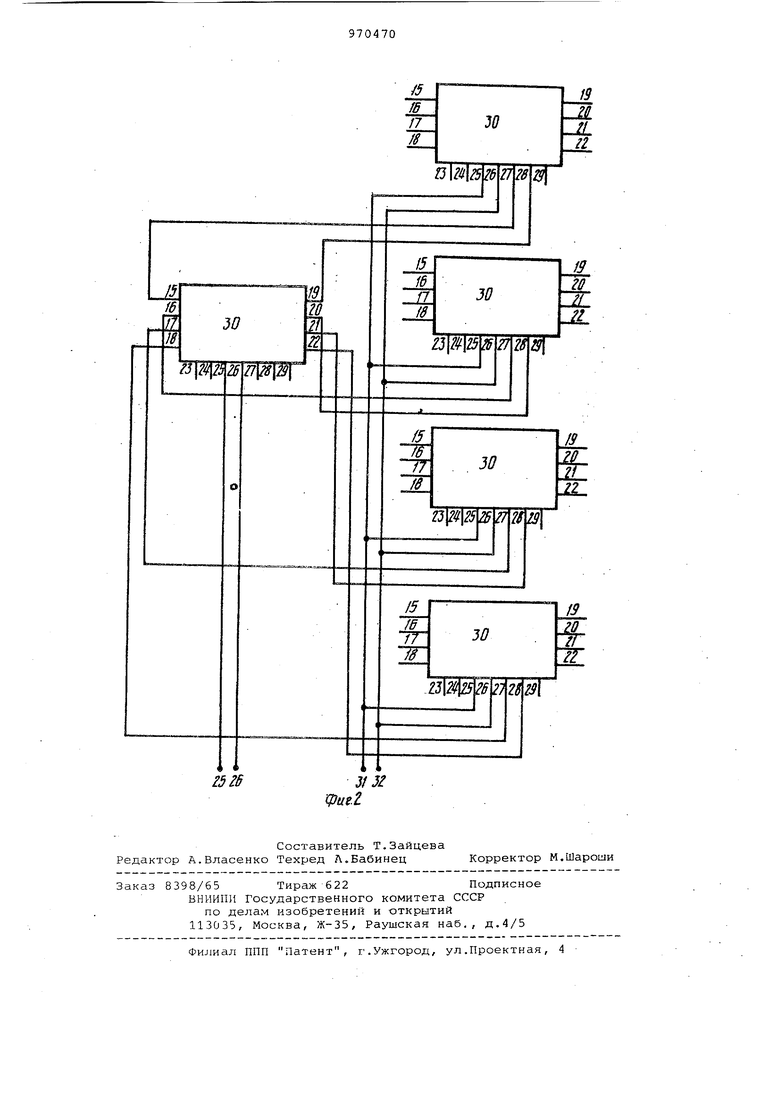

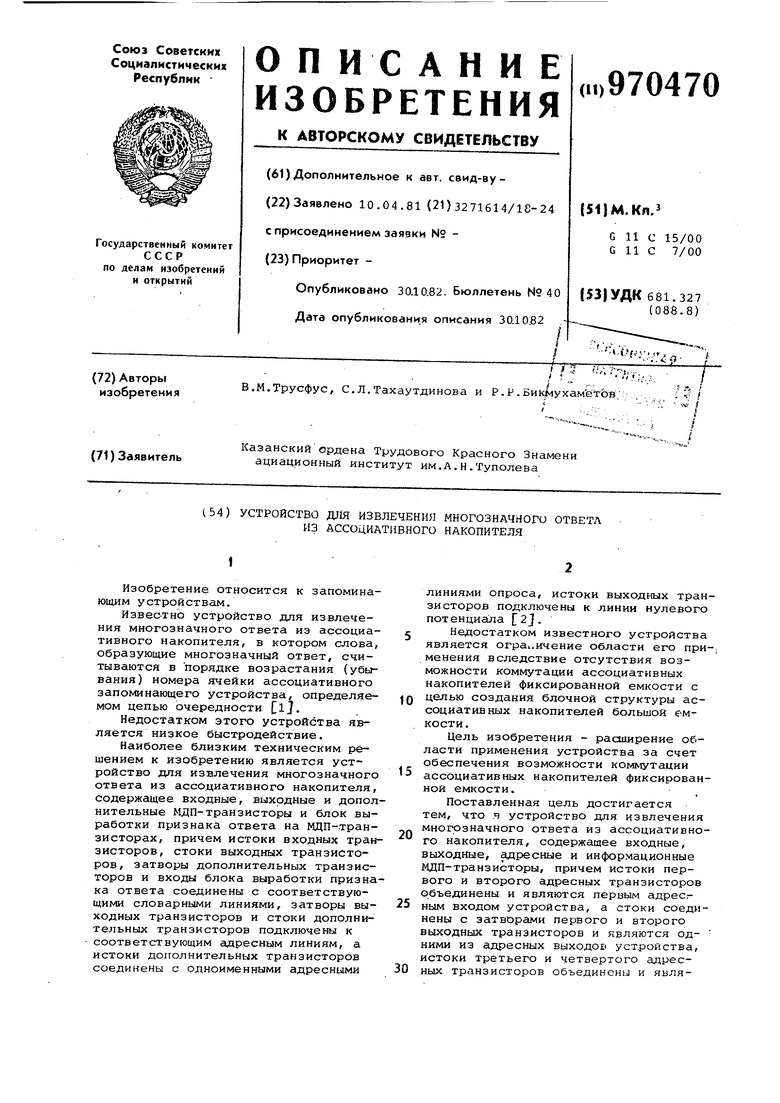

25 ным входом устройства, а стоки соединены с затворами первого и второго выходных транзисторов и являются одними из адресных выходов устройства, истоки третьего и четвертого адрес30ных транзисторов объединены и являются вторым адресным входом устройст ва, а стоки подключены к затворам третьего и четвертого выходных транзисторов и являются другими адресным выходами устройства,.информационными входами которого являются затворы входных транзисторов с первого по четвертый, истоки выходных транзисторов подключены к шине нулевого потенциала, исток первого входного трайзистора соединен со стоками nepjвого и третьего выходных транзисторов и затвором первого информационного тран зистора,исток второго входного транзи тора подключен к затворам второго инфор мационного и третьего адресного транзисторов и стоку второго выходного транзистора, исток третьего входного транзистора соединен с затворами первого адресного и третьего информа ционного транзисторов и стоком четвертого выходного транзистора, исток четвертого входного транзистора подключен к затворам второго и четвертого адресных транзисторов и четвертого информационного транзистора, ист токи информационных транзисторов сое динены с шиной.постоянного потенциала, а стоки объединены и являются ин формационным выходом. устро.йства, введены коммутирующие и пе.реключающи транзисторы, причем сток каждого из коммутирующих транзистввров, с первого по четвертый, подключен к истоку соответствующего входдного транзистора, затворы коммутирующих транзисторов подключены к стоку первого и истоку второго переключающих транзисторов, истоки первого переключающего и коммутирующих транзисторов соедине ны с шиной Нулевого потенциала, затвор первого переключаквдего транзис- тора является первым управляющим вхо дом устройства, а затвор и сток второго переключающего.транзистора объе динены и являются вторым управляющим входом устройства. На фиг.1 изображена принципйальная( схема предлагаемого устройства извлечения многозначного ответа из ассоциативного запоминающего устройства, содержащего, например, четыре слова) на фиг. 2 - структурная схема устройства, содержащего, например, 16 слов, организованного на основе идентичных блоков, содержащих четыре слова. Устройство, содержит первый-четвер тый входные МДП-транзисторы 1.1-1.4, первый 2, второй 3, третий 4 и четвертый 5 адресные МДП-транзисторы, первый 6, второй 7, третий 8 и четвертый 9 выходные- МДП-транзисторы, первый 10.1, второй 10.2, третий 10. и четвертый 10.4 информационные МДПтранзисторы с истоками 11, первый 12.1, второй 12.2, третий12.3 и четвертый 12.4 коммутируквдиетранзисторы, первый 13 и второй 14переключающие транзисторы. На фиг.1 и 2 обозначены информационные входы 15-18 устройства, словарные линии 19-22, адресные входы 23, 24 и выходы 25, 26 устройства, информаиионный выход 27 и управлякнцие входы 28 и 29 предлагаемого устройства 30. На фиг.2 обозначены также адресные выходы 31 и 32 устройства, реализованного на основе блоков 30 {фиг.1). в устройстве предполагается использование ВДП-транзисторов с индуцированным каналом. Устройство работает следующим образом. Перед началом работы производят опрос ассоциативного накопителя. Сигналы из ячеек памяти, удовлетворящих заданному критерию поиска и составляющих многозначный ответ, поступают на затворы входных транзисторов 1.1-1.4, Соответствукадие из входных транзисторов 1«.1-1.4 открываются И через них происходит заряд одноименных словарных линий 19-22. Словарные линии 1922 расположены в поряд-ке возрастания их кода адреса от 00 до 11. После этого транзисторы 1.1-1.4 закрываются. Далее работа устройства зависит от сигналов на входах 28 и 29. Обозначим через Р1 значение сигнала на входе 28, через Р2 - значение сигнала на входе 29. Тогда при Р1Р2 на затворы коммутирующих транзисторов 12.1-12.4 поступает нулевой сигнал, запираияций их. В этом случае дальнейшая работа устройства аналогична работе прототипа. Пусть в многозначный ответ входят первое и третье слова, т.е. после опроса памяти оказываются заряженными словарные линии 20 и 22 с кодами адреса 01 и 11. Потенциалы с этих линий 20 и 22 поступают на затворы соответствующих транзисторов 11.1-11.4, которые открываются и на выходе 27 устанавливается потенциал Признак ответа 1. Затем на вход 23 подают сигнал опроса первого разряда адреса, который через открытый транзистор 3 (фиг.1) поступает на выходы 25 (адресную линию первого разряда) и на затворы выходных транзисторов 6 и 7. Транзистор 7 открывается и через него происходит разряд словарной линии 20 с номером 01. После этого подают сигнал опроса второго разряда на вход 24, который через открытый транзистор 5 поступает в одноименную адресную линию 26. В итоге единичный потенциал сохранит толькй одна еловарная линия 22, соответствующая третьему слову, а на исходах 25 и 26 будет.сформирован код ее адреса 11 Аналогично будет сформирован код адреса следующего первого слова, входящего в многозначный ответ, если исключить из рассмотрения третье сло во. При наличии на входах 28 и 29 ком бинации сигналов Р1Р2 1 на затвор транзисторов 12.1-12.4 поступает единичный отпирающий сигнал и через них происходит разряд соответствующих заряженных словарных линия 19-22. На выходе 27 устанавливается потенциал Признак ответа - О, а на выходах 25 к 26 - код адреса 00, которые сохранятся и при дальнейшем опросе устройства. Таким образом, наличие на входах 28 и 29 комбинации сигналов PlP2 1 блокирует работу устройства Устройство извлечения многозначного ответа из ассоциативного накопителя, содержащего, например, шестнадцат слов, реализованное на основе блоков 30, выполнено в виде двух ступеней. Первая ступень состоит из одного блош ка 30 иобе9печивает формирование старших разрядов адреса. Вторая ступень включает в себя четыре блока 30 и формирует младшие разряды адреса. , Технико-экономическое преимущество предлагаемого устройства заключается в более широкой области его применения по сравнению с прототипом за счет возможности создания устройств блочной структуры. Формула изобретения Устройство для извлечения многозначного ответа из ассоциативного на копителя, содержащее входные, выходные, адресные и информационные МДПтранзисторы, причем истоки первого и второго адресных транзисторов объединены и являются первым адресным входом устройства, а стоки соединены с затворами первого и второго выходных транзисторов и являются одними из адресных выходов устройства, истоки третьего и четвертого адресных транзисторов объединены и являются вторым адресным входом устройства, а стоки подключены к затворам третьего и четвертого выходных транзисторов и являются другими адресными выходами устройства, информационными входами которого являются затворы входных транзисторов с первого по четвертый, истоки выходных транзисторов подключены к шине нулевого потенциала, исток первого входного транзистора соединен со стоками первого и третьего выходных транзисторов и эатиором первого информационного транзистора, исток второго входного транзистора подключен к затворам второго информационного и третьего адресного транзисторов и стоку второго выходного транзистора, исток третьего входного транзистора соединен с затворами первого адресного и третьего информационного транзисторов и стоком четвертого выходного транзистора, исток четвертого входного транзистора подключен к затворам второго и четвертого адресных транзисторов и четвертого информационного транзистора, истоки информационных транзисторов соединены с шиной постоянного потенциала, а стоки объедииены и являются информационным выходом устройства, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечения возможности коммутации ассоциативных накорчтелей фиксированной емкости, в него введены коммутирующие и переключающие транзисторы, причем сток каждого из коммутирукяцих транзисторов, с первого по четвертый, подключен к истоку соответствующего входного транзистора, затворы коммутирующих транзисторов подключены к стоку первого и истоку второго переключающих транзисторов, истоки первого переключающего и коммутирующих транзисторов соединены с шиной нулевого потенциала, затвор первого пере ключ аиоще го транзистора является первым управляющим входом устройства, а затвор и сток второго переключающего транзистора объединены и являются вторым управляющим входом устройства. Источники информации, Принятые во внимание при экспертизе 1.Крайзмер Л.П. Ассоциативные запоминающие устройства. Л., Энерг. гия, 1967, с.67-68. 2.Авторское свидетельство СССР № 497636, кл. G 11 С 15/00, 1975 (прототип).

Л LJi

C

J/7

12

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для считывания информации из ассоциативной памяти | 1981 |

|

SU955203A1 |

| Устройство для считывания информации из блоков памяти | 1977 |

|

SU746718A1 |

| Устройство для считывания информации из ассоциативного запоминающего блока | 1974 |

|

SU497636A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1978 |

|

SU769628A1 |

| Блок для обнаружения многозначного ответа в ассоциативном запомиющем устройстве | 1975 |

|

SU566269A1 |

| Формирователь записи-считывания для запоминающих устройств | 1978 |

|

SU765873A1 |

| Адресный формирователь | 1981 |

|

SU1007133A1 |

| Устройство для считывания информации из ассоциативной памяти | 1981 |

|

SU964734A1 |

| Запоминающее устройство | 1987 |

|

SU1465911A1 |

20

дО

«1

fЦ2

26

ПЩЩ

19

5

30

JL

2S

9

20

JL

M,

23Щ2т.

IL,

30

Ml

Авторы

Даты

1982-10-30—Публикация

1981-04-10—Подача