10

15

20

25

Изобретение относится к вычислительной технщсе .и может (Зыть использовано для сопряжения вычислительных устройств с разным быстродействием.

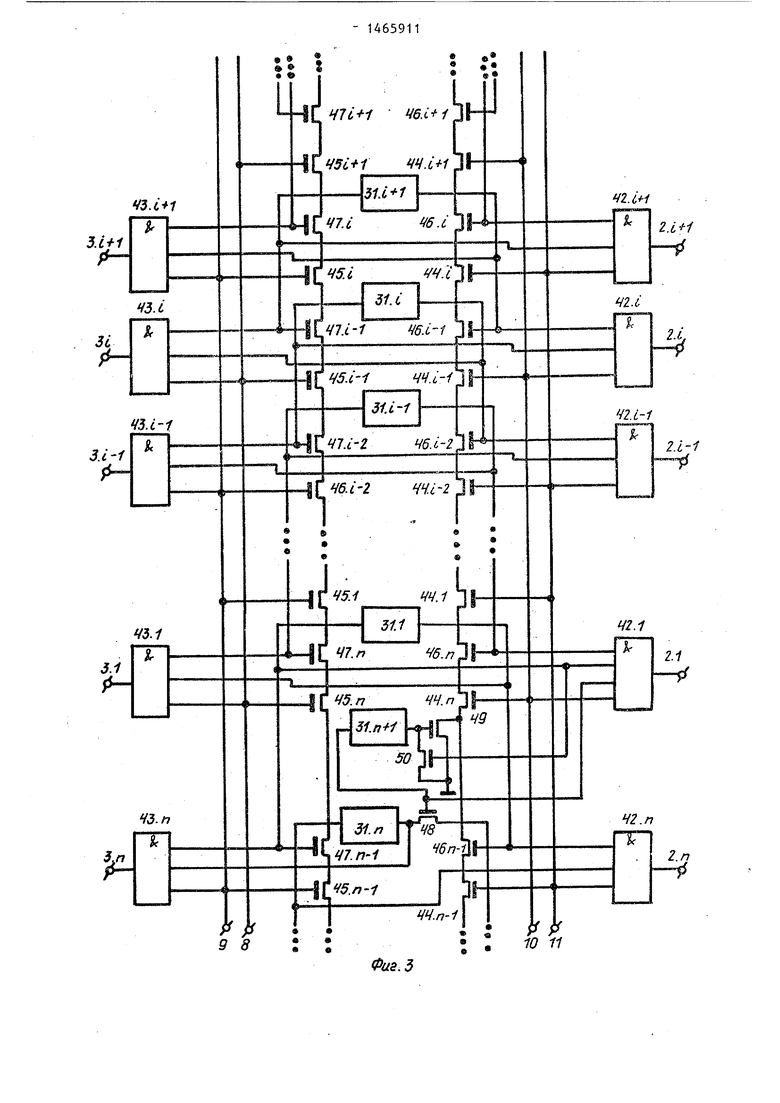

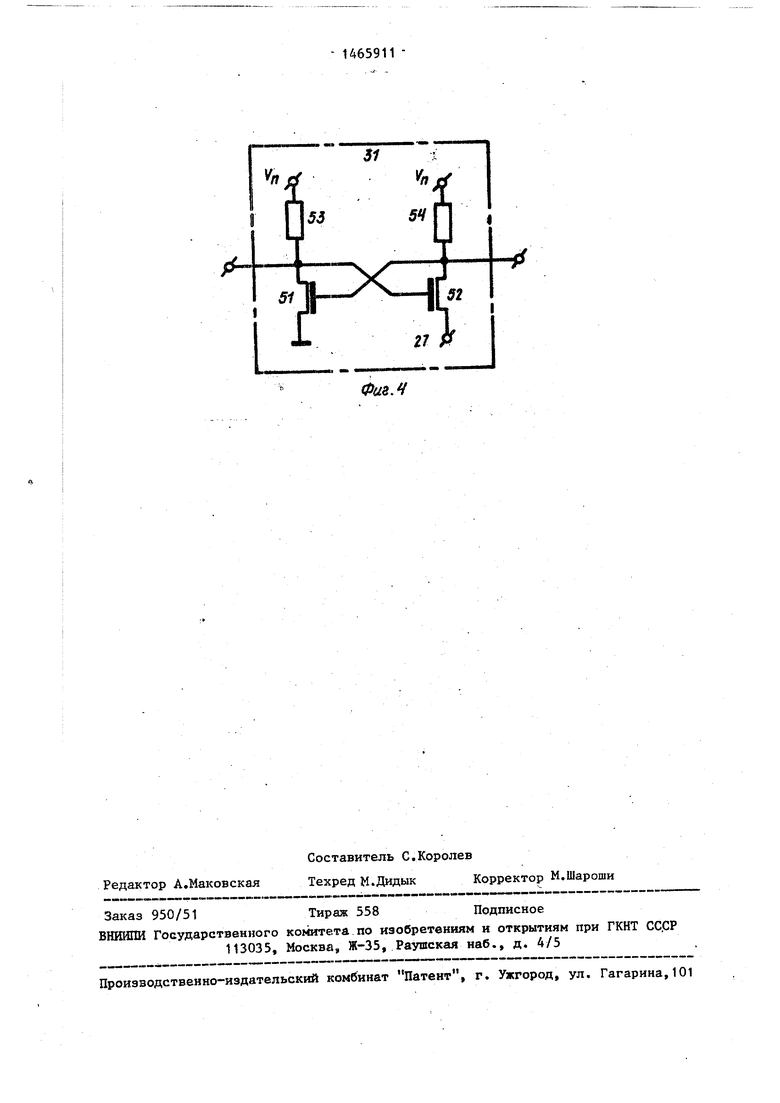

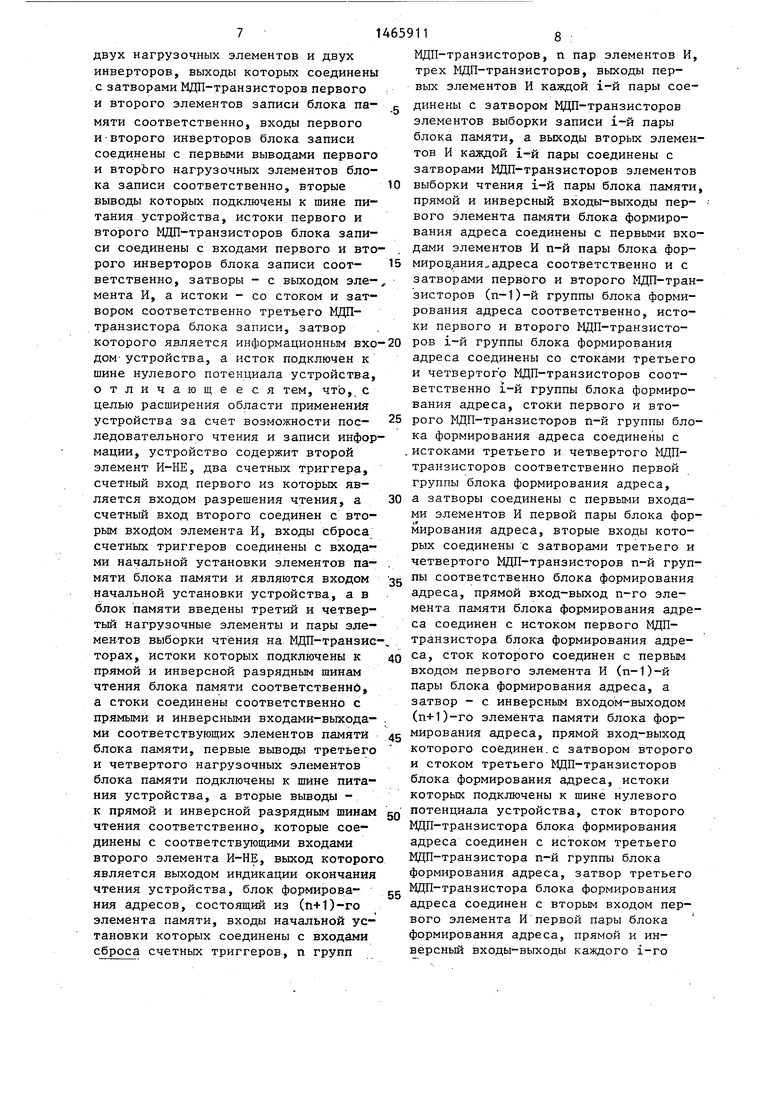

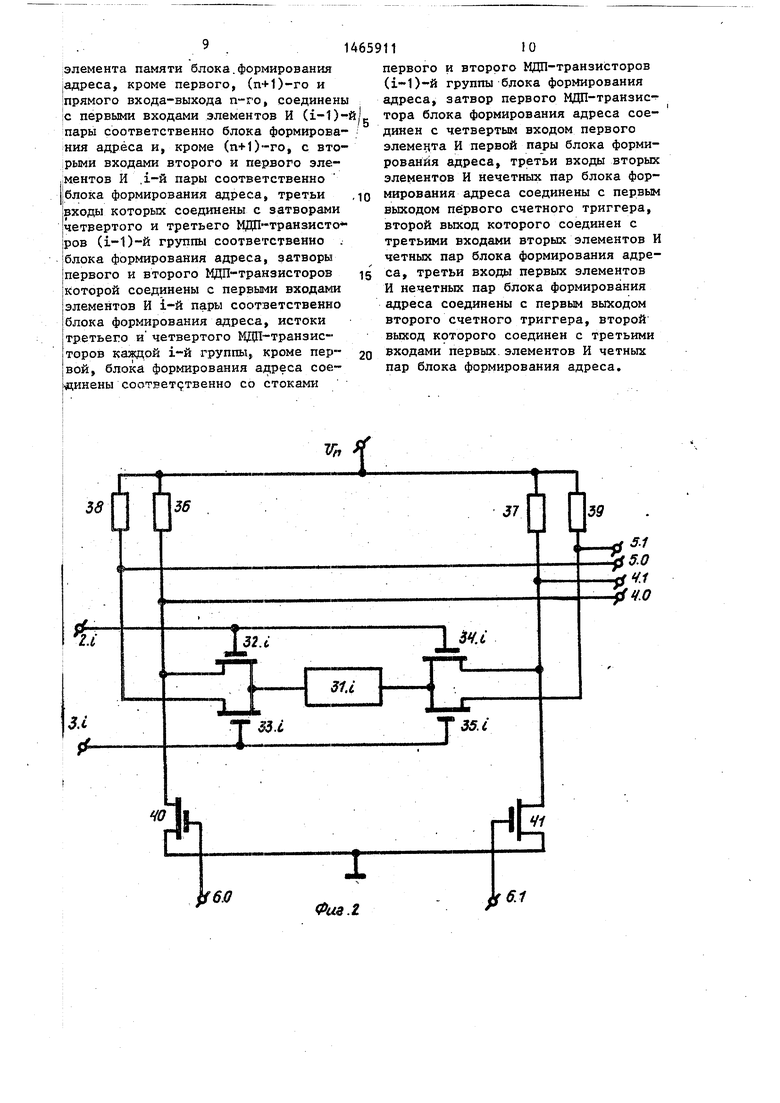

Цель изобретения - расширение об- 5 ласти применения устройства за счет обеспечения возможности последовательного (л:ения и записи информации, На фиг.1 представлена структурная- схема запоминающего устройства; на фиг.2 - схема блока памяти; на,фиг,3 схема блока формирования адреса; на фиг,4 пример реализации элемента памяти.

Запоминающее устройство содержит блок 1 памяти с адресными входами записи и чтения 2,,3j информационными выходами записи и чтения 4, 5, ин- формационньми входами 6, блок 7 формировании адреса с входами управления чтением 8, 9 и записью 10, 11, первый 12 и второй 13 счетные триггеры, инверторы 14, 15 блока записи, первьй 16 и второй 17 элементы И-НЕ, элемент И 18, триггер 19 индикации окончания зап иси, состоящий из эле- мента .1 1-ШШ-НЕ и инвертора,МДП-тран- зисторы 20-22 блока записи, нагрузочные элементы 23, 24 блока записи, вход 25 разрешения чтения, вход 26 разреше шя записи, вход 27 начальной установки 3 информационны вход 28, выход 29 индикации окончания чтения, выход 30 индикации окончания записи.

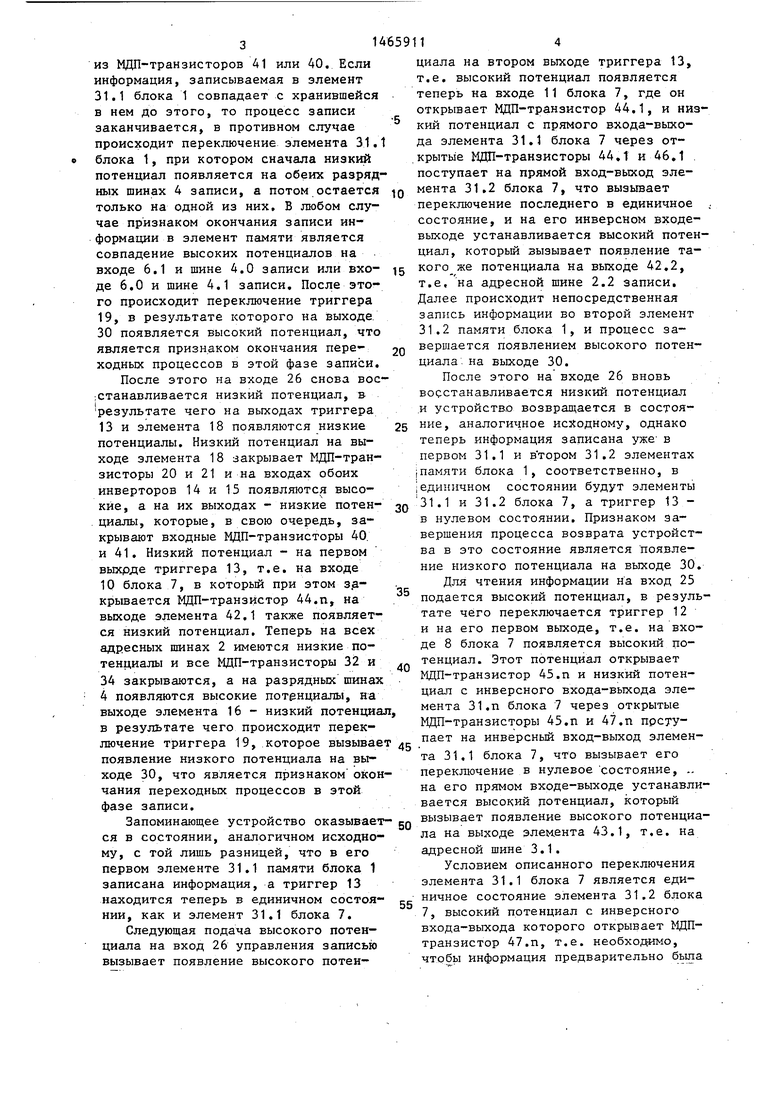

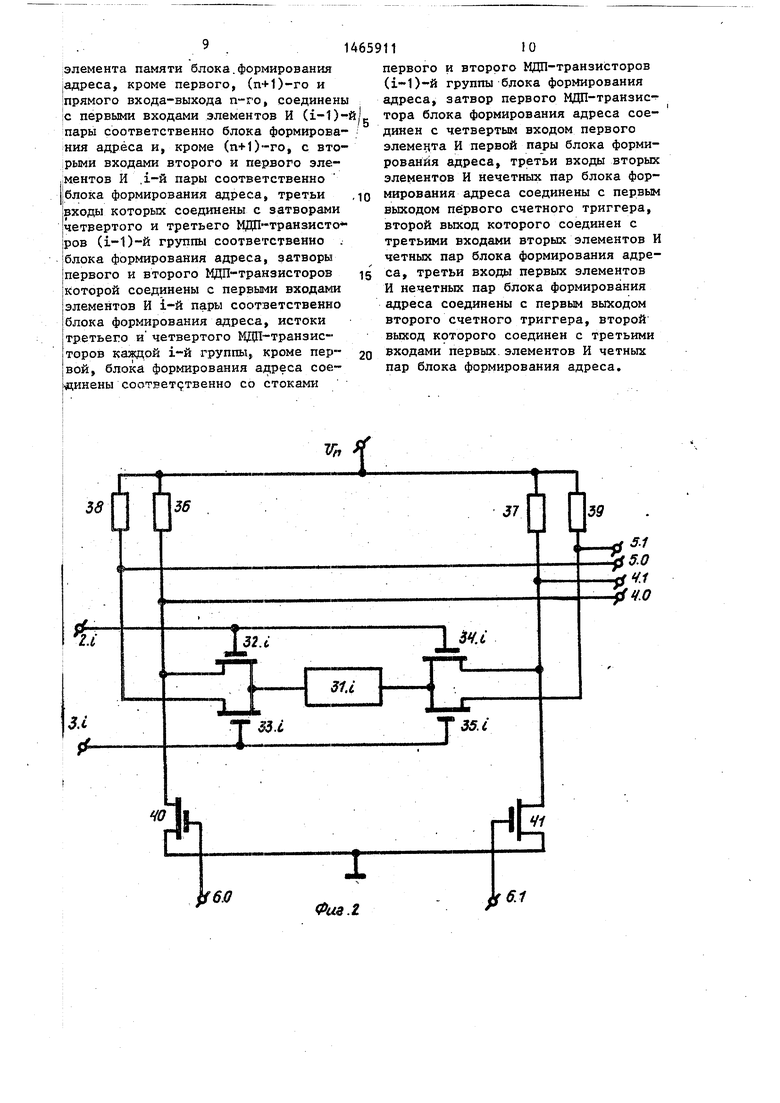

Блок 1 памяти (фиг,2) содержит элементы 31 памяти, ВДП-транзисторы 32-35 элементов выборки З аписи и чте- кия, нагрузочные элементы 36-39, МДП-транзисторы 40, 41 элементов за-. писи, .40

Блок 7 формирования адреса (фиг.З) состоит из элементов 31 памяти, первых 42 и вторых 43 элементов И, М,Ц11- транзисторов 44-47, ВДП-транзисторов 48-50.45

Элементы 31 памяти (фиг,4) состоят из МДП-транзисторов 51, 52 и элементов 53, 54 нагрузки.

Запоминающее устройство функционирует следующим образом.

Перед началом работы на вход 27 начальной установки подается высокий потенциал, в результате чего триггеры 12 и 13 и все элементы 31 памяти сбрасываются в нулевое состояние, при этом на прямых входах-выходах элементов 31 памяти, устанавливаются высокие, а на их инверсных входах- выходах низкие потенциалы. В ис35

55

30

50

0

5

0

5

0

5

ходном состоянии на всех входах 25- ,27 имеются-; низкие потенциалы, при этом на всех выходах триггеров 12 и 13 - низкие потенциалы, вследствие чего на адресных шинах 2 чтения и 3 записи также низкие потенциалы, на разрядных шинах 4,5 - высокие потенциалы, на выходах элементов 14-18 - низкие потенциалы, а значит, низкие потенциалы будут исхрдно и на выходах 29, 30, Описанное исходное сос- тояние соответствует пустому (очищенному от информации) запоминающему устройству.

Работа устройства начинается с записи информации в первый элемент 31,1 блока 1, Для этого информация выставляется на вход 28, а на вход 26 подается высокий потенциал, в результате чего переключается триггер 13 и на его первом выходе, т,е, на входе 10 блока 7 появляется высокий потенциал. Этот потенциал открывает ВДП-транзистор 44.п и низкий потенциал через цепь открытых МДП- транзисторов 49, 44.П и 46.п попадает на прямой вход-выход элемента 31,1 блока 7 и переключает его в единичное состояние. При этом на инверсном входе-выходе элемента 31,1 блока 7 устанавливается высокий потенциал, который открывает МДПгтран- зистор 50, и на прямой вход-выход элемента 31, (п+1) блока 7. через этот

5 открытый МДП-транзистор поступает

низкий потенциал, который переключает его в единичное состояние. При этом на инверсном входе-выходе элемента 31,(п+1) блока 7 устанавливается высокий потенциал, который открывает МДП-транзистор 48, включая тем самым элемент 31,п блока 7 в общую цепь элементов 31 блока 7, Кроме того, этот потенциал поступает на четвертый вход элемента 42.1, в результате чего на адресной, шине 2.1 записи появляется высокий потенциал. Этот потенциал открывает МДП-транзисторы 32.1 и 34,t, и низкий потенциал с одного из входов-выходов элемента 31.1 поступает на одну из разрядных шин 4 записи, В результате переключается элемент 16 и высокий потенциал с его выхода, пройдя через элемент 18, от5 крываёт МДП-транзисторы 20 и 21, после чего переключается один из инве р- торов 14 или 15 и на одном из информационных входов 6 появляется высокий потенциал, который открывает один

0

0

из МДП-транзисторов 41 или 40. Если информация, записываемая в элемент 31.1 блока 1 совпадает с хранившейся в нем до этого, то процесс записи заканчивается, в противном случае происходит переключение элемента 31. блока 1, при котором сначала низкий потенциал появляется на обеих разрядных шинах 4 записи, а потом остается только на одной из них. В любом случае признаком окончания записи информации в элемент Пс1мяти является совпадение высоких потенциалов на входе 6.1 и шине 4.0 записи или вхо- де 6.0 и шине 4.1 записи. После этого происходит переключение триггера 19, в результате которого на выходе. 30 появляется высокий потенциал, что является признаком окончания переходных процессов в этой фазе записи.

После этого на входе 26 снова вос ,станавливается низкий потенциал, в- результате чего на выходах триггера 13 и элемента 18 появляются низкие потенциалы. Низкий потенциал на выходе элемента 18 закрывает МДП-транзис торы 20 и 21 и на входах обоих инверторов 14 и 15 появляются высокие, а на их выходах - низкие потен- циалы, которые, в свою очередь, закрывают входные МДП-транзисторы 40. и 41. Низкий потенциал - на первом вьпфде триггера 13, т.е. на входе 10 блока 7, в которьй при этом з.а- крывается МДП-транзистор 44.п, на выходе элемента 42.1 также появляется низкий потенциал. Теперь на всех адресных шинах 2 имеются низкие потенциалы и все МДП-транзисторы 32 и 34 закрываются, а на разрядных шинах 4 появляются высокие потенциалы, на выходе элемента 16 - низкий потенциа

Для чтения информации н а вход 25 подается высокий потенциал, в результате чего переключается триггер 12 и на его первом выходе, т.е. на входе 8 блока 7 появляется высокий потенциал. Этот потенциал открывает МДП-транзистор 45.п и низкий потенциал с инверсного входа-выхода элемента 31.П блока 7 через открытые МДП-транзисторы 45.п и 47.п прсууВ результате чего происходит перек- лючение триггера 19, которое вызывает 45 . инверсный вход-выход элемен- появление низкого потенциала на вы- та 31.1 блока 7, что вызывает его ходе 30, что является признаком окончания переходных процессов в этой фазе записи.

переключение в нулевое состояние, .. на его прямом входе-выходе устанавливается высокий потенциал, который

Запоминающее устройство оказывает- сп вызывает появление высокого потенциала на выходе элем.ента 43.1, т.е. на адресной шине 3.1.

Условием описанного переключения элемента 31.1 блока 7 является единичное состояние элемента 31.2 блока 7, высокий потенциал с инверсного входа-выхода которого открывает МДП- транзистор 47.п, т.е. необходешо.

ся в состоянии, аналогичном исходному, с той лишь разницей, что в его первом элементе 31.1 памяти блока 1 записана информация, а триггер 13 находится теперь в единичном состоянии, как и элемент 31,1 блока 7.

55

Следующая подача высокого потенциала на вход 26 управления записью вызывает появление высокого потенчтобы информация предварительно бьша

10

15

59114

циала на втором выходе триггера 13, т.е. высокий потенциал появляется теперь на входе 11 блока 7, где он открывает МДП-транзистор 44.1, и низкий потенциал с прямого входа-выхода элемента 31.1 блока 7 через открытые МДП-транзисторы 44,1 и 46,1 . поступает на прямой вход-выход элемента 31.2 блока 7, что вызывает переключение последнего в единичное ..

0

5

о

состояние, и на его инверсном входе- выходе устанавливается высокий потенциал, который вызывает появление такого же потенциала на выходе 42,2, т.е. на адресной шине 2.2 записи. Далее происходит непосредственная запись информации во второй элемент 31.2 памяти блока 1, и процесс завершается появлением высокого потенциала на выходе 30.

После этого на входе 26 вновь восстанавливается низкий потенциал и устройств.о возвращается в состоя- 5 ние, аналогичное исходному, однако теперь информация записана уже в первом 31.1 и в тором 31.2 элементах |памяти блока 1, соответственно, в iединичном состоянии будут элементы 31.1 и 31.2 блока 7, а триггер 13 - в нулевом состоянии. Признаком завершения процесса возврата устройства в это состояние является появление низкого потенциала на выходе 30.

Для чтения информации н а вход 25 подается высокий потенциал, в результате чего переключается триггер 12 и на его первом выходе, т.е. на входе 8 блока 7 появляется высокий потенциал. Этот потенциал открывает МДП-транзистор 45.п и низкий потенциал с инверсного входа-выхода элемента 31.П блока 7 через открытые МДП-транзисторы 45.п и 47.п прсуу5

0

45 . инверсный вход-выход элемен- та 31.1 блока 7, что вызывает его

55

чтобы информация предварительно бьша

записана не только в элемент 31,1 блока 1, но и в элемент 31.2 памяти блока 1.

Высокий потенциал на адресной ши- не 3.1 открывает М,ЦП-транзисторы 33.1 и 35.1, и низкий потенциал с одного из вхддов-выходов элемента 31.1 памяти блока 1 поступает на соответствующую разрядную шину 5.0 или 5.1, в результате чего на выходе элемента 17, т.е. на выходе 29, появляется высокий потенциал, что является приз .наком окончания переходных процессов в этой фазе чтения.

После этого на входе 25 восстанав л1-шается .низкий потенциал, в результате чего на выходах триггера 12 также появляются низкие потенциалы, которые, поступив ,на входы 8 и 9 управ ления блока 7, приводят к появлению такг-ix же потенциалов на выходах всех элементов 43, т.е. на адресных шинах 3 чтения, чего, закрываются все П-транзисторы 33 и 35 и на обеих |разрядных шинах 5 восстанавливаются высокие потенциалы, что вызывает по- рвление низкого потенциала на выходе Элемента 17, т.е. на выходе 29. Пос- Ьеднее является признаком окончания переходных процессов в этой, фазе чте |ния,

; Теперь запоминшощее устройство Ьказывается в состоянии, аналогичном р1сходному, причем его первьй элемент р1.1 -блока 1 очищен (соответственно, ервый элемент 31.1 блока 7 находитс нулевом состоянии), а триггер 12 Находится в единичном состоянии

Следующая подача высокого потенци :а на вхдд 25. вызывает появление высокого потенциала на втором выходе |григгера 12, т.е. на.вхдде 9 управ- Ьения блока 7, где открывается МДП- гранзистор 45.1, и, если элемент 31.1 блока 7 находится в единичном состоянии и открыт МДП-транзистор 47.1, то потенциал с инверсного вхо- йа-выхода элемента 31.1 блока 7 попадает на инверсный вход-выход элемента 31.2 блока 7 и переводит его В нулевое состояние, что вызывает, как и в предыдущем случае, чтение информации из соответствующего элемента 31,2 памяти блока 1, которое завершается появлением высокого потенциала на выходе 29.

После этого на входе 25 снова восстанавливается низкий потенциал

ал с

5

с 0 5

0

0

0

5

5

0

5

и устройство переходит в состояние, аналогичное исходному, что завершается появлением низкого потенциала на выходе 29.

Формула изобретения

Запоминающее устройство, содержащее блок памяти, состоящий из п элементов памяти, где п - информационная емкость устройства, п пар элементов выборки записи на НЦП-транзисторах, двух элементов записи на МДП-транзис- торах и двух нагрузочных элементов, первые выводы которых подключены к шине питания устройства, а вторые - к прямой и инверсной разрядным шинам записи блока памяти соответственно, которые подключены к токам МДП-тран- зисторов первого и второго элементов записи соответственно, истоки которьк подключены к шине нулевого потенциала устройства, истоки ВДП-транзисто- ров элементов выборки записи каждой пары подключены к прямой и инверсной . разрядным шинам записи блока памяти соответственно, а стоки соединены соответственно с прямьм и инверсным входом-выходом соответствующих элементов памяти блока памяти, затворы ВДП-транзисторов элементов выборки записи каждой пары объединены, перг вый элемент И-НЕ, входы которого подключены к прямой и инверсной разрядным шинам записи блока памяти, элемент И-ИЛИ-НЕ, инвертор, выход которого яв.ляется выходом признака окончания записи устройства, а вход соединен с выхддом элемента И-ИЛИ-НЕ, первый и. второй входы первой группы которого соединены соответственно с выходами инвертора и первого элемента И-НЕ, первый и второй входы второй, групгш соединены соответственно с прямой разрядной шиной записи блока I памяти и затвором МДП-транзистора I второго элемента записи блока -памяти, I первый и второй входы третьей группы входов элемента И-ШЖ-НЕ соединены соответственно с инверсной разрядной шиной записи блока памяти и затвором МДП-транзистора второго элемента записи блока памяти, элемент И, первый вход которого соединен с выходом первого элемента И-НЕ, второй вход которого является входом разрешения {записи устройства, блок записи, состоящий из трех МДП-транзисторов,

двух нагрузочных элементов и двух инверторов, выходы которых соединены с затворами МДП-транзисторов первого и второго элементов записи блока памяти соответственно, входы первого и-второго инверторов блока записи соединены с первыми выводами первого и вторЬго нагрузочных элементов блока записи соответственно, вторые выводы которых подключены к шине питания устройства, истоки первого и второго МДП-транзисторов блока записи соединены с входами первого и второго инверторов блока записи соот- ветственно, затворы - с выходом элемента И, а истоки - со стоком и затвором соответственно третьего МДП- транзистора блока записи, затвор

МДП-транзисторов, п пар элементов И, трех МДП-транзисторов, вькоды первых элементов И каждой i-й пары соединены с затвором МДП-транзисторов элементов выборки записи i-й пары блока памяти, а выходы вторых элементов И каждой i-й пары соединены с затворами МДП-транзисторов элементов выборки чтения i-й пары блока памяти, прямой и инверсный входы-выходы пер- вого элемента памяти блока формирования адреса соединены с первыми входами элементов И п-й пары блока фор- миро8,ания адреса соответственно и с затворами первого и второго МДП-транзисторов (п-1)-й группы блока формирования адреса соответственно, истоки первого и второго ВДП-транзисто

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство типа "очереди | 1987 |

|

SU1532977A1 |

| Магазинное запоминающее устройство | 1986 |

|

SU1472947A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1987 |

|

SU1494785A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Запоминающее устройство | 1987 |

|

SU1474738A1 |

| Параллельный асинхронный регистр | 1988 |

|

SU1607016A1 |

| Д-триггер | 1985 |

|

SU1261085A1 |

| Элемент памяти | 1989 |

|

SU1635214A1 |

| ЯЧЕЙКА ПАМЯТИ | 1985 |

|

RU1318096C |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения вычислительных устройств с разным быстродействием. Цель изобретения - расширение области применения устройства за счет возможности,.последовательного чтения и записи информации. Поставленная цель достигается тем, что устройство содержит блок 7 фррмиро- вания адресов, два рчетных триггера 12, 13, второй элемент И-НЕ 17 с соответствующими связями. Блок 7 формирования адресов последовательно перебирает адреса всех элементов памяти блока 1 памяти по сигналам, выдаваемым счетными триггерами 12, 13. 4 ил,jfju ч О5 01

которого является информационным вхо-20 Ров х-й группы блока формирования

дом-устройства, а исток подключен к шине нулевого потенциала устройства, отличающееся тем, что,, с

целью расширения области применения устройства за счет возможности последовательного чтения и записи информации, устройство содержит второй элемент И-НЕ, два счетных триггера, счетный вход первого из является входом разрешения чтения, а счетный вход второго соединен с вторым входом элемента И, входы сброса счетных триггеров соединены с входами начальной установки элементов памяти блока памяти и являются входом начальной установки устройства, а в блок памяти введены третий и четвертый нагрузочные элементы и пары элементов выборки чтения на МДП-транзис торах, истоки которых подключены к прямой и инверсной разрядным шинам чтения блока памяти соответственно, а стоки соединены соответственно с прямыми и инверсными входами-выходами соответствующих элементов памяти блока памяти, первые выводы третьего и четвертого нагрузочных элементов блока памяти подключены к шине питания устройства, а вторые выводы - к прямой и инверсной разрядным шинам чтения соответственно, которые соединены с соответствующими входами второго элемента И-НЕ, выход которог является выходом индикации окончания чтения устройства, блок формирования адресов, состоящий из (li+1)-ro элемента памяти, входы начальной установки которых соединены с входами сброса счетных триггеров, п групп

адреса соединены со стоками третьего и четвертого МДП-транзисторов соответственно i-й группы блока формирования адреса, стоки первого и второго ЩП-транзисторов п-й группы блока формирования адреса соединены с истоками третьего и четвертого МДП- транзисторов соответственно первой группы блока формирования адреса,

а затворы соединены с первыми входами элементов И первой пары блока формирования адреса, вторые входы которых соединены с затворами третьего и четвертого МДП-транзисторов п-й группы соответственно блока формирования адреса, прямой вход-выход п-го элемента памяти блока формирования адреса соединен с истоком первого ЩП- транзистора блока формирования адреса, сток которого соединен с первым входом первого элемента И (п-1)-й пары блока формирования адреса, а затвор - с инверсным входом-выходом (п+1)-го элемента памяти блока формирования адреса, прямой вход-выход которого соединен.с затвором второго и стоком третьего МДП-транзисторов блока формирования адреса, истоки которых подключены к шине нулевого потенциала устройства, сток второго МДП-транзистора блока формирования адреса соединен с истоком третьего ВДП-транзистора п-й группы блока формирования адреса, затвор третьего МДП-транзистора блока формирования адреса соединен с вторым входом первого элемента И первой пары блока формирования адреса, прямой и инверсный входы-выходы каждого i-ro

;элемента памяти блока.формирования адреса, кроме первого, (п+1)-го и прямого входа-выхода п-го, соединены }с первыми входами элементов И (1-1)пары соответственно блока формирования адреса и, кроме (п+1)-го, с вторыми входами второго и первого элементов И Д-й пары соответственно блока формирования адреса, третьи входы которых соединены с затворами четвертого и третьего МДП-транзисто - ров (1-1)-й группы соответственно . блока формирования адреса, затворы первого и второго МДП-транзисторов которой соединены с первыми входами элементов И i-й пары соответственно блока формирования адреса, истоки третьего и четвертого МДП-транзисторов каждой i-й группы, кроме первой, блока формирования адреса соединены соответственно со стоками

Vn

38

36

первого и второго МДП-транзисторов (1-1)-й группы блока формирования адреса, затвор первого НДП-транзис- тора блока формирования адреса соединен с четвертым входом первого элемер та И первой пары блока формирования адреса, третьи входы вторых элементов И нечетных пар блока формирования адреса соединены с первым выходом первого счетного триггера, второй выход которого соединен с третьими входами вторых элементов И четных пар блока формирования адреса, третьи входы первых элементов И нечетных пар блока формирования адреса соединены с первым выходом второго счетного триггера, второй выход которого соединен с третьими

входами первых.элементов И четных пар блока формирования адреса.

I

37

йИ

0us.5

.-У

| Полупроводниковое запоминающее устройство | 1978 |

|

SU748508A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство на МОП-транзисторах | 1986 |

|

SU1411823A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-03-15—Публикация

1987-01-04—Подача