Изобретение относится к вычислительной технике и может быть испсшь зовано для считываемой с машинного носителя (например перфоленты, магнитной ленты) ияи пералаваемой через аппаратуру связи в ЭВМ

ИНфОрМсЩИИ..

Известно устройство для контроля принимаемой информации, содержащее группу приемных регистров и мажеритарный элемент, причем информационный вход устройства соединен с входами регистров, а. их выход - с межеритарным элементом С-- Недостаток данного устройства состоит в его сложности. Так как для принятия решения межеритарным блоком требуется как минимум трехкратный прием информации, что с одной стороны усложняет устройство, а с другой уменьшает его быстродействие

Наиболее близким К предлагаемому . по технической сущности является устройство обнаружения и исправления ошибок,, содержащее блок контроля:: четности, регистры, дешифратор, схемы ИСКЛЮЧАЮЩЕЕ ИЛИ, генератор синдрома, устройство обнаружения двойной ошибки, устройство проверки, устройство обнаружения одиночной ошибки И..

Недостатком известного устройства является ограниченность функции корректировки, сводящейся только к исправлению одиночной ошибки, и сложность конструкции.

Целы изобретения является повышение .эффективности контроля информации за счет возможности правильного ввода информации при наличии любых

10 искс1жений в одном из слов пары и даже при постоянном искажении информации одного разряда, в том числе и контрольного. Например, при неправ вильной записи или считьгааник одной

15 дорожки перфоленты или магнитной ленты, при отказе одного канала (соответствующего одному разряду) во время параллельной перед;ачи информации по проводам, применение пред20лагаемой передачи информации по проводам, применение предлагаемой системы позволяет безошибочно восстанавливать информацию.

Поставленная цель достигается

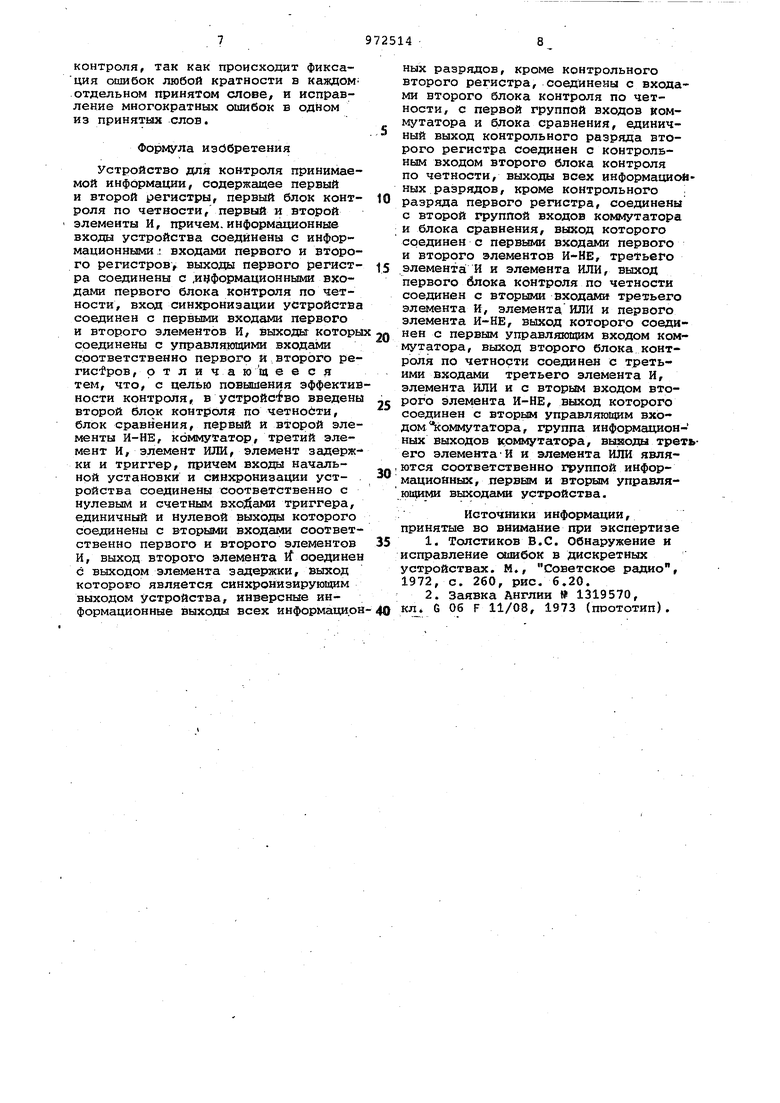

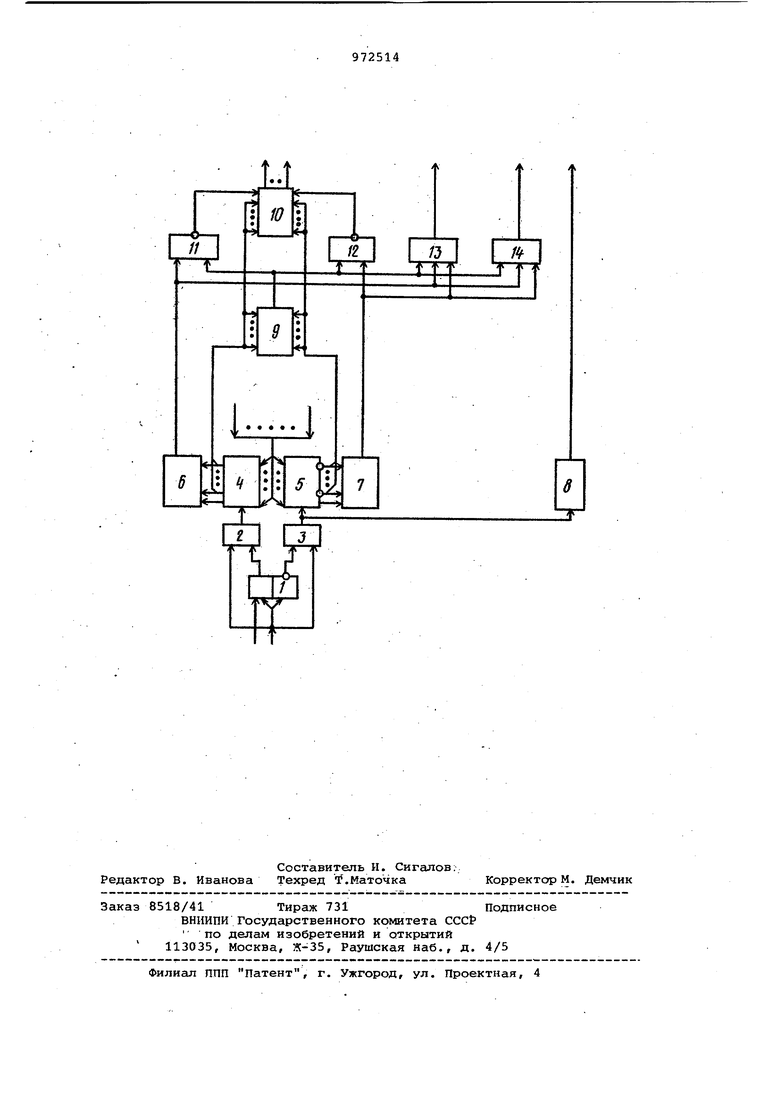

25 тем, что устройство для контроля принимаемой информации, содержащее первый и второй регистры, первый , блок контроля по четн.ссти, первый и второй элементы И, причем информаци30онные входы устройства соединены с информационньи- и входами первого и второго регистров, выходы первого регистра соединены с информационнЕлми входами первого блока контроля по четности, вход синхронизации устройства соединен с первыми входами первого и второго элементов И, выходы Которых соединены с управляющими входами соответственно первого и второго регистров, в устройство введены второй блок контроля по четноети, блок сравнения, первый и второй элементы И-НЕ, коммутатор, третий элемент И, элемент ИЛИ, элемент задержки и триггер, причем входы начальной установки и синхронизации устройства соединены соответственно :с нулевым и счетным входами триггера, единичный и нулевой выходы которого соединены с вторыми входами соответственно первого и второго элементов И, выход второго элемента И-соединен с выходом элемента задерж ки, выход которого является синхрони зирующим выходом устройства, инверсные информационные выходы всех инфор мационных разрядов, кроме контрольного второго регистра, соединены со входами второго блока контроля по четности, с первой группой входов коммутатора и блока сравнения, единичный выход контрольного разряда второго регистра соединен с контроль ным входом второго блока контроля по четности, выходы всех информационных разрядов, кроме контрольного разряда первого регистра, соединены, с второй группой входов коммутатора и блока сравнения, выход которого соединен с первыми входами первого и второго элементов И-НЕ, третьего элемента И и элемента ИЛИ, выход первого блока контроля по четности соединен с вторыми входами третьего элемента И, элемента ИЛИ и первого элемента И-НЕ выход которого соединен с первым управляющим входом коммутатора, выхо второго блока контроля по четности соединен с третьими входами третьего элемента И, элемента ИЛИ и С вторым входом второго. элемента И-НЕ, выход которого соединен с вторым управляющим входом коммутатора, группа информационных выходов коммутатора, выходы третьего элемента И и элемента ИЛИ являются соответственно группой информационных, первым и вторым управляющими выходами устройства. Устройство предполагает, что каждое информационное слово записывается дваяоды: один раз в прямом коде, второй - в дополнительном для про-, верки четности и каждое слово имеет контрольный разряд (например 7 ,00000111 . РОДЦЩЮО) 1-Й байт 2-й байт; На чертеже приведено устройство для контроля принимаемой информации. Устройство содержит триггер 1 счета слов, первый 2 и второй 3 элементы И, первый и второй регистры 4 и 5, первый и второй 6 и 7 блоки контроля по четности; элементы 8 задержки, блок 9 сравнения, коммутатор 10; первый 11 и второй 12 элементы И-НЕ, третий элемент И 13 и элемент ИЛИ 14. Установочный вход устройства подключен к входу Установка в О триггера 1. Вход синхронизации устройства соединен со счетным входом триггера 1 счета слов и входами первого и второго элементов И 2 и 3, Единичный и нулевой выходы триггера 1 Первое слово и Второе слово подключены соответственно к входам первого и второго элементов И 2 и 3. Выход элемента И 2 соединен с С-входами триггеров регистра 4, а выход второго элемента И 3 соединен с С-входами триггеров регистра 5 и входом элемента 8 задержки, выход которого подключен у выходу синхронизации устройства, стробирующий ввод информации в ЭВМ после контроля. Информационные входы, включая и вход контрольного разряда, параллельно подключены к Д-входам триггеров регистров 4 и 5., Единичные выходы триггеров информа- ции регистра 4 (все, кроме контрольного разряда) подключены к входам блока 6 контроля по четности первого слова, входам блока 9 сравнения и информационным входом коммутатора 10. Нулевые выходы регистра 5 (все, кроме контрольного разряда) подключены к входам второго блока 7 контроля по четности второго слова, к входам блока 9 сравнения и информационным входам коммутатора 10. Единичные выходы контрольного разряда регистров 4 и 5 подключены соответственно к входам блоков б и 7 контроля по четности. Выходы Ошибка четности блоков 6 и 7 контроля по четности соединены с входами первого и второго элементов И-НЕ 11 и 12, входами третьего элемента И 13 и „элемента ИЛИ 14. Выход Не равно блока 9 сравнения также подключается к входам элементов И-НЕ 11 и 12, входу третьего элемента И 13 и входу элемента ИЛИ 14 Выходы элементов И-НЕ 11 и 12 соединены с управляющими входами коммутатора 10, выходы которого подключены к информационным выходам устройства. Выходы элементов И 13 и ИЛИ 14 подключены к управляющим выходам устройства соответственно к выходам Неустранимая ошибка и Ошибка. Устройство работает следующим образом. Перед началом поступления информацчи установочный импульс с входа Начальный сброс приходит на вход Установка в О триггера 1 и сбрасывает его. Импульс синхронизации, который вырабатывается ли,бо при чтеНИИ синхродорожки, например при рабо те с перфолентой, либо с помощью специальной схемы, обеспечивающей обязательное тактирование каждого информационного слова, поступает на счетный вход триггера 1 счета слов и на входы первого 2 и второго 3 элементов И. Сигнал Первое слово с выхода единичного триггера 1 посту пает иа второй вход первого элемента И 2, разрешая прохождение импульса синхронизации воспроизведейия с выхода первого элемента И 2 на импульсные С-входы триггеров регистра 4 и, обеспечивая запись в регистр 4 первого слова информации, поступаю щей с группы информационных входов устройства, включая вход контрольног разряда, на потенциальные Д-входы триггеров регистров 4 и 5. Сигнал Второе слово с нулевого выхода триггера 1 поступает на второй вход второго элемента И 3, разрешаг прохождение импульса синхронизации воспроизведения с выхода второго эле мента И 3 на импульсные С-входы триг геров регистра 5 и обеспечивая запись в регистр 5 второго словаг информации, которое поступает с информационных входов устройства, включая и контрольный разряд, на потенциальные Д-входы триггеров регистров 4 и 5. Кроме того, импульс с выхода второго элемента И 3, сопровождающий второе слово информации, через элемент 8 задержки поступает на выход устройства и обеспечивает стробиро.ва ние и ввод информации в ЭВМ после контроля. Сигналы с единичных выходов триггеров информации (все, кроме контрольного разряда) регистра 4, со держащего первое слово, поступают на входы блока б контроля пр четности, входы блока 9 сравнения/информационные входы коммутатора 10. Сигнал с нулевых выходов триггеров информации(все, кроме контрольного разряда) регистра 5, содержащего второе слово, поступают на входы- блока 7 контроля по четности второго слова, входы блока 9 сравнения и входы комм татора 10. Сигналы с единичного выхода триггера контрольного разряда регистров 4 и 5 поступают соответственно на входы блоков 6 и 7 контроля по четности. Сигналы Ошибка четноети с выходов блоков 6 и 7 контроля по четности пЬиходят на входы первого и второго элементов И-НЕ 11 и 12у входы третьего элемента И 13 совпадения и элемента ИЛИ 14. На входы этих же элементов 11-14 поступает сигнал Не равно с выхода блока 9 сравнения. Сигналы с выхода элементов И-НЕ 11 и 12 приходят на управляющие входы коммутатора 10, разрешающие соответственно прохождение первого или второго слова через коммутатор 10 на информационные выходы устройства. Сигналы с выхода третьего элемента Н 13 и элемента 14 ИЛИ приходят на выход устройства соответственно Неустранимая ошибка и Ошибка . Информационные разряды первого и второго слова дополняют друг друга (второе слово формируется путем инвертирования информационных разрядов первого слова и добавлением контрольного разряда, который равен контрольному разряду первого слова). Если оба слова, первое и второе, или хотя бы их информационные разряды, прочтены правильно, даже при ошибках в котрольном разряде, на. выходе блока 9 сравнения отсутствует сигнал Не равное и сигналы с выходов элементов И-НЕ 11 и 12 разрешают прохождение через коммутатор 10 На выходные информационные шины информационных сигналов этой пары слов. Если содержимое регистра 4 первого слова не будет равно инвертированному содержимому регистра 5 второго слова, например, в случае, когде одна из информационных дорожек постоянно не читается из-за неисправности устройства ввода, и соответствующий информационный бит отсутствует как в первом, так и во втором информационном слове, сигнал, Не равно с выхода блока 9 сравне-, ния открывает элементы И-НЕ 11 и 12, запрещая прохождение через коммутатор, 10 того информационного слова, у которого обнаружена ошибка четности. При этом сработает элемент И 13, который выдает на выход блока сигнал Ошибка, свидетельствующий о наличии ошибки в одном из слов или в обоих. Если при несравнении двух слов в обоих словах обнаруживается ошибка четности, сигналы на выходе коммутатора 10 будут отсутствовать, т.е. информация теряется, так как на оба управляющих входа коммутатора будут поступать запрещающие сигналы, в этом случае сработают элементы И 13 и элемент ИЛИ 14 и на выходе устройства появятся сигналы Неисправимая ошибка и Ошибка, что свидетельствует о том, что информация не поддается восстановлению. Применение второго блока контроля на четность, блок сравнения, первого и второго элемента И-НЕ, коммутатора, третьего элемента И, элемента ИЛИ, элемента задержки и три1тера значиельно увеличивает эффективность

контроля, так как происходит фиксация ошибок любой кратности в каждоМ отдельном принятом суюве, и исправление многократных ошибок в одном из принятых слов.

Формула изобретения

Устройство для контроля принимаемой информации, содержащее первый и второй регистры, первый блок контроля по четности, первый и второй элементы И, причем.информационные входы устройства соединены с информационными ; входами первого и второго регистров, выходы первого регистра соединены с .информационными входами первого блока контроля по четности, вход синхронизации устройства соединен с первыми входами первого и второго элементов И, выходы- которы соединены с управляющими входами соответственно первого и второго регистров , о т л и ч а ю щ е е с я тем, что, с целью повышения эффективности контроля, в устройс- во введены второй блок контроля по четнойти, блок сравнения, первый и второй элементы И-НЕ, коммутатор, третий элемент И, элемент ИЛИ, элемент задержки и триггер, причем входы начальной установки и синхронизации устройства соединены соответственно с нулевым и счетным входами триггера, единичный и нулевой выходы которого соединены с вторыми входами соответственно первого и второго элементов И, выход второго элемента rf соединен с выходом элемента задержки, выход которого является синхронизирующим выходом устройства, инверсные информационные выходы всех информацией

ных разрядов, кроме контрольного второго регистра, соединены с входами второго блока контроля по четности, с первой группой входов коммутатора и блока сравнения, единичный выход контрольного разряда второго регистра соединен с контрольным входом второго блока контроля по четности, выходы всех информациейных разрядов, кроме контрольного разряда первого регистра, соединены с второй группой входов коммутатора и блока сравнения, выход которого соединен с первыми входами первого и второго элементов И-НЕ, третьего элемента: И и элемента ИЛИ, выход первого блока контроля по четности соединен с вторыми входами третьего элемента И, элемента ИЛИ и первого элемента И-НЕ, выход которого соединен с первым управляющим входом коммутатора, выход второго блока контроля по четности соединен с третьими входами третьего элемента И, элемента ИЛИ и с вторым входом второго элемента И-НЕ, выход которого соединен с вторым управляющим входом Коммутатора , группа информациейных выходов коммутатора, выходщ треего элемента-И и элемента ИЛИ являются соответственно группой информационных, первым и вторым управляюйчими выхода1ми устройства,

; Источники информации, принятые во внимание при экспертизе

1.Толстиков B.C. Обнаружение и исправление шшбок в дискретных устройствах. М., Советское радио, 1972, с. 260, рис. 6.20.

2.Заявка Англии 1319570, кл G Об F 11/08, 1973 (шэототип).

м

1

10

//

u:

/J

±

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля двоичного кода на четность | 1981 |

|

SU989558A1 |

| Устройство для кодирования и декодирования последовательного кода с коррекцией одиночных ошибок | 1976 |

|

SU732877A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1265860A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1985 |

|

SU1249523A2 |

| Устройство для сдвига информации | 1983 |

|

SU1188783A2 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство для аппаратурной трансляции языков программирования | 1985 |

|

SU1270766A1 |

i 1

д

Авторы

Даты

1982-11-07—Публикация

1981-02-17—Подача