входами второго коммутатора, выход сумматора по модулю два блока контроля

ошибки является выходом ошибки устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сдвига информации с контролем | 1985 |

|

SU1325481A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| Устройство для мажоритарного выбора сигналов | 1989 |

|

SU1656539A1 |

| Устройство для сдвига информации | 1986 |

|

SU1363310A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1092570A1 |

| Устройство для сдвига информации с контролем | 1983 |

|

SU1095184A1 |

УСТРОЙСТВО ДЛЯ СДВИГА ИНФОРМАЦИИ по авт. св. № 1014031, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения контроля сдвига, в него введены пятый и шестой коммутаторы, сумматор по модулю два, блок формирования четности данных, содержаший три сумматора по модулю два, блок записи контрольного разряда, содержащий элемент И, два элемента ИЛИ и триггер, блок коррекции четности, содержащий элемент ИЛИ-НЕ и элемент И, блок контроля ошибки, содержащий элемент ИЛИ и сумматор по модулю два, причем в блоке записи контрольного разряда выход элемента И соединен с первым входом первого элемента ИЛИ, выход которого соединен с информационным входом триггера, вход синхронизации которого соединен с выходом второго элемента ИЛИ, первый вход которого объединен с входом элемента И, в блоке коррекции четности выход элемента ИЛИ-НЕ соединен с первым входом элемента И, в блоке контроля ошибки выход элемента ИЛИ соединен с первым входом сумматора по модулю два, первая, вторая и третья группы выходов блока коммутаторов соединены соответственно с группами входом первого, второго и третьего сумматоров по модулю два блока формирования четности данных, выходы которых соединены соответственно с вторым входом сумматора по модулю два и первым и вторым входами элемента ИЛИ блока контроля ошибки, выход сумматора по модулю два блока контроля ошибки является выходом ошибки устройства, группа выходов первого мультиплексора соединена с группой входов сумматора по модулю два, выход которого является выходом контрольного разряда устройства, второй вход элемента И блока записи контрольного разряда является входом контрольного разряда устройства, первые выходы пятого и шестого коммутаторов соединены соответственно с вторым н третьим входами первого элемента ИЛИ блока записи контрольного разряда, первый вход второго элемента ИЛИ блока записи контрольного разряда объединен с входом записи регистра и третьим входом устройства, второй вход второго элемента ИЛИ блока записи контрольного разряда соединен с шестым выходом блока управления, пер(Л вые информационные входы пятого и шестого коммутаторов являются соответственно входами левого и правого контрольных разрядов устройства, вторые выходы пятого и шестого коммутаторов являются соответственно выходами переноса контрольных разрядов устройства при сдвиге влево и вправо, вторые информационные входы пятого и шестого коммутаторов и третий оо вход сумматора по модулю два объединены 00 и подключены к выходу триггера блока записи контрольного разряда, четвертый вход сумматора по модулю два блока контроля 00 ошибки соединен с выходом элемента И оо блока коррекции четности, вход элемента ИЛИ-НЕ блока коррекции четности соединен с ВЫХОДО1Й третьего коммутатора, второй и третий входы элемента И блока коррекции четности объединены соответственно с первым и вторым входами формирователя записи, первый и второй управляющие входы пятого коммутатора объединены соответственно с первым и вторым управляющими входами первого коммутатора, первый и второй управляющие входы шестого коммутатора объединены соответственно с первым и вторым управляющими

i

Изобретение относится к вычислительной технике, предназначено для сдвига информации на заданное число разрядов с соответствующим заполнением высвобождающихся позиций и контроля по четности правильности выполнения операций сдвига и может быть использовано в ЭВМ, вычислительных устройствах и приборах цифровой автоматики (например, для построения АЛУ с плавающей запятой, умножителей, устройств деления, для выравнивания границ слов, считанных из памяти и др.), а также для построения сдвигающих устройств повышенной разрядности.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения контроля сдвига.

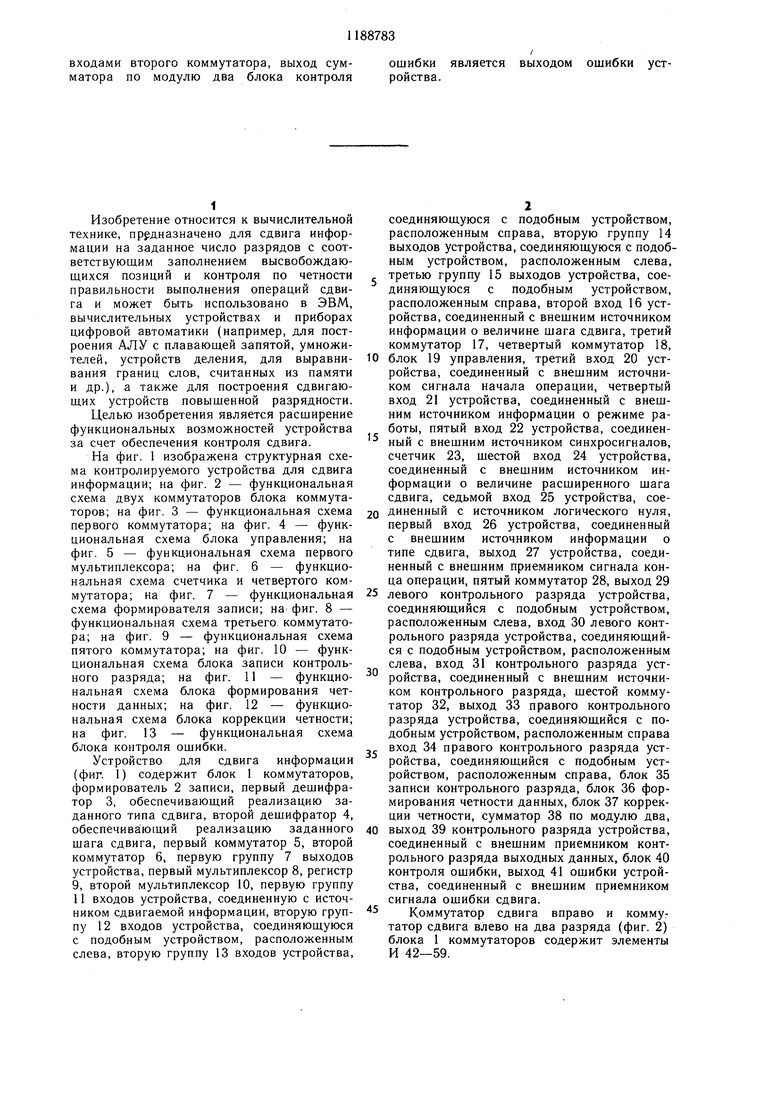

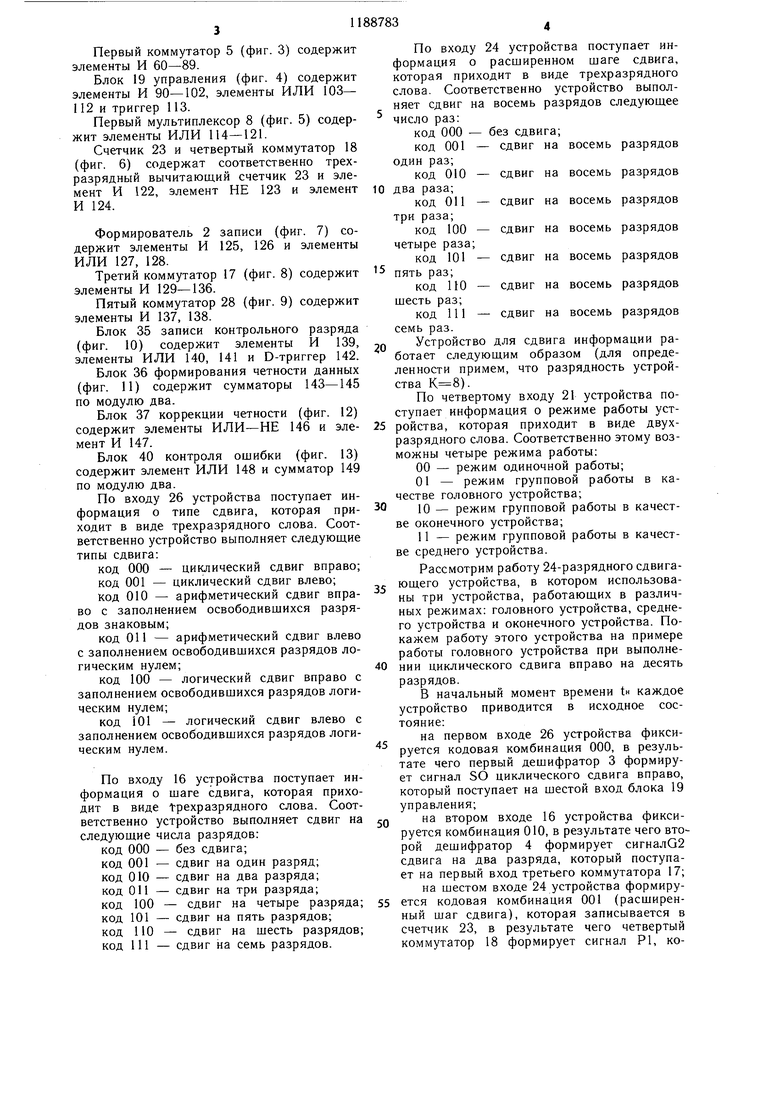

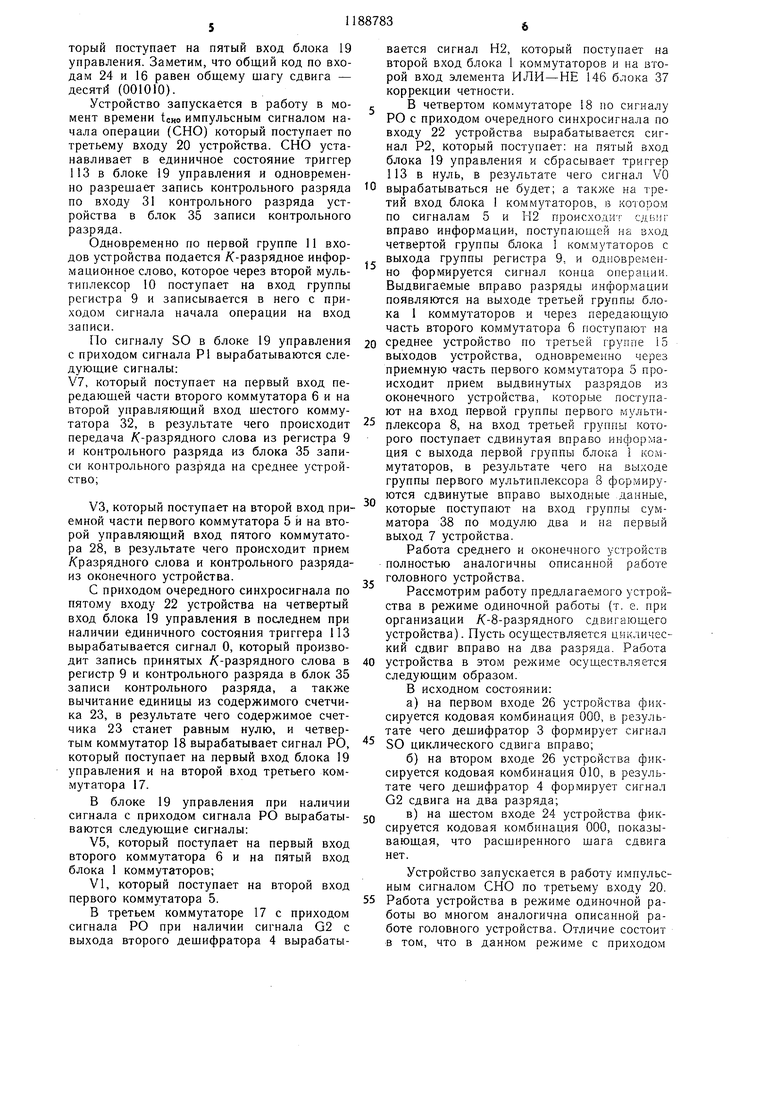

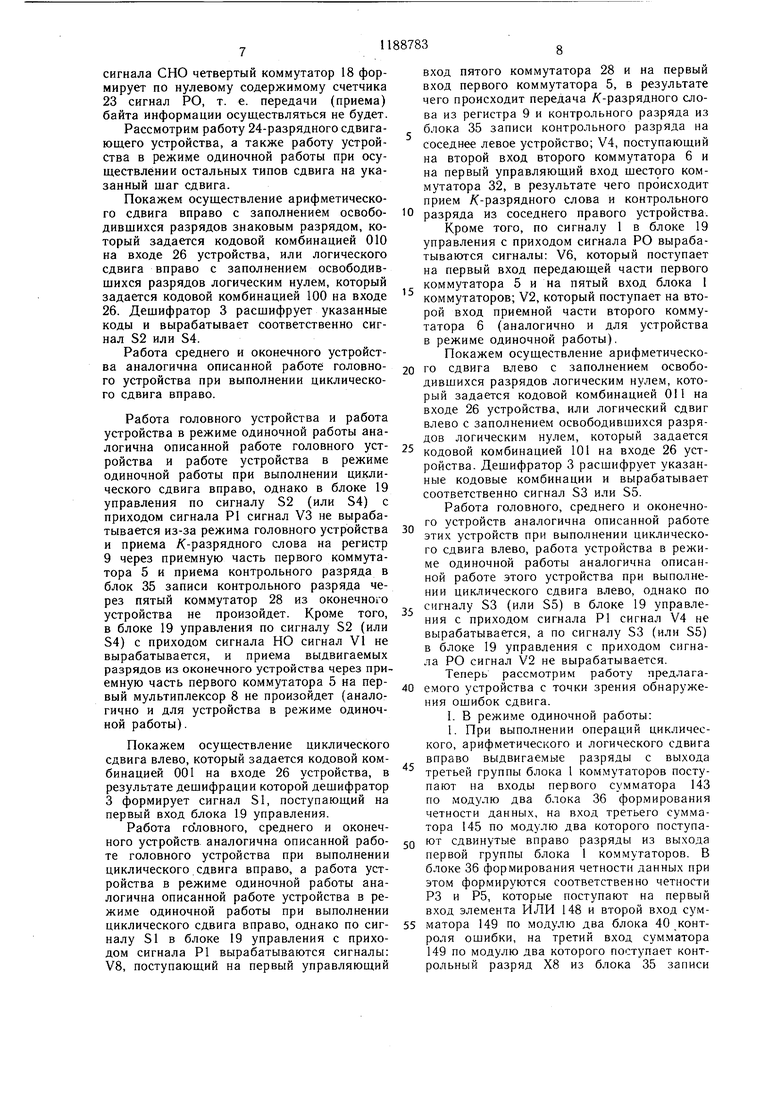

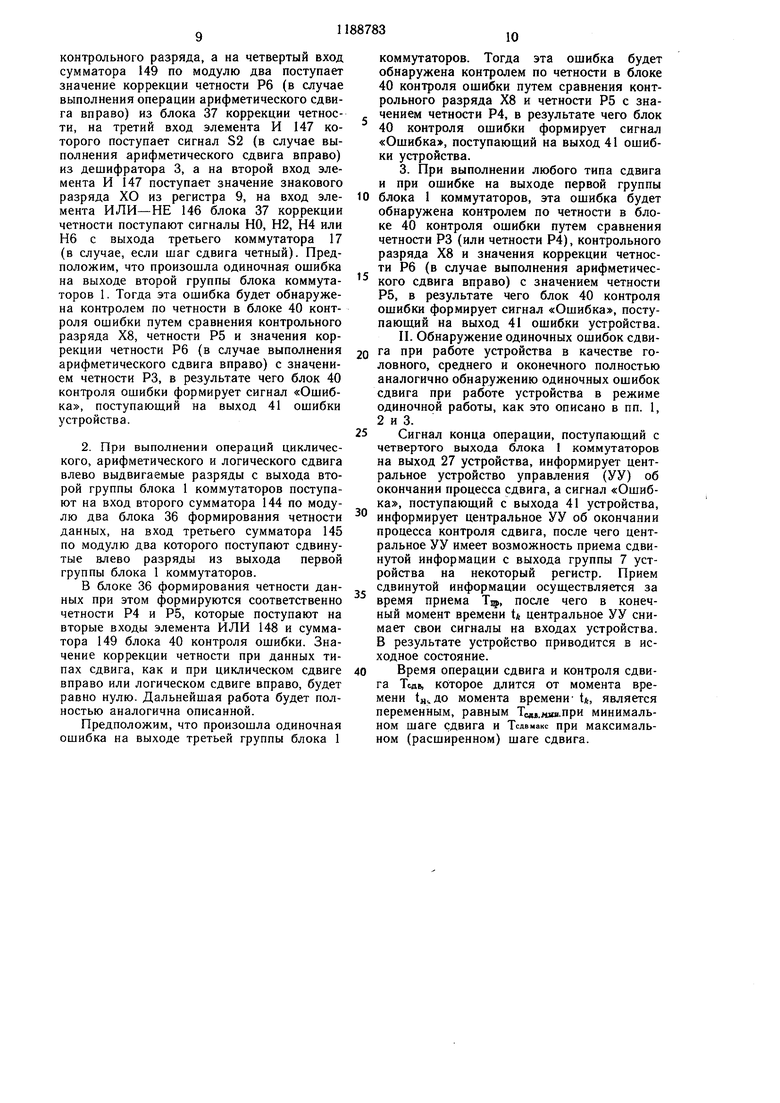

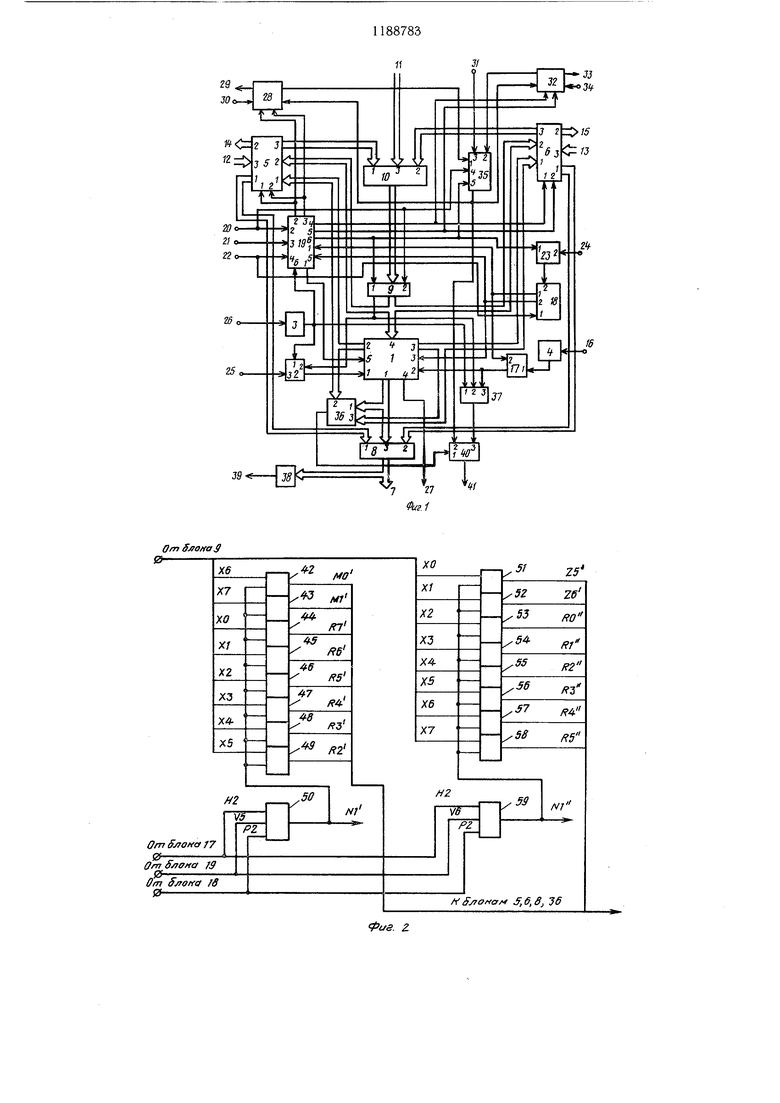

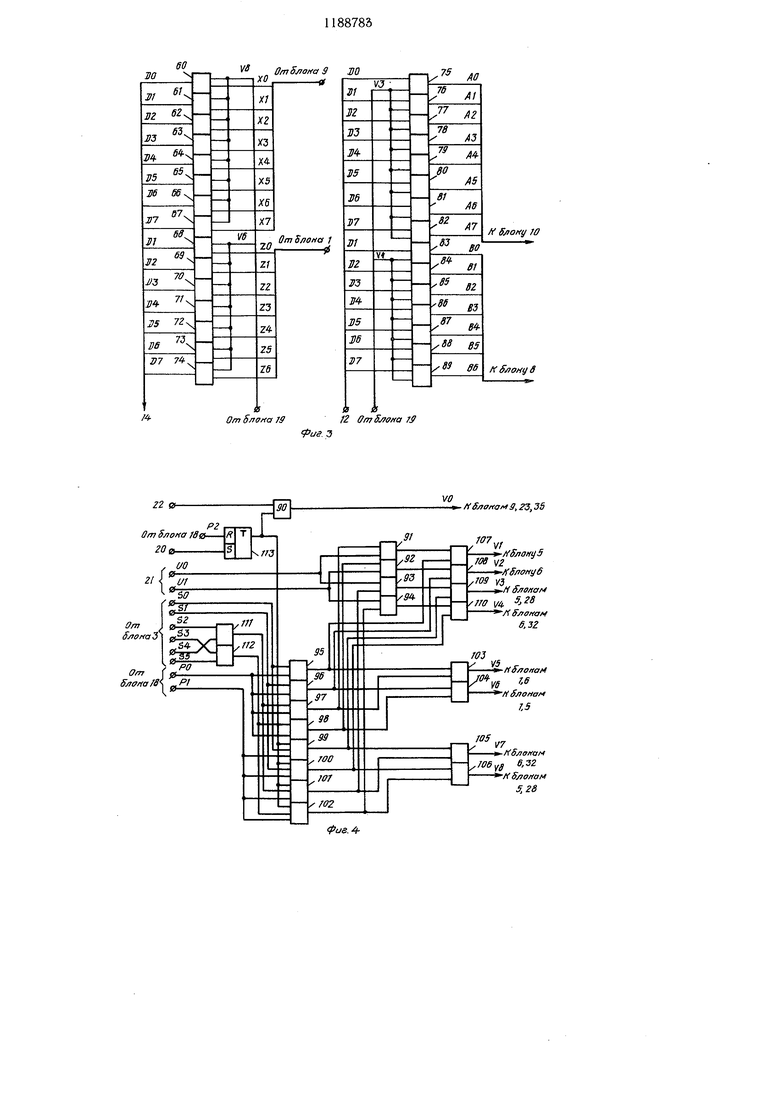

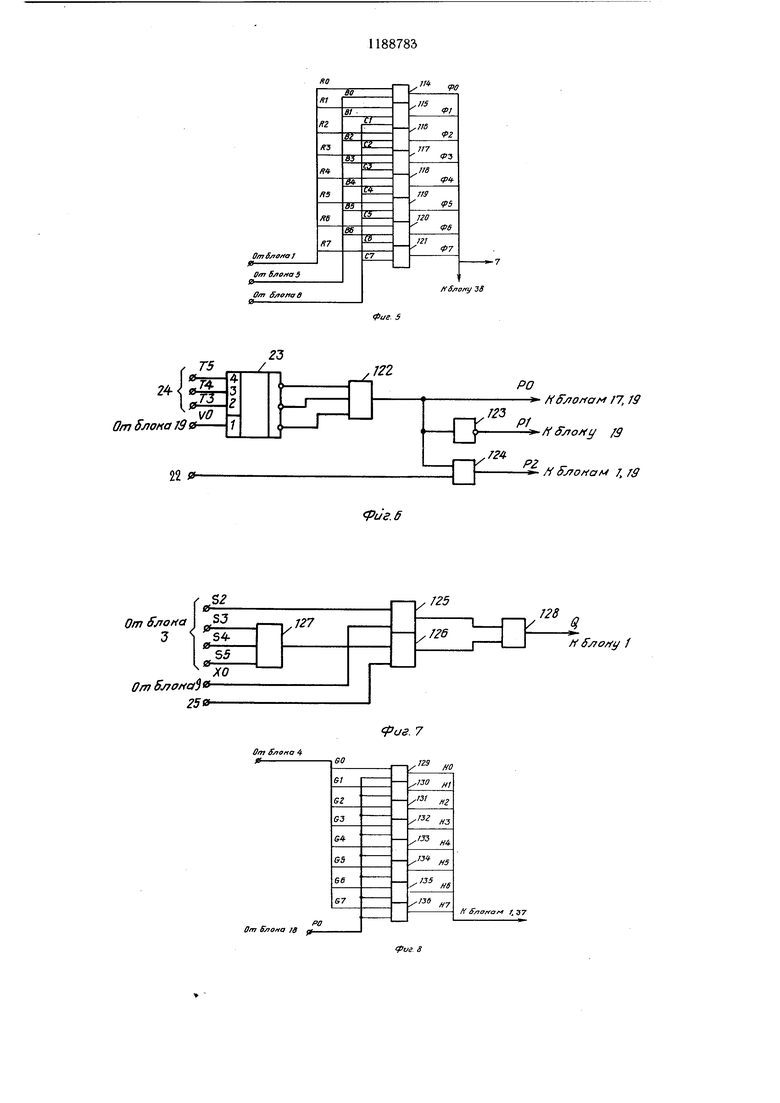

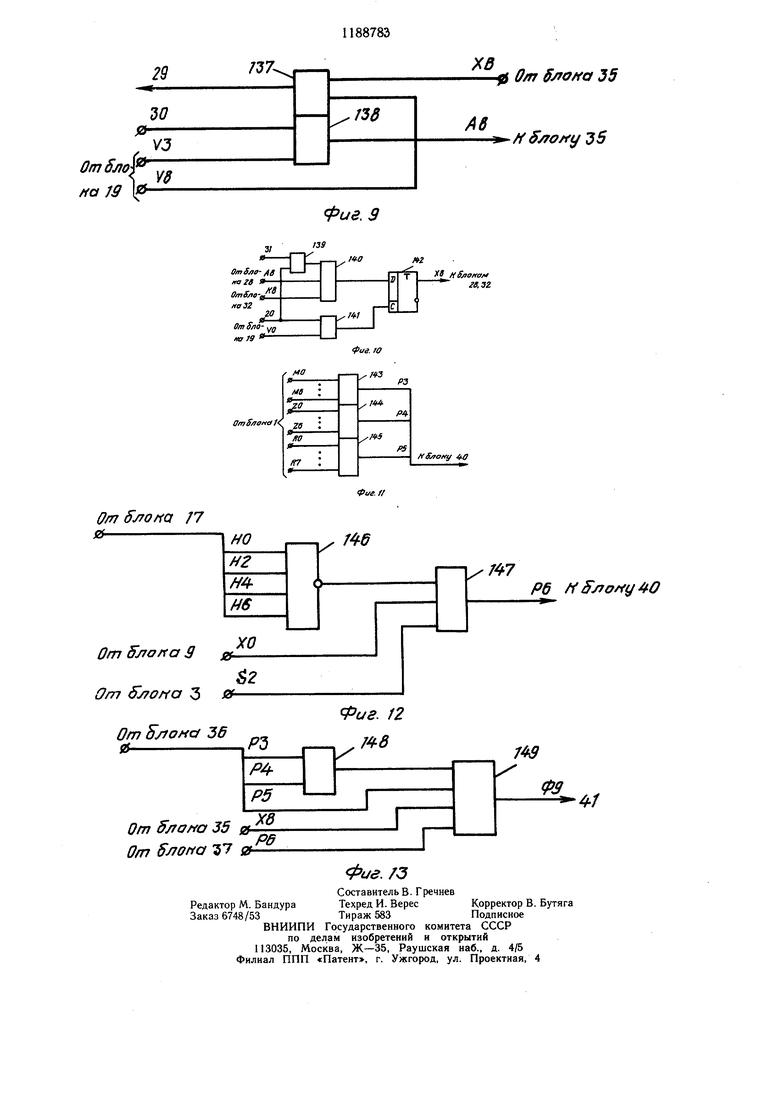

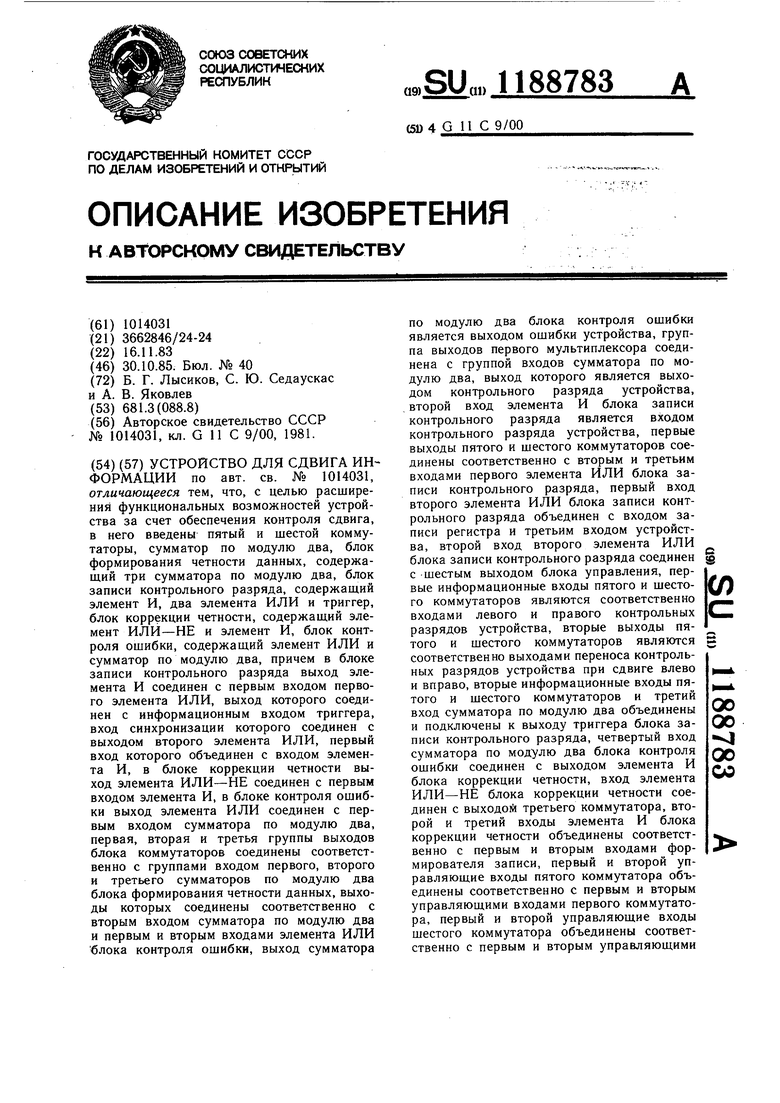

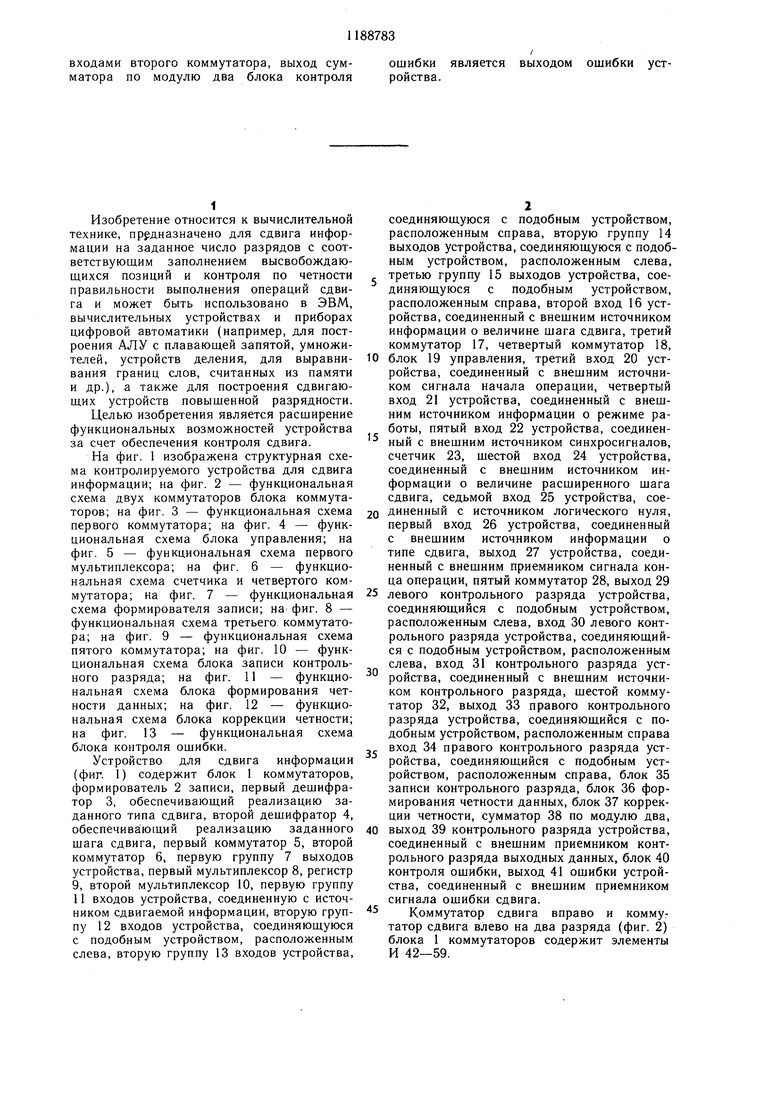

На фиг. 1 изображена структурная схема контролируемого устройства для сдвига информации; на фиг. 2 - функциональная схема двух коммутаторов блока коммутаторов; на фиг. 3 - функциональная схема первого коммутатора; на фиг. 4 - функциональная схема блока управления; на фиг. 5 - функциональная схема первого мультиплексора; на фиг. 6 - функциональная схема счетчика и четвертого коммутатора; на фиг. 7 - функциональная схема формирователя записи; на фиг. 8 - функциональная схема третьего коммутатора; на фиг. 9 - функциональная схема пятого коммутатора; на фиг. 10 - функциональная схема блока записи контрольного разряда; на фиг. 11 - функциональная схема блока формирования четности данных; на фиг. 12 - функциональная схема блока коррекции четности; на фиг. 13 - функциональная схема блока контроля ошибки.

Устройство для сдвига информации (фиг. 1) содержит блок 1 коммутаторов, формирователь 2 записи, первый дешифратор 3, обеспечивающий реализацию заданного типа сдвига, второй дешифратор 4, обеспечива ющий реализацию заданного шага сдвига, первый коммутатор 5, второй коммутатор 6, первую группу 7 выходов устройства, первый мультиплексор 8, регистр 9, второй мультиплексор 10, первую группу 11 входов устройства, соединенную с источником сдвигаемой информации, вторую группу 12 входов устройства, соединяющуюся с подобным устройством, расположенным слева, вторую группу 13 входов устройства.

соединяющуюся с подобным устройством, расположенным справа, вторую группу 14 выходов устройства, соединяющуюся с подобным устройством, расположенным слева, третью группу 15 выходов устройства, соединяющуюся с подобным устройством, расположенным справа, второй вход 16 устройства, соединенный с внещним источником информации о величине щага сдвига, третий коммутатор 17, четвертый коммутатор 18, блок 19 управления, третий вход 20 устройства, соединенный с внешним источником сигнала начала операции, четвертый вход 21 устройства, соединенный с внешним источником информации о режиме работы, пятый вход 22 устройства, соединенный с внешним источником синхросигналов, счетчик 23, шестой вход 24 устройства, соединенный с внешним источником информации о величине расширенного щага сдвига, седьмой вход 25 устройства, соединенный с источником логического нуля, первый вход 26 устройства, соединенный с внещним источником информации о типе сдвига, выход 27 устройства, соединенный с внешним приемником сигнала конца операции, пятый коммутатор 28, выход 29 левого контрольного разряда устройства, соединяющийся с подобным устройством, расположенным слева, вход 30 левого контрольного разряда устройства, соединяющийся с подобным устройством, расположенным слева, вход 31 контрольного разряда устройства, соединенный с внещним источником контрольного разряда, шестой коммутатор 32, выход 33 правого контрольного разряда устройства, соединяющийся с подобным устройством, расположенным справа вход 34 правого контрольного разряда устройства, соединяющийся с подобным устройством, расположенным справа, блок 35 записи контрольного разряда, блок 36 формирования четности данных, блок 37 коррекции четности, сумматор 38 по модулю два, выход 39 контрольного разряда устройства, соединенный с внещним приемником контрольного разряда выходных данных, блок 40 контроля ощибки, выход 41 ощибки устройства, соединенный с внешним приемником сигнала ошибки сдвига.

Коммутатор сдвига вправо и коммутатор сдвига влево на два разряда (фиг. 2) блока 1 коммутаторов содержит элементы И 42-59.

Первый коммутатор 5 (фиг. 3) содержит элементы И 60-89.

Блок 19 управления (фиг. 4) содержит элементы И 90-102, элементы ИЛИ 103- 112 и триггер 113.

Первый мультиплексор 8 (фиг. 5) содержит элементы ИЛИ 114-121.

Счетчик 23 и четвертый коммутатор 18 (фиг. 6) содержат соответственно трехразрядный вычитающий счетчик 23 и элемент И 122, элемент НЕ 123 и элемент И 124.

Формирователь 2 записи (фиг. 7) содержит элементы И 125, 126 и элементы ИЛИ 127, 128.

Третий коммутатор 17 (фиг. 8) содержит элементы И 129-136.

Пятый коммутатор 28 (фиг. 9) содержит элементы И 137, 138.

Блок 35 записи контрольного разряда (фиг. 10) содержит элементы И 139, элементы ИЛИ 140, 141 и D-триггер 142.

Блок 36 формирования четности данных (фиг. 11) содержит сумматоры 143-145 по модулю два.

Блок 37 коррекции четности (фиг. 12) содержит элементы ИЛИ-НЕ 146 и элемент И 147.

Блок 40 контроля ошибки (фиг. 13) содержит элемент ИЛИ 148 и сумматор 149 по модулю два.

По входу 26 устройства поступает информация о типе сдвига, которая приходит в виде трехразрядного слова. Соответственно устройство выполняет следующие типы сдвига:

код 000 - циклический сдвиг вправо;

код 001 - циклический сдвиг влево;

код 010 - арифметический сдвиг вправо с заполнением освободившихся разрядов знаковым;

код 011 - арифметический сдвиг влево с заполнением освободившихся разрядов логическим нулем;

код 100 - логический сдвиг вправо с заполнением освободившихся разрядов логическим нулем;

код 101 - логический сдвиг влево с заполнением освободившихся разрядов логическим нулем.

По входу 16 устройства поступает информация о шаге сдвига, которая приходит в виде tpexpaзpяднoгo слова. Соответственно устройство выполняет сдвиг на следующие числа разрядов:

код 000 - без сдвига;

код 001 - сдвиг на один разряд;

код 010 - сдвиг на два разряда;

код 011 - сдвиг на три разряда;

код 100 - сдвиг на четыре разряда;

код 101 - сдвиг на пять разрядов;

код ПО - сдвиг на шесть разрядов;

код 111 - сдвиг на семь разрядов.

По входу 24 устройства поступает информация о расширенном шаге сдвига, которая приходит в виде трехразрядного слова. Соответственно устройство выполняет сдвиг на восемь разрядов следующее число раз:

код 000 - без сдвига;

код 001 - сдвиг на восемь разрядов один раз;

код 010 - сдвиг на восемь разрядов 0 два раза;

код 011 - сдвиг на восемь разрядов три раза;

код 100 - сдвиг на восемь разрядов четыре раза;

код 101 - сдвиг на восемь разрядов

пять раз;

код 110 - сдвиг на восемь разрядов шесть раз;

код 111 - сдвиг на восемь разрядов семь раз.

Q Устройство для сдвига информации работает следующим образом (для определенности примем, что разрядность устройства ).

По четвертому входу 21 устройства поступает информация о режиме работы уст5 ройства, которая приходит в виде двухразрядного слова. Соответственно этому возможны четыре режима работы:

00- режим одиночной работы;

01- режим групповой работы в качестве головного устройства;

10 - режим групповой работы в качестве оконечного устройства;

11 - режим групповой работы в качестве среднего устройства.

Рассмотрим работу 24-разрядного сдвигающего устройства, в котором использованы три устройства, работающих в различных режимах: головного устройства, среднего устройства и оконечного устройства. Покажем работу этого устройства на примере работы головного устройства при выполнеНИИ циклического сдвига вправо на десять разрядов.

В начальный момент времени t« каждое устройство приводится в исходное состояние:

на первом входе 26 устройства фиксируется кодовая комбинация 000, в результате чего первый дешифратор 3 формирует сигнал SO циклического сдвига вправо, который поступает на шестой вход блока 19 управления;

на втором входе 16 устройства фиксируется комбинация 010, в результате чего второй дешифратор 4 формирует сигналО2 сдвига на два разряда, который поступает на первый вход третьего коммутатора 17; на шестом входе 24 устройства формируется кодовая комбинация 001 (расширенный шаг сдвига), которая записывается в счетчик 23, в результате чего четвертый коммутатор 18 формирует сигнал Р1, который поступает на пятый вход блока 19 управления. Заметим, что общий код по входам 24 и 16 равен общему шагу сдвига - десяти (001010).

Устройство запускается в работу в момент времени 1сно импульсным сигналом начала операции (СНО) который поступает по третьему входу 20 устройства. СНО устанавливает в единичное состояние триггер 113 в блоке 19 управления и одновременно разрешает запись контрольного разряда по входу 31 контрольного разряда устройства в блок 35 записи контрольного разряда.

Одновременно по первой группе 11 входов устройства подается /С-разрядное информационное слово, которое через второй мультиплексор 10 поступает на вход группы регистра 9 и записывается в него с приходом сигнала начала операции на вход записи.

По сигналу SO в блоке 19 управления с приходом сигнала Р1 вырабатываются следующие сигналы:

V7, который поступает на первый вход передающей части второго коммутатора 6 и на второй управляющий вход шестого коммутатора 32, в результате чего происходит передача /(-разрядного слова из регистра 9 и контрольного разряда из блока 35 записи контрольного разряда на среднее устройство;

V3, который поступает на второй вход приемной части первого коммутатора 5 и на второй управляющий вход пятого коммутатора 28, в результате чего происходит прием /(разрядного слова и контрольного разрядаиз оконечного устройства.

С приходом очередного синхросигнала по пятому входу 22 устройства на четвертый вход блока 19 управления в последнем при наличии единичного состояния триггера 113 вырабатывается сигнал О, который производит запись принятых /(-разрядного слова в регистр 9 и контрольного разряда в блок 35 записи контрольного разряда, а также вычитание единицы из содержимого счетчика 23, в результате чего содержимое счетчика 23 станет равным нулю, и четвертым коммутатор 18 вырабатывает сигнал РО, который поступает на первый вход блока 19 управления и на второй вход третьего коммутатора 17.

В блоке 19 управления при наличии сигнала с приходом сигнала РО вырабатываются следующие сигналы:

V5, который поступает на первый вход второго коммутатора 6 и на пятый вход блока 1 коммутаторов;

VI, который поступает на второй вход первого коммутатора 5.

В третьем коммутаторе 17 с приходом сигнала РО при наличии сигнала G2 с выхода второго дещифратора 4 вырабатывается сигнал Н2, который поступает на второй вход блока 1 коммутаторов и на второй вход элемента ИЛИ-НЕ 146 блока 37 коррекции четности.

В четвертом коммутаторе 18 по сигналу РО с приходом очередного синхросигнала по входу 22 устройства вырабатывается сигнал Р2, который поступает: на пятый вход блока 19 управления и сбрасывает триггер 113 в нуль, в результате чего сигнал VO

0 вырабатываться не будет; а также на третий вход блока 1 коммутаторов, в котором по сигналам 5 и Н2 происходит сдызг вправо информации, поступающей на вход четвертой группы блока 1 коммутаторов с выхода группы регистра 9, и одновременно формируется сигнал конца операции. Выдвигаемые вправо разряды информации появляются на выходе третьей группы блока 1 коммутаторов и через передающую часть второго коммутатора 6 поступают на

0 среднее устройство по третьей группе 15 выходов устройства, одновременно через приемную часть первого коммутатора 5 происходит прием выдвинутых разрядов из оконечного устройства, которые поступают на вход первой группы первого мультиплексора 8, на вход третьей группы которого поступает сдвинутая вправо информация с выхода первой группы блока 1 коммутаторов, в результате чего на выходе группы первого мультиплексора 8 формируются сдвинутые вправо выходные данные, которые поступают на вход группы сумматора 38 по модулю два и на первый выход 7 устройства.

Работа среднего и оконечного устройств полностью аналогичны описанной рабоге

, головного устройства.

Рассмотрим работу предлагаемого устройства в режиме одиночной работы (т. е. при организации / -8-разрядного сдвигающего устройства). Пусть осуществляется циклический сдвиг вправо на два разряда. Работа

устройства в этом режиме осуществляется следующим образом.

В исходном состоянии:

а)на первом входе 26 устройства фиксируется кодовая комбинация 000, в результате чего дешифратор 3 формирует сигнал

SO циклического сдвига вправо;

б)на втором входе 26 устройства фиксируется кодовая комбинация 010, в результате чего дешифратор 4 формирует сигнал G2 сдвига на два разряда;

в)на шестом входе 24 устройства фиксируется кодовая комбинация 000, показывающая, что расширенного щага сдвига нет.

Устройство запускается в работу импульсным сигналом СНО по третьему входу 20. 5 Работа устройства в режиме одиночной работы во многом аналогична описанной работе головного устройства. Отличие состоит в том, что в данном режиме с приходом

сигнала СНО четвертый коммутатор 18 формирует по нулевому содержимому счетчика 23 сигнал РО, т. е. передачи (приема) байта информации осуществляться не будет.

Рассмотрим работу 24-разрядного сдвигающего устройства, а также работу устройства в режиме одиночной работы при осуществлении остальных типов сдвига на указанный шаг сдвига.

Покажем осуществление арифметического сдвига вправо с заполнением освободившихся разрядов знаковым разрядом, который задается кодовой комбинацией 010 на входе 26 устройства, или логического сдвига вправо с заполнением освободившихся разрядов логическим нулем, который задается кодовой комбинацией 100 на входе 26. Дещифратор 3 расщифрует указанные коды и вырабатывает соответственно сигнал S2 или S4.

Работа среднего и оконечного устройства аналогична описанной работе головного устройства при выполнении циклического сдвига вправо.

Работа головного устройства и работа устройства в режиме одиночной работы аналогична описанной работе головного устройства и работе устройства в режиме одиночной работы при выполнении циклического сдвига вправо, однако в блоке 19 управления по сигналу S2 (или S4) с приходом сигнала Р1 сигнал V3 не вырабатывается из-за режима головного устройства и приема /(-разрядного слова на регистр 9 через приемную часть первого коммутатора 5 и приема контрольного разряда в блок 35 записи контрольного разряда через пятый коммутатор 28 из оконечного устройства не произойдет. Кроме того, в блоке 19 управления по сигналу S2 (или S4) с приходом сигнала НО сигнал VI не вырабатывается, и приема выдвигаемых разрядов из оконечного устройства через приемную часть первого коммутатора 5 на первый мультиплексор 8 не произойдет (аналогично и для устройства в режиме одиночной работы).

Покажем осуществление циклического сдвига влево, который задается кодовой комбинацией 001 на входе 26 устройства, в результате дешифрации которой дешифратор 3 формирует сигнал S1, поступающий на первый вход блока 19 управления.

Работа головного, среднего и оконечного устройств аналогична описанной работе головного устройства при выполнении циклического сдвига вправо, а работа устройства в режиме одиночной работы аналогична описанной работе устройства в режиме одиночной работы при выполнении циклического сдвига вправо, однако по сигналу S1 в блоке 19 управления с приходом сигнала Р1 вырабатываются сигналы: V8, поступающий на первый управляющий

вход пятого коммутатора 28 и на первый вход первого коммутатора 5, в результате чего происходит передача /(-разрядного слова из регистра 9 и контрольного разряда из блока 35 записи контрольного разряда на соседнее левое устройство; V4, поступающий на второй вход второго коммутатора 6 и на первый управляющий вход шестого коммутатора 32, в результате чего происходит прием /(-разрядного слова и контрольного

О разряда из соседнего правого устройства. Кроме того, по сигналу 1 в блоке 19 управления с приходом сигнала РО вырабатываются сигналы: V6, который поступает на первый вход передающей части первого коммутатора 5 и на пятый вход блока 1 коммутаторов; V2, который поступает на второй вход приемной части второго коммутатора 6 (аналогично и для устройства в режиме одиночной работы).

Покажем осуществление арифметического сдвига влево с заполнением освободившихся разрядов логическим нулем, который задается кодовой комбинацией 011 на входе 26 устройства, или логический сдвиг влево с заполнением освободившихся разрядов логическим нулем, который задается

5 кодовой комбинацией 101 на входе 26 устройства. Дешифратор 3 расшифрует указанные кодовые комбинации и вырабатывает соответственно сигнал S3 или S5.

Работа головного, среднего и оконечного устройств аналогична описанной работе

0 этих устройств при выполнении циклического сдвига влево, работа устройства в режиме одиночной работы аналогична описанной работе этого устройства при выполнении циклического сдвига влево, однако по

г сигналу S3 (или 35) в блоке 19 управления с приходом сигнала Р1 сигнал V4 не вырабатывается, а по сигналу S3 (или S5) в блоке 19 управления с приходом сигнала РО сигнал V2 не вырабатывается.

Теперь рассмотрим работу предлагаемого устройства с точки зрения обнаружения ошибок сдвига.

I. В режиме одиночной работы: 1. При выполнении операций циклического, арифметического и логического сдвига вправо выдвигаемые разряды с выхода

5 третьей группы блока 1 коммутаторов поступают на входы первого сумматора 143 по модулю два блока 36 формирования четности данных, на в.ход третьего сумматора 145 по модулю два которого поступают сдвинутые вправо разряды из выхода первой группы блока 1 коммутаторов. В блоке 36 формирования четности данных при этом формируются соответственно четности РЗ и Р5, которые поступают на первый вход элемента ИЛИ 148 и второй вход сумматора 149 по модулю два блока 40 контроля ошибки, на третий вход сумматора 149 по модулю два которого поступает контрольный разряд Х8 из блока 35 записи

контрольного разряда, а на четвертый вход сумматора 149 по модулю два поступает значение коррекции четности Р6 (в случае выполнения операции арифметического сдвига вправо) из блока 37 коррекции четности, на третий вход элемента И 147 которого поступает сигнал S2 (в случае выполнения арифметического сдвига вправо) из дешифратора 3, а на второй вход элемента И 147 поступает значение знакового разряда ХО из регистра 9, на вход элемента ИЛИ-НЕ 146 блока 37 коррекции четности поступают сигналы НО, Н2, Н4 или Н6 с выхода третьего коммутатора 17 (в случае, если шаг сдвига четный). Предположим, что произошла одиночная ошибка на выходе второй группы блока коммутаторов 1. Тогда эта ошибка будет обнаружена контролем по четности в блоке 40 контроля ошибки путем сравнения контрольного разряда Х8, четности Р5 и значения коррекции четности Р6 (в случае выполнения арифметического сдвига вправо) с значением четности РЗ, в результате чего блок 40 контроля ошибки формирует сигнал «Ошибка, поступаюший на выход 41 ошибки устройства.

В блоке 36 формирования четности данных при этом формируются соответственно четности Р4 и Р5, которые поступают на вторые входы элемента ИЛИ 148 и сумматора 149 блока 40 контроля ошибки. Значение коррекции четности при данных типах сдвига, как и при циклическом сдвиге вправо или логическом сдвиге вправо, будет равно нулю. Дальнейшая работа будет полностью аналогична описанной.

Предположим, что произошла одиночная ошибка на выходе третьей группы блока 1

коммутаторов. Тогда эта ошибка будет обнаружена контролем по четности в блоке 40 контроля ошибки путем сравнения контрольного разряда Х8 и четности Р5 с значением четности Р4, в результате чего блок 40 контроля ошибки формирует сигнал «Ошибка, поступаюший на выход 41 ошибки устройства.

0 блока 1 коммутаторов, эта ошибка будет обнаружена контролем по четности в блоке 40 контроля ошибки путем сравнения четности РЗ (или четности Р4), контрольного разряда Х8 и значения коррекции четности Р6 (в случае выполнения арифметического сдвига вправо) с значением четности Р5, в результате чего блок 40 контроля ошибки формирует сигнал «Ошибка, поступающий на выход 41 ошибки устройства. II. Обнаружение одиночных ошибок сдвига при работе устройства в качестве головного, среднего и оконечного полностью аналогично обнаружению одиночных ошибок сдвига при работе устройства в режиме одиночной работы, как это описано в пп. 1, 2 и 3.

5 Сигнал конца операции, поступающий с четвертого выхода блока 1 коммутаторов на выход 27 устройства, информирует центральное устройство управления (УУ) об окончании процесса сдвига, а сигнал «Ошибка, поступающий с выхода 41 устройства,

информирует центральное УУ об окончании процесса контроля сдвига, после чего центральное УУ имеет возможность приема сдвинутой информации с выхода группы 7 устройства на некоторый регистр. Прием сдвинутой информации осуществляется за время приема Tjg,, после чего в конечный момент времени t центральное УУ снимает свои сигналы на входах устройства. В результате устройство приводится в исходное состояние.

0 Время операции сдвига и контроля сдвига Тадв, которое длится от момента времени 1я.,ло момента времени- U, является переменным, равным Тои,лда.при минимальном шаге сдвига и Тсдвмакс при максимальном (расширенном) шаге сдвига.

/4

От Влама 79

}2 7S

22 0Л30

20 е

21

От f/JOHoS

От f 0. jrOfta/S

VO

КВлана/ 9,23,35

107

ЮЗ У5

НоланаИ

VS IS SJJOMOM

1° V7

i ,OByj ft 32

/f S/jo/taM 5,28

23

75

/

Om 5лона 79

От f /roffci

Огп5ло«а

ftSjmriy 3S

V

/f /

fas. 7

Фиа. 9

urnSffOHff

/7

НО

/

М2

/W

Н6

ХО

От Sjforta 3 gf.

2

я

ff/77 3 . 12

От 36

Л SjroHOf

ге, зг

Р5

ffS/roefy О

/47

Рб ff S offy4O

| Устройство для сдвига информации | 1981 |

|

SU1014031A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-10-30—Публикация

1983-11-16—Подача