Изобретение относится к вычислительной технике и может использоваться при создании быстродействующих операционных систем обработки информации, при непосредственной реализа1ДИИ языков высокого уровня, в системах с диалоговым режимом разработки, отладки и вьтолнения программ, анулирующих системах и аппаратурных интерпретаторах и трансляторах.

Целью изобретения является повьшение достоверности работы при возникновении отказов ячеек памяти.

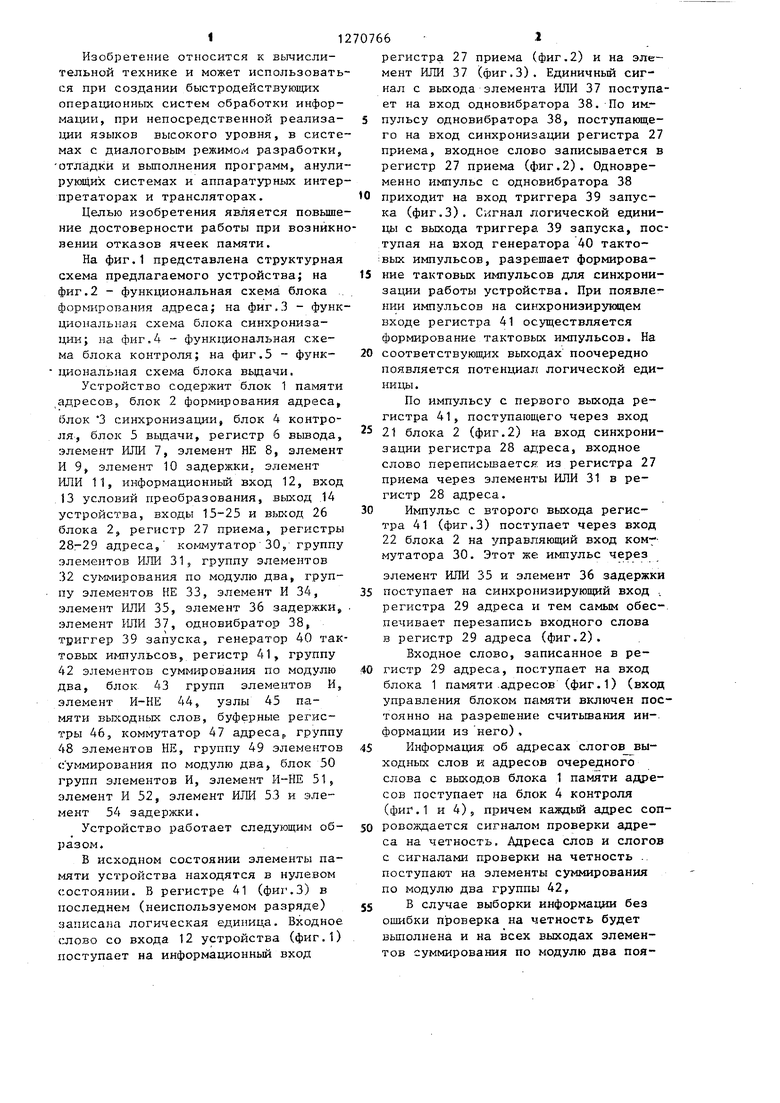

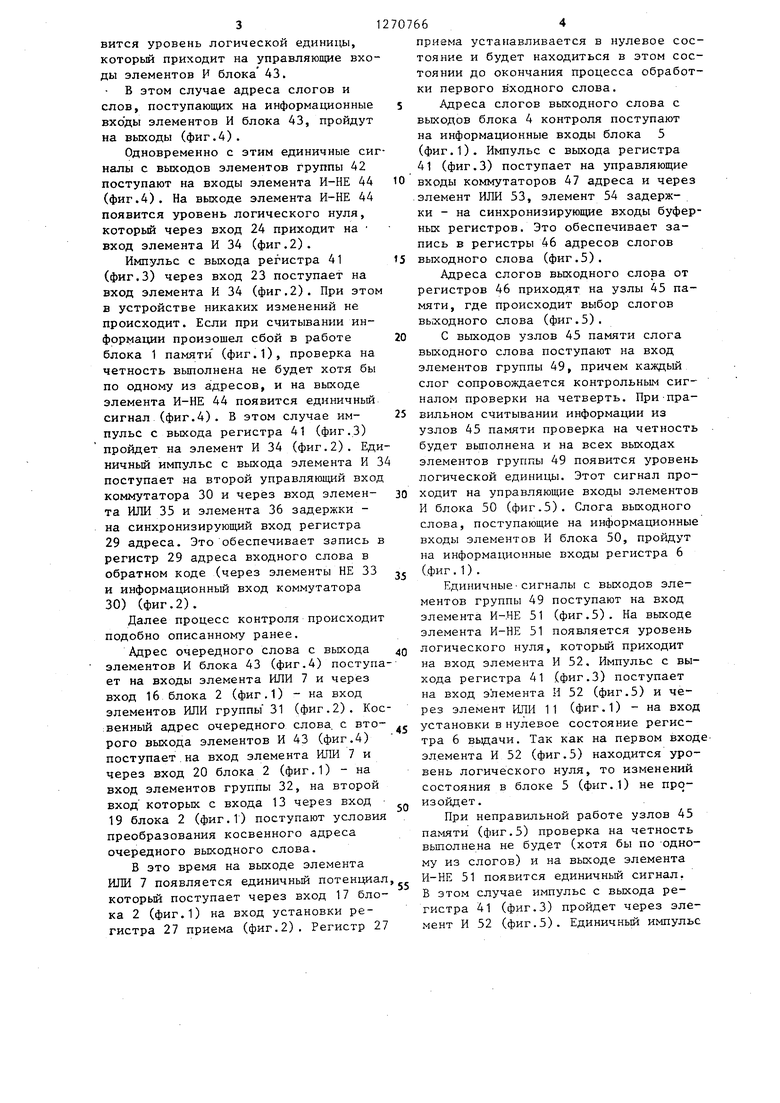

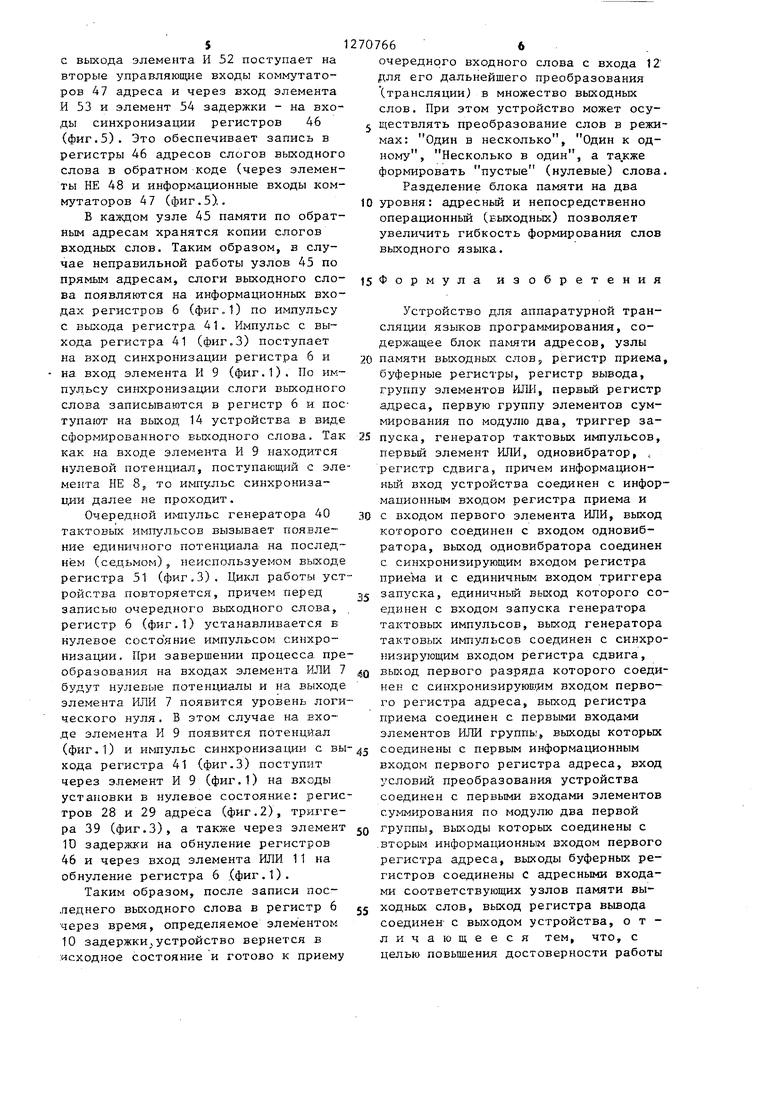

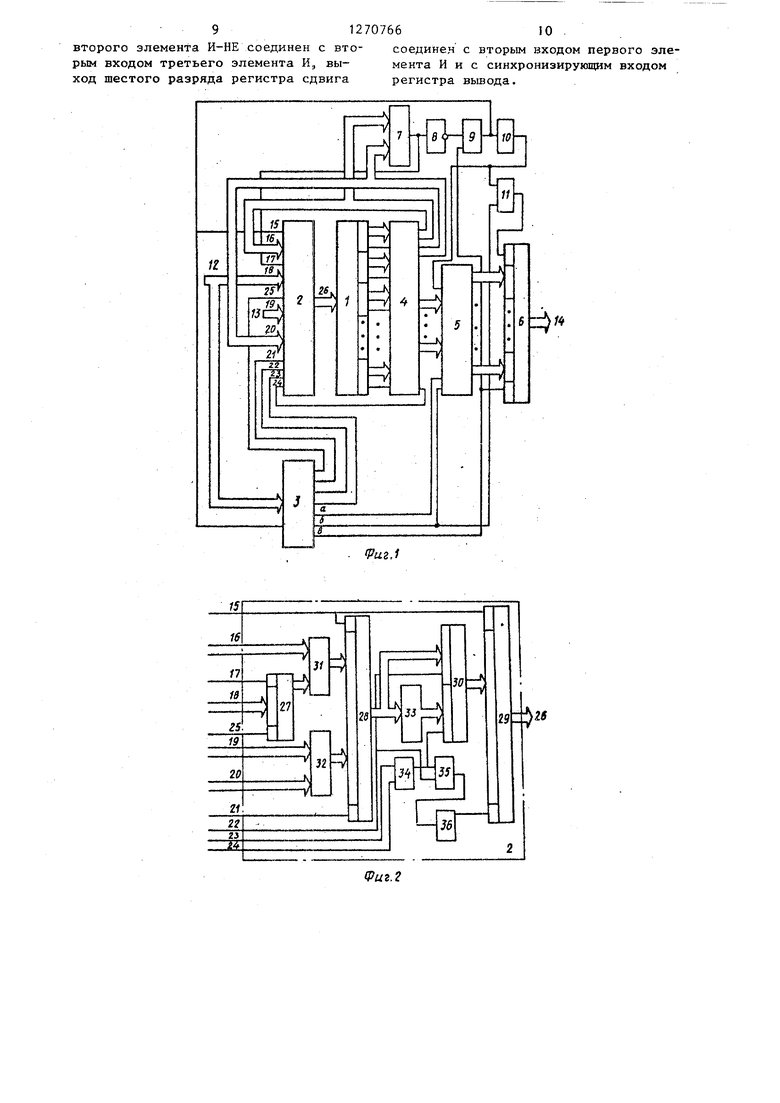

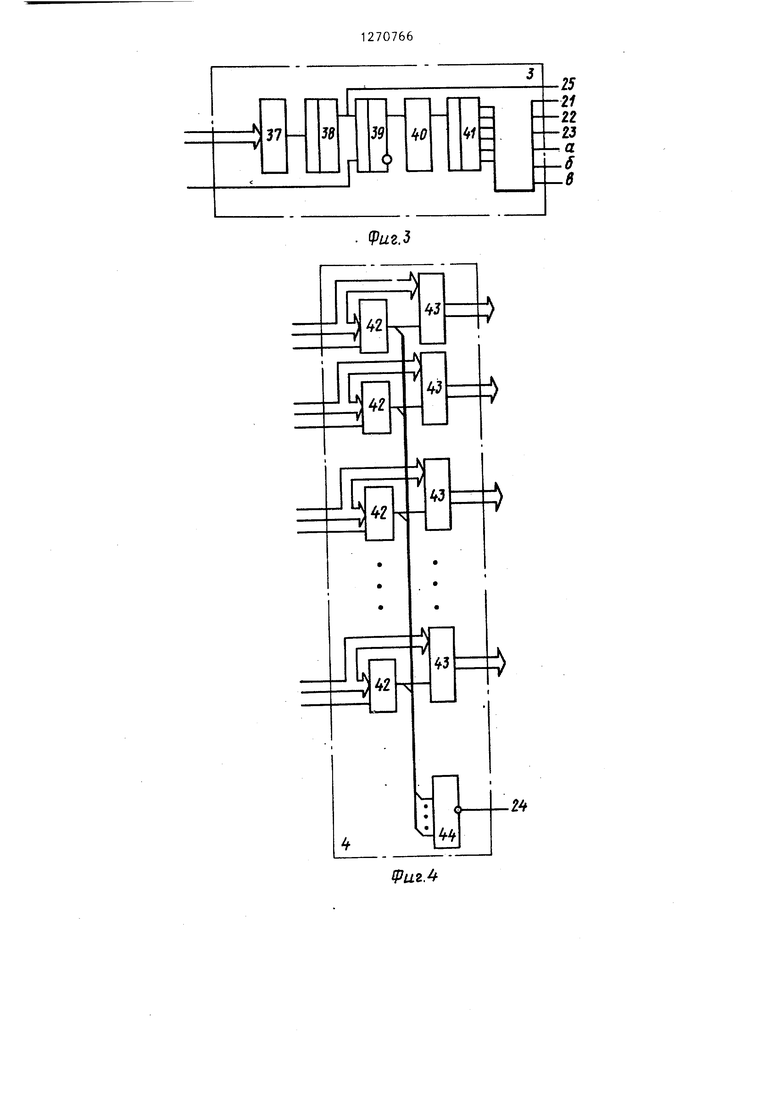

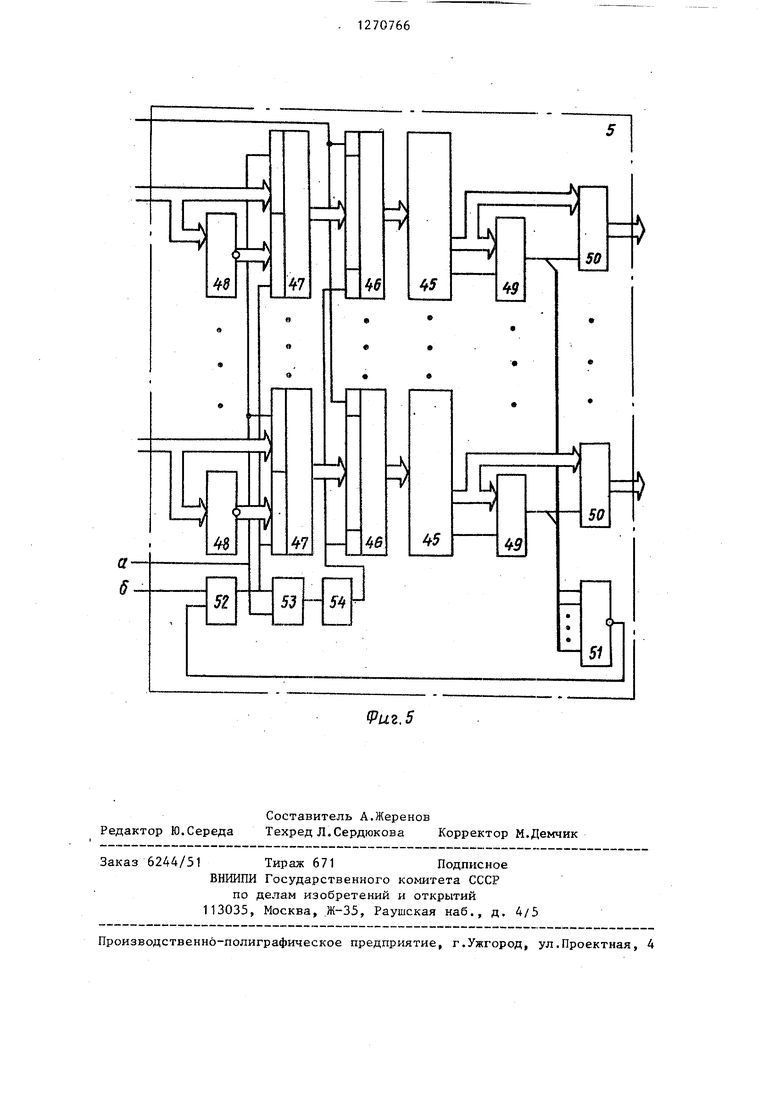

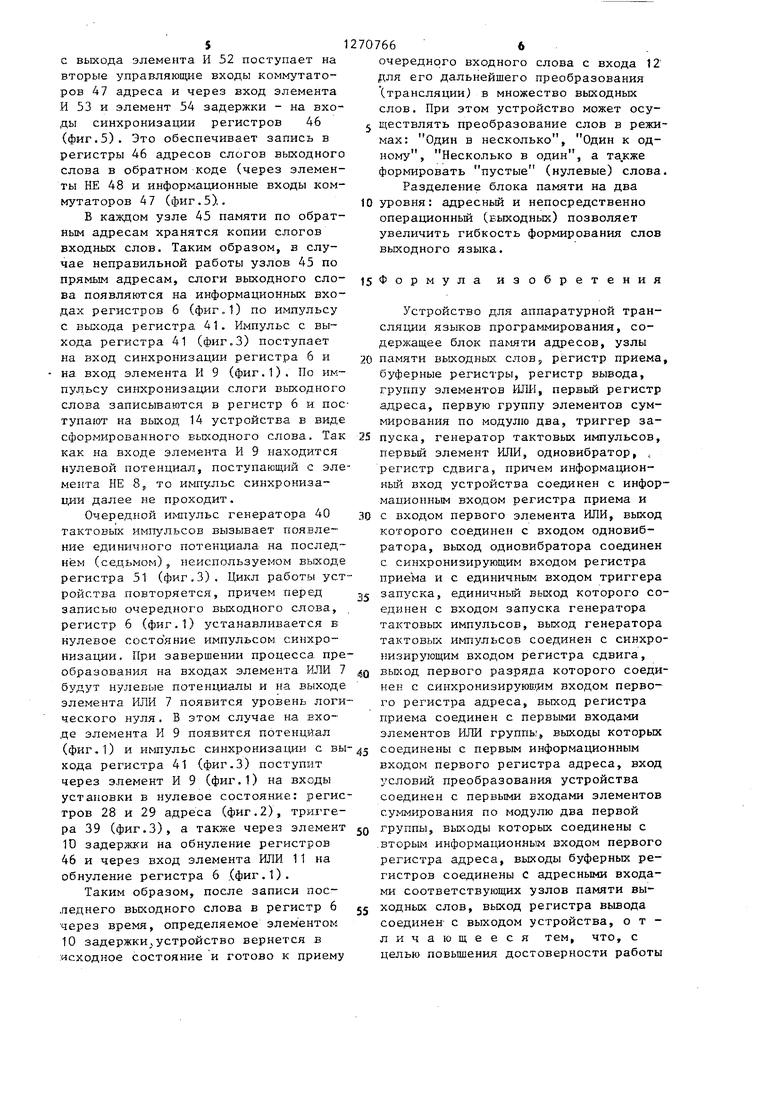

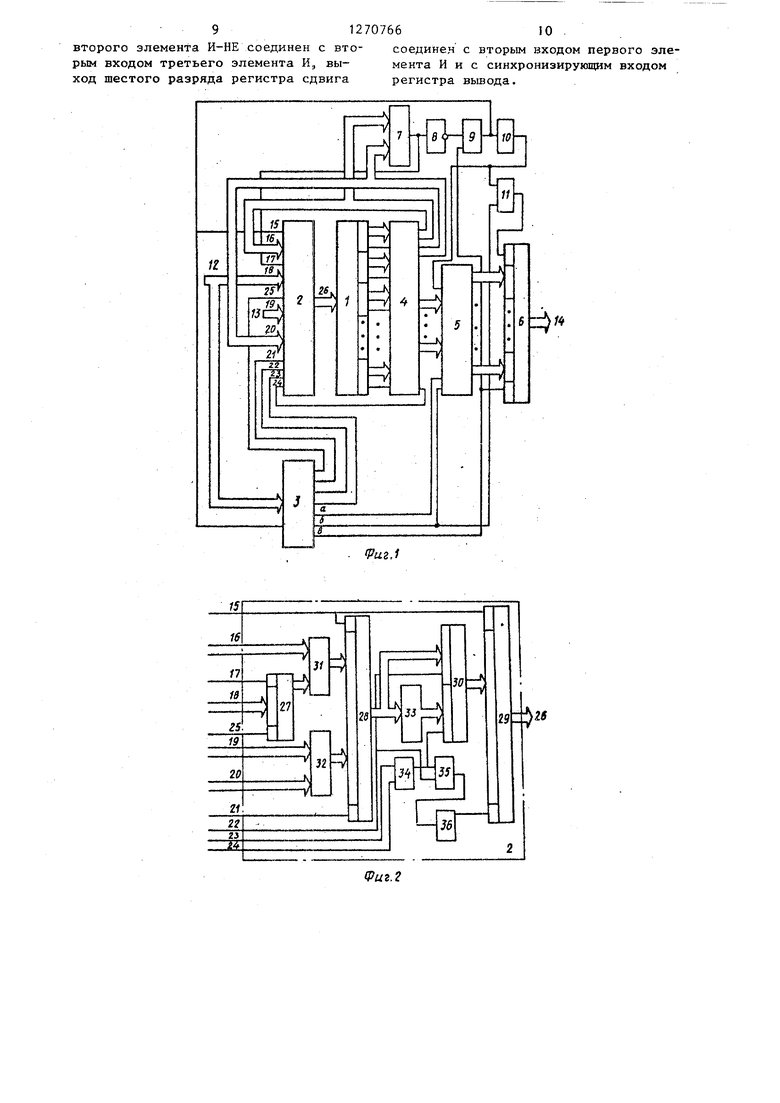

На фиг.1 представлена структурная схема предлагаемого устройства; на фиг.2 - функциональная схема блока форьгарования адреса; на фиг.З - функциональная схема блока синхронизации; иа фиг.4 - функциональная схема блока контроля; на фиг.5 - функ1даональная схема блока выдачи.

Устройство содержит блок 1 па1У1Яти адресов, блок 2 формирования адреса, блок 3 синхронизации, блок 4 контроля, блок 5 вьщачи, регистр 6 вывода, элемент ИЛИ 7, элемент НЕ 8, элемент И 9, элемент 10 задержки, элемент ИЛИ 11, информационный вход 12, вход 13 условий преобразования, выход ,14 устройства, входы 15-25 и выход 26 блока 2, регистр 27 приема, регистры 28-29 адреса, коммутатор30., группу элементов ИЛИ 31s группу элементов 32 суммирования по модулю два, группу элементов НЕ 33, элемент И 34, элемент ИЛИ 35, элемент 36 задер:жки, . элемент 1-ШИ 37, одновибратор 38, триггер 39 запуска, генератор 40 тактовых импульсов, регистр 41, группу 42 элементов суммирования по модулю два, блок 43 групп элементов И, элемент И-НЕ 44, узлы 45 выходных слов, буферные регистры 46, коммутатор 47 адресад, группу 48 элементов НЕ, группу 49 элементов суммирования по модулю два, блок 50 групп элементов И, элемент И-НЕ 51, элемент И 52, элемент ИЛИ 53 и элеент 54 задержки.

Устройство работает следующим обазом,

В исходном состоянии элементы паяти устройства находятся в нулевом состоянии. В регистре 41 (фиг.З) в оследнем (неиспользуемом разряде) написана логическая единица. Входное слово со входа 12 устройства (фиг.1) оступает на информационный вход

регистра 27 приема (фиг.2) и на элемент ИЛИ 37 (фиг.З). Единичный сигнал с выхода элемента ИЛИ 37 поступает на вход одновибратора 38. По им,пульсу одновибратора 38, поступающего на вход синхрониза1;ии регистра 27 приема, входное слово записывается в регистр 27 приема (фиг.2). Одновременно импульс с одновибратора 38

приходит на вход триггера 39 запуска (фиг.З). Сигнал логической единицы с выхода триггера 39 запуска, поступая на вход генератора 40 такто:вых импульсов, разрешает формирование тактовых импульсов для синхронизации работы устройства. При появлении импульсов на синхронизирующем входе регистра 41 осуществляется формирование тактовых импульсов. На

cooтвeтcтвyюш x выходах поочередно появляется потенциал логической единицы .

По импульсу с первого выхода регистра 41, поступающего через вход

21 блока 2 (фиг.2) на вход синхронизации регистра 28 адреса, входное слово переписьшается из регистра 27 приема через элементы ИЛИ 31 в регистр 28 адреса.

Импульс с второго выхода регистра 41 (фиг.З) поступает через вход 22 блока 2 на управляющий вход ком-мутатора 30. Этот же импульс через

элемент ИЛИ 35 и элемент 36 задержки

поступает на синхронизирующий вход . регистра 29 адреса и тем самым обеспечивает перезапись входного слова в регистр 29 адреса (фиг.2).

Входное слово, записанное в регистр 29 адреса, поступает на вход блока 1 памяти .адресов (фиг.1) (вход управления блоком Пс1мяти включен постоянно на разрешение считьшания ий-. формации из него),

Информация об адресах слогов выходных слов и адресов очередного слова с выходов блока 1 памяти адресов поступает на блок 4 контроля (фиг.1 и 4)э причем каждый адрес сопровождается сигналом проверки адреса на четность. Адреса слов и слогов с сигналами проверки на четность . поступаю на элементы суммирования по модулю два группы 42,

В случае выборки информации без ошибки проверка на четность будет вьшолнена и на всех выходах элементов суммирования по модулю два появится уровень логической единицы, который приходит на управляющие вхо ды элементов И блока 43. В этом случае адреса слогов и слов, поступающих на информационные входы элементов И блока 43, пройдут на выходы (фиг.4). Одновременно с этим единичные си налы с выходов элементов группы 42 поступают на входы элемента И-НЕ 44 (фиг.4). На выходе элемента И-НЕ 44 появится уровень логического нуля, который через вход 24 приходит на вход элемента И 34 (фиг.2). Импульс с выхода регистра 41 (фиг.З) через вход 23 поступает на вход элемента И 34 (фиг.2). При этом в устройстве никаких изменений не происходит. Если при считывании информации произошел сбой в работе блока 1 памяти (фиг.1), проверка на четность выполнена не будет хотя бы по одному из адресов, и на выходе элемента И-НЕ 44 появится единичный сигнал (фиг.4). В этом случае импульс с выхода регистра 41 (фиг.З) пройдет на элемент И 34 (фиг.2). Еди ничный импульс с выхода элемента И поступает на второй управляющий вход коммутатора 30 и через вход элемента ИЛИ 35 и элемента 36 задержки на синхронизирующий вход регистра 29 адреса. Это обеспечивает запись в регистр 29 адреса входного слова в обратном коде (через элементы НЕ 33 и информационный вход коммутатора 30) (фиг.2). Далее процесс контроля происходит подобно описанному ранее. Адрес очередного слова с выхода элементов И блока 43 (фиг.4) поступа ет на входы элемента ИЛИ 7 и через вход 16 блока 2 (фиг.1) - на вход элементов ИЛИ группы 31 (фиг.2). Кос : венный адрес очередного слова, с второго выхода элементов И 43 (фиг.4) поступает.на вход элемента ИЛИ 7 и через вход 20 блока 2 (фиг.1) - на вход элементов группы 32, на второй вход которых с входа 13 через вход 19 блока 2 (фиг.1) поступают условия преобразования косвенного адреса очередного выходного слова. Б это время на выходе элемента ИЛИ 7 появляется единичный потенциал которьй поступает через вход 17 бло ка 2 (фиг.1) на вход установки регистра 27 приема (фиг.2). Регистр 2 664 приема устанавливается в нулевое состояние и будет находиться в этом состоянии до окончания процесса обработки первого входного слова. Адреса слогов выходного слова с выходов блока 4 контроля поступают на информационные входы блока 5 (фиг.1). Импульс с выхода регистра 41 (фиг.З) поступает на управляющие входы коммутаторов 47 адреса и через элемент ИЛИ 53, элемент 54 задержки - на синхронизирующие входы буферных регистров. Это обеспечивает запись в регистры 46 адресов слогов выходного слова (фиг.5). Адреса слогов выходного слова от регистров 46 приходят на узлы 45 памяти, где происходит выбор слогов выходного слова (фиг.5). С выходов узлов 45 памяти слога выходного слова поступают на вход элементов группы 49, причем каждый слог сопровождается контрольным сигналом проверки на четверть. При-правильном считывании информации из узлов 45 памяти проверка на четность будет вьшолнена и на всех выходах элементов группы 49 появится уровень логической единицы. Этот сигнал проходит на управляющие входы элементов И блока 50 (фиг.5). Слога выходного слова, поступающие на информационные входы элементов И блока 50, пройдут на информационные входы регистра 6 (фиг.1). Единичные-сигналы с выходов элементов группы 49 поступают на вход элемента И-.ЧЕ 51 (фиг.5). На выходе элемента И-НЕ 51 появляется уровень логического нуля, которьй приходит на вход элемента И 52. Импульс с выхода регистра 41 (фиг.З) поступает на вход элемента И 52 (фиг.5) и через элемент ИЛИ 11 (фиг.1) - на вход установки в нулевое состояние регистра 6 выдачи. Так как на первом входеэлемента И 52 (фиг.5) находится уровень логического нуля, то изменений состояния в блоке 5 (фиг.1) не произойдет. При неправильной работе узлов 45 памяти (фиг.5) проверка на четность вьшолнена не будет (хотя бы по -одному из слогов) и на выходе элемента И-НЕ 51 появится единичный сигнал. Б этом случае импульс с выхода регистра 41 (фиг.З) пройдет через элемент И 52 (фиг.5). Единичньм импульс с выхода элемента И 52 поступает на вторые управляющие входы коммутаторов 47 адреса и через вход элемента И 53 и элемент 54 задержки - на входы синхронизации регистров 46 (фиг.5). Это обеспечивает запись в регистры 46 адресов слогов выходного слова в обратном коде (через элементы НЕ 48 и информахдаонные входы коммутаторов 47 (фиг.5).. В каждом узле 45 памяти по обратным адресам хранятся копии слогов входных слов. Таким образом, з случае неправильной работы узлов 45 по прямым адресам, слоги выходного слова появляются на информационных входах регистров 6 (фиг,1) по импульсу с выхода регистра 41. Импульс с выхода регистра 41 (фиг.З) поступает на вход синхронизации регистра 6 и на вход элемента И 9 (фиг.1). По импульсу синхронизации слоги выходного слова записываются в регистр 6 и пос тупают на выход 14 устройства в виде сформированного выходного слова. Так как на входе элемента И 9 находится нулевой потенциал, поступающий с эле мента НЕ 8, то и шyльc синхронизаи ш далее не проходит. Очередной и яIyльc генератора 40 тактовых импульсов вызывает появление единичного потенциала на последнем (седьмом)5 неиспользуемом выходе регистра 51 (фиг.З). Цикл работы уст ройства повторяется, причем перед записью очередного выходного слова, регистр 6 (фиг.1) устанавливается в нулевое состояние импульсом, синхронизации. При завершении процесс«э. пре образования на входах элемента ИЛИ 7 будут нулевые потенциалы и на выходе элемента ШЛИ 7 появится уровень логи ческого нуля. В этом случае на входе элемента И 9 появится потенциал (фиг.1) и импульс синхронизации с вы хода регистра 41 (фиг.З) поступит через элемент И 9 (фиг.1) на входы установки в нулевое состояние: регис тров 28 и 29 адреса (фиг.2), триггера 39 (фиг.З), а также через элемент 10 задержки на обнуление регистров 46 и через вход элемента ИЛИ 11 на обнуление регистра 6 .(Фиг.1). Таким образом, после записи последнего выходного слова в регистр 6 через время, определяемое элементом 10 задержки,устройство вернется в исходное состояние и готово к приему 7666 очередного входного слова с входа 1Z для его дальнейшего преобразования (трансляции) в множество выходных слов. При этом устройство может осуществлять преобразование слов в режимах: Один в несколько, Один к i rfTJU ТЗ tlftl/ ТЛ/ fT t ТУ-j-ч ному, Несколько в один, а та,кже формировать пустые (нулевые) слова. Разделение блока памяти на два уровня: адресный и непосредственно операциоиньм (выходных) позволяет увеличить гибкость формирования слов выходного языка. Формула изобретения 5стройство для аппаратурной трансляции языков программирования, содержащее блок памяти адресов, узлы памяти выходных; слов, регистр приема, буферные регистры, регистр вывода, группу элементов Ш1К, первьш регистр адреса, первую группу элементов суммирования по модулю два, триггер запуска, генератор тактовых импульсов, первый элемент ИЛИ, одновибратор, , регистр сдвига, причем информационньш вход устройства соединен с информационным входом регистра приема и с входом первого элемента ИЛИ, выход которого соединен с входом одновибратора, выход одновибратора соединен с синхронизирующим входом регистра приема и с единичным: входом триггера запуска, единичньй выход которого соединен с входом запуска генератора тактовых импульсов, выход генератора тактовых импульсов соединен с синхронизирующим входом регистра сдвига, выход первого разряда которого соединен с синхронизируюв-гим входом первого регистра адреса, выход регистра приема соединен с первыми входами элементов ИЛИ группы, выходы которых соединены с первым информационным входом первого регистра адреса, вход условий преобразования устройства соединен с первыми входами элементов суммирования по модулю два первой группы, выходы которых соединены с вторым информационным входом первого регистра адреса, выходы буферных регистров соединены с адресными входами соответствующих узлов памяти выходных слов, выход регистра вьшода соединен с выходом устройства, отличающееся тем, что, с целью повьшения достоверности работы

при возникновении отказов ячеек памяти, в него введены второй регистр адреса, коммутатор группы элементов НЕ, коммутаторы адреса, вторая и третья группы элементов суммирования по модулю два, два блока групп элементов И, первьй и второй элементы И-НЕ, второй, третий, четвертый и пятый элементы ИЛИ, первый, второй, и третий элементы И, первый, второй и : третий элементы задержки, элемент НЕ причем выход первого регистра адреса соединен с первым информационным входом коммутатора и входами элементов НЕ группы, выходы которых соединены с вторым информационным входом коммутатора, выход коммутатора соединен с информационным входом второго регистра адреса, выход которого соединен с адресным входом блока памяти адресов, i-й информационный выход i-й ячейки (i 1,п+ 2) блока памяти адресов соединен с группой входов соответствующего элемента суммирования по модулю два второй группы и первыми входами элементов И первого блока, выход элементов И первой группы первого блока соединен соответственно с первым входом второго элемента ИЛИ и вторыми входами элементов ИЛИ группы, выход элементов И второй группы первого блока соединен соответственно с вторым входом втоporja элемента ИЛИ и с вторыми входами элементов суммирования по модулю два первой группы, выход элементов И j-й группы (J 3, п + 2) первого блока соединен с первым информационным входом соответствующего коммутатора адреса и входами соответствующих элементов НЕ группы, выходы которых соединены с вторым и 1формационным входом соответствующего коммутатора адреса, выход которого соединен с информационным входом, соответствующего буферного регистра, выходы узлов памяти выходных слов соединены с первыми входами соответствующих элементов суммирования по модулю два третьей группы и первыми входами соответствующих элементов И второго блока, выходы которых соединены с информационными входами регистра вывода, выход второго элемента ИЛИ соединен с входом установки регистра приема и с входом элемента НЕ выход которого соединен с первым входом первого элемента И, выход первого элемента И соединен с входом первого элемента задержки, входами установки первого и второго регистров адреса и с нулевым входом триггера запуска, выход первого элемента задержки соединен с первым входом третьего элемента ИЛИ и с входом установки буферных регистров, выход третьего элемента ИЛИ соединен с входом установки регистра вьшода,. выход второго разряда регистра сдвига соединен с первым управляющим входом

коммутатора и с первым входом четвертого элемента ИЛИ, выход которого соединен с входом второго элемента задержки, выход второго элемента задержки соединен с синхронизирующим входом второго регистра адреса, выход третьего разряда регистра сдвига соединен с первым входом второго элемента И, выход которого соединен с вторым управляющим входом коммутатора и с вторым входом четвертого элемента ИЛИ, выход признака четности i-й ячейки (i 1, п + 2) блока памяти адресов соединен с управляющим входом соответствующего элемента

г

суммирования по модулю два второй группы, выходы элементов суммирования по модулю два второй группы соединены соответственно с вторыми входами элементов И первого блока и с входами первого элемента И-НЕ, выход которого соединен с вторым входом второго элемента И, выход четвертого разряда регистра сдвига соединен с первым входом пятого элемента ИЛИ и с первыми управляющими входами коммутаторов адреса, выход пятого разряда регистра сдвига соединен с вторым входом третьего элемента ИЛИ и с первым входом третьего элемента И, выход которого соединен с вторыми управляющими входами коммутаторов адреса и с вторым входом пятого элемента ИЛИ, выход пятого элемента ИЛИ соединен с входом третьего элемента задержки, выход которого соединен с синхронизирующими входами буферных

регистров, выходы признака четности узлов памяти выходных слов соединены с вторыми входами соответствующих элементов суммирования по модулю два третьей группы, выходы которых соединены соответственно с вторыми входами элементов И второго блока и с входами второго элемента И-НЕ, выход

9127076610 .

второго элемента И-НЕ соединен с вто- соединея с вторым входом первого элерым входом третьего элемента И,, вы- мента И и с синхронизирующим входом ход шестого разряда регистра сдвига регистра вывода.

/г

26

22

тЖ

. (puz.S

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1985 |

|

SU1319029A1 |

| Микропрограммный процессор | 1986 |

|

SU1365091A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Устройство для преобразования кодов с одного языка на другой | 1984 |

|

SU1238104A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

| Система передачи и приема информации с коррекцией ошибок | 1985 |

|

SU1311036A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Устройство для формирования периодических функций | 1987 |

|

SU1441391A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для формирования тестов | 1990 |

|

SU1800458A1 |

Изобретение относится к вычислительной технике. Целью изобретения является повьппение достоверности работы при возникновении отказов ячеек памяти. Это достигается за счет формирования выходных слов-дубликатов при возникновении отказов ячеек памя ти. Каждое слово в памяти (адресного и .операционного уровней) записано дважды: по прямому коду, а дубль (копия) этого слова записан по обратному (инверсному) коду. Считанные коды адреса и слогов выходного слова контролируются на четность и в случае обнаружения ошибки в одном (или нескольких слогах) происходит его замещение дублем. Устройство содержит блок памяти адресов, узлы памяти выходных слов, регистр приема, буферные регистры для хранения адресов, регистр вывода, два регистра адреса, три группы элементов суммы по модулю два, одновибратор для подключения триггера запуска, осуществляющего S пуск генератора тактовых импульсов, регистр сдвига для формирования син(Л С хронизирующих импульсов, коммутаторы адреса, группы элементов И, ИЛИ, элементы И, ИЛИ, НЕ, И-НЕ, элементы задержки . 5 ил.

fpLLZ.

iPuz,5

| Устройство для преобразования кодов с одного языка на другой | 1978 |

|

SU780011A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для преобразования кодов с одного языка на другой | 1983 |

|

SU1136183A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-15—Публикация

1985-02-11—Подача