Изобретение относится к вычислительной технике и может быть исполь зовано для контроля элементов и цепей выработки управляющих сигналов в различных устройствах цифровйх вычисли-, тельных машин и других дискретных автоматов.

Известно устройство для контроля микропрограммного автомата, содержащее два элемента И, элемент Ш1И, триггер и линию задержки. Это устройство обнаруживает отсутствие сигнала на. выходе контролируемого /автомата Г1 Однако это устройство предназначено для контроля автоматов, у которых каждый момент времени сигнал появляется только на одном из выходов. . .

Наиболее близким к изобретению техническим решением является устройство для контроля цепей управления операцишли, coдepжaщef два регистра, схему функции ошибки,элемент задержки и элементы И и ИЛИ.

Б известном устройстве выработка устройством управления заданных наборов сигналов контролируется путем сравнения контролируемых наборов с некоторыми этсшонными наборами L2j.

Однако известное устройство сложно и малонадежно. Кроме того,оно не обеспечивает обнаружение ошибок, связанных с выработкой одним и тем же элементом двух последовательных сигналов, один из которых является ложным. Кроме того, в известном устройстве имеется линия задержки на время выполнения каждой из контроли10руемых операций для установки в соответствующее состояние разрядов второго регистра. Следовательно, возни; кает необходимость построения линий задержки для каждой операции, так

15 как время их выполнения и наборы управлякяцих сигналов различны. На .построение таких линий задержки при большом наборе контролируемых операций (в современных ЭВМ SOrlOO операций)

20 будет затрачено до 50% оборудования всего устройства контроля.

Контролируемые сигналы поступают через группу элементов ИЛИ на вход

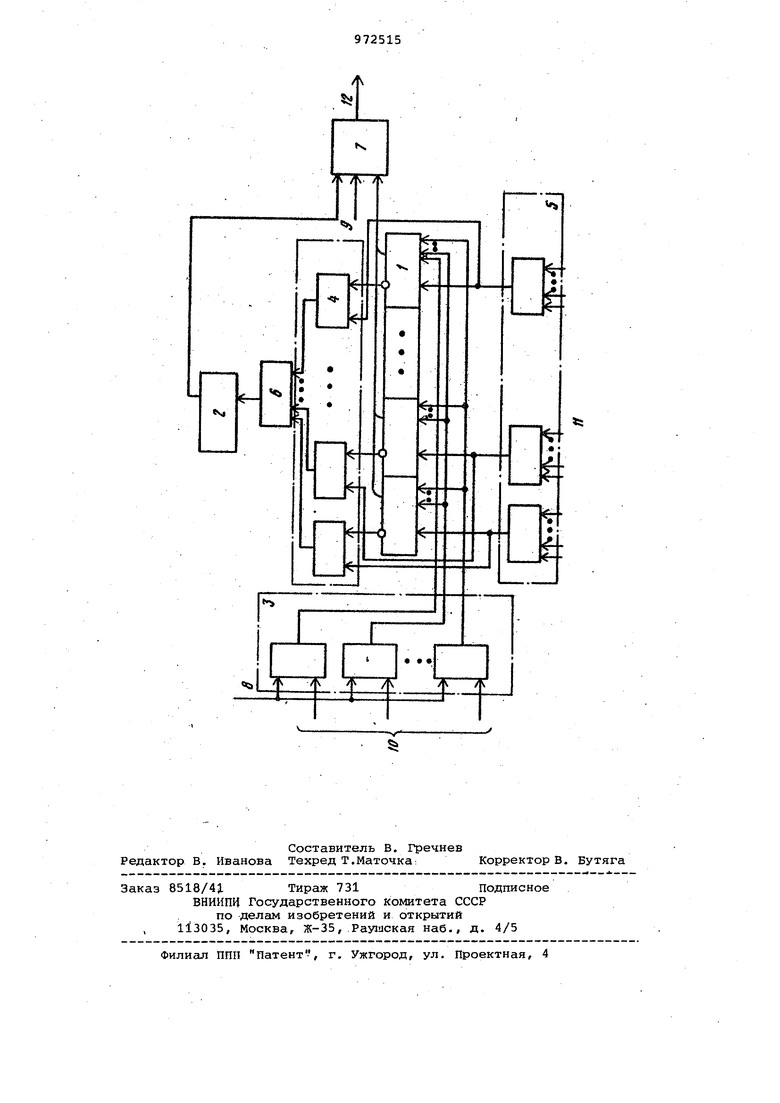

25 установки в нуль соответетвукядих разрядов регистра и через вторую группу элементов и, и элемент. ИЛИ. на вход установки в единицу триггера контроля. На вторые входы элементов И второй группу поступают. сигналы с нулевых выходов соответствующих разрядов регистра. Запись этгшонного кода в регистр производится с элементов И первой группы, первые входы которых соединены группой входов шин операций, вторые - с входом записи эталонных кодов. Единичные выходы регистра и триггера соединены с узлом фиксации ошибки. Триггер контроля обеспечивает контроль появления ложных сигналов управления. Цель изобретения - расширение функциональных возможностей устройства путем обнаружения двойных сигналов, из которых один ложный, и упрощение устройства. Поставленная цель достигается тем, что в устройство, содержащее р гистр, первую группу элементов И, группу элементов ИЛИ и узел фиксации ошибки, причем первые входы эле ментов И первой труппы являются группой входов кодов операций устройства, вход записи эталонных кодо устройства соединен с вторыми входа ми элементов И первой группы, выход которых соединены с единичными входами триггеров регистра, нулевые вх ды которых соединены с выходами соо ветствующих элементов ИЛИ группы, входы которых подключены к выходам контролируемого устройстваj единичные выходы триггеров регистра-соеди нены с группой входов узла фиксации ошибки, выход которого является выходом устройства, а первый вход опрашивающим входом устройства, введены вторая группа элементов И; элемент ИЛИ и триггер контроля, при чем второй вход узла фиксации . ошибк соединен с единичным выходом тригге ра контроля, единичный вход которог соединен с выходом элемента ИЛИ, входы которого соединены с выходами элементов И второй группы, первые входы которых соединены с нулевыми выходами соответствующих триггеров регистра, а вторые входы - соединены с выходами соответствующих элементов ИЛИ группы. На чертеже приведена блоктсхема устройства для,контроля цепей управления операциями. Устройство содержит регистр 1, триггер 2 контроля, первую группу элементов И, вторую группу 4 элеме тов И, группу 5 элементов ИЛИ, эле мент ИЛИ б, узел 7 фиксации ошибки вход 8 записи эталонных кодов, опрашивающий вход 9, группу 10 входо кодов операций, rpyhny входов 11, выход 12 устройства. Входы установки в единицу разряд регистра 1 объединены в определенн комбинациях в группу в соответстви с управляющими сигналами, вырабатываемыми при выполнении операций. Каждая группа подключена к одному из элементов И первойгруппы 3, управляемь:х сигналами операций с группы входов 10. Входы установки в нулб .регистра 1 подключены к выходам элементов ИЛИ группы 5, На входы которых поступают контролируемые сигналы из блока управления операциями. Единичные выходы-регистра 1 подключены к группе входов узла 7 фиксации ошибки. Вход установки в единицу триггера 2 контроля соединен с выходом элемента ИЛИ б, на вход которого поступают сигналы с элементов И второй группы 4. На вторые входы элементов И второй группы 4 поступают сигналы с выходом соответствующих элементов ИЛИ группы 5, а на первые - с нуле- . вых выходов соответствующих разрядов регистра ,1. Узел 7 фиксации ошибки может быть выполнен в виде группы двухвходовых элементов И, первые входы которых соединены с опрашивающим входом 9, а вторые входы - соединены с единичными выходами триггеров регистра 1 и триггера 2 контроля. Выходы элементов И группы соединены с элементом ИЛИ, выход которого является выходом узла 7 фиксации ошибки. Сигнал ошибки будет формироваться на выходе 12, если к моменту появления сигнала на .опрашивающем входе 9 хотя бы один из триггеров, соединенных с узлом 7 фиксации ошибки, будет находиться в единичном состоянии. Перед началом выполнения каждой из операций, регистр 1 и триггер 2 контроля устанавливаются в нулевое : состояние. После-расшифровки кода .1 очередной операции сигнал операции подается на первый вход одного из элементов И первой группы 3. Одновременно подается сигнал через вход в записи эталонного кода, на вторые входы элементов И первой группы 3 и контрольный эталонный код заносится в регистр 1. При выполнении операции контролируемые сигналы поступают : на входы соответствующих разрядов регистра 1, установленные ранее в единицу сигналом с выхода одного из элементов И первой группы 3, устанавливая их в нуль. Кроме того, управляющие сигналы поступают на элементы И второй группы. 4. Сигналов на этих эле,ментов выходах не будет, так как на нулевых выходах соответствующих разрядов регистра 1 будут сигналы, соответствующие коду 0. При правиль-. ном функционировании цепей управления операциями регистр 1 к концу операции фиксирует нулевой код, и триггер 2 контроля находится в нулевом состоянии.

В том случае, если один из конт- poлиpye ыx сигналов не будет выработан схемой управления, в соответствющем раэр.чде регистра 1 после выполнения операции зафиксируется код единицы, который поступает на узел фиксации ошибки, при опросе которой по oпpaluивaюttte fy входу 9 вырабатывается сигнал ошибки на выходе 12.

Таким образом, отсутствие управлющего сигнёша определяется по окончании выполнения операции.

Работа схемы при вь аботкег ложного управляющего сигнала происходит следующим образом.

Так как соответствуюпщй разряд регистра 1 находится в нулевом состоянии, то сигнал с его нулевого выхода открывает соответствующий элмент И второй группы 4. Ложный управляющий сигнал, поступающий на соответствующий вход установки в нуль соответствующего разряда регис ра 1, не изменяет его состояния, но проходит через элементы И второй группы 4 и элемент ИЛИ 6 и устанав-ливает триггер 2 контроля в единичное состояние. Сигнал с единичного выхода триггера 2 контроля поступает на второй вход узла фиксации ошибки, которая вырабатывает сигнал оищбки на выходе 12. Следовательно, выработка ложного управляющего сигнала обнаруживается сразу же при его возникновении.

Работа схемы при поступлении ложного сигнала по одной и той же цепи после выработки истинного сигнала управления происходит следуюощм образом. Первый контролируемый сигнал переводит соответствующий разряд регистра 1 в нулевое состояние, в дальнейшем обнаружение ложного сигнала происходит так же, как указывалось вьвце.

Таким образом, предлагаемое устройство позволяет упростить процесс обнаружения ошибки в цепях упоавления операциями.

Формула изобретения

Устройство для контроля блоков управления операциями, содержащее регистр, первую группу элементов И, группу элементов ИЛИ и узел фиксации ошибки, причем первые входы элементов И первой группы являются группой входов кодов операций устройства, вход записи эталонных кодов уст0ройства соединен с вторыми входами всех элементов И первой группы, выходф 1 которых соединены с единичными входами триггеров регистра, нулевые входы которых соединены с выхода1«в1 соответствующих элементов ИЛИ груп5пы, входы которых подключены к выходам контролируемого устройства, единичные выходы триггеров регистра соединены с группой входов узла фиксации сапибки, выход которого является

0 выходом устройства, а первый вход опрашивающим входом устройства, отличающееся тем, что, с целью, расширения функциональных возможностей устройства путетк обна5ружения ДВОЙНЫХ сигналов, один из которых ложный, и упрощения устройства, в него введены вторая группа элементов И, эле1«юнт ИЛИ и триггер контроля, причем второй вход узла

0 фиксации ашкбкп соединен с еяиничньм выходе триггера контроля, единичный вход которого соединен с выходом элемента ИЛИ, входы которого соединены с выходами элементов И второй

5 группы, первые входы которых соединены с нулевыми выходами соответствукяцих триггеров регистра, а вторые входы соединены с выходами соответствующих элементов ИЛИ ГРУППЫ.

0

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 391563, кл. G Об F 11/02, 1969.

2.Автс ское свидетельство СССР

5 401998, кл. G 06 F 11/00, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цепей управления операциями | 1982 |

|

SU1088001A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Устройство для контроля схем управления | 1984 |

|

SU1252785A1 |

| Устройство для автоматического контроля блоков | 1984 |

|

SU1179348A1 |

| Устройство для регистрации гальванических связей | 1979 |

|

SU860083A1 |

| Устройство для контроля управляющих сигналов микропроцессора | 1989 |

|

SU1656536A1 |

| Устройство для контроля монтажа | 1986 |

|

SU1312616A1 |

| Устройство для контроля | 1986 |

|

SU1396145A2 |

| Устройство для контроля срабатывания клавиш наборного поля | 1985 |

|

SU1297050A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

Авторы

Даты

1982-11-07—Публикация

1980-12-17—Подача