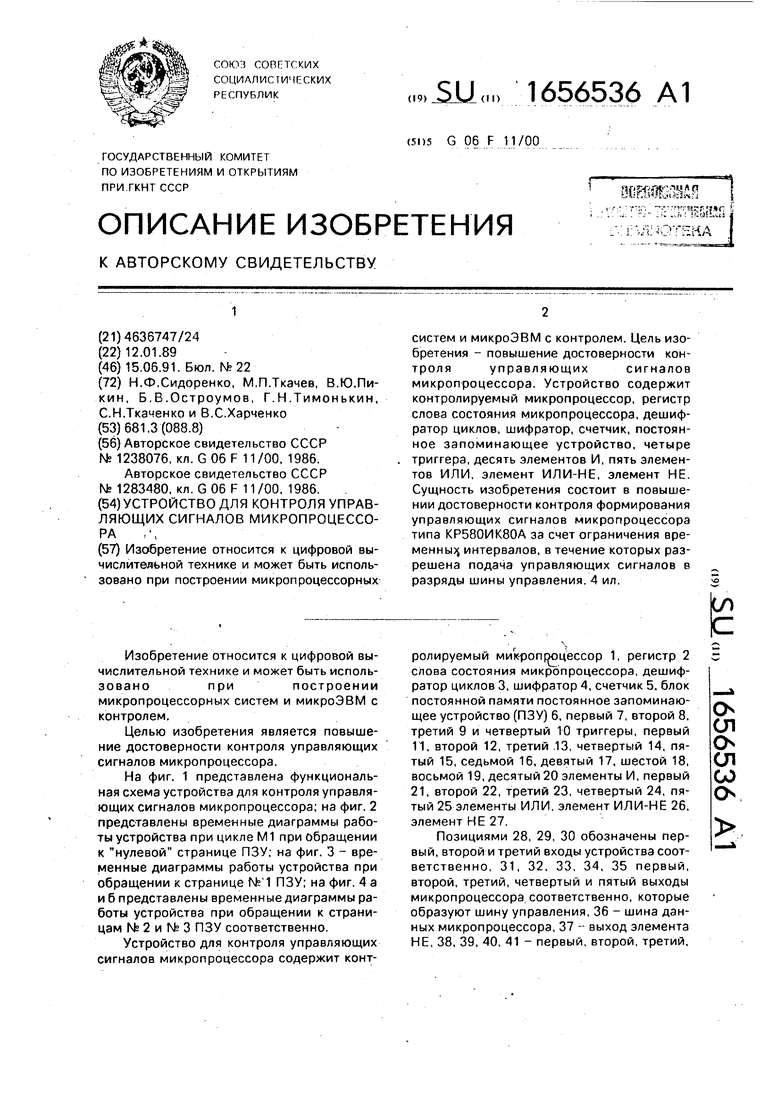

Изобретение относится к цифровой вычислительной технике и может быть использованоприпостроениимикропроцессорных систем и микроЭВМ с контролем.

Целью изобретения является повышение достоверности контроля управляющих сигналов микропроцессора.

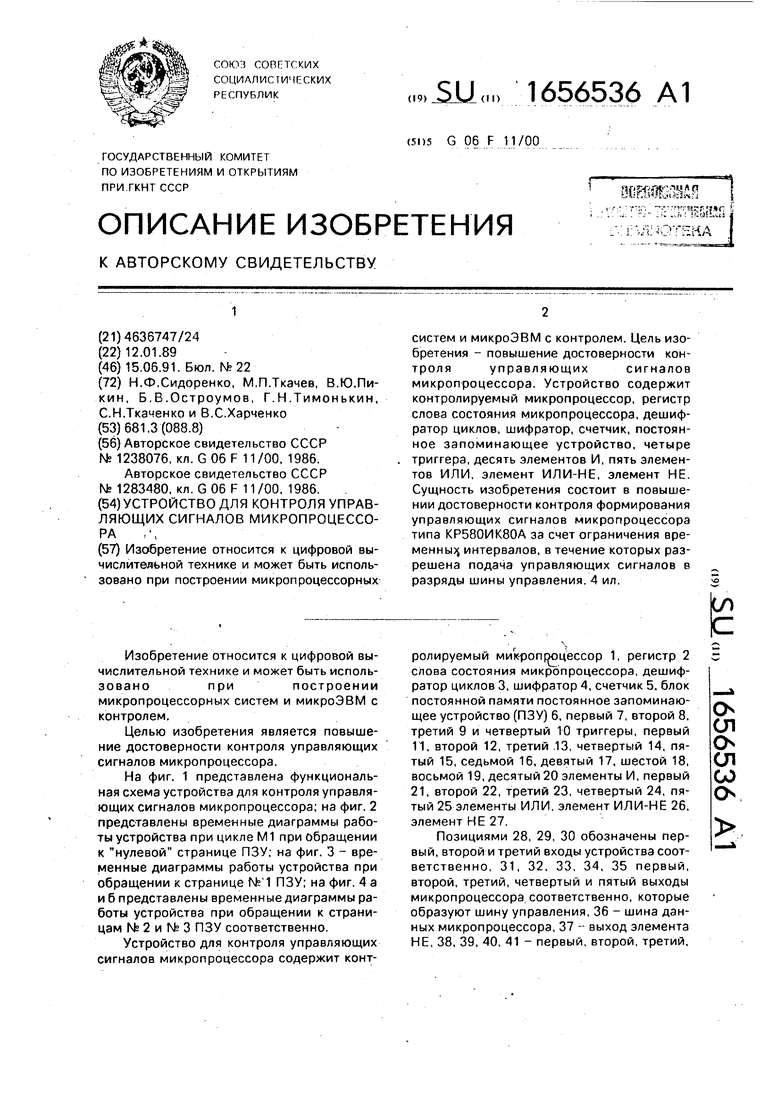

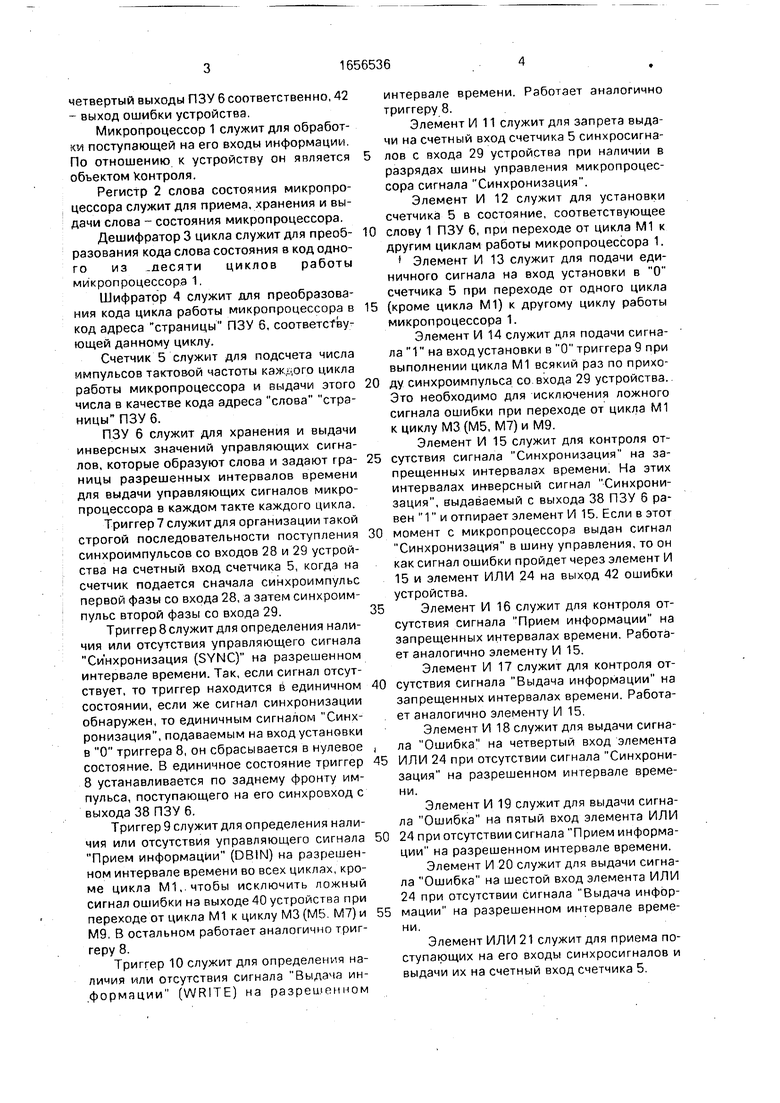

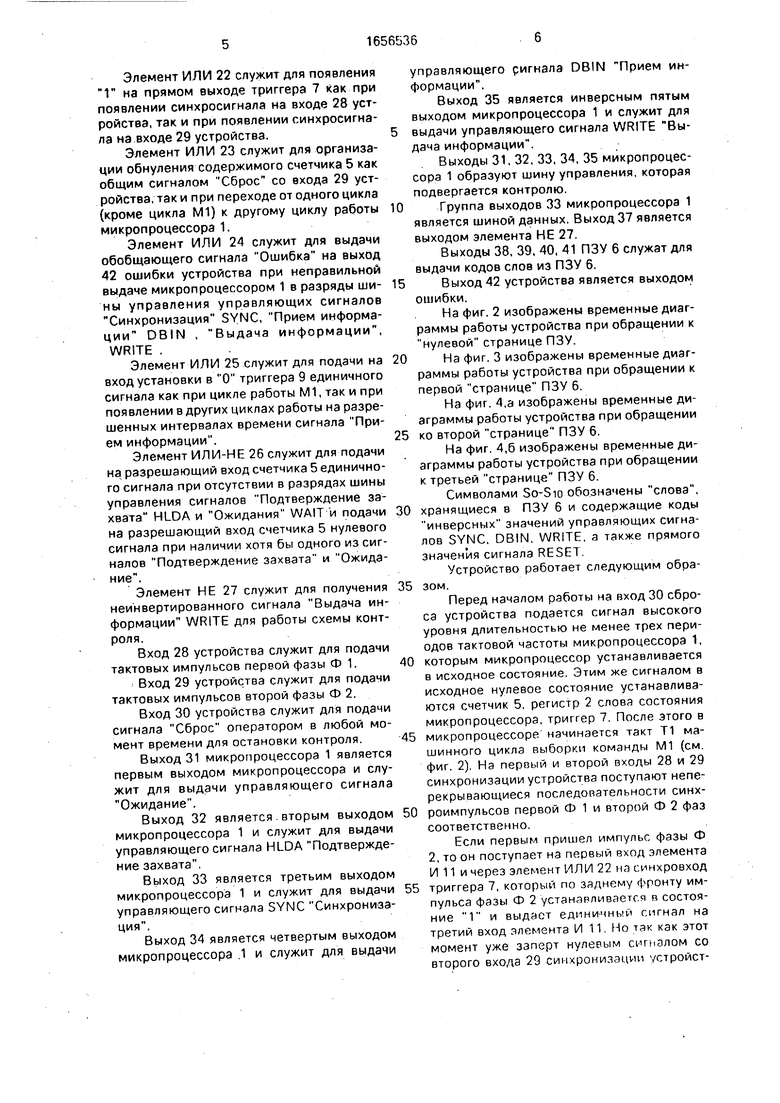

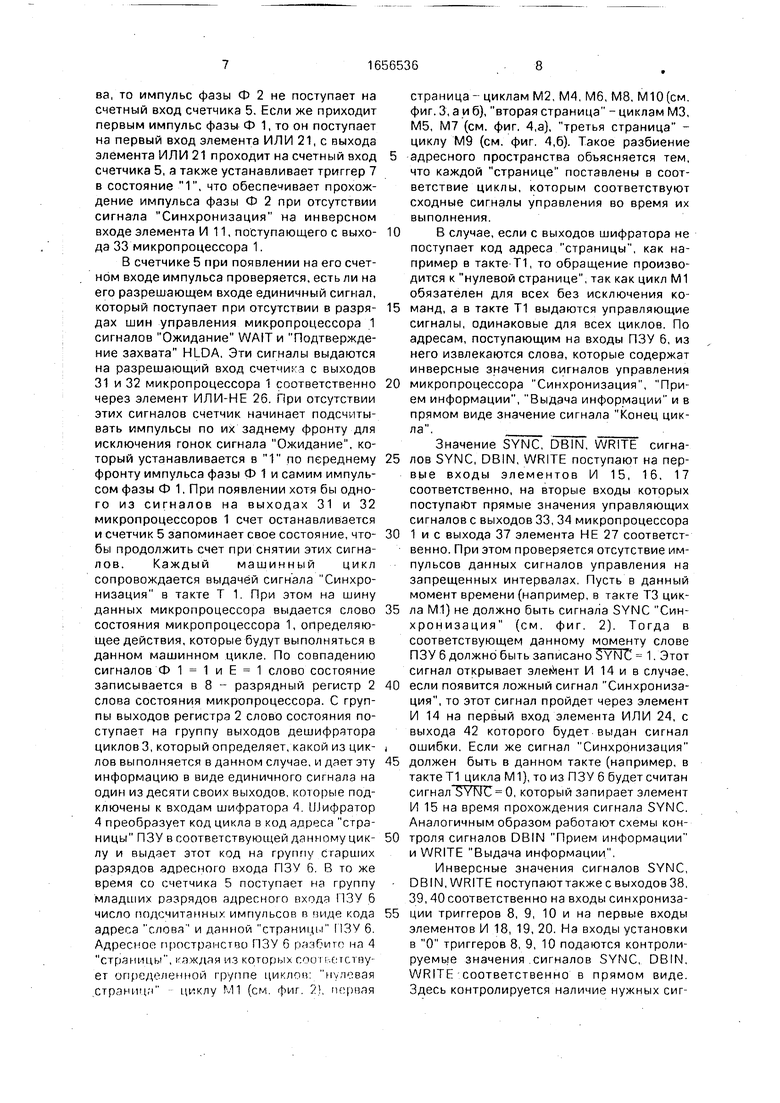

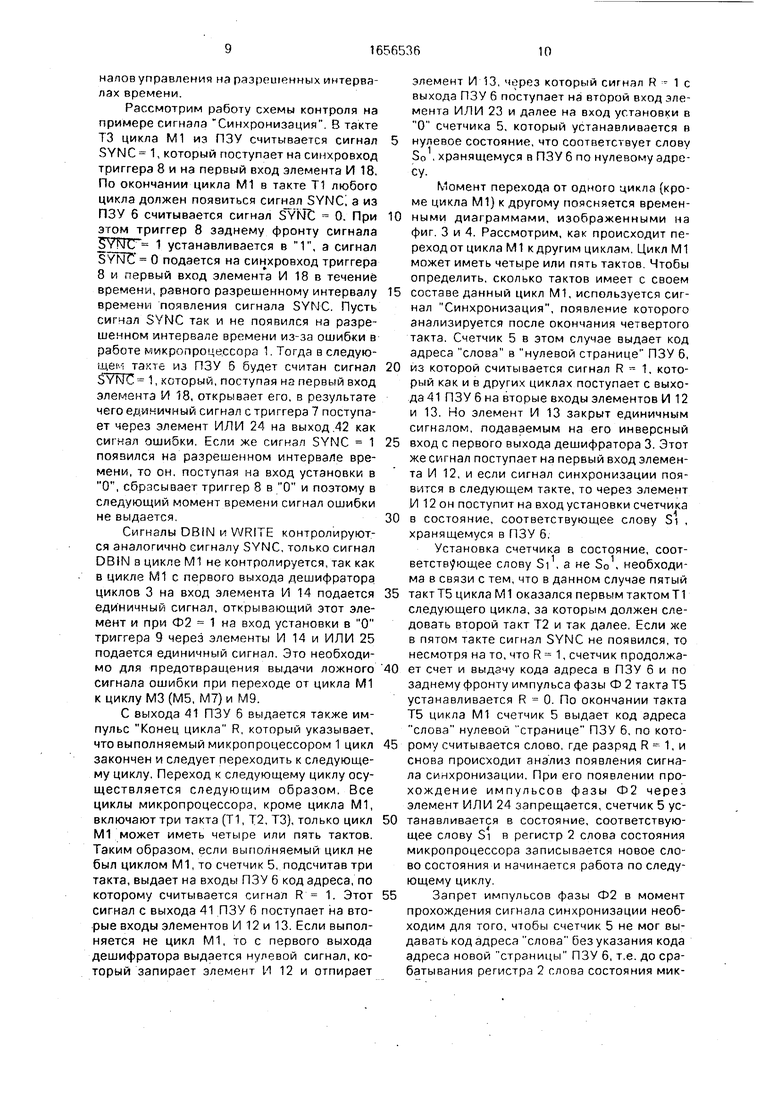

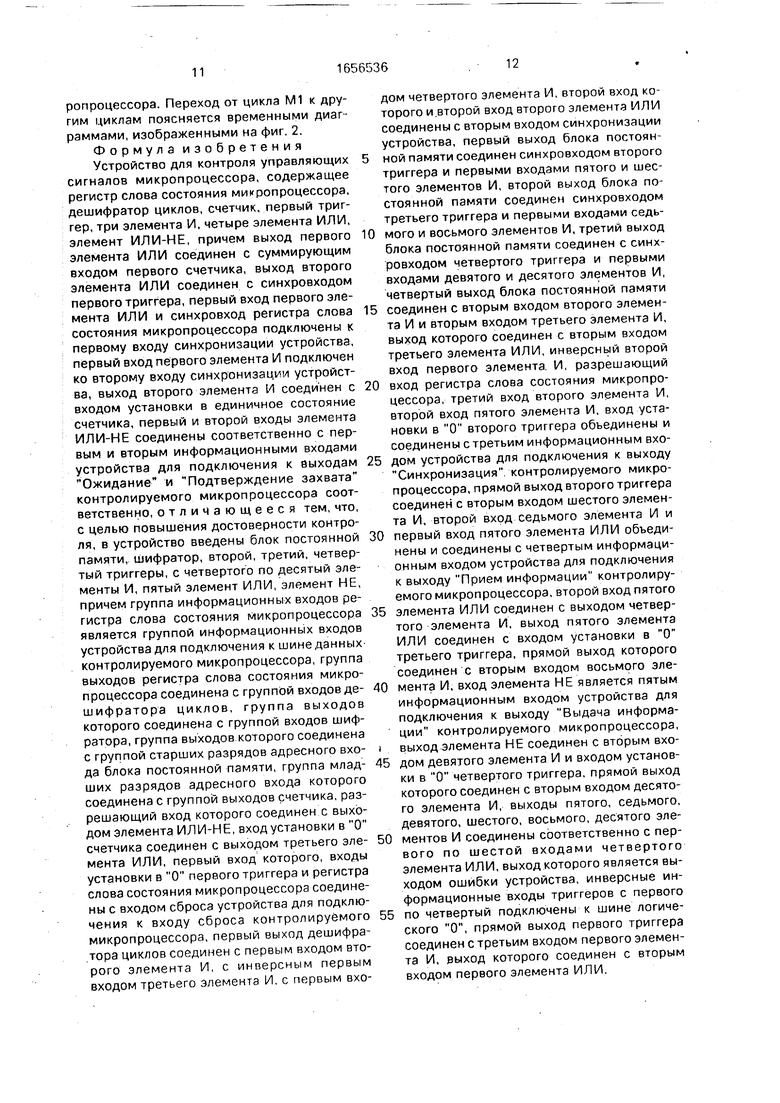

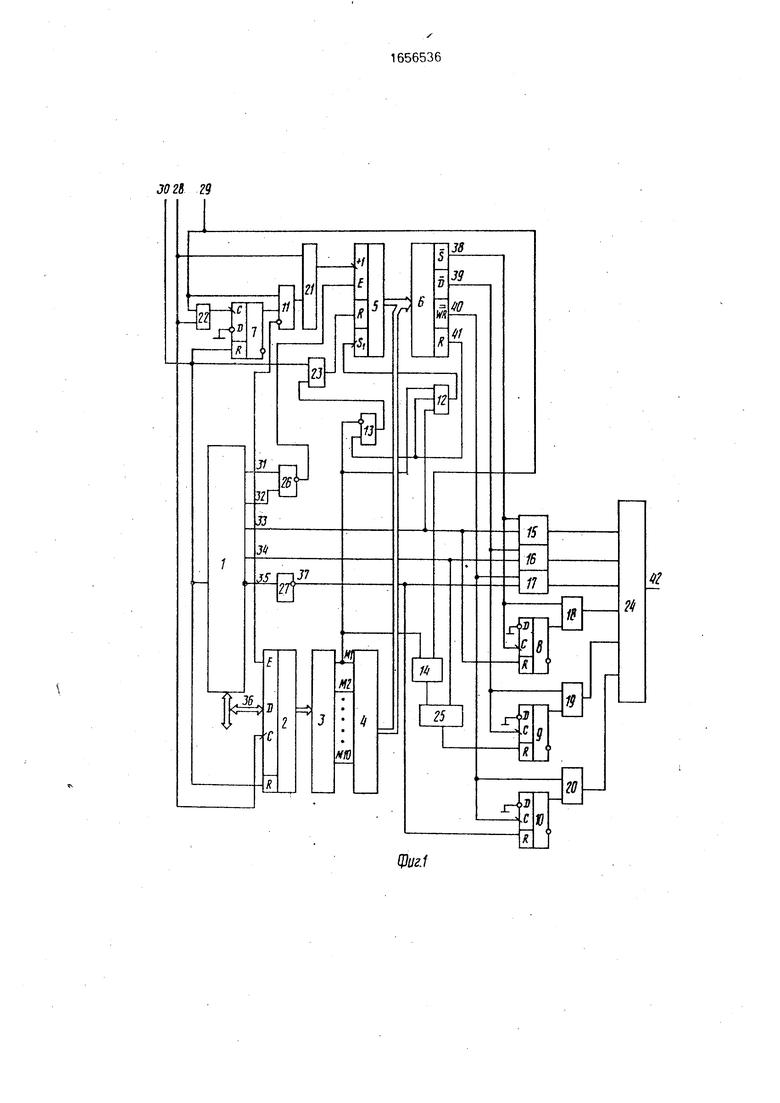

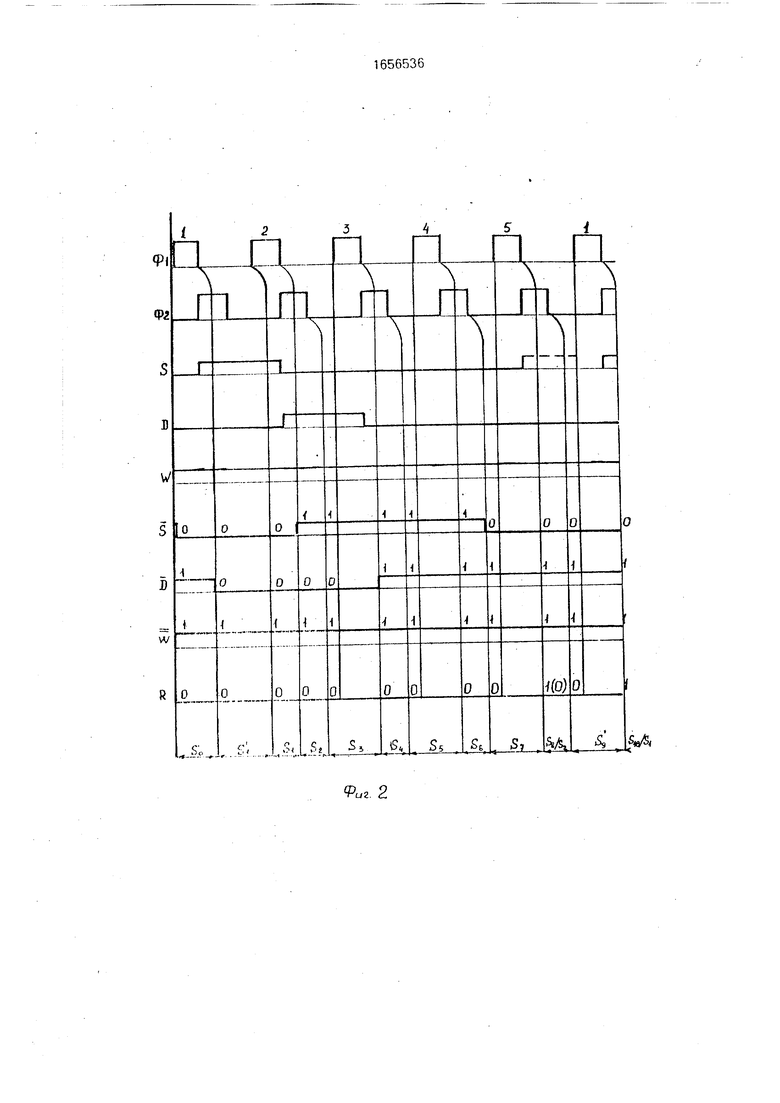

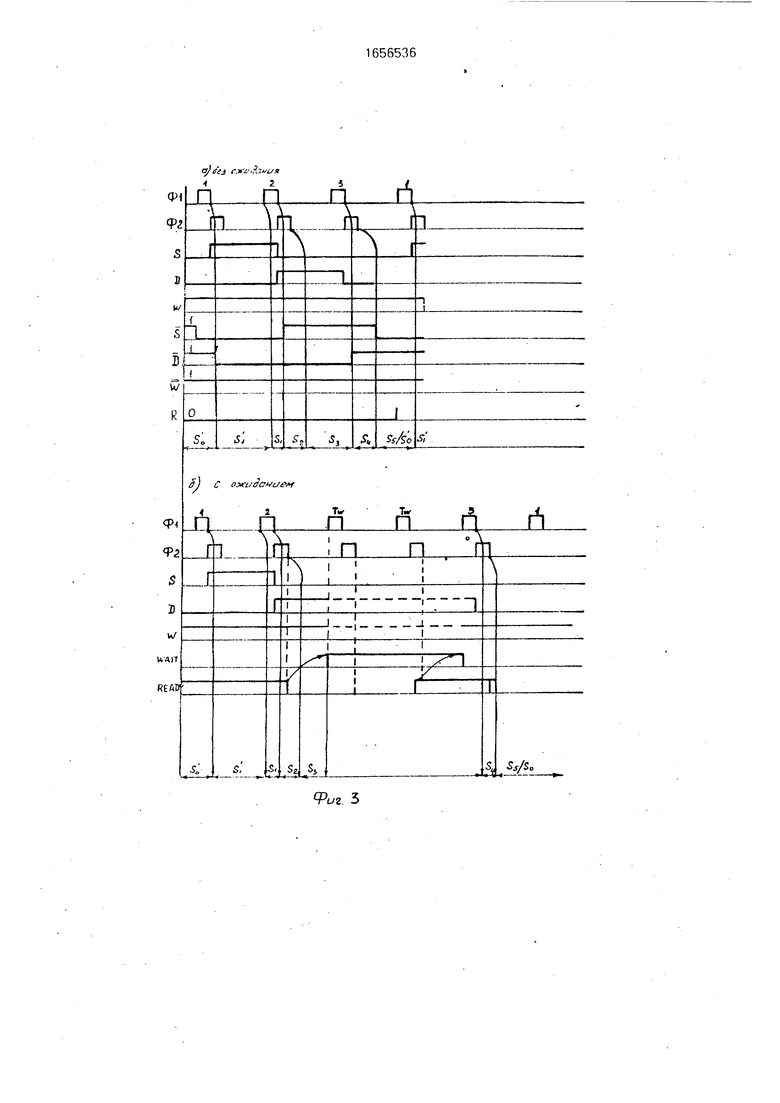

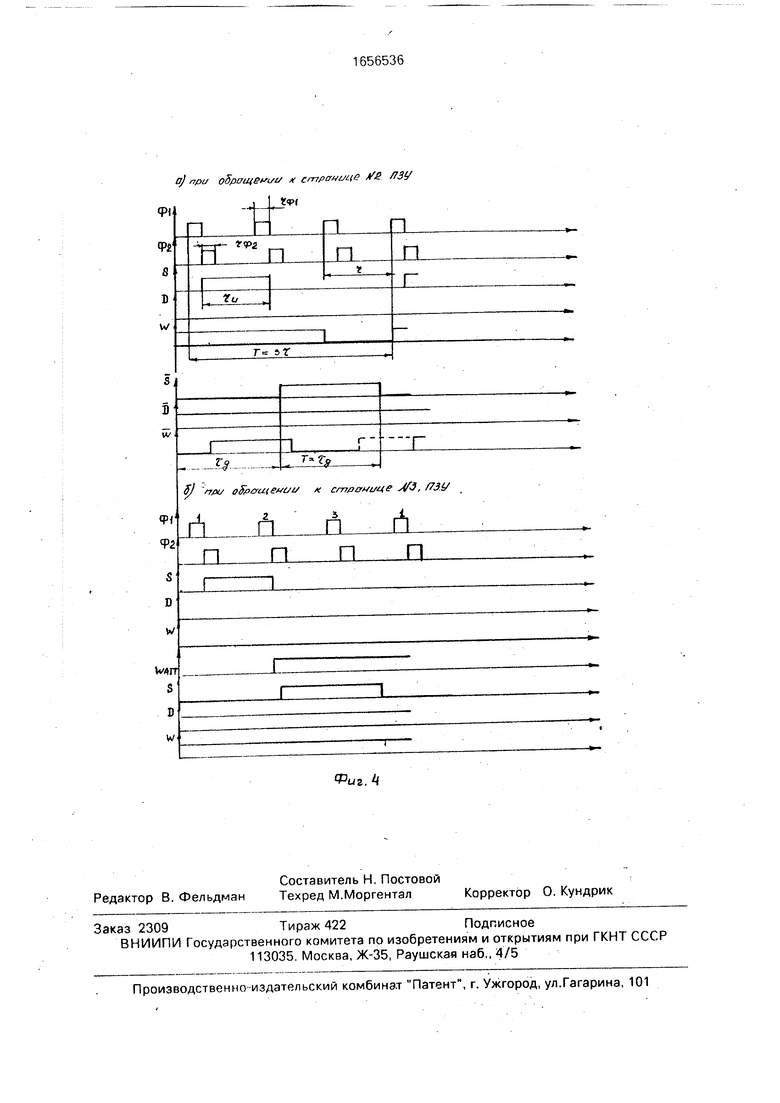

На фиг. 1 представлена функциональная схема устройства для контроля управляющих сигналов микропроцессора; на фиг. 2 представлены временные диаграммы работы устройства при цикле М1 при обращении к нулевой странице ПЗУ, на фиг. 3 - временные диаграммы работы устройства при обращении к странице № 1 ПЗУ; на фиг. 4 а и б представлены временные диаграммы работы устройства при обращении к страницам № 2 и fxb 3 ПЗУ соответственно.

Устройство для контроля управляющих сигналов микропроцессора содержит контролируемый микропроцессор 1, регистр 2 слова состояния микропроцессора, дешифратор циклов 3, шифратор 4, счетчик 5, блок постоянной памяти постоянное запоминающее устройство (ПЗУ) 6, первый 7, второй 8, третий 9 и четвертый 10 триггеры, первый 11. второй 12, третий 13, четвертый 14, пятый 15, седьмой 16, девятый 17. шестой 18, восьмой 19, десятый 20 элементы И, первый 21, второй 22, третий 23, четвертый 24, пятый 25 элементы ИЛИ, элемент ИЛИ-НЕ 26, элемент НЕ 27

Позициями 28, 29, 30 обозначены первый, второй и третий входы устройства соответственно, 31, 32. 33, 34, 35 первый, второй, третий, четвертый и пятый выходы микропроцессора соответственно, которые образуют шину управления, 36 - шина данных микропроцессора, 37 - выход элемента НЕ, 38, 39, 40. 41 - первый, второй, третий,

о ел о ел

OJ

о

четвертый выходы ПЗУ 6 соответственно, 42 - выход ошибки устройства.

Микропроцессор 1 служит для обработки поступающей на его входы информации. По отношению к устройству он яяляется объектом Контроля.

Регистр 2 слова состояния микропроцессора служит для приема, хранения и выдачи слова - состояния микропроцессора.

Дешифратор 3 цикла служит для преобразования кода слова состояния в код одного из десяти циклов работы микропроцессора 1.

Шифратор 4 служит для преобразования кода цикла работы микропроцессора в код адреса страницы ПЗУ 6, соответствующей данному циклу.

Счетчик 5 служит для подсчета числа импульсов тактовой частоты каждого цикла работы микропроцессора и выдачи этого числа в качестве кода адреса слова страницы ПЗУ 6.

ПЗУ 6 служит для хранения и выдачи инверсных значений управляющих сигналов, которые образуют слова и задают границы разрешенных интервалов времени для выдачи управляющих сигналов микропроцессора в каждом такте каждого цикла.

Триггер 7 служит для организации такой строгой последовательности поступления синхроимпульсов со входов 28 и 29 устройства на счетный вход счетчика 5, когда на счетчик подается сначала синхроимпульс первой фазы со входа 28, а затем синхроимпульс второй фазы со входа 29.

Триггер 8 служит для определения наличия или отсутствия управляющего сигнала Синхронизация (SYNC) на разрешенном интервале времени. Так, если сигнал отсутствует, то триггер находится в единичном состоянии, если же сигнал синхронизации обнаружен, то единичным сигналом Синхронизация, подаваемым на вход установки в О триггера 8, он сбрасывается в нулевое состояние. В единичное состояние триггер 8 устанавливается по заднему фронту импульса, поступающего на его синхровход с выхода 38 ПЗУ 6.

Триггер 9 служит для определения наличия или отсутствия управляющего сигнала Прием информации (DBIN) на разрешенном интервале времени во всех циклах, кроме цикла М1, чтобы исключить ложный сигнал ошибки на выходе 40 устройства при переходе от цикла М1 к циклу МЗ (М5 М7) и М9. В остальном работает аналогично триггеру 8.

Триггер 10 служит для определения наличия или отсутствия сигнала Выдача информации (WRITE) на разрешенном

интервале времени. Работает аналогично триггеру 8.

Элемент И 11 служит для запрета выдачи на счетный вход счетчика 5 синхросигналов с входа 29 устройства при наличии в разрядах шины управления микропроцессора сигнала Синхронизация.

Элемент И 12 служит для установки счетчика 5 в состояние, соответствующее

слову 1 ПЗУ 6, при переходе от цикла М1 к другим циклам работы микропроцессора 1. ( Элемент И 13 служит для подачи единичного сигнала на вход установки в О счетчика 5 при переходе от одного цикла

(кроме цикла М1) к другому циклу работы микропроцессора 1.

Элемент И 14 служит для подачи сигнала 1 на вход установки в О триггера 9 при выполнении цикла М1 всякий раз по приходу синхроимпульса со входа 29 устройства. Это необходимо для исключения ложного сигнала ошибки при переходе от цикла М1 к циклу МЗ (М5, М7) и М9.

Элемент И 15 служит для контроля отсутствия сигнала Синхронизация на запрещенных интервалах времени. На этих интервалах инверсный сигнал Синхронизация, выдаваемый с выхода 38 ПЗУ 6 равен 1 и отпирает элемент И 15. Если в этот

момент с микропроцессора выдан сигнал Синхронизация в шину управления, то он как сигнал ошибки пройдет через элемент И 15 и элемент ИЛИ 24 на выход 42 ошибки устройства.

Элемент И 16 служит для контроля отсутствия сигнала Прием информации на запрещенных интервалах времени. Работает аналогично элементу И 15.

Элемент И 17 служит для контроля отсутствия сигнала Выдача информации на запрещенных интервалах времени. Работает аналогично элементу И 15.

Элемент И 18 служит для выдачи сигнала Ошибка на четвертый вход элемента

ИЛИ 24 при отсутствии сигнала Синхронизация на разрешенном интервале времени.

Элемент И 19 служит для выдачи сигнала Ошибка на пятый вход элемента ИЛИ

24 при отсутствии сигнала Прием информации на разрешенном интервале времени.

Элемент И 20 служит для выдачи сигнала Ошибка на шестой вход элемента ИЛИ 24 при отсутствии сигнала Выдача информации на разрешенном интервале времени.

Элемент ИЛИ 21 служит для приема поступающих на его входы синхросигналов и выдачи их на счетный вход счетчика 5.

Элемент ИЛИ 22 служит для появления 1 на прямом выходе триггера 7 как при появлении синхросигнала на входе 28 устройства, так и при появлении синхросигнала на входе 29 устройства.

Элемент ИЛИ 23 служит для организации обнуления содержимого счетчика 5 как общим сигналом Сброс со входа 29 устройства, так и при переходе от одного цикла (кроме цикла М1) к другому циклу работы микропроцессора 1.

Элемент ИЛИ 24 служит для выдачи обобщающего сигнала Ошибка на выход 42 ошибки устройства при неправильной выдаче микропроцессором 1 в разряды ши- ны управления управляющих сигналов Синхронизация SYNC, Прием информации DBIN , Выдача информации, WRITE .

Элемент ИЛИ 25 служит для подачи на вход установки в О триггера 9 единичного сигнала как при цикле работы М1, так и при появлении в других циклах работы на разрешенных интервалах времени сигнала Прием информации.

Элемент ИЛИ-НЕ 26 служит для подачи на разрешающий вход счетчика 5 единичного сигнала при отсутствии в разрядах шины управления сигналов Подтверждение захвата HLDA и Ожидания WAIT и подачи на разрешающий вход счетчика 5 нулевого сигнала при наличии хотя бы одного из сигналов Подтверждение захвата и Ожидание.

Элемент НЕ 27 служит для получения неинвертированного сигнала Выдача информации WRITE для работы схемы контроля.

Вход 28 устройства служит для подачи тактовых импульсов первой фазы Ф 1.

Вход 29 устройства служит для подачи тактовых импульсов второй фазы Ф 2.

Вход 30 устройства служит для подачи сигнала Сброс оператором в любой момент времени для остановки контроля.

Выход 31 микропроцессора 1 является первым выходом микропроцессора и служит для выдачи управляющего сигнала Ожидание.

Выход 32 является вторым выходом микропроцессора 1 и служит для выдачи управляющего сигнала HLDA Подтверждение захвата.

Выход 33 является третьим выходом микропроцессора 1 и служит для выдачи управляющего сигнала SYNC Синхронизация,

Выход 34 является четвертым выходом микропроцессора 1 и служит для выдачи

управляющего сигнала DBIN Прием информации.

Выход 35 является инверсным пятым выходом микропроцессора 1 и служит для выдачи управляющего сигнала WRITE Выдача информации.

Выходы 31, 32, 33, 34, 35 микропроцессора 1 образуют шину управления, которая подвергается контролю.

Группа выходов 33 микропроцессора 1 является шиной данных. Выход 37 является выходом элемента НЕ 27.

Выходы 38, 39, 40, 41 ПЗУ 6 служат для выдачи кодов слов из ПЗУ 6.

Выход 42 устройства является выходом ошибки.

На фиг. 2 изображены временные диаграммы работы устройства при обращении к нулевой странице ПЗУ.

На фиг. 3 изображены временные диаграммы работы устройства при обращении к первой странице ПЗУ 6.

На фиг. 4.а изображены временные диаграммы работы устройства при обращении ко второй странице ПЗУ 6.

На фиг. 4,6 изображены временные диаграммы работы устройства при обращении к третьей странице ПЗУ 6.

Символами So-Sio обозначены слова, хранящиеся в ПЗУ 6 и содержащие коды инверсных значений управляющих сигналов SYNC, DBIN, WRITE, а также прямого значения сигнала RESET

Устройство работает следующим образом.

Перед началом работы на вход 30 сброса устройства подается сигнал высокого уровня длительностью не менее трех периодов тактовой частоты микропроцессора 1, которым микропроцессор устанавливается в исходное состояние. Этим же сигналом в исходное нулевое состояние устанавливаются счетчик 5, регистр 2 слова состояния микропроцессора, триггер 7. После этого в микропроцессоре начинается такт Т1 машинного цикла выборки команды М1 (см. фиг. 2). На первый и второй входы 28 и 29 синхронизации устройства поступают неперекрывающиеся последовательности синхроимпульсов первой Ф 1 и второй Ф 2 фаз соответственно.

Если первым пришел импульс фазы Ф 2, то он поступает на первый вход элемента И 11 и через элемент ИЛИ 22 нл i инхровход триггера 7, который по заднему фронту импульса фазы Ф 2 устанавливается п состояние 1 и выдаст единичный сигнал на третий вход элемента И 11 Но так как этот момент уже заперт нулевым сигналом со второго входа 29 синхронизации уст роиства, то импульс фазы Ф 2 не поступает на счетный вход счетчика 5. Если же приходит первым импульс фазы Ф 1, то он поступает на первый вход элемента ИЛИ 21, с выхода элемента ИЛИ 21 проходит на счетный вход счетчика 5, а также устанавливает триггер 7 в состояние 1. что обеспечивает прохождение импульса фазы Ф 2 при отсутствии сигнала Синхронизация на инверсном входе элемента И 11, поступающего с выхода 33 микропроцессора 1.

В счетчике 5 при появлении на его счетном входе импульса проверяется, есть ли на его разрешающем входе единичный сигнал, который поступает при отсутствии в разрядах шин управления микропроцессора 1 сигналов Ожидание WAIT и Подтверждение захвата HLDA, Эти сигналы выдаются на разрешающий вход ч с выходов 31 и 32 микропроцессора 1 соответственно через элемент ИЛИ-НЕ 26 При отсутствии этих сигналов счетчик начинает подсчитывать импульсы по их заднему фронту для исключения гонок сигнала Ожидание, который устанавливается в 1 по переднему фронту импульса фазы Ф 1 и самим импульсом фазы Ф 1. При появлении хотя бы одного из сигналов на выходах 31 и 32 микропроцессоров 1 счет останавливается и счетчик 5 запоминает свое состояние, чтобы продолжить счет при снятии этих сигналов, Каждый машинный цикл сопровождается выдачей сигнала Синхронизация в такте Т 1. При этом на шину данных микропроцессора выдается слово состояния микропроцессора 1, определяющее действия, которые будут выполняться в данном машинном цикле. По совпадению сигналов Ф 1 1 и Е 1 слово состояние записывается в 8 - разрядный регистр 2 слова состояния микропроцессора С группы выходов регистра 2 слово состояния поступает на группу выходов дешифратора циклов 3, который определяет, какой из циклов выполняется в данном случае и длет эту информацию в виде единичного сигнала на один из десяти своих выходов, которые подключены к входам шифраторп 1 Шифратор 4 преобразует код цикла в код адреса страницы ПЗУ в соответствующей данному циклу и выдает этот код на rpynnv старших разрядов адресного входа ПЯУ ь R то же время со СЧРТЧИКЗ 5 поступает нл группу младших разрядов адресного пхпдч ПЗУ 6 число подсчитанных импульсов п ЧНДР кода адреса глопя и данной страниц: i I I3v 6 Адресное пргилрлпстпо ПЗУ 6 p;i if i/мг мл 4 страпиць каждая из которЫ) Г чт и i ny ет определенной группе цикл и страниц.i циклу Ml (см фи П Чнзая

страница - циклам М2, М4, Мб, М8, М10(см. фиг. 3, а и б), вторая страница - циклам МЗ, М5, М7 (см. фиг. 4,а), третья страница - циклу М9 (см. фиг. 4,6). Такое разбиение

адресного пространства обьясняется тем, что каждой странице поставлены в соответствие циклы, которым соответствуют сходные сигналы управления во время их выполнения.

0В случае, если с выходов шифратора не

поступает код адреса страницы, как например в такте Т1, то обращение производится к нулевой странице, так как цикл М1 обязателен для всех без исключения ко5 манд, а в такте Т1 выдаются управляющие сигналы, одинаковые для всех циклов. По адресам, поступающим на входы ПЗУ 6, из него извлекаются слова, которые содержат инверсные значения сигналов управления

0 микропроцессора Синхронизация, Прием информации, Выдача информации и в прямом виде значение сигнала Конец цикла.

Значение SYNC, DBIN. WRITE сигна5 лов SYNC, DBIN, WRITE поступают на первые входы элементов И 15, 16. 17 соответственно, на вторые входы которых поступают прямые значения управляющих сигналов с выходов 33, 34 микропроцессора

0 1 и с выхода 37 элемента НЕ 27 соответственно. При этом проверяется отсутствие импульсов данных сигналов управления на запрещенных интервалах. Пусть в данный момент времени (например, в такте ТЗ цик5 ла М1) не должно быть сигнала SYNC Син хронизация (см. фиг. 2). Тогда в соответствующем данному моменту слове ПЗУ 6 должно быть записано SYNC - 1. Этот сигнал открывает элемент И 14 и в случае

0 если появится ложный сигнал Синхронизация, то этот сигнал пройдет через элемент И 14 на первый вход элемента ИЛИ 24, с выхода 42 которого будет выдан сигнал

ошибки. Если же сигнал Синхронизация

5 должен быть в данном такте (например, в такте Т1 цикла М1). то из ПЗУ 6 будет считан сигнал SYNC - 0, который запирает элемент И 15 на время прохождения сигнала SYNC. Аналогичным образом работают схемы кон0 троля сигналов DBIN Прием информации и WRITE Выдача информации.

Инверсные значения сигналов SYNC DBIN, WRITE поступают также с выходов 38 39, 40 соответственно на входы синхрониза5 ции триггеров 8, 9, 10 и на первые входы элементов И 18, 19, 20. На входы установки в О триггеров 8, 9, 10 подаются контролируемые значения сигналов SYNC, DBIN, WRITE соответственно в прямом виде Здесь контролируется наличие нужных сиг

налов управления на разрешенных интерв лах времени.

Рассмотрим работу схемы контроля на примере сигнала Синхронизация В такте 73 цикла М1 из ПЗУ считывается сигнал SYNC 1, который поступает на симхровход триггера 8 и на первый вход элемента И 18, По окончании цикла М1 в такте 1 } любого цикла должен появиться сигнал SYNC, а из ПЗУ 6 считывается сигнал SYNT - 0. При этом триггер 8 заднему фронту сигнала 5VNC 1 устанавливается в 1, а сигнал SVКГС 0 подается на синхровход триггера 8 и гтервый вход элемента И 18 в течение времени, равного разрешенному интервалу времени появления сигнала SYNC. Пуо.™ сиГ Мл SYNC так и не появился на разрешенном интервале времени из-за ошибки в работе икр процг:сслра 1 Тогда в следую- (Ц01 .1с из ПЗУ 5 будет считан сигнал - 1, который, поступая на перв гй вход элемента И 18, открывает его, в результате чего единичный сигнал с триггера 7 поступя ет через элемент ИЛИ 24 на выход 42 как ens нал ошибки. Если ж€ SYNC 1 появился на разрешенном интервале времени, то он. поступая на вход установки в О1 , сбр зсываег триггер 8 в О и поэтому в следующий момент времени сигнал ошибки не выдается

Сигналы DBIN и WRITE контролируются аналогично сигналу SYNC, только сигнал DBIN в цикле М1 не контролируется, так ка в цикле М1 с первого выхода дешифратора циклов 3 на вход элемента 1/1 14 подается единичный сигнал, открывающий этот элемент и при Ф2 - 1 на вход установки в О триггеоа 9 через элементы И 14 и ИЛИ 2Г подается единичный сигнал Это необходимо для предотвращения выдачи ложного сигнала ошибки при переходе от цикла М1 к циклу МЗ(М5, М7)и М9.

С выхода 41 ПЗУ 6 выдается также импульс Конец цикла R, который указывает, что выполняемый микропроцессором 1 цикл закончен и следует переходить к следующему циклу. Переход к следующему циклу осуществляется следующим образом. Все циклы микропроцессора, кроме цикла М1. включают три такта (Т1, Т2, ТЗ), только цикл М1 может иметь четыре или пять тактов. Таким образом, если выполняемый цикл не был циклом М1, то счетчик 5, подсчитав три такта, выдает на входы ПЗУ 6 код адреса, по которому считывается сигнал R 1. Этот сигнал с выхода 41 ПЗУ 6 поступает на вторые входы элементов И 12 и 13. Если выполняется не цикл М1, то с первого выхода дешифратора выдается нулевой сигнал, который запирает элемент И 12 и отпирает

члемент И 13, через который сигнап Н - 1 с выхода ПЗУ 6 поступает на второй вход элемента ИЛИ 23 и далее на вход установки в О счетчика 5. который устанавливается н нулевое состояние, что соответствует слову So , хранящемуся в ПЗУ б по нулевому адресу.

Момент перехода от одного цикла (кроме цикла М1) к другому поясняется времен0 ными диаграммами, изображенными на фиг. 3 и 4. Рассмотрим, как происходит переход от цикла М1 к другим циклам Цикл М1 может иметь четыре или пять тактов Чтобы определить, сколько тактов имеет с своем

5 составе данный цикл М1, используется сигнал Синхронизация, появление которого анализируется после окончания че;вертого такта. С«етчик 5 в этом случае выдает код адреса слова в нулевой странице ПЗУ 6,

0 из которой считывается сигнал R - 1. который как и в других циклах поступает с выхода 41 ПЗУ б на вторые входы элементов И 12 и 13. Но элемент И 13 закрыт единичным сигналом, подаваемым на его инверсный

5 вход с первого выхода дешифратора 3 Этот же сигнал поступает на первый вход элемента И 12, и если сигнал синхронизации появится в следующем такте, го через элемент И 12 он поступит на вход установки счетчика

0 в состояние, соответствующее слову Si , хранящемуся в ПЗУ 6.

Установка счетчика в состояние, соответствующее слову Si , а не So , необходи ма в связи с тем, что в данном случае пятый

5 тактТ5 цикла М1 оказался первым тактом Т1 следующего цикла, за которым должен следовать второй такт Г2 и так далее Если же в пятом такте сигнал SYNC не появился, то несмотря на то, что R - 1, счетчик продолжа0 ет счет и выдачу кода адреса в ПЗУ б и по заднему фронту импульсзфазы Ф2 такта Т5 устанавливается R - 0. По окончании такта Т5 цикла М1 счетчик 5 выдает код адреса слова нулевой странице ПЗУ 6. по кото5 рому считывается слово, где разряд R -- 1, и снова происходит анализ появления сигнала синхронизации. При его появлении прохождение импульсов фазы Ф2 через элемент ИЛИ 24 запрещается, счетчик 5 ус0 танавливается в состояние, соответствующее слову Si в регистр 2 слова состояния микропроцессора записывается новое слово состояния и начинается работа по следующему циклу.

5Запрет импульсов фазы Ф2 в момент

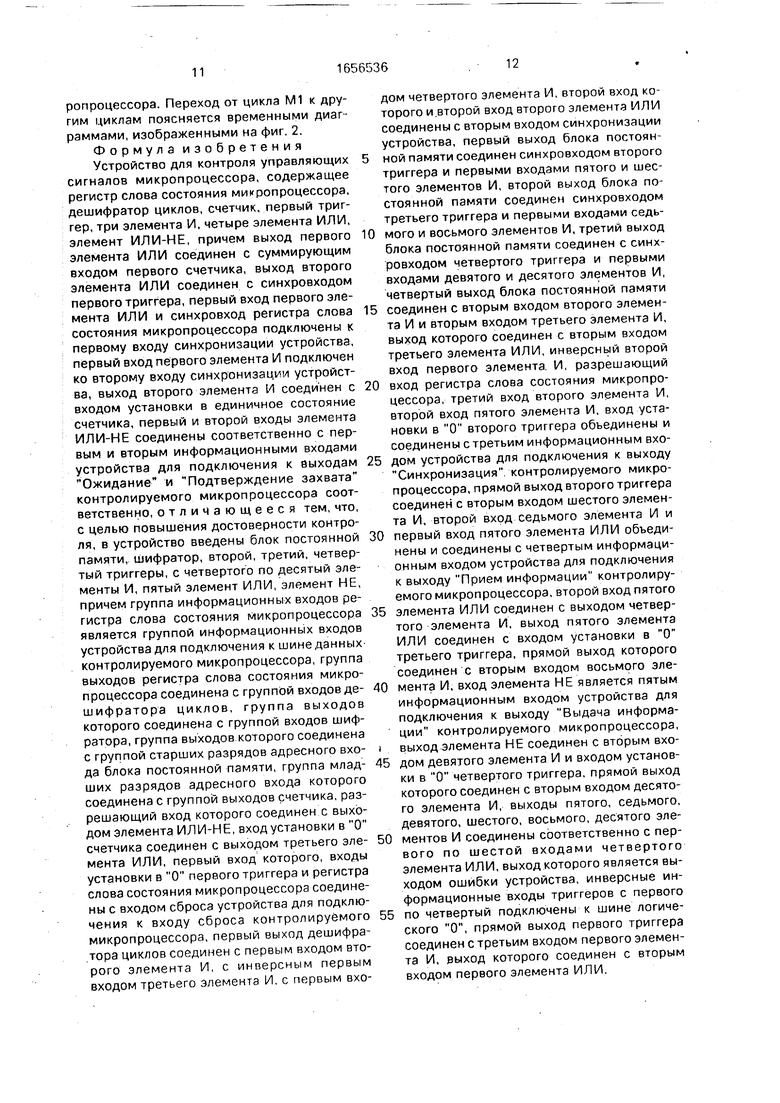

прохождения сигнала синхронизации необходим для того, чтобы счетчик 5 не мог выдавать код адреса слова без указания кода адреса новой страницы ПЗУ 6, т.е. до срабатывания регистра 2 слова состояния микропроцессора. Переход от цикла М1 к другим циклам поясняется временными диаграммами, изображенными на фиг. 2. Формула изобретения Устройство для контроля управляющих сигналов микропроцессора, содержащее регистр слова состояния микропроцессора, дешифратор циклов, счетчик, первый триггер, три элемента И, четыре элемента ИЛИ, элемент ИЛИ-НЕ, причем выход первого элемента ИЛИ соединен с суммирующим входом первого счетчика, выход второго элемента ИЛИ соединен с синхровходом первого триггера, первый вход первого элемента ИЛИ и синхровход регистра слова состояния микропроцессора подключены к первому входу синхронизации устройства, первый вход первого элемента И подключен ко второму входу синхронизации устройства, выход второго элемента И соединен с входом установки в единичное состояние счетчика, первый и второй входы элемента ИЛИ-НЕ соединены соответственно с первым и вторым информационными входами устройства для подключения к выходам Ожидание и Подтверждение захвата контролируемого микропроцессора соответственно, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введены блок постоянной памяти, шифратор, второй, третий, четвертый триггеры, с четвертого по десятый элементы И. пятый элемент ИЛИ, элемент НЕ, причем группа информационных входов регистра слова состояния микропроцессора является группой информационных входов устройства для подключения к шине данных контролируемого микропроцессора, группа выходов регистра слова состояния микропроцессора соединена с группой входов де- шифратора циклов, группа выходов которого соединена с группой входов шифратора, группа выходов которого соединена с группой старших разрядов адресного входа блока постоянной памяти, группа младших разрядов адресного входа которого соединена с группой выходов счетчика, разрешающий вход которого соединен с выходом элемента ИЛИ-НЕ, вход установки в О счетчика соединен с выходом третьего элемента ИЛИ, первый вход которого, входы установки в О первого триггера и регистра слова состояния микропроцессора соединены с входом сброса устройства для подключения к входу сброса контролируемого микропроцессора, первый выход дешифратора циклов соединен с первым входом второго элемента И, с инверсным первым входом третьего элемента И. с первым входом четвертого элемента И. второй вход которого и второй вход второго элемента ИЛИ соединены с вторым входом синхронизации устройства, первый выход блока постоянной памяти соединен синхровходом второго триггера и первыми входами пятого и шестого элементов И, второй выход блока постоянной памяти соединен синхровходом третьего триггера и первыми входами седьмого и восьмого элементов И, третий выход блока постоянной памяти соединен с синхровходом четвертого триггера и первыми входами девятого и десятого элементов И, четвертый выход блока постоянной памяти

соединен с вторым входом второго элемента И и вторым входом третьего элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ. инверсный второй вход первого элемента И, разрешающий

вход регистра слова состояния микропроцессора, третий вход второго элемента И, второй вход пятого элемента И, вход установки в О второго триггера объединены и соединены с третьим информационным входом устройства для подключения к выходу Синхронизация контролируемого микропроцессора, прямой выход второго триггера соединен с вторым входом шестого элемента И, второй вход седьмого элемента И и

первый вход пятого элемента ИЛИ объединены и соединены с четвертым информационным входом устройства для подключения к выходу Прием информации контролируемого микропроцессора, второй вход пятого

элемента ИЛИ соединен с выходом четвертого элемента И, выход пятого элемента ИЛИ соединен с входом установки в О третьего триггера, прямой выход которого соединен с вторым входом восьмого элемента И, вход элемента НЕ является пятым информационным входом устройства для подключения к выходу Выдача информации контролируемого микропроцессора,

выход элемента НЕ соединен с вторым входом девятого элемента И и входом установки в О четвертого триггера, прямой выход которого соединен с вторым входом десятого элемента И, выходы пятого, седьмого, девятого, шестого, восьмого, десятого элементов И соединены соответственно с первого по шестой входами четвертого элемента ИЛИ, выход которого является выходом ошибки устройства, инверсные информационные входы триггеров с первого

по четвертый подключены к шине логического О, прямой выход первого триггера соединен с третьим входом первого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ.

30 2В 29

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессора | 1990 |

|

SU1765828A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1753474A1 |

| Электронная вычислительная машина для ускоренной обработки запросов прерываний | 1988 |

|

SU1621029A1 |

| Имитатор локальной шины микропроцессора | 1987 |

|

SU1644144A1 |

| Микропроцессорная система с контролем | 1984 |

|

SU1242976A1 |

| Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем | 1984 |

|

SU1242956A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1460722A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1737453A1 |

| Устройство для управления памятью программ и данных | 1988 |

|

SU1674137A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении микропроцессорных систем и микроЭВМ с контролем. Цель изобретения - повышение достоверности контроляуправляющихсигналов микропроцессора. Устройство содержит контролируемый микропроцессор, регистр слова состояния микропроцессора, дешифратор циклов, шифратор, счетчик, постоянное запоминающее устройство, четыре триггера, десять элементов И, пять элементов ИЛИ, элемент ИЛИ-НЕ, элемент НЕ Сущность изобретения состоит в повышении достоверности контроля формирования управляющих сигналов микропроцессора типа КР580ИК80А за счет ограничения временны интервалов, в течение которых разрешена подача управляющих сигналов в разряды шины управления 4 ил.

Фиг 2

to

IT

tc if

о) при сгпрпнгл(Ј Aff /73V

Ф

Ф в

D w

PI

- Ч

.

SJ при о5р/уще /сл/ к странице stfJ. /73У

Л

п.

Й1

п

Д

S

Г

D

w

и

А

и

и

| Устройство для контроля условных переходов микропроцессора | 1984 |

|

SU1238076A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Предохранительный клапан | 1985 |

|

SU1283480A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-06-15—Публикация

1989-01-12—Подача