(54) ОПЕРАТИВНОЕ ЗАПОМИНАЮ1-ДЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения цифровой и аналоговой вычислительных машин | 1983 |

|

SU1128273A1 |

| Устройство для сбора передачи и приема информации | 1975 |

|

SU550666A1 |

| Реверсивный счетчик импульсов | 1972 |

|

SU437231A1 |

| Многоканальное измерительно-регистрирующее устройство (его варианты) | 1982 |

|

SU1038807A1 |

| Устройство для входного контроля изделий | 1990 |

|

SU1746388A2 |

| Опреративное запоминающее устройство | 1976 |

|

SU645204A1 |

| Оперативное запоминающее устройство | 1978 |

|

SU752469A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1984 |

|

SU1840075A1 |

| Устройство для циклового программного управления | 1986 |

|

SU1381432A1 |

Изобретение относится к радиоэлектронике и может быть использовано в вычислительной и цифровой измерительной технике для запоминания и преобразования чисел, представленных многозначными кодами.

Известно устройство для запоминания многозначной информации,выполненное на основе динамических пересчетных или релаксационных схем (делителей частоты).

Необходимость обеспечения динамического режима работы элементов памяти усложняет структуру оперативных запоминающих устройств и не позволяет производить преобразование информации из одной формы в другую (из фазоампульсной в -двоично-десятичную, времяимпульсную и т.п.), а наличие реактивных компонентов исключает их реализацию в виде больших интегральных схем.

Наиболее близким по технической сущности к изобретению является устройство памяти, содержащее накопитель (двоичный адресний регистр), дешифратор адреса и регистр адреса (блоки, обеспечивающие коммутацию или выбор чисел и разрядов чисел), генератор импульсов, блок синхронизации, обеспечивающий формирование опорных меток времени и опорного двоичного или двоично-десятичного кода), сумматоры по модулю 2 и элемент И (выполняющие функцию схемы сравнения двоичных кодов), при этом входы дешифратора адреса подключены к выходам регистра адреса, входы сумматоров по модулю 2 подключены к выходам накопителя, вы10ходы генератора импульсов соединены с другими входами накопителя и другими входами сумматоров по модулю 2, выходы которых подключены ко входам элемента И, выход которого является вы15ходсм устройства.

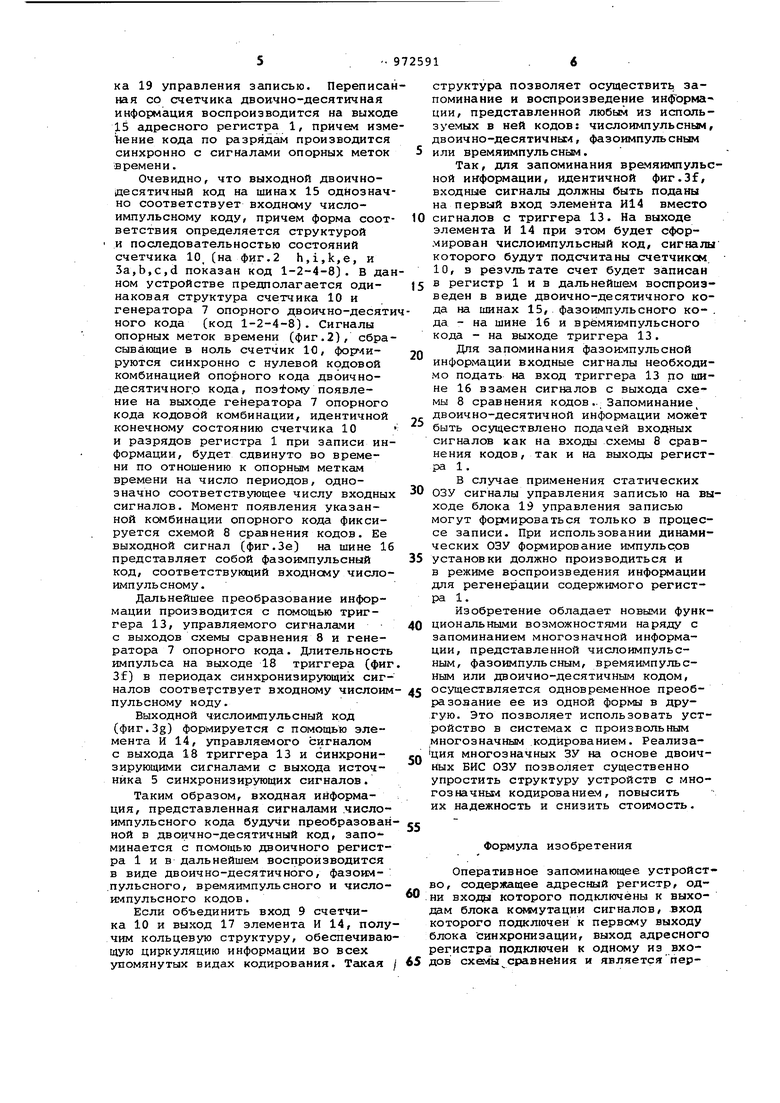

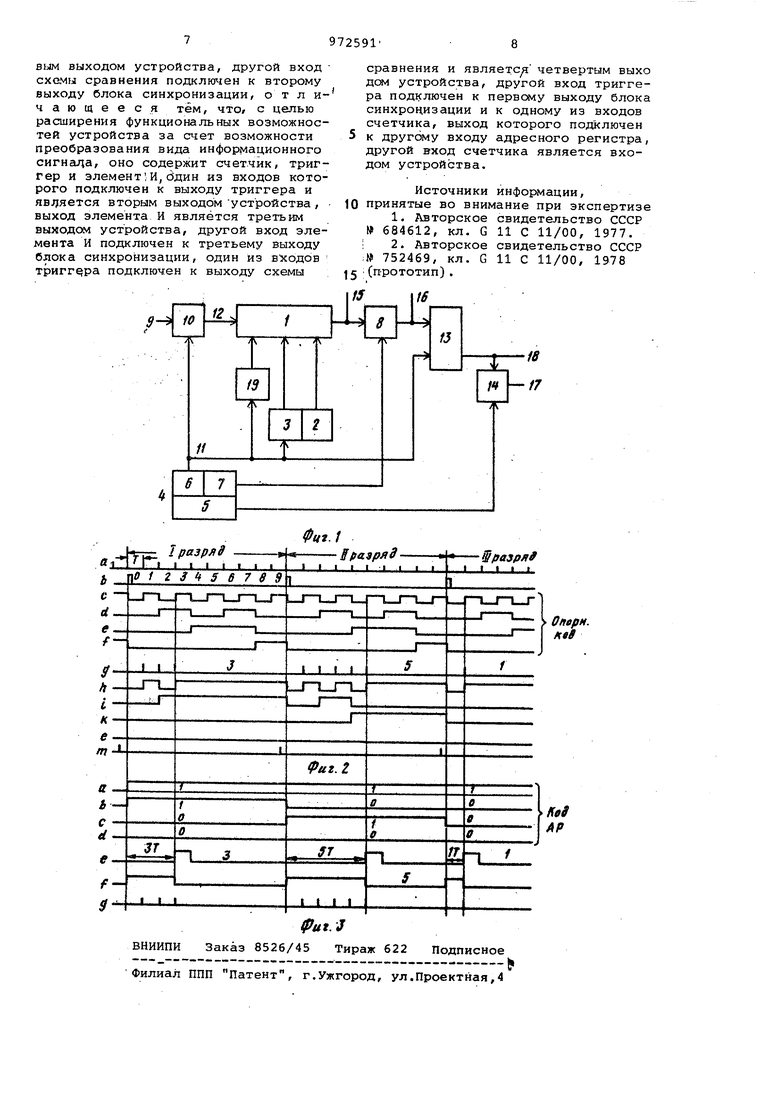

В этом устройстве для целей запоминания последовательной многозначной фазоимпульсной информации используется двоичный накопитель БИС адресно20го регистра двоичного оперативного запоминающего устройства. В нем вход информационных сигналов соединен со входом синхронизации записи накопителя, на информационные входы нако25пителя полаются сигналы с вспомогательного генератора импульсов опорного кода, период изменения которого равен периоду следования входного сигнала. Таким образом, устанавливается одно30значное соответствие значения опорного кода на выходе генератора и временного положения входного сигна ла. Значение опорного кода запомина ется в накопителе и в дальнейшем преобразуется в выходной сигнал в фазоимпульсной форме путем сравнени кода на выходе накопителя с опорным кодомХ2. Подобная структура, обеспечивает возможность запоминания информации, представленной только фазоимпульсными сигналами, когда имеется соответствие между периодом следования (временным положением) входного сигнала и цикла опорного кода. того, отсутствие взаимной временной синхронизации входного сигнал и начальногозначения опорного кода не позволяет по значению двоичной комбинации в накопителе однозначно судить о входной информации, т.е. устройство не обеспечивает преобразование информации из одной фор мы в другую, в нем входная и выходна информации представляются только в фазоимпульсной форме, что сужает, об ласти применения двоичных оперативны запоминающих устройств на основе больших интегральных схем в системах с многозначным, в частности чис лоимпульсным-, времяимпульсным представлением информации, когда значе ние каждого разряда кода представля ется количеством импульсов или длительностью импульсов, Целью изобретения является расши рение функциональных возможностей устройства за счет преобразования информации. Поставленная цель достигается тем что в оперативное запоминающее устройство, содержащее адресный регистр одни входы которого подключены к выходам блока.коммутации сигналов, вход которого подключен к первому выходу блока синхронизации, выход адресного регистра подключен к одном из входов схемы сравнения и является первым выходом устройства, другой вход схемы сравнения подключен к второму выходу блока синхронизации, дополнительно введены счетчик, триггер и элемент И, один из входов KOTtiporo подключен к выходу триггера и является вторым выходом устройства виход элемента И является третьим выходом устройства, другой вход элемента И подключен к третьему ходу блока синхронизации, один из входов триггера подключен к выходу схемы сравнения и является четвертым выходом устройства, другой вход триггера подключен к первому выходу блока синхронизации и к одному иэ вх дев счетчика, выход которого подключен к другому входу адресного регист ра, другой вход счетчика является входом устройства. На фиг. 1 представлена Функциональная схема устройства; на фиг.2 и 3 - временные диаграммы его работы. Оперативное запоминающее устройство содержит адресный регистр 1, блок коммутации сигналов,состоящий из блока 2 коммутации чисел и блока 3 коммутации разрядов, блок 4 синхронизации, включающий в себя источник 5 синхронизирующих сигналов, формирователь 6 опорных меток времени и генератор 7 опорного двоичнодесятичного кода, схему 8 сравнения кодов, счетный вход 9 счетчика 10, выход 11 формирователя б опорных меток времени, информационные выходы12 счетчика 10, триггер 13, элемент И 14, выход 15 адресного регистра 1, выход16 схемы 8 сравнения кодов, выход 17 элемента И 14iвыход 18 триггера 13 и блок 19,управления записью . На фиг.2 представлено: а - синхронизирующие сигналы, b - опорные метки времени, с, d, е, - опорный двоично-десятичный код. В данном устройстве опорные метки врв«1ени b совпадают с моментом формирования нулевой двоично-десятичной комбинации опорного двоично-десятичного кода и, кроме того, служат для разделения во времени разрядов входной информации (шина 11 соединена со входом блока 3 коммутации разрядов ) . . „ Работа устройства описывается на примере запоминания и воспроизведения информации, представленной числоимпульсным кодом (последовательно числа 3-5-1). При числоимпульсном представлении информации (фиг.2) количество иглпульсов в промежутке времени, ограниченHovi двумя соседними опорными сигналами, определяет значение представляемого числа. Блок 2 коммутации чисел своими выходными сигналами определяет область памяти регистра 1, предназначенную для запоминания определенного многоразрядного числа, а блок 3 коммутации разрядов, управляемый сигналами опорных меток времени, обеспечивает ьыбор адреса ячейки памяти для запоминания конкретного разряда ходного числа. Счетчик 10 устанавливается опорными метками времени в нулевое состояние. При поступлении числоимпульсногО кода числа (фиг.2§), подлежащего запоминанию, входные сигналы каждого разряда кода подсчитываются счетчиком 10. Получаемое значение двоичного кода (h,i,k,I) с выхода 12 счетчика 10 записывается в регистр 1 сигналом Сфиг.2 т) на выходе блока 19 управления записью. Переписа ная со счетчика двоично-десятичная информация воспроизводится на выход 15 адресного регистра 1, причем изм 11ение кода по разрядам производится синхронно с сигналами опорных меток времени. Очевидно, что выходной двоичнодесятичный код на шинах 15 однознач но соответствует входному числоимпульсному коду, причем форма соот ветствия определяется структурой и последовательностью состояний счетчика 10(на фиг.2 h,i,k,e, и 3a,b,c,d показан код 1-2-4-8). В да ном устройстве предполагается одинановая структура счетчика 10 и генератора 7 опорного двоично-десят ного кода (код 1-2-4-8). Сигналы опорных меток времени (фиг.2), сбра сывающие в ноль счетчик 10, форчируются синхронно с нулевой кодовой комбинацией опорного кода двоичнодесятичного кода, поэтому появление на выходе генератора 7 опорного кода кодовой комбинации, идентичной конечному состоянию счетчика 10 и разрядов регистра 1 при записи ин формации, будет сдвинуто во времени по отношению к опорным меткам времени на число периодов, однозначно соответствующее числу входны сигналов. Момент появления указанной комбинации опорного кода фиксируется схемой 8 сравнения кодов. Ее выходной сигнал (фиг.Зе) на шине 1 представляет собой фазоимпульсный код, соответствующий входному число импульсному. Дальнейшее преобразование информации производится с помощью триггера 13, управляемого сигналами с выходов схемы сравнения 8 и генератора 7 опорного кода. Длительност импульса на выходе 18 триггера (фи 3f) в периодах синхронизирующих сиг налов соответствует входному числоим пульсному коду. Выходной числоимпульсный код (фиг.Зд) формируется с помощью элемента И 14, управляемого сигналом с выхода 18 триггера 13 и синхронизирующими сигналами с выхода источника 5 синхронизирующих сигналов. Таким образом, входная информация, представленная сигналами .числоимпульсного кода будучи преобразован ной в двоично-десятичный код, запоминается с помощью двоичного регистра 1 и в дальнейшем воспроизводится в виде двоично-десятичного, фазоим.пульсного, времяимпульсного и числоимпульсного кодов. Если объединить вход 9 счетчика 10 и выход 17 злемента И 14, полу чим кольцевую структуру, обеспечиваю щую циркуляцию информации во всех упомянутых видах кодирования. Такая структура позволяет осуществить запоминание и воспроизведение информации, представленной любым из используемых в ней КОДОВ числоимпульсным, двоично-десятичны:, фазоимпульсным или времяимпульсным. Так, для запоминания времяимпульсной информации, идентичной фиг.3, входные сигналы должны быть поданы на первый вход элемента И14 вместо сигналов с триггера 13. На выходе элемента И 14 при этом будет сформирован числоимпульсный код, сигналы которого будут подсчитаны счетчиком 10, в результате счет будет записан в регистр 1 и в дальнейшем воспроизведен в виде двоично-десятичного кода на шинах 15, фазоимпульсного ко-. да - на шине 16 и времяимпульсного кода - на выходе триггера 13. Для запоминания фазоимпульсной информации входные сигналы необходимо подать на вход триггера 13 по шине 16 взамен сигналов с выхода схемы 8 сравнения кодов .., Запоминание двоично-десятичной информации может быть осуществлено подачей входных сигналов как на входы схемы 8 сравнения кодов, так и на выходы регистра 1. В случае применения статических ОЗУ сигналы управления записью на выходе блока 19 управления записью могут формироваться только в процессе записи. При использовании динамических ОЗУ формирование импульсов установки должно производиться и в режиме воспроизведения информации для регенерации содержимого регистра 1. Изобретение обладает новыми функциональными возможностями наряду с запоминанием многозначной информации, представленной числоимпульсным, фазоимпульсным, времяимпульсным или двоично-десятичным кодом, осуществляется одновременное преобразование ее из одной формы в другую. Это позволяет использовать устройство в системах с произвольным многозначным кодированием. Реализация многозначных ЗУ на основе двоичных БИС ОЗУ позволяет существенно упростить структуру устройств с многозначные кодированием, повысить их надежность и снизить стоимость. Формула изобретения Оперативное запоминающее устройство, содержащее адресный регистр, одни входы которого подключены к выходам блока коммутации сигналов, вход которого подключен к первому выходу блока синхронизащ1и, выход адресного регистра подключен к одному из входов схелы сравнейия и являетсяпервым выходом устройства, другой вход схемы сравнения подключен к второму выходу блока синхронизации, о т л ичающееся тем, что/ с целью расширения функциональных возможностей устройства за счет возможности преобразования вида информационного сигнала, оно содержит счет.чик, триггер и элемент:И,бдин из входов которого подключен к выходу триггера и яв; яется вторым выходом устройства , выход элемента И является третьим выходом устройства, другой вход элемента И подключен к третьему выходу блока синхронизации, один из входов триггера подключен к выходу схемы

ts сравнения и являете четвертым выхо цсм устройства, другой вход триггера подключен к первому выходу блока синхронизации и к одному из входов счетчика, выход которого подключен к другому входу адресного регистра, другой вход счетчика является входом устройства. Источники информации, принятые во внимание при экспертизе 1, Авторское свидетельство СССР 684612, кл. G 11 С 11/00, 1977. I 2. Авторское свидетельство СССР .№ 752469, кл. G 11 С 11/00, 1978 : (прототип).

Авторы

Даты

1982-11-07—Публикация

1981-05-25—Подача