Устройство для входного контроля изделий относится к автоматике, может быть использовано при входном контроле изделий на производстве и является усовершенствованием устройства по авт.св. № 1619313.

Цель изобретения - повышение быстродействия за счет сокращения числа операций контроля.

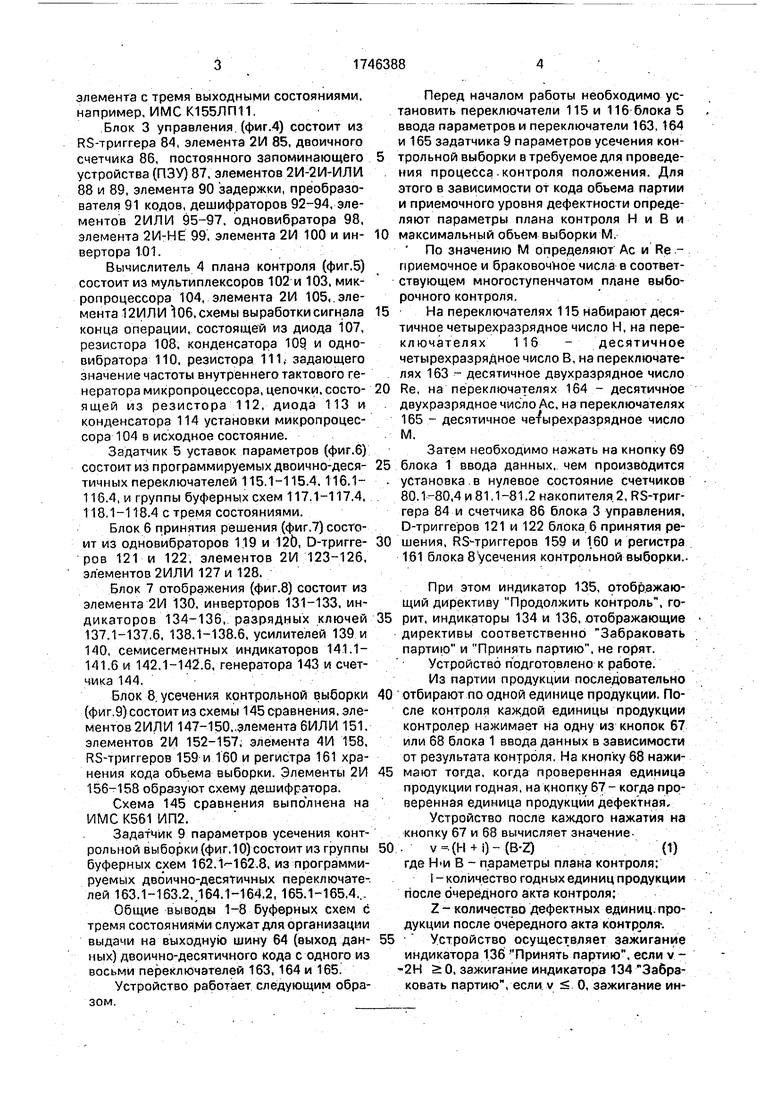

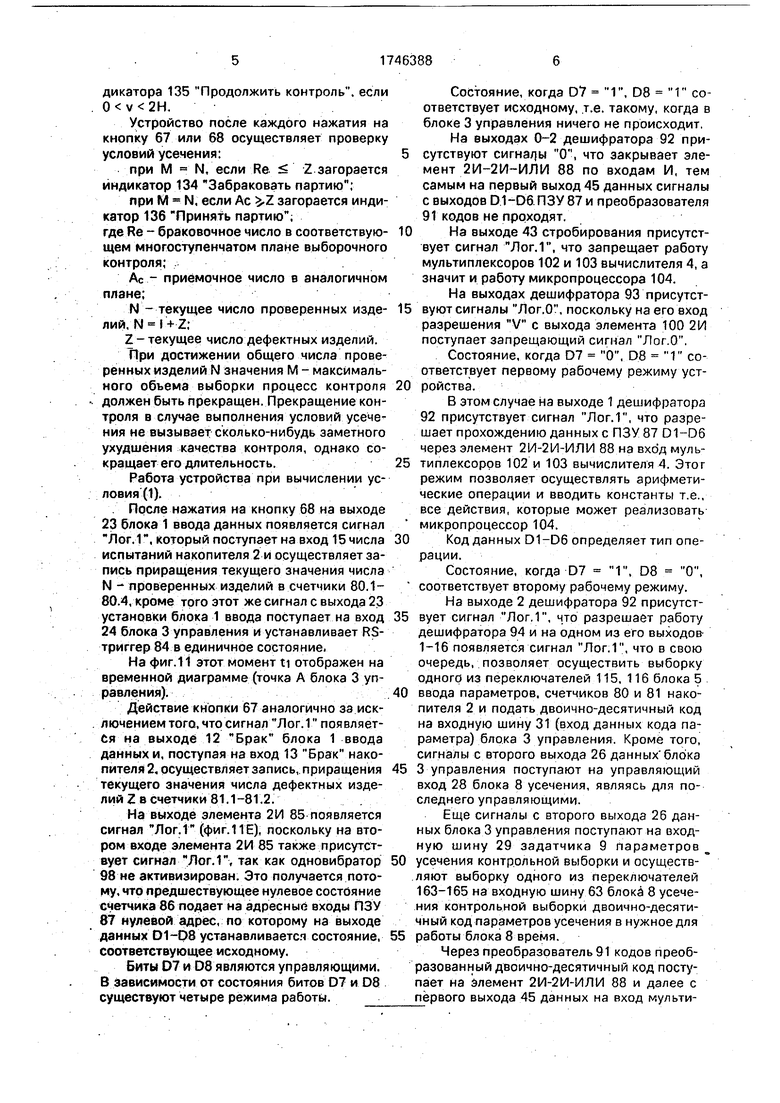

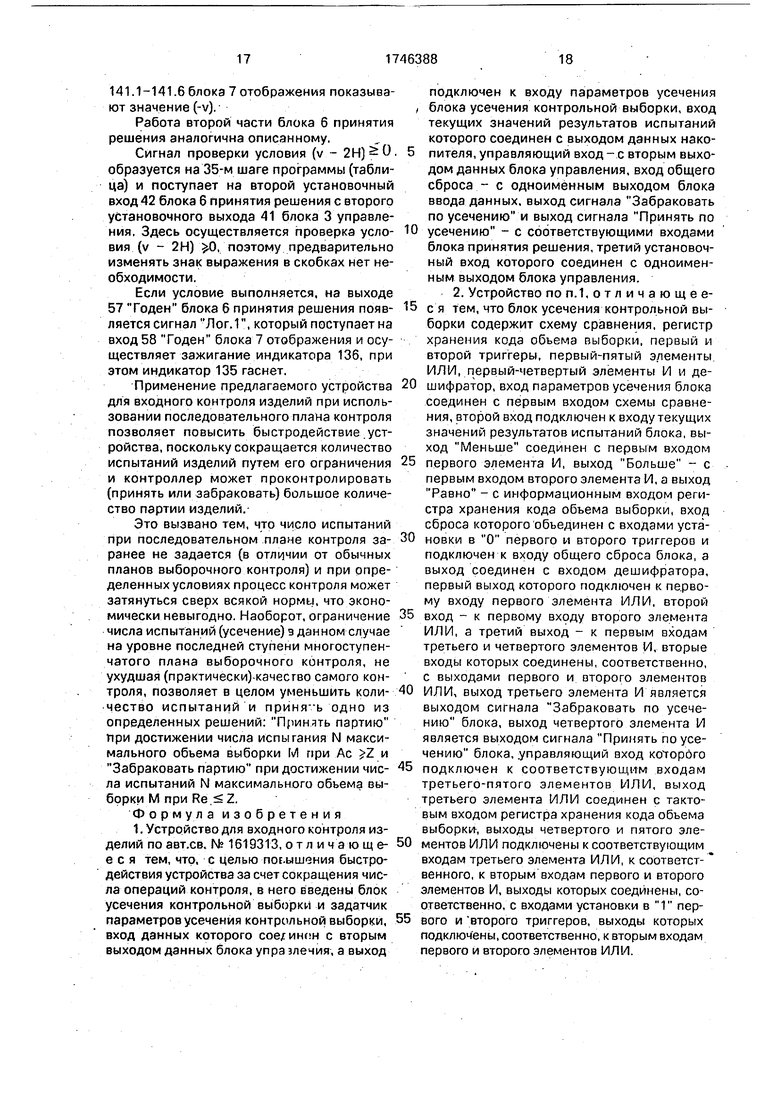

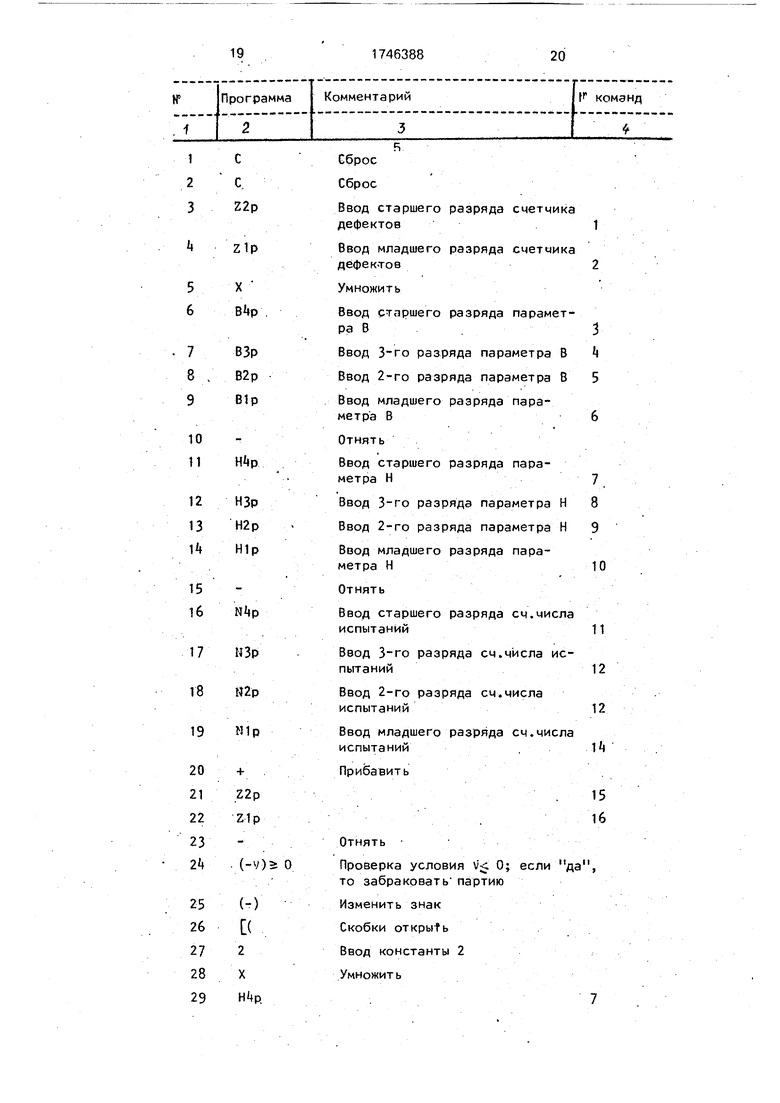

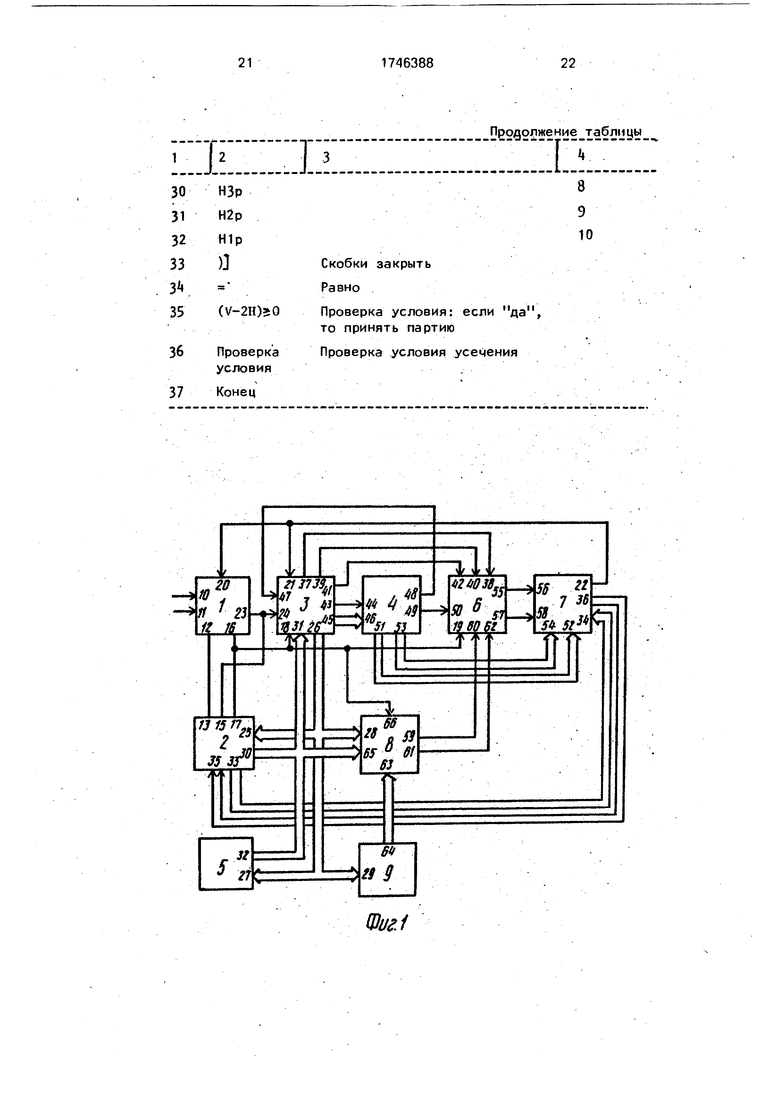

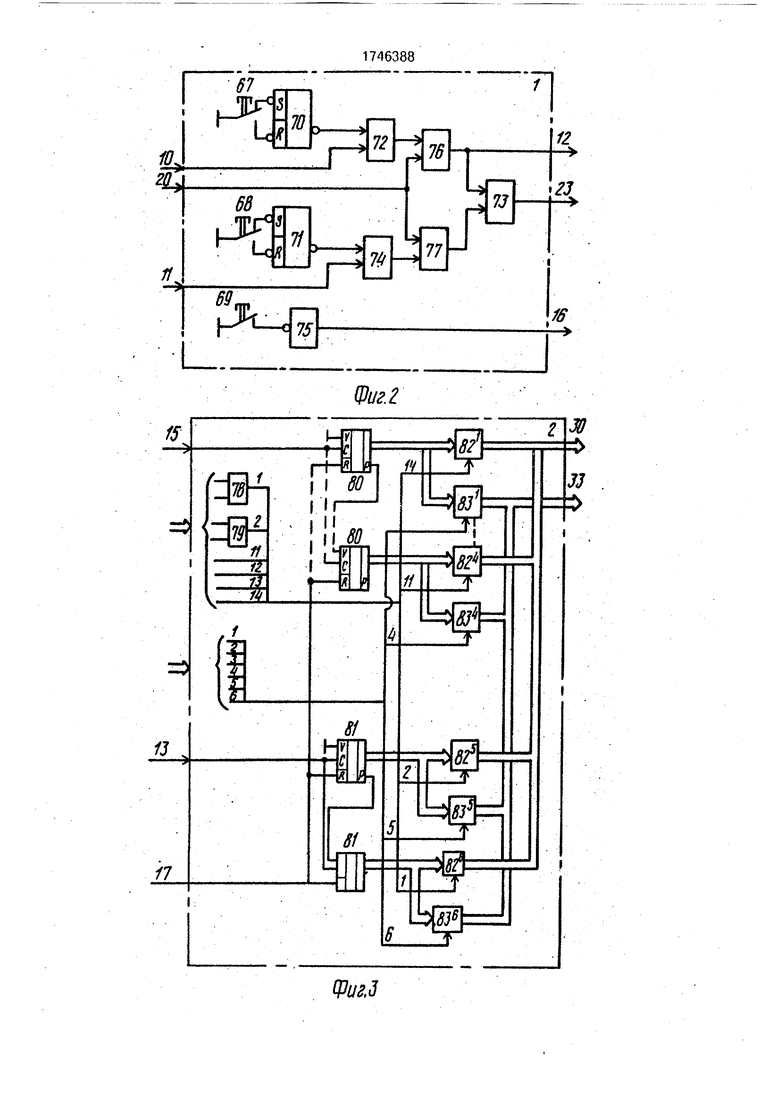

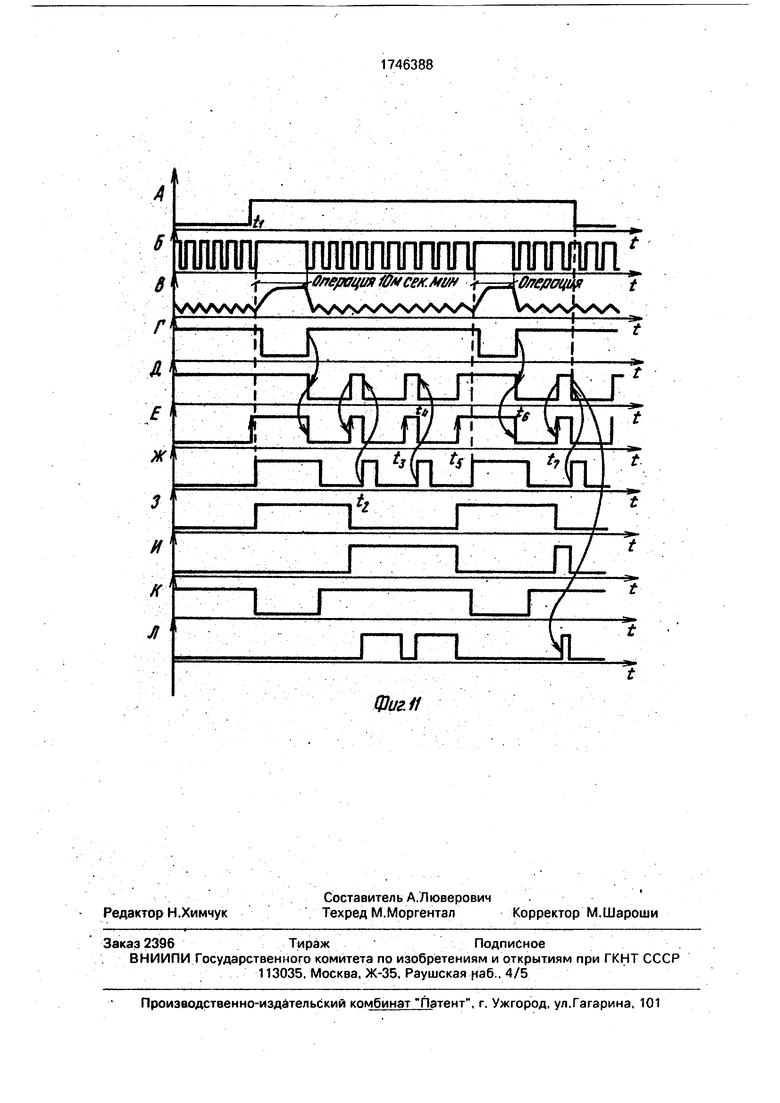

На фиг.1 представлена структурная схема устройстве для входного контроля изделий; на фиг.2 - блок ввода данных; на фиг.З - накопитель; на фиг.4 - блок управления; на фиг.5 - вычислитель плана контроля; на фиг.6 - задатчик уставок параметров; на фиг.7 - блок принятия решения; на фиг.8 - блок отображения; на фиг.9 - блок усечения контрольной выборки; на фиг, 10 - задатчик параметров усечения контрольной выборки; на фиг. 11 - временная диаграмма работы устройства.

. Устройство для входного контроля изделий (фиг.1) содержит блок 1 ввода данных, накопитель 2, блок 3 управления, вычислитель 4 плана контроля, задатчик 5 уставок параметров, блок 6 принятия решения, блок 7 отображения, блок 8 усечения контрольной выборки и задатчик 9 параметров усечения контрольной выборки.

Входы и выходы блоков и шины устройства обозначены позициями 10-66.

Блок 1 ввода данных (фиг.2) состоит из трех кнопок 67-69, двух RS-триггеров 70 и 71, тре элементов 2ИЛИ 72-74 двух элементов 2И 76 и 77 и элемента НЕ 75.

Накопитель 2 (фиг.З) состоит из двух элементов 2ИЛИ 78 и 79, двоично-десятичных счетчиков 80.1-80.4 и 81.1 -81.2, буферных схем 82.1-82.6 и 83.1-83.6.. Каждая буферная схема представляет собой четыре

2

О

w

00

со

го

элемента с тремя выходными состояниями, например, ИМС К155ЛП11.

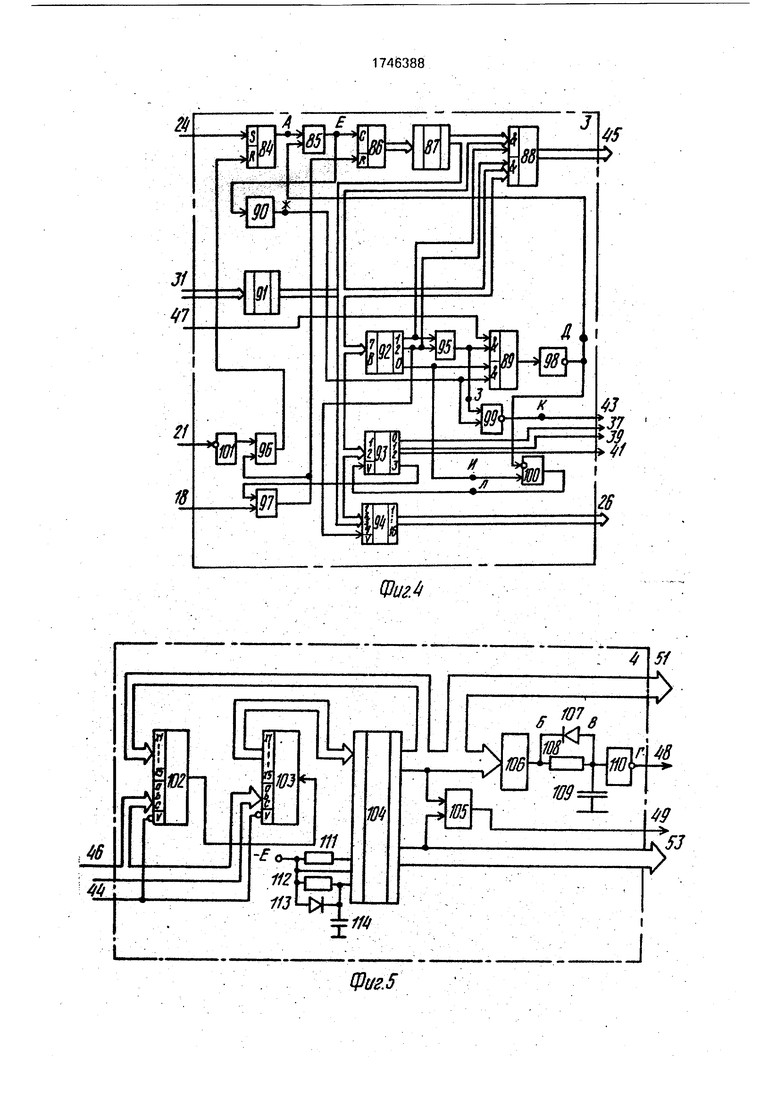

Блок 3 управления (фиг.4) состоит из RS-триггера 84, элемента 2И 85, двоичного счетчика 86, постоянного запоминающего устройства (ПЗУ) 87, элементов 2И-2И-ИЛИ 88 и 89, элемента 90 задержки, преобразователя 91 кодов, дешифраторов 92-94, элементов 2ИЛИ 95-97, одновибратора 98, элемента 2И-НЕ 99. элемента 2И 100 и инвертора 101.

Вычислитель 4 плана контроля (фиг.5) состоит из мультиплексоров 102 и 103, микропроцессора 104, элемента 2И 105, элемента 12ИЛИ10б, схемы вы работки си гнала конца операции, состоящей из диода 107, резистора 108, конденсатора 109 и одно- вибратора 110, резистора 111. задающего значение частоты внутреннего тактового генератора микропроцессора, цепочки, состо- ящей из резистора 112, диода 113 и конденсатора 114 установки микропроцессора 104 в исходное состояние.

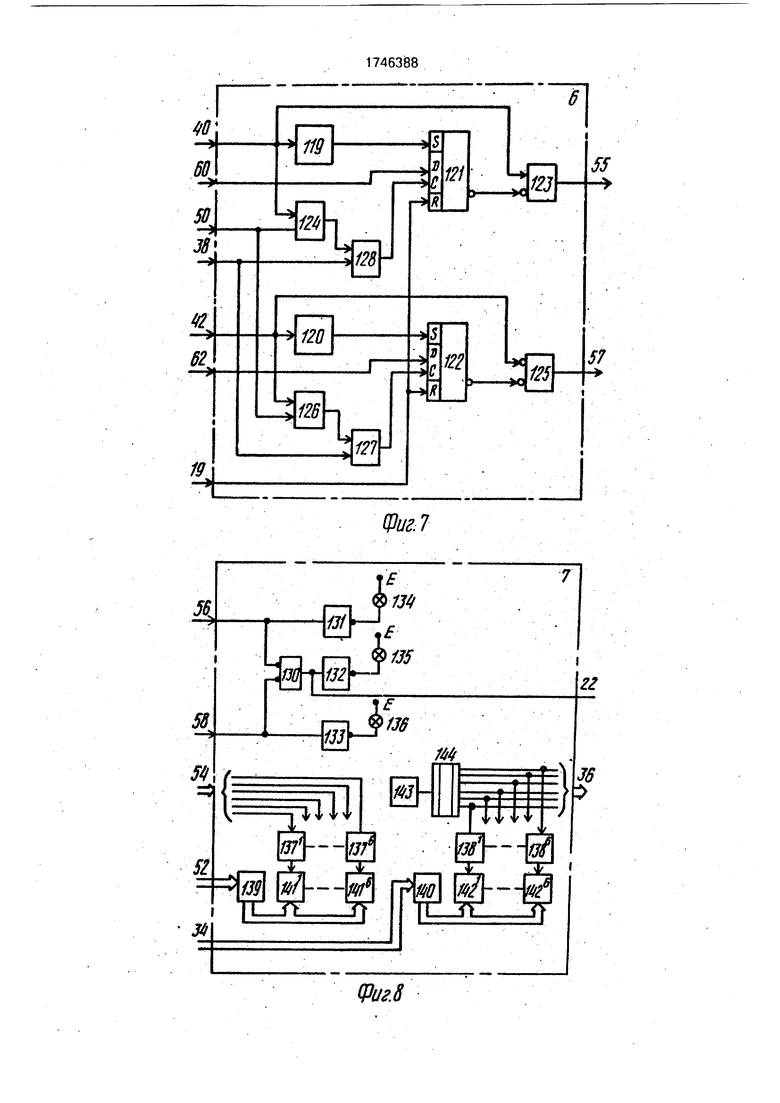

Задатчик 5 уставок параметров (фиг.6) состоит из программируемых двоично-десятичных переключателей 115.1-115.4,116.1- 116.4, и группы буферных схем 117.1-117.4, 118.1-118.4 с тремя состояниями.

Блок 6 принятия решения (фиг.7) состоит из одновибраторов 119 и 12Ь, D-тригге- ров 121 и 122. элементов 21/1 123-126. элементов 2ИЛИ 127 и 128.

Блок 7 отображения (фиг.8) состоит из элемента 2И 130, инверторов 131-133, индикаторов 134-136. разрядных ключей 137.1-137.6. 138.1-138.6, усилителей 139 и 140, семисегментных индикаторов 141.1- 141.6 и 142,1-142.6, генератора 143 и счетчика 144.

Блок 8 усечения контрольной выборки (фиг,9) состоит из схемы 145 сравнения, элементов 2ИЛИ 147-150..элемента 6ИЛИ 151. элементов 2И 152-157, элемента 4И 158, RS-триггеров 159 и 160 и регистра 161 хранения кода объема выборки. Элементы 2И 156-158 образуют схему дешифратора.

Схема 145 сравнения выполнена на ИМС К561 ИП2.

Задатчик 9 параметров усечения контрольной выборки (фиг. 10) состоит из группы буферных схем 162.1-162.8, из программируемых двоично-десятичных переключателей 163.1-163.2J64.1-164.2, 165.1-165.4... Общие выводы 1-8 буферных схем с тремя состояниями служат для организации выдачи на выходную шину 64 (выход данных) двоично-десятичного кода с одного из восьми переключателей 163, 164 и 165.

Устройство работает следующим образом.

Перед началом работы необходимо установить переключатели 115 и 116 блока 5 ввода параметров и переключатели 163, 164 и 165 задатчика 9 параметров усечения контрольной выборки в требуемое для проведения процесса .контроля положения. Для этого в зависимости от кода объема партии и приемочного уровня дефектности определяют параметры плана контроля Н и В и

максимальный обьем выборки М.

По значению М определяют Ас и Re - приемочное и браковочное числа в соответствующем многоступенчатом плане выборочного контроля,

На переключателях 115 набирают десятичное четырехразрядное число Н, на переключателях 116 - десятичное четырехразрядное число В, на переключателях 163 - десятичное двухразрядное число

Re, на переключателях 164 - десятичное двухразрядное число Ас, на переключателях 165 - десятичное четырехразрядное число М.

Затем необходимо нажать на кнопку 69

блока 1 ввода данных, чем производится . установка в нулевое состояние счетчиков 80.1-80,4 и 81.1 -81.2 накопителя 2, RS-триггера 84 и счетчика 86 блока 3 управления. D-триггеров 121 и 122 блока 6 принятия решения, RS-триггеров 159 и 160 и регистра 161 блока 8 усечения контрольной выборки..

При этом индикатор 135, отображающий директиву Продолжить контроль, го- рит, индикаторы 134 и 136, отображающие директивы соответственно Забраковать партию и Принять партию, не горят. Устройство подготовлено к работе. Из партии продукции последовательно отбирают по одной единице продукции. После контроля каждой единицы продукции контролер нажимает на одну из кнопок 67 или 68 блока 1 ввода данных в зависимости от результата контроля. На кнопку 68 нажи- мают тогда, когда проверенная единица продукции годная, на кнопку 67 - когда проверенная единица продукции дефектная.

Устройство после каждого нажатия на кнопку 67 и 68 вычисляет значение- - v(H + i)-(B-Z)(1)

где Н И В - параметры плама контроля:

I - количество годных единиц продукции после очередного акта контроля;

Z- количество дефектных единиц, продукции после очередного акта контроля-. 5 Устройство осуществляет зажигание индикатора 136 Принять партию, если v - -2Н 0, зажигание индикатора 134 Забраковать партию, если v S О, зажигание индикатора 135 Продолжить контроль, если 0 .

Устройство после каждого нажатия на кнопку 67 или 68 осуществляет проверку условий усечения:

при М N, если Re : Z загорается индикатор 134 Забраковать партию ;

при М N. если Ас ,7. загорается индикатор 136 Принять партию, где Re - браковочное число в соответствую- щем многоступенчатом плане выборочного контроля;

Ас - приемочное число в аналогичном плане;

N - текущее число проверенных изде- лий, N I + Z;

Z - текущее число дефектных изделий.

При достижении общего числа проверенных изделий N значения М - максимального объема выборки процесс контроля должен быть прекращен. Прекращение контроля в случае выполнения условий усечения не вызывает сколько-нибудь заметного ухудшения качества контроля, однако сокращает его длительность.

Работа устройства при вычислении условия (1).

После нажатия на кнопку 68 на выходе

23блока 1 ввода данных появляется сигнал Лог.1, который поступает на вход 15 числа испытаний накопителя 2 и осуществляет запись приращения текущего значения числа

N - проверенных изделий в счетчики 80.1- 80.4, кроме того этот же сигнал с выхода 23 установки блока 1 ввода поступает на вход

24блока 3 управления и устанавливает RS- триггер 84 в единичное состояние.

На фиг. 11 этот момент ti отображен на временной диаграмме (точка А блока 3 управления).

Действие кнопки 67 аналогично зз исключением того, что сигнал Лог.1 появляется на выходе 12 Брак блока 1 ввода данных и, поступая на вход 13 Брак накопителя 2, осуществляет запись, приращения текущего значения числа дефектных изделий Z в счетчики 81.1-81.2.

На выходе элемента 2И 85 появляется сигнал Лог.Г (фиг.11Е), поскольку на втором входе элемента 2И 85 также присутствует сигнал Лог.Г, так как одновибратор 98 не активизирован. Это получается потому, что предшествующее нулевое состояние счетчика 86 подает на адресные входы ПЗУ 87 нулевой адрес, по которому на выходе данных D1-D8 устанавливается состояние, соответствующее исходному.

Биты 07 и D8 являются управляющими. В зависимости от состояния битов О7 и D8 существуют четыре режима работы.

Состояние, когда D7 1, D8 1 соответствует исходному, т.е. такому, когда в блоке 3 управления ничего не происходит.

На выходах 0-2 дешифратора 92 присутствуют сигналы О, что закрывает элемент 2И-2И-ИЛИ 88 по входам И, тем самым на первый выход 45 данных сигналы с выходов D1-D6 ПЗУ 87 и преобразователя

91кодов не проходят.

На выходе 43 стробирования присутствует сигнал Лог.1, что запрещает работу мультиплексоров 102 и 103 вычислителя 4, а значит и работу микропроцессора 104.

На выходах дешифратора 93 присутствуют сигналы Лог.О, поскольку на его вход разрешения V с выхода элемента 100 2И поступает запрещающий сигнал Лог О.

Состояние, когда D7 О, D8 1 соответствует первому рабочему режиму устройства.

В этом случае на выходе 1 дешифратора

92присутствует сигнал Лог.Г, что разрешает прохождению данных с ПЗУ 87 D1-D6 через элемент 2И-2И-ИЛИ 88 на вход мультиплексоров 102 и 103 вычислителя 4. Это г режим позволяет осуществлять арифметические операции и вводить константы т.е., все действия, которые может реализовать микропроцессор 104.

Код данных D1-D6 определяет тип операции.

Состояние, когда D7 Г, D8 О, соответствует второму рабочему режиму.

На выходе 2 дешифратора 92 присутствует сигнал Лог.Г, что разрешает работу дешифратора 94 и на одном из его выходов 1-16 появляется сигнал Лог.Г, что в свою очередь, позволяет осуществить выборку одного из переключателей 115, 116 блока 5 ввода параметров, счетчиков 80 и 81 накопителя 2 и подать двоично-десятичный код на входную шину 31 (вход данных кода параметра) блока 3 управления. Кроме того, сигналы с второго выхода 26 данных блока 3 управления поступают на управляющий вход 28 блока 8 усечения, являясь для последнего управляющими.

Еще сигналы с второго выхода 26 данных блока 3 управления поступают на входную шину 29 задатчика 9 параметров в усечения контрольной выборки и осуществляют выборку одного из переключателей 163-165 на входную шину 63 блока 8 усечения контрольной выборки двоично-десятичный код параметров усечения в нужное для работы блока 8 время.

Через преобразователь 91 кодов преобразованный двоично-десятичный код поступает на элемент 2И-2И-ИЛИ 88 и далее с первого выхода 45 данных на вход мультиплексоров 102 и 103 вычислителя 4. Этим самым осуществляется ввод параметров контроля и переменных в микропроцессор 104 с блока 5 ввода параметров и с накопителя.

Состояние, когда D7 О, D8 О соответствует третьему рабочему режиму, при котором осуществляется проверка условия усечения, когда на входе 0 дешифратора 93 появляется сигнал Лог.1, условия v О, когда на выходе 1 дешифратора 93 появляется сигнал Лог.1, условия (v - 2Н) JJ 0. когда на выходе 2 дешифратора 93 появляется сигнал Лог.1 и когда на выходе 3 дешифратора 93 появляется Лог.1, это соответствует окончанию очередного цикла контроля. При этом сигнал Лог.1 проходит через элемент 21/1ЛИ 97 и устанавливает в нулевое состояние счетчик 86 и далее этот же сигнал, пройдя через элемент 2ИЛИ 96, устанавливает в нуль RS-триггер 84.

Продолжим рассмотрение работы устройства с момента, когда на выходе элемента 2И 85 появляется сигнал Лог.1.

Положительным фронтом этого сигнала счетчик 86 переключается в следующее состояние, тем самым изменяется адрес ПЗУ 87

Предположим, что по этому адресу в ПЗУ 87 записаны данные D1-D6, в соответствии с которыми должна быть выполнена какая-либо арифметическая операция, что соответствует первому рабочему режиму.

В этом случае D7 « О, D8 1. На выходе 1 дешифратора 92 появляется сигнал Лог.1, который разрешает прохождение данных D1-D6 через элемент 2И-2И-ИЛ1/1 88 по первой выходной шине 45 на входную шину 46 вычислителя 4.

На выходе элемента 2ИЛИ 95 появляется сигнал Лог,1 (фиг.И.з) подготавливая элемент 2И-НЕ 99 к выдаче стробирующего сигнала на выход 43 стробирования.

Сигнал Лог.1 с выхода элемента 2И 85 поступает на схему 90 задержки, на выходе которой этот сигнал появляется через 6 мс (фиг.11,ж).

С выходе элемента 90 задержки сигнал Лог.1 поступает на второй вход элемента 2И-НЕ 99. На выходе элемента 2И-НЕ 99 появляется-сигнал Лог.1 (фиг. 11,к), который поступает на выход 43 стробирования блока 3 управления и на вход 44 стробирования вычислителя 4:

Двунаправленные мультиплексоры 102 и 103 осуществляют подключение соответствующего выхода фазоимпульсно-кодиро- ванных разрядных сигналов к соответствующему управляющему входу микропроцессора 104 в соответствии с ко

0

5

дом на адресных входах мультиплексоров 102 и 103, чем обеспечивается выполнение микропроцессором 104 арифметических операций или операций ввода.

Микропроцессор (МП) 104 прекращает выдачу семисегментных кодов на время операции, а затем снова возобновляет. Этот момент отражен на фиг.116 на выходе элемента 12ИЛИ 106 вычислителя 4.

На вход элемента 12ИЛИ 106 поступают 12 фазоимпульсных разрядных сигналов МП 104. Для организации цикличности работы микропроцессорной БИС необходимо выделить момент окончания операции, минимальное значение длительности которой составляет 10 мс. Для этого служат резистор 108 и конденсатор 109, осуществляющие интегрирование поступающего сигнала. Параметры цепочки- R 10 кОм, С 0,32 мкФ.

Диод 107 служит для быстрого восстановления отрицательного фронта сигнала (фиг. 11,Б).

На фиг. 11.Г показан сформированный импульс, положительный фронт которого несет информацию об окончании операции. Этот импульс с выхода 48 Конец операции вычислителя 4 поступает на одноименный вход 47 блока 3 управления и на вход элемента 2И-2И-ИЛЙ 89, а с его выхода на вход одновибратора (ОВ) 98, который запускается положительным фронтом импульса (фиг.11,Д). Длительность импульса, вырабатываемого ОВ 98 равна 12 х Тр 12 х 410 мс 5 мс, и выбрана такой с тем, чтобы МП 104 полностью закончил выработку результата.

Здесь Тр - длительность периода одного разрядного сигнала.

Импульс с выхода ОВ 98 поступает на второй вход элемента 2И 85. с выхода которого этот импульс поступает на вход счетчика 86. Положительный фронт импульса вызывает срабатывание счетчика 86, осуществляя приращение его содержимого на 5 единицу (фиг. 11,Е).

ПЗУ 87 с выхода счетчика 86 поступает следующий адрес. Управляющие биты ПЗУ 87 D7 и D8 реализуют один из трех рабочих режимов.

В случае, когда реализуются первые два рабочих режима, работа устройства аналогична описанному.

Рассмотрим теперь переход к третьему рабочему режиму, который характеризуется тем, что при этом режиме осуществляются операции проверки.

Управляющие биты D7 и D8 ПЗУ 87 принимают нулевое значение. На выходе О дешифратора 92 появляется сигнал Лог.1 .11,И), который разрешает прохожде

0

5

0

5

0

0

5

ние сигнала с выхода схемы 90 задержки .через элемент 2И-2И-ИЛИ 89 (фиг.11.Ж, момент времени tp. Сигнал с выхода элемента 2И-2И-ИЛИ 89 положительным фронтом запускает бдновибратор 98. Сигнал с выхода 0В 98 (фиг. 11 ,Д) поступает на вход элемента 2И 100, с выхода которого стробирующий сигнал поступает на вход разрешения V дешифратора 93 (фиг.11 ,Д).

Дешифратор 93 в зависимости от данных на его информационных входах, выдает на свои выходы 0-3 один из управляющих сигналов : усечения, проверки или останова.

Сигнал с выхода 0В 98 поступает также на второй вход элемента 2И 85. С выхода элемента 2И 85 сигнал поступает на счетный вход счетчика 86 и положительным фронтом осуществляет приращение на единицу его содержимого (фиг.11Е, момент т.з).

Для наглядности на временной диаграмме (фиг.11. моменты времени ) изображена выработка двух подряд управляющих сигналов на установочных выходах 37 или 39 или 41 блока 3 управления, т.е. когда устройство дважды обращается к третьему рабочему режиму. ,

Содержимое ПЗУ 87, соответствующее очередному адресу таково, что D7 D8 О. На выходе 0 дешифратора 92 снова присутствует Лог. 1. Элемент2И 100 снова подго- товлен-к разрешению прохождения сигнала с выхода элемента 90 задержки.

В момент времени и (фиг.11,Д) 0В 98 вырабатывает очередной импульс, который пройдя элемент 2И 85, вызывает очередное приращение счетчика 86 (фиг.11,Е, момент времени ts).

Предположим-, что новое содержимое ПЗУ 87, соответствующее очередному адресу, таково, что D7 1, D8 О, что соответствует второму рабочему режиму. На выходе 2 дешифратора 92 будет сигнал Лог.1, который разрешает прохождение через элемент 2И-2И-ЙЛИ 88 на первый выход 45 данных сигналов с выхода преобразователя 91 кодов.

Сигнал с выхода 2 дешифратора 92 поступает также на стробирующий вход V дешифратора 94, на одном из выходов 1-16 которого появляется сигнал Лог.1,

С второго выхода 26 данных блока 3 управления-сигналы с дешифратора 94 поступают на первый вход 25 данных накопителя 2, на вход 27 данных блока 5 ввода параметров, на управляющий вход 28 блока 8 усечения и на вход 29 данных задатчика 9 параметров усечения.

Этим самым на входе 31 данных кода параметра блока 3 управления появляется код выбранного параметра Н, В или переменных N, Z. Кроме того сигналы с второго выхода 26 блока 3 управления поступают на управляющий вход 28 блока 8 усечения и на вход 29 данных задатчика 9 параметров усе- 5 чения,

На входе элемента 2ИЛИ 95 появляется сигнал Лог.1 (фиг. 11,3). подготавливая элемент2И-НЕ 99 к прохождению сигнала с выхода элемента 90 задержки (фиг. 11,Ж).

10 При совпадении этих сигналов по времени на выходе элемента 2И-НЕ 99 появляется стробирующий сигнал (фиг.11,К), который с выхода 43 стробирования поступает на вход 44 стробирования вычислителя 4,

5 Мультиплексоры 102 и 103 вычислителя 4 осуществляют соединение в соответствии с калькуляторным кодом управляющих сходов с фазоимпульсными разрядными выходами., МП 104 прекращает выдачу

0 семисегментных кодов и осуществляет операцию ввода (фиг.11,Б).Сформированный импульс с выхода 48 Конец операции вычислителя 4 (фиг.11,Г) поступает на элемент 2И-2И-ИЛИ 89.

5 Сигнал Лог.1 с выхода элемента 2И- 2И-ИЛИ 89 поступает на вход 0В 98 и запускает его (фиг.11,Д, момент времени te).

Импульс с выхода 0В 98 поступает на второй вход элемента 2И 85, сигнал с выхо0 да которого поступает на счетный вход счот- чика 86 и вызывает приращение его содержимого на единицу (фиг.11.Е, момент времени t).

5 Содержимое ПЗУ 87. соответствующее очередному адресу, теперь таково, что D7 - D8 О. На выходе 0 дешифратора 92 присутствует сигнал Лог. 1 (фиг. 11 ,И).

Сигнал с выхода элемента 90 задержки

0 меняет свое состояние с Лог.О на Лог.1 (фиг, 11 .Ж) и поступает на вход элемента 21Л- 2И-ИЛИ 89, с выхода которого поступает на вход 0В 98 и положительным фронтом сигнала запускает его (фиг.11,Д). Отрицатель5 ный фронт сигнала с выхода 0В 98 поступает на вход элемента 2И 100, с выхода которого сигнал поступает на стробирующий вход V дешифратора 93 (фиг.11,Д). Рассматриваемый режим является третьим

0 рабочим, причем примем, что вырабатыва- „ ется сигнал окончания. В этом случае на выходе 3 дешифратора 93 появляется сигнал Лог.1, который поступает на вход элемента 2ИЛИ 97, с выхода которого сигнал

5 Лог. 1 поступает на вход установки в нулевое состояние - исходное счетчика 86 и на вход элемента 2ИЛИ 96, с выхода которого сигнал Лог.1 поступает на R-вход RS-триг- гера 84 и устанавливает его в нулевое состо- яние (фиг. 11,А).

ПЗУ 87 выдает на управляющие выходы О7и D8 сигналы Лог.1. что вызывает появление сигнала Лог.О на выходе дешифратора 92, а, следовательно, на выходе элемента 2И 100 возникает сигнал Лог.О (фиг.11,И,Л).

Сигнал с выхода 0В 98 поступает на вход элемента 2И 85. Однако, теперь элемент 2И 85 закрыт для прохождения положительного фронта сигнала с выхода ОВ 98 потому, что на втором его входе присутствует сигнал Лог.О,

Работа схемы приостанавливается. МП 104 продолжает генерацию семисегмент- ных кодов, обеспечивания индикацию на индикаторах 141.1-141.6 текущего результата очередного акта контроля, в данном случае (v - 2Н).

Работа блока 8 усечения.

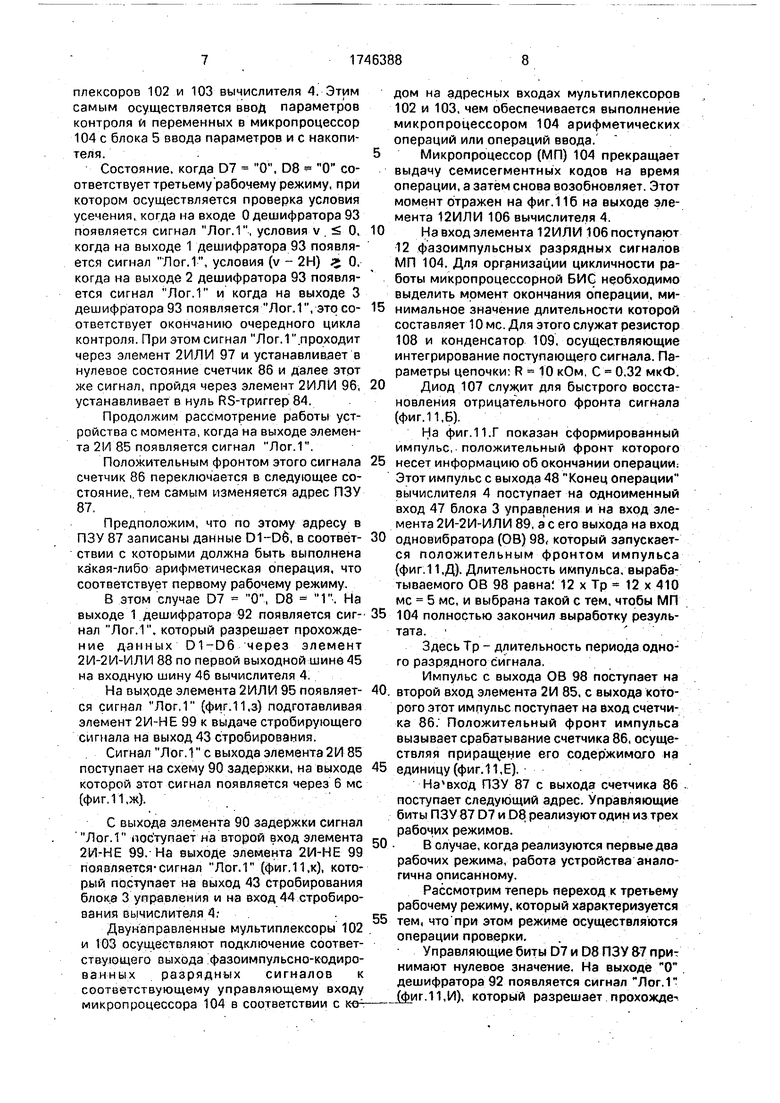

В соответствии с управляющей программой, записанной в ПЗУ 87 блока 3 управления, устройство шаг за шагом осуществляет вычисление формулы (1). Вся программа, записанная в управляющем ПЗУ 87, составляет37 шагов. В таблице приведена программа.

Проверка условий усечения осуществляется на 36-м шаге программы. Используя те же управляющие сигналы, которые вырабатываются дешифратором 94 блока 3 управления и служащие по основному своему назначению для организации вычисления формулы (1), можно осуществлять проверку условия усечения.

В процессе выполнения программы соответствующие тетрады двоично-десятичных слов последовательно появляются на двух шинах: шине 63 параметров усечения и шине 65 текущих значений результатов испытаний бгока 8 усечения контрольной выборки. К этим шинам подключена схема 145 сравнения, осуществляющая сравнение двух слов, которые поступают на ее входы и вырабатывающая сигналы Больше, Меньше или Равно.

Последовательный способ обработки информации не лозволяет определить равенство двух слов только по одному разряду. Необходимо, чтобы были равны между собой все разряды слова. Это достигается введением регистра 161 хранения кодаобь- ема выборки и элементов 2И 156 и 157 и элемента 4И158, образующих схему дешифратора.

RS-триггеры 159 и 160 служат для временного запоминания соответствующих условий Больше или Меньше.

На третьем шаге программы (таблица) дешифратора 94 команд блока 3 управления вырабатывает на своем первом выходе сигнал Лог.Г, соответствующий первой команде: Вводг2р.

Этот сигнал, входящий во вторую шину 26 данных блока 3 управления, поступает на

первую входную шину 25 накопителя 2 и включает буферные схемы 82.6, в связи с чем на первой выходной шине 30 накопителя 2 появляется значение Z2p - старший разряд счетчика дефектов и осуществляется

0 его ввод через входную шину 32 блока 3 управления и далее через первую выходную шину 45 в вычислитель 4.

В то же время значение Z2p появляется на входной шине 65 блока 8 усечения

5 контрольной выборки. В то же время сигнал Лог.1 с первого выхода дешифратора 94 команд блока 3 управления поступает через входную шину 29 за датчика 9 параметров усечения контрольной выборки и активизи0 рует буферную схему 162.1, что позволяет выдать на шину 64 значение Re2p - старший разряд браковочного числа, установленного на переключателе 163.1.

На входе 63 параметров усечения блока

5 8 появляется значение Re2p. Схема 145 сравнения производит сравнение двух слов: Z2p и Re2p. Выход Меньше схемы 145 сравнения подключен к одному из входов элемента 2И 152. Выход Больше схемы

0 145 сравнения подключен к одному из входов элемента 2И 153. Выход Равно подключен к информационному входу (D-входу) регистра 161.

С небольшой задержкой (на фиг.9 не

5 показано) управляющие сигналы поступают с дешифратора 94 команд блока 3 управления на управляющий вход 28 блока 8 усечения контрольной выборки. В данном случае сигнал Лог. Г, соответствующий все той же

0 первой команде, поступает на первый выход элемента 2ИЛИ 147 и далее на другой вход элемента 2И 152.

Если выполняется условие Re2p Z2p, то на выходе элемента 2И 152 появляется

5 сигнал Лог.1, устанавливающий RS-триг- гер в единичное состояние,

В то же время сигнал Лог.1, соответствующий первой команде, поступает на первый вход элемента 6ИЛИ 151 и далее на

0 тактовый вход (С вход) регистра 161. Если выполняется условие Re2p Z2p, то на D- входе регистра 161 будет присутствовать сигнал Лог. Г и с приходом сигнала на тактовый вход, на первом его выходе запишет5 ся сигнал Лог.1.

Если условие Re2p Z2p не выполняется, тогда на выходе элемента 2И 152 будет присутствовать сигнал Лог.О и RS-триггер 159 останется в нулевом состоянии. Если не выполняется условие Re2p Z2p. тогда на

первом выходе регистра 161 будет присутствовать сигнал Лог..

Далее поступает вторая команда (4-й шаг программы по таблице). Дешифратор 94 блока 3 управления вырабатывает на своем втором выходе сигнал Лог. Г, соответствующий второй команде Ввод Zip. В результате на входных шинах 63 и 65 блока 8 появляются значения Re1p и Zip.

Как и ранее, задержанный сигнал Лог. Г, соответствующий второй команде, поступает на второй вход элемента 2ИЛИ 147. Происходят действия, аналогичные описанным: проверяется условие Re1 р Z1 р и если ранее оно не выполнялось, а сейчас выполняется, то в RS-триггер 159 записывается Лог. Г.

Если выполняется условие Re1p « Zip: на первом выходе регистра 161 появляется Лог.1, а предыдущая информация либо Лог.1 либо Лог.О сдвигается на один шаг вправо, т.е. в сторону старших разрядов регистра и появляется на его втором выходе.

На этом проверка условия Re Z закончена и результат зафиксирован в RS-тригге- ре 159. Результат проверки условия Re Z хотя и зафиксирован в регистре 161, однако он появляется на выходе элемента 2И 157 только через шесть последующих тактов (поскольку информация постоянно сдвигается), а именно, после выполнения 16-й команды (22-й шаг программы по таблице) и к 36-му шагу программы, когда производится проверка результата контроля по усечению на выходе элемента 149 будет сформирован результат проверки условия Re Z, а на выходе элемента 2И 154 к этому условию добавится еще условие М N.

Это условие реализуется следующим образом.

Устройство последовательно выполняет программу и на 16-19 шагах осуществляется ввод N - числа испытаний со счетчиком 80.1-80.4 накопителя 2 в блок 3 управления. Одновременно, на выходе 64 данных задат- чика 9 параметров усечения контрольной выборки появляются значения М - максимального объема выборки, установленные на переключателях 165.1-165.4.

На шинах 63 и 65 блока 7 усечения контрольной выборки появляются разряд за разрядом в двоично-десятичном коде, начиная со старшего, величины М и N соответственно. На входы 11-14 элемента 151 поступают .последовательно сигналы Лог.1, соответствующие командам с 11-й по 14-тую включительно (соответствуют шагам 16-19 программы).

На D-входе регистра 161 последовательно появляются результаты сравнения

чисел М и N, которые заносятся в регистр и сдвигаются вправо по сигналам на его тактовом входе.

После 16-й команды на выходе элемента 5 4И 158 будет сформирован результат проверки условия М N.

И, наконец, сигналы Лог.1-, появляющиеся на входе элемента 2ИЛИ 148, соответствующие 15-й и 16-й командам. 10 осуществляют проверку условия Ас Z.

На шинах 63 и 65 блока 8 появляются последовательно старший и младший разряды чисел Ас и Z соответственно

В RS-триггер 160 будет занесен резуль- 15 тат проверки условия Ас Z. Если условие выполняется,.тогда триггер будет установлен в единичное состояние, если нет - останется в нулевом.

На.выходе элемента 2И 156 появляются 0 результат проверки Ас Z, а на выходе элемента 2 ИЛ И 150-Ас 2:7.

На выходе элемента 2И 156 и последнему условию добавляется еще условие М N. Таким образом, на выходе 59 Забрако- 5 вать партию по усечению блока 8 усечения контрольной выборки будет сформировано условие Re z при М N, что соответствует условию забракованию партии (по усечению), а на выходе 61 Принять партию по 0 усечению будет сформировано условие Ас5 ЈZ при М N, что соответствует условию (по усечению).

Работа блока 6 принятия решения. В соответствии с управляющей про- 5 граммой, записанной.в ПЗУ 87 блока 3 управления, на 36-м шаге программы (таблица) на 0 выходе дешифратора 93 появляется сигнал Лог. 1й - сигнал проверки условия усечения.

0 с третьего установочного выхода 37 блока 3 управления этот сигнал поступает на третий установочный вход 38 блока 6 принятия решения.

На D-входах триггеров 121 и 122 (входы 5 60 и 62) к этому моменту времени присутствуют сигналы, соответствующие условиям забракованию или принятию партии по усечению. Эти сигналы поступают на входы 60 и 62 блока 6 принятия решения с выходов 59 0 и 61 соответственно блока 8 усечения конт- „ рольной выборки.

Сигнал проверки условия усечения проходит через элемент 2ЙЛИ 128 и через элемент 2ЙЛИ 127, поступает на С-входы 5 D-триггеров 121 и 122 соответственно и осуществляет в них запись результатов проверки условий усечения.

.Если.одно из условий усечений выполнилось, то в один из D-триггеров будет за- писана Лог.1.

На одном из выходов элементов 2И 123 ли 125 появится сигнал Лог.1.

Если условия усечения не выполняются, огда на выходах элементов 2И 123 и 125 удут сохраняться сигналы Лог.О. В этом 5 лучае ничего не произойдет и устройство продолжит выполнять программу и на 37-м шагу закончит свою работу.

Если на одном из выходов 55 Брак или 57 Годен появится сигнал Лог.1, то он Ю появится также на одном из входов 56 Брак или 58 Годен блока 7 отображения, что приведет к загоранию одного из индикаторов 134 или 136 (в зависимости от результата) и к тому, что индикатор 135 погаснет. 15

На выходе элемента 2И 130 блока 7 отображения появляется сигнал Лог.0, который с выхода 22 Общей блокировки поступает на вход 21 блокировки блока 3 управления и на вход 20 блокировки блока 20 1 ввода данных, что блокирует работу последнего, поскольку элементы 2И 76 и 77 блока 1 оказываются закрытыми и сигналы кнопок 67 и 68 не проходят на выходы 12 Брак и 23 установки.25

Сигнал Лог.О проходите входа21 блока 3 управления через инвертор 101, элемент 2ИЛИ 96, с выхода которого поступает на R-вход RS-триггера 84 и устанавливает его в нулевое состояние. Элемент 2И 85 30 оказывается закрытым и не пропускает на свой выход сигнал с выхода 0В 98.. Устройство приостанавливает свою работу.

Индикаторы 142.1-142.6 показывают текущее значение величин N и Z.35

На 23-м шаге программы (таблица) осуществилось вычисление значения (-v), тогда на 24-м шаге на 1 выходе дешифратора-93 блока 3 управления появляется сигнал Лог.1 - сигнал проверки условия v S- 0. 40

Первый разрядный фазоимпульсный сигнал совместно с одним из сегментных сигналов на выходах МП 104 вычислителя 4 определяет знак результата вычисленного значения, причем первый сигнал перекры- 45 оает по времени второй. Длительность первого 400 мкс. а второго 300 мкс.

При наличии знака минус на выходе элемента 2И 105 вычислителя 4 появляется положительный импульс. 50

При наличии положительного числа или нуля сигнал на выходе элемента 2И 105 отсутствует. Поэтому осуществить проверку 0 напрямую затруднительно.

Для реализации проверки условия v :Ј 0 55 производится эквивалентная проверка (-v)# ;jO. Изменение знака числа v производится предварительно в программе,

На первый установочный вход 40 блока 6 принятия решения поступает сигнал

Лог.1 с первого установочного выхода 39 блока 3 управления. Этот сигнал поступает на первый вход элемента 2И 123 и запрещает его работу на все время действия сигнала.

На фиг. 11 .Д первые два положительных импульса соответствуют длительности импульсов проверки условий.

Этот же сигнал поступает на вход одно- вибратора 119, с выхода которого короткий положительный импульс устанавливает D- триггер 121 в единичное состояние, так как предварительно он был установлен в нулевое состояние по входу 19 Общий сброс. Этим самым осуществляется проба - проверка условия (-v) 0.

На вход 50 Знак операнда блока 6 принятия решения поступает импульс знака минус с выхода 49 Знак операнда вычислителя 4.

Если знак минус отсутствует, на выходе элемента 2И 124 положительный импульс знака будет на время действия импульса проверки условия отсутствовать. Триггер 121 сохранит свое единичное состояние и по окончании сигнала на втором входе 35 данных на выходе элемента 2И 123 сформируется сигнал Лог.1, который будет соответствовать условию (-v). 0. т.е. v 0. Если знак минус на входе 50 Знак операнда будет присутствовать, то. с выхода элемента 2И 124 через элемент 2ИЛИ 128 поступит положительный импульс на счетный вход триггера 121 и установит его в нулевое состояние, так как на его D-входе постоянно присутствует сигнал Лог.О.

По окончании сигнала проверки на первом установочном входе 40 «а выходе элемента 2И 123 сформируется сигнал Лог.О, который будет соответствовать условию (-v) 0, т.е. v 0.

Сигнал Лог.1 с выхода 55 Брак блока 6 принятия решения поступает на вход 56 Брак блока 7 отображения и вызывает загорание индикатора 134, индикатор 135 при этом гаснет.

На выходе элемента 2И 130 появляется сигнал Лог.О, который поступает на выход 20 блокировки блока 1 ввода данных. Элементы 2И 76 и 77 оказываются заблокированными и не пропускают сигналы с элементов ИЛИ 72 и 73. Это сделано для того, чтобы исключить случайные действия оператора для сохранения результата.

Кроме того, сигнал с выхода 22 Общей блокировки блока 7 отображения поступает на вход 21 блокировки блока 3 управления, что вызывает установку RS-триггера 84 в нулевое состояние, который останавлива- ет работу блока 3 управления. Индикаторы

141.1-141.6 блока 7 отображения показывают значение (-v).

Работа второй части блока б принятия решения аналогична описанному.

Сигнал проверки условия (v - 2Н) - 0 образуется на 35-м шаге программы (таблица) и поступает на второй установочный вход 42 блока 6 принятия решения с второго установочного выхода 41 блока 3 управления. Здесь осуществляется проверка уело- вия (v - 2Н) Ј0, поэтому предварительно изменять знак выражения в скобках нет необходимости.

Если условие выполняется, на выходе 57 Годен блока 6 принятия решения появ- ляется сигнал Лог. 1, который поступает на вход 58 Годен блока 7 отображения и осуществляет зажигание индикатора 136, при этом индикатор 135 гаснет.

Применение предлагаемого устройства для входного контроля изделий при использовании последовательного плана контроля позволяет повысить быстродействие устройства, поскольку сокращается количество испытаний изделий путем его ограничения и контроллер может проконтролировать (принять или забраковать) большое количество партии изделий.

Это вызвано тем, что число испытаний при последовательном плаче контроля за- ранее не задается (в отличии от обычных планов выборочного контроля) и при определенных условиях процесс контроля может затянуться сверх всякой нормы, что экономически невыгодно. Наоборот, ограничение числа испытаний (усечение) з данном случае на уровне последней ступени многоступенчатого плана выборочного контроля, не ухудшая (практически) качество самого контроля, позволяет в целом уменьшить коли- чество испытаний и приня ь одно из определенных решений: Принять партию при достижении числа испытания N максимального объема выборки М при Ac Z и Забраковать партию при достижении чис- ла испытаний N максимального объема выборки М при Re Z.

Формула изобретения

1. Устройство для входного контроля изделий по авт.св, № 1619313, отличающе- е с я тем, что, с целью ПОЕ. быстродействия устройства за счет сокращения числа операций контроля, в него введены блок усечения контрольной выборки и задатчик параметров усечения контрольной выборки, вход данных которого сое/инпн с вторым выходом данных блока упра злечия, а выход

подключен к входу параметров усечения блока усечения контрольной выборки, вход текущих значений результатов испытаний которого соединен с выходом данных накопителя, управляющий вход - с вторым выходом данных блока управления, вход общего сброса - с одноименным выходом блока ввода данных, выход сигнала Забраковать по усечению и выход сигнала Принять по усечению - с соответствующими входами блока принятия решения, третий установочный вход которого соединен с одноименным выходом блока управления.

2. Устройство по п. 1,отличающе е- с я тем, что блок усечения контрольной выборки содержит схему сравнения, регистр хранения кода объема выборки, первый и второй триггеры, первый-пятый элементы ИЛИ, первый-четвертый элементы И и дешифратор, вход параметров усечения блока соединен с первым входом схемы сравнения, второй вход подключен к входу текущих значений результатов испытаний блока, выход Меньше соединен с первым входом первого элемента И, выход Больше - с первым входом второго элемента И, а выход Равно - с информационным входом регистра хранения кода объема выборки, вход сброса которого объединен с входами установки в О первого и второго триггеров и подключен к входу общего сброса блока, а выход соединен с входом дешифратора, первый выход которого подключен к первому входу первого элемента ИЛИ, второй вход - к первому входу второго элемента ИЛИ, а третий выход - к первым входам третьего и четвертого элементов И, вторые входы которых соединены, соответственно, с выходами первого и второго элементов ИЛИ, выход третьего элемента И является выходом сигнала Забраковать по усечению блока, выход четвертого элемента И является выходом сигнала Примять по усечению блока, управляющий вход которйго подключен к соответствующим входам третьего-пятого элементов ИЛИ, выход третьего элемента ИЛИ соединен с тактовым входом регистра хранения кода объема выборки, выходы четвертого и пятого элементов ИЛИ подключены к соответствующим входам третьего элемента ИЛИ, к соответст- венного, к вторым входам первого и второго элементов И, выходы которых соединены, соответственно, с входами установки в 1 первого и второго триггеров, выходы которых подключены, соответственно, к вторым входам первого и второго элементов ИЛИ.

J

1131 Ж,

j Z

J. gj//rj-

4f

и

#

« 57

ggg/

Iff « 7 J5

-

J-«57

Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для входного контроля изделий | 1989 |

|

SU1619313A1 |

| Многоканальное устройство тестового контроля логических узлов | 1990 |

|

SU1837295A1 |

| Устройство для входного контроля | 1985 |

|

SU1298769A1 |

| Репродукционный фотоаппарат | 1987 |

|

SU1633372A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1583757A1 |

| Устройство для отображения символьной информации на экране видеоконтрольного блока | 1991 |

|

SU1836678A3 |

| Делитель частоты с переменным дробным коэффициентом деления | 1989 |

|

SU1746530A1 |

| Устройство для тренировки памяти обучаемого | 1988 |

|

SU1531125A1 |

| Устройство для формирования тестов памяти | 1989 |

|

SU1711235A1 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СЕЙСМОРАЗВЕДОЧНАЯ СИСТЕМА | 1994 |

|

RU2107312C1 |

Изобретение относится к автоматике, мджет быть применено при входном контроле изделий на производстве и является усовершенствованием устройства по авт.св. № 1619313. Цель изобретения - повышение быстродействия за счет сокращения числа операций контроля. Устройство содержит блок ввода данных, накопитель, предназначенный для подсчета общего числа проверенных изделий и числа дефектных изделий, блок управления, вычислитель плана контроля для проведения вычислений над двоично-десятичными числами, задатчик контроля параметров, блок принятия.реше- ний, выдающий на основе обработанной информации сигналы, соответствующие директивным указаниям Принять партию или 3абраковать партию, блок отображения, блок усечения контрольной выборки, формирующие сигналы, соответствующие забракованию и принятию партии (по усечению) соответственно, и задатчик парамшя.-1 ров усечения контроля контрольной выработки. 1 з.п. ф-лы. 11 ил., 1 табл. у Ё

ute/

2 Ы&

88С9Ш

tt

ргпф

88С9Ш

V

г 7

MM

/

-tЈЈj

jЈ

--X.,0 9ft

Ш

htvr

jL. r-,-x,

F

,///

-«

rtvrlj

Ш J

i

.1

L

t

It

-г Ш Ј

,SV

JL /

t

nirdJ

88C9t il

Фиг. 7

Фиг.8

6L 65

Я5

Ц№ 15

Cjf

Шп

ft я

13м151

UJ

iS

59

г

-

150

81

а,

Фиг. 10

#«.//

| Устройство для входного контроля изделий | 1989 |

|

SU1619313A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-07-07—Публикация

1990-01-11—Подача