ройства. Вход 9 синхронизации записи служит входом устройства.

Работа ОЗУ заключается в следующем.

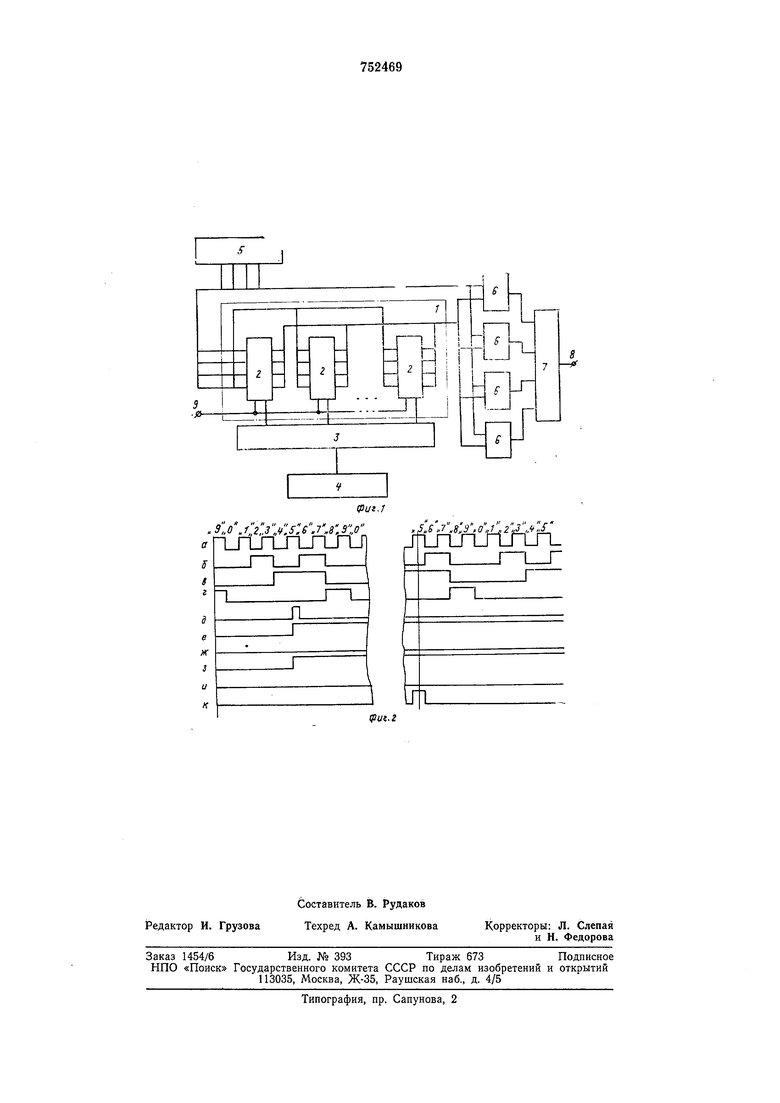

Генератор 5 импульсов выдает циклически комбинации потенциалов, например, на четырех выходах в двоично-десятичном коде (см. фиг. 2,а-г). Смена кодовой комбинации производится с частотой в десять раз большей, чем частота следования сигналов входного фазоимпульсного кода с десятичным кодированием, подаваемых на вход 9. При записи информации в накопитель 1 с регистра 4 адреса поступает сигнал и дешифратор 3 подключает входы определенной группы двоичных запоминаюш,их элементов 2 к входу 9. Сигнал входного фазоимпульсного кода (см. фиг. 2,) по входу 9 обеспечивает запись в двоичные запоминаюш,ие элементы 2 накопителя 1 той комбинации (см. фиг. 2, е-и), которая в данный момент образовалась на выходах генератора 5 импульсов.

При считывании ипформации по адресу выбирается группа двоичных запоминаюш,их элементов 2 и их выходы подключаются к выходам накопителя 1. При совпадении кодовой комбинации (см. фиг. 2, а-г и фиг. 2, д-з) на входах сумматоров б по модулю два на выходе элемента И 7 появляется сигнал в фазоимпульсном коде (см. фиг. 2, к). На приведенных диаграммах изображен случай, когда записано и считано число «5 в десятичной системе счисления в фазоимпульсном коде.

ОЗУ может работать с разным основанием системы счисления, которая определяется системой счисления фазоимпульсного кода, цикличностью повторения кодовых комбинаций на выходах генератора и не зависит от вида кода ( или «1 - «2 - «4 - «2 и т. д.).

Устройство может быть реализовано на основе интегральных схем (ИС) серий 155, 133, 505, 176, 527 и т. д. В качестве генератор.а импульсов может быть использована декада К155ИЕ2, в качестве накопителя - К155РУ2, а в качестве сумматоров - К155ЛРЗ.

Описанное устройство позволяет существенно уменьшить число ИС и увеличить надежность оперативного запоминающего устройства с фазоимпульсным представлением информации.

Формула изобретения

Оперативное запоминающее устройство, содержащее накопитель, дешифратор адреса и регистр адреса, причем входы дешифратора адреса подключены к выходам регистра адреса, а выходы - к одним из входов накопителя, отличающееся тем, что, с целью упрощения устройства и повышения его надежности, оно содержит

генератор импульсов, сумматоры по модулю два и элемент И, причем одни из входов сумматоров по модулю два подключены к выходам накопителя, выходы генератора импульсов соединены с другими входами накопителя и другими входами сумматоров по модулю два, выходы которых подключены к входам элемента И, выход которого является выходом устройства.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 313222, кл. G ПС 11/00, 1969.

2.Авторское свидетельство по заявке 2457817/18-24, кл. Q ПС 11/00, 1977 (прототип).

3

я1

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1981 |

|

SU972591A1 |

| Преобразователь кодов | 1974 |

|

SU548857A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| Устройство для суммирования @ -разрядных чисел | 1985 |

|

SU1273917A1 |

| Устройство для сжатия и восстановления информации | 1983 |

|

SU1149295A1 |

| Формирователь квазиоптимальных дискретно-частотных сигналов | 1988 |

|

SU1578836A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ В ТРОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ НА НЕЙРОНАХ | 2010 |

|

RU2453900C2 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Устройство для формирования оптимальных дискретно-частотных сигналов | 1988 |

|

SU1552395A1 |

| Устройство избирательного вызова и передачи кодограмм | 1983 |

|

SU1136326A1 |

,:fjj.S3,a,j,:Z,,,f,.f

Авторы

Даты

1980-07-30—Публикация

1978-10-24—Подача