(5) ОБУЧАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Обучающее устройство | 1979 |

|

SU842924A1 |

| Устройство для обучения | 1980 |

|

SU985814A1 |

| Устройство для обучения | 1981 |

|

SU985813A1 |

| Устройство для обучения | 1981 |

|

SU974395A1 |

| Устройство для контроля знаний обучаемых | 1981 |

|

SU985811A1 |

| Многопультовый тренажер операторов систем управления | 1981 |

|

SU953651A1 |

| Устройство для обучения | 1983 |

|

SU1273974A1 |

| Устройство для обучения | 1981 |

|

SU963063A1 |

| Устройство для обучения | 1981 |

|

SU985812A1 |

| Устройство для контроля знаний обучаемых | 1987 |

|

SU1524082A1 |

1

Изобретение относится к автоматике и вычислительной технике, в частно ти к техническим средствам обучения, и может быть использовано для генерации учебных заданий по разветвленной информационно-логической модели курса.

Известно устройство, содержащее связанные соответствующим образом пульт преподавателя, блок отсчета времени, блоки технических средств обучения, пульты обучаемых, блок определения средней оценки, задатчик времени, блок деления, блок перемножения, блок индикации, блок коррекции учебного процесса СОИзвестно также обучающее устройст- во, содержащее связанные соответствующим образом блок ввода учебной информации , блок вывода учебной информации, блок управления, генератор тестов, -генератор случайных чисел, формирователь управляющих сигналов,

регистры, блоки памяти, дешифратор, блок сравнения, коммутатор 2.

Однако эти устройства имеют ограниченные дидактические возможности.

Наиболее близким к предлагаемому является обучающее устройство, содержащее связанные соответствующим образом блок ввода, регистры ответа и номера обучаемого, триггер готовности, четыре блока памяти, блок памяти заданий, два блока элементов ИЛИ, два блока элементов И, формирователь кодов, блок индикации, блок инверторов t З.

Недостатком этого устройства является возможность генерации учебных заданий курса имеющего линейно-последовательную информационно-логическую структуру. Однако при генерации заданий реальных курсов, последние зачастую имеют разветвленную информационно-логическую структуру.

Цель изобретения - расширение дидактических возможностей устройства за счет генерации оптимального учебного задания по разветвленной информационно-логической структуре курса.

.Указанная цель достигается тем, что в обучающее устройство, содержащее последовательно соединенные пульт обучаемого, триггер, первый счетчик первый блок памяти и узел фиксации нулевого кода, выход которого соединен со входом пульта обучаемого, второй выход которого подключен ко входу второго блока памяти; блок индикации, вход которого соединен с . выходом третьего блока памяти, подключенным ко второму входу первого блока памяти, блок сравнения, второй и третий счетчики, дешифратор, два блока элементов И и первый элемент ИЛИ. введены формирователь кодов, формирователь импульсов и первый элемент задержки, выход которого соединен с первым входом первого элемента ИЛИ, а вход - с первым выходом блока сравнения, соединенным с первым входом третьего блока памяти, второй вход которого подключен к первому выходу второго счетчика, соецинениому с первыми входами блока сравнения и формирователя кодов, второй третий, и четвертый входы которого

подключены соответственно к 1зь1ходам первого и второго блоков памяти и третьего счетчика, а выход к первым входам первого и второго блоков элементов И, вторые входы которых соединены соответственно с первым и аторым выхрдами триггера, а выходы соответственно со входом деш1- фратора и с первым входом третьего счетчика, второй вход которого подключен к первому выходу формирователя импульсов, второй выход которого соединен со вторым входом первого счетчика, а вход - с третьим выходом пульта обучаемого, второй выход триггера подключен к первому входу второго счетчика, выход которого соединен со вто рым входом триггера, а второй вход с выходом первого элемента ИЛИ, второй вход которого подключен ко второму выходу блока сравнения, а третий вход - к первому выходу дешифратора, второй выход которого соединен со вторым входом блока сравнения

Формирователь кодов содержит блок элементов ИЛИ и последовательно включенные первый коммутатор, блоки элементов ИЛИ группы, первый регистр и второй коммутатор, выход которого является выходом формирователя, а второй вход через блок элементов ИЛИ соединен с первым и вторым входами формирователя, вторые входы

блоков элементов ИЛИ группы являются третьим входом формирователя, первый и второй входы первого коммутатора являются вторым и четвертым входами формирователя соответственно.

Формирователь импульсов содержит последовательно соединенные второй элемент задержки, третий элемент задерЛки и второй элемент ИЛИ, второй вход и выход которого являются соответственно входом и вторым выходом формирователя, выход второго элемента задержки является первым выходом формирователя .

Блок сравнения содержит последовательно соединенные второй регистр, первый узел элементов И, третий регистр и второй узел элементов И, второй вход которого подключен к выходу второго регистра, первый вход ,

которого является первым входом

блока, третий вход второго узла элементов И является вторым входом блока, первый и второй выходы второго узла элементов И являются первым и

вторым выходами блока, второй вход первого узла элементов И соединен с первым выходом второго узла элементов И,

Третий блок памяти содержит последовательно включенные третий узел элементов И и четвертый регистр, выход которого является выходом блока, первый и второй входы третьего узла элементов И являются соответственно

первым и вторым входами блока.

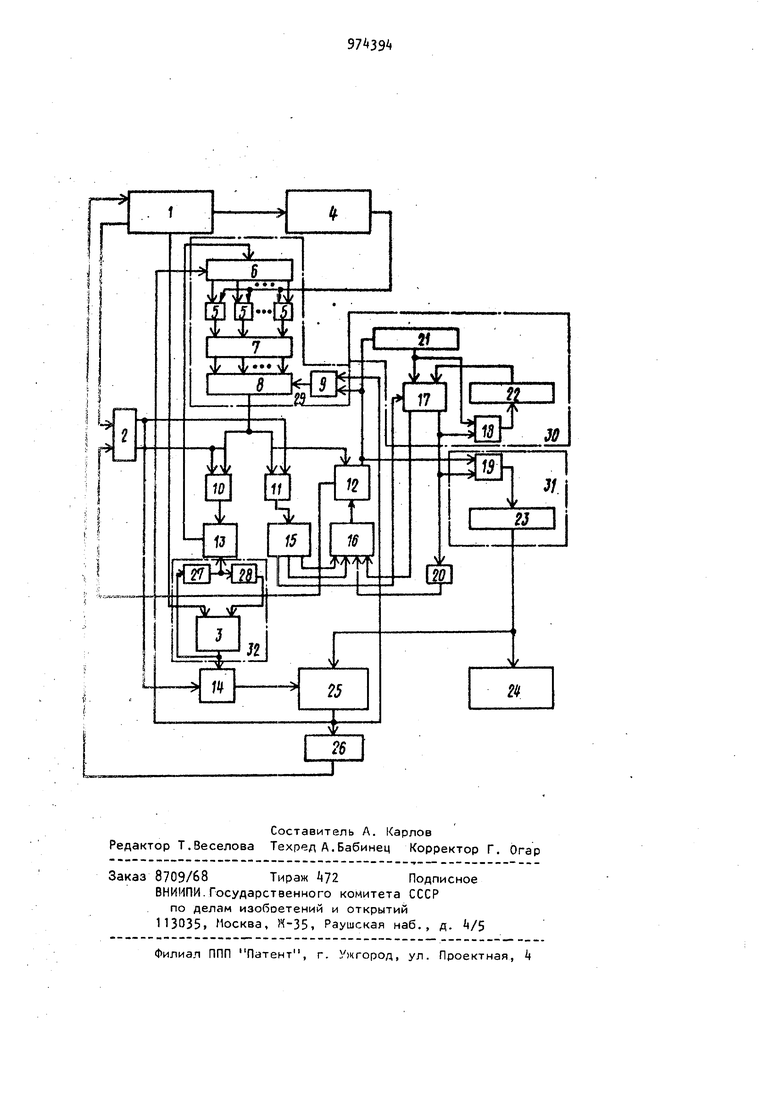

На чертеже приведена блок-схема устройства.

Обучающее устройство содержит . пульт 1 обучаемого, триггер 2, элемент ИЛИ 3, блок памяти, блоки 5 элементов ИЛИ, коммутатор 6, регистр 7, коммутатор 8, блок 9 элементов 11ЛИ, блоки 10 и П элементов И, счетчики 12-14, дешифратор 15, элемент ИЛИ 1б второй узел 17 элементов И, узлы 18 и 19 элементов И, элемент 20 задержки, регистры 21-23, блок 2k индикации, блок 25 памяти, узел 26 фиксации нулевого кода, элементы 27 и 28 задержки. Блок 5,коммутатор 6, ре- гистр 7, коммутатор 8 и блок 9 объединены в формирователь 29 кодов,.узлы 17 и 18 и регистры 21 и 22 - в блок 30 сравнения, узел 19 и регистр 23 - в блок 31 памяти, а элементы 3, 27 и 28 - в формирователь 32 импульсов. Перед началом работы устройства в блоки и 25 и на регистр 21 заносится Снапример,из центральной вычис лительной машины) информация о струк туре учебного курса и об изученности понятий курса каждым обучаемым, регистры 7, 22 и 23 обнуляются. В блоке k хранятся коды изученности каждо го понятия учебного курса каждым обу чаемым, причем указанный код равен увеличенному на единицу числу неизученных обучаемым понятий, непосредственно предшествующих данному. В случае, когда все понятия, непосредственно предшествующие данному изуче ны, указанный код равен единице , а когда изучено и само данное понятиенулю. В блоке 25 хранится информация о структуре учебного курса в виде со вокупности списков понятий непосредственно следующего за данным так,чт код, подаваемый на первый адресный вход блока 25 и являющийся номером понятия, определяет номер списка, а код, подаваемый на второй адресный вход, определяет номер элемента в выбранном списке. На регистре 21 хра нятся коды важности понятий курса, т.е. коды числа зависимых от данного понятия. Устройство работает следующим образом. С Пульта 1 на адресный вход блока Ц поступает номер обучаемого, считанные по которому коды изученности понятий курса через группу блоков 5 считываются на регистр 7- Поступаемым с пульта 1 сигналом триггер 2 ус танавливается в единичное состояние, выдавая сигнал установки в ноль счет чика 1, открывая блок 11 и снимая сигнал установки в ноль с управляющего входа счетчика 12. Кодом, снимаемым с выходом последнего и подаваемым через блок 9 на управляющие входы коммутатора 8, последовательно с выхода коммутатора 8 снимаются код изученности понятий, которые через блок 11 поступают на дешифратор 15Если код изученности понятия не равен единице, т.е. в случае, когда понятие уже изучено или не может быть изучено по причине неизученности предшествующих понятий, дешифратором 15 формируются сигналы, которые, пройдя через элемент ИЛИ 16 подаются на счетный вход счетчика 12. В случае, если код изученности понятия равен единице, дешифратором 15 выдается разрешающий сигнал на узел 17, по которому производится сравнение кода важности понятия, считанного из регистра 21 и содержимого регистра 22, в случае, когда код, считанный из регистра 21, больше считанного из регистра 22, узлом 17 формируется сигнал, разрешающий запись через узел 18 кода, считанного с регистра 21 на регистр 22 и через узел 19 У кода счетчика 12 на регистр 22 и через узел 19 У кода счетчика 12 на регистр 23- Этот же СИ1- нал, задержанный элементом 20, поступает через элемент ИЛИ 16 на счетный вход счетчика 12. При невыполнении указанного условия узлом 17 формируется сигнал, поступающий через элемент ИЛИ 16 на счетный вход счетчика 12. В результате описанной процедуры, когда все понятия курса обработаны указанным образом и счетчик 12 выдает сигнал переполнения, на регистре 23 записывается номер понятия максимальной важности, подлежащий изучению. Указанный номер поступает в блок 2k, которым предъявляется обучаемому содержание выбранного понятия. Одновременно номер выбранного для изучения понятия поступает на первый адресный вход блока 25Сигналом переполнения счетчика 12 триггер 2 сбрасывается в нуль, выдавая сигнал на сброс в нуль счетчика 12, открывая блок 10 и снимая сигнал сброса в нуль с управляющих входов счетчика 1. Кодом, снимаемым с выходом последнего по окончат НИИ цикла обучения, т.е. по выдаче с пульта 1 обучаемого сигнала на элемент ИЛИ 3, из блока 25 последовательно считываются номера понятий, следующие за изученным. Указанные номера, поступая через блок 9 элементов ИЛИ на управляющие входы коммутатора 8, вызывают считывание из регистра 7 через коммутатор 8, блок 10 на счетчик 13 кода изученности понятия, номер которого считан с блока 25. Сигналом с выхода элемента ИЛИ 3. задержанным элементом 27, содержимое счетчика 13 уменьшается на единицу и через коммутатор 6, на управляющий вход которого подается код с выхода блока 25, записывается через группу блоков 5 на регистр 7- Таким образом, производится коррекция кодов изученности понятий, следующих за изученным. Когда все такие понятия пер браны, с выходов блока 25 считывает ся нулевой код и узлом 26 формирует ся сигнал на пУльт обучаемого об окончании цикла Коррекции. Устройст во готово к выдаче задания на изуче ние следующего понятия курса. Таким образом, предлагаемое устройство позволяет генерировать опти мальную дозу изучаемого материала п разветвленной информационно-логичес модели курса. Формула изобретения 1. Обучающее устройство, содержа ее последовательно соединенные пул ооучаемого, триггер, первый счетчик первый блок памяти и узел фиксации левого кода, выход которого соедине :.о входом пульта обучаемого, второй ;.1ход которого подключен ко входу йтсрого блока памяти, блок индикаци ii/од которого соединен с выходом ре; ьего блока памяти, подключенным :; .бторсму входу первого блока памя ;; блок сравнения, второй и третий счетч гки, дешифратор, два блока эле Mei-rros И и первый элемент. ИЛИ, от личающееся тем, что, с целью расширения дидактических возможностей устройства, в него введены формирователь кодов, формирователь и пульсов и первый элемент задержки, выход которого соединен с первым входом первого элемента ИЛИ, а вход с первым выходом блока сравнения, соединенным с первым входом третьего блока памяти, второй вход которого подключен к первому выходу второго счетчика, соединенному с первыми входами блока сравнения и формирователя кодов, второй, третий и четвертый входы которого подключены соответственно к выходам первого и второго блоков памяти и третьего «8 счетчика, а выход - к первым входам первого и второго блоков элементов И, вторые входы которых соединены соответственно с первым и вторым выходами триггера, а выходы - соответственно со входом дешифратора и с первым входом третьего счетчика, второй вход которого подключен к первому выходу формирователя импульсов, второй выход которого соединен со вторым входом первого счетчика, а вход - с третьим выходом пульта обучаемого, второй выход триггера подключен к первому входу второго счетчика, выход которого соединен со вторым входом триггера, а второй вход с выходом первого элемента ИЛИ, второй ВХОД которого подключен ко второму выходу блока сравнения, а третий вход - к первому выходу дешифратора, второй выход которого соединен со вторым входом блока сравнения. 2. Устройство по п.1, о т л и чающееся тем, что в нем формирователь кодов содержит блок элементов ИЛИ и последовательно включенные первый коммутатор, блоки элементов ИЛИ группы, первый регистр и второй коммутатор, выход которого является выходом формирователя, а второй вход через блок элементов ИЛИ соединен с первым и вторым входами формирователя, вторые входы блоков элементов ИЛИ группы являются третьим входом формирователя, первый и второй входы первого коммутатора являются вторым и четвертым входами формирователя соответственно. 3- Устройство по п.1, о т л и чающееся тем, что в нем формирователь импульсов содержит последовательно соединенные второй элемент задержки, третий элемент задерж-t. ки и второй элемент ИЛИ, второй вход и выход которого являются соответственно входом и вторым выходом формирователя, выход второго элемента задержки является первым выходом формирователя . k. Устройство по п.1, о т л и ч аю 1Д е е с я тем, что в нем блок сравнения содержит последовательно соединенные второй регистр, первый узел элементов И, третий регистр и второй узел элементов И, второй вход которого подключен к выходу второго регистра, первый вход которого является первым входом блока, третий вход второго узла элементов И ляется вторым входом блока, первый второй выходы второго узла элементов И являются первым и вторым выходами блока, второй вход первого узла элементов И соединен с первым выходом второго узла элементов И. 5. Устройство по п,1, о т л и чающееся тем, что в нем третий блок памяти содержит послет довательно включенные третий узел элементов М и четвертый регистр, вы 10 ХОД которого является выходом блока первый и второй входы третьего узла элементов И являются соответственно первым и вторым входами блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР Н 35«««5, кл. G 09 В 7/00, 1970. 2.Авторское свидетельство СССР , кл. G 09 В 7/02, IRSO.3.Авторское свидетельство СССР по заявке V 2828170/18-2, кл. G 09 В 7/02, 1970 (прототип).

Авторы

Даты

1982-11-15—Публикация

1981-04-22—Подача