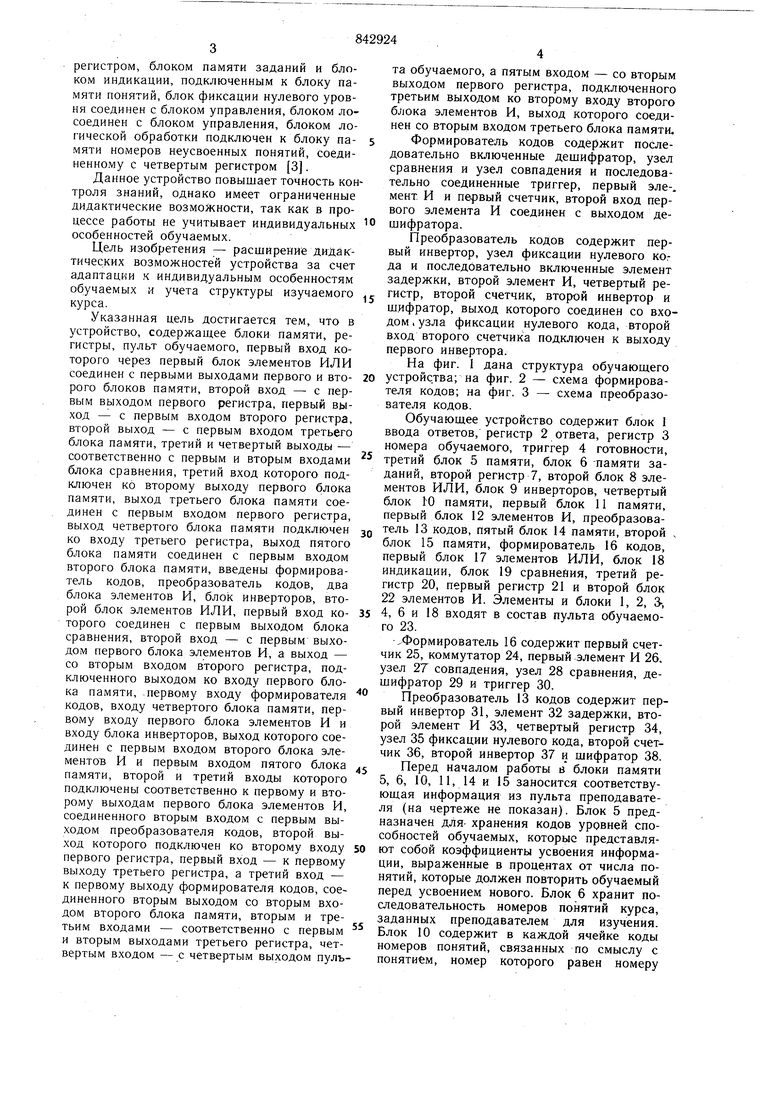

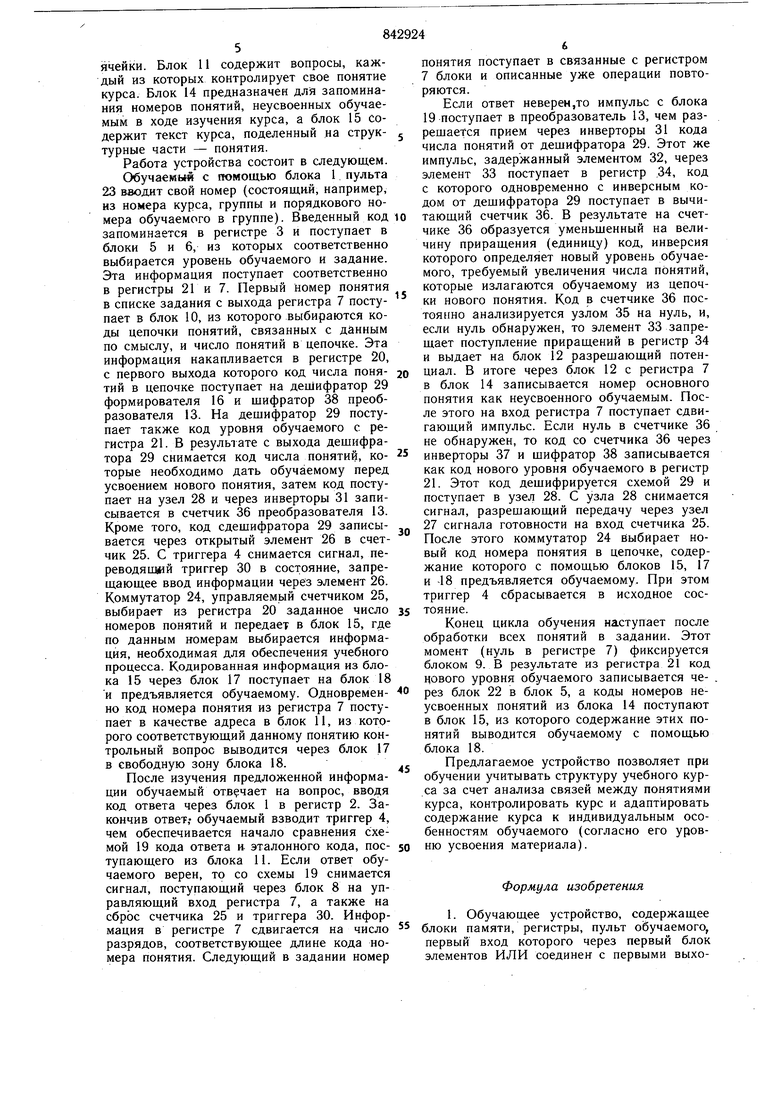

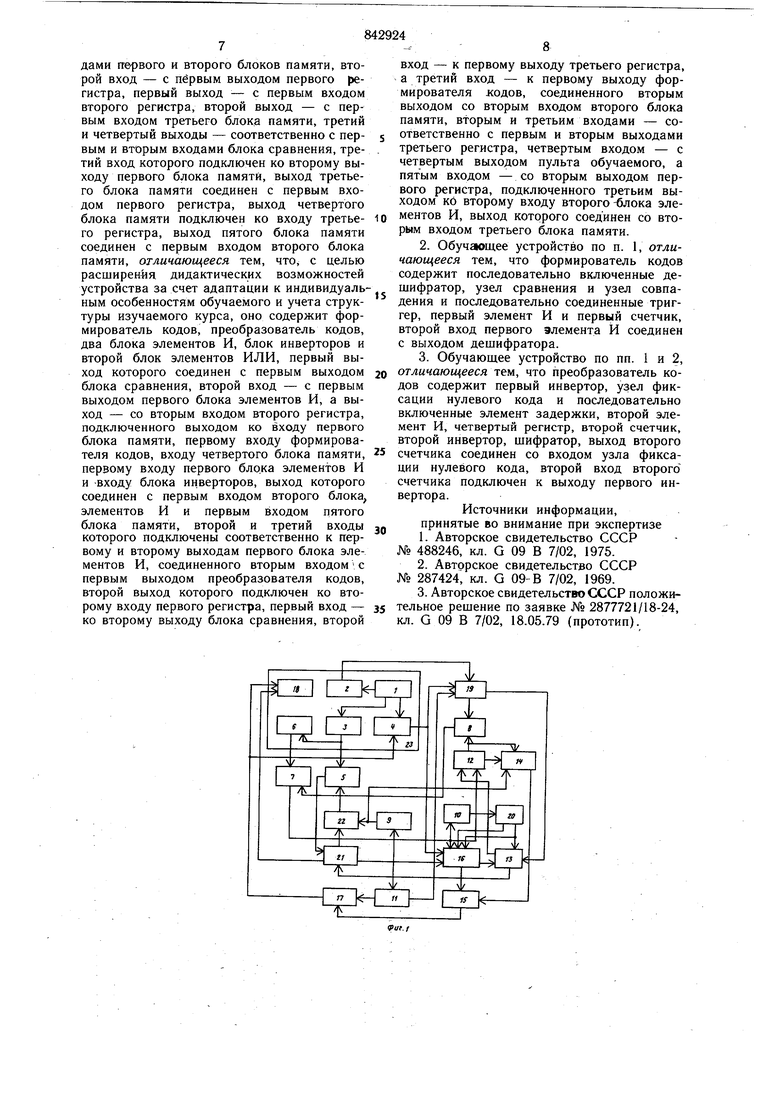

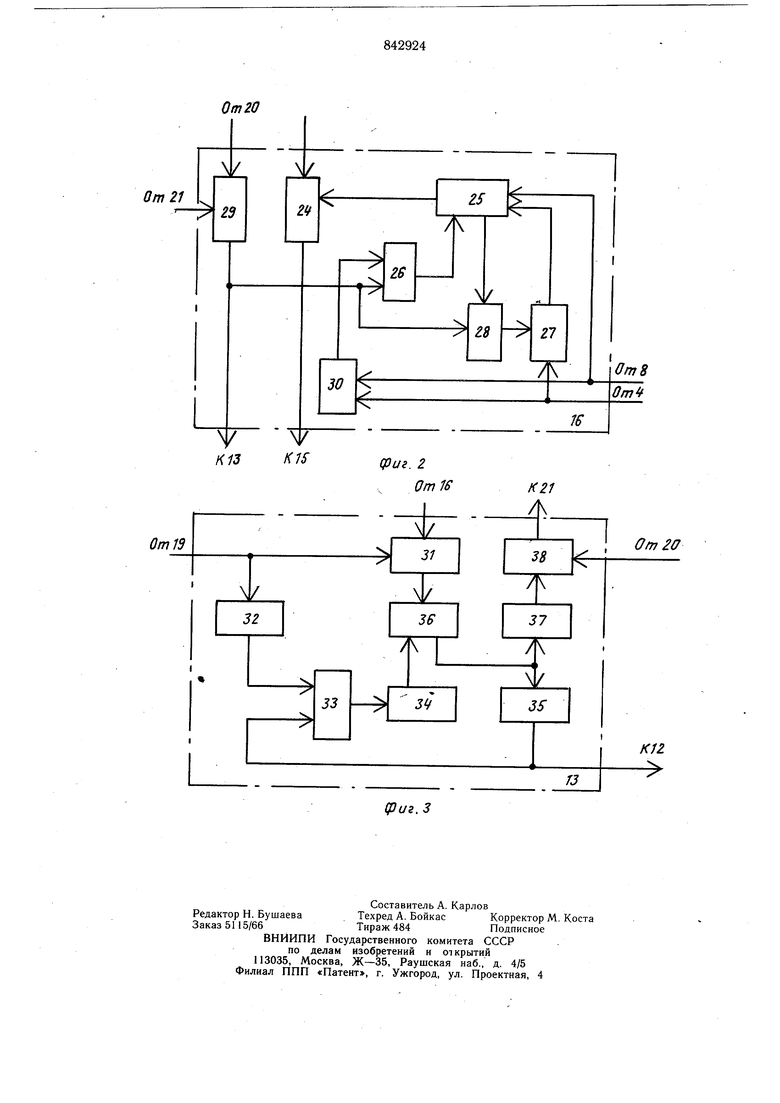

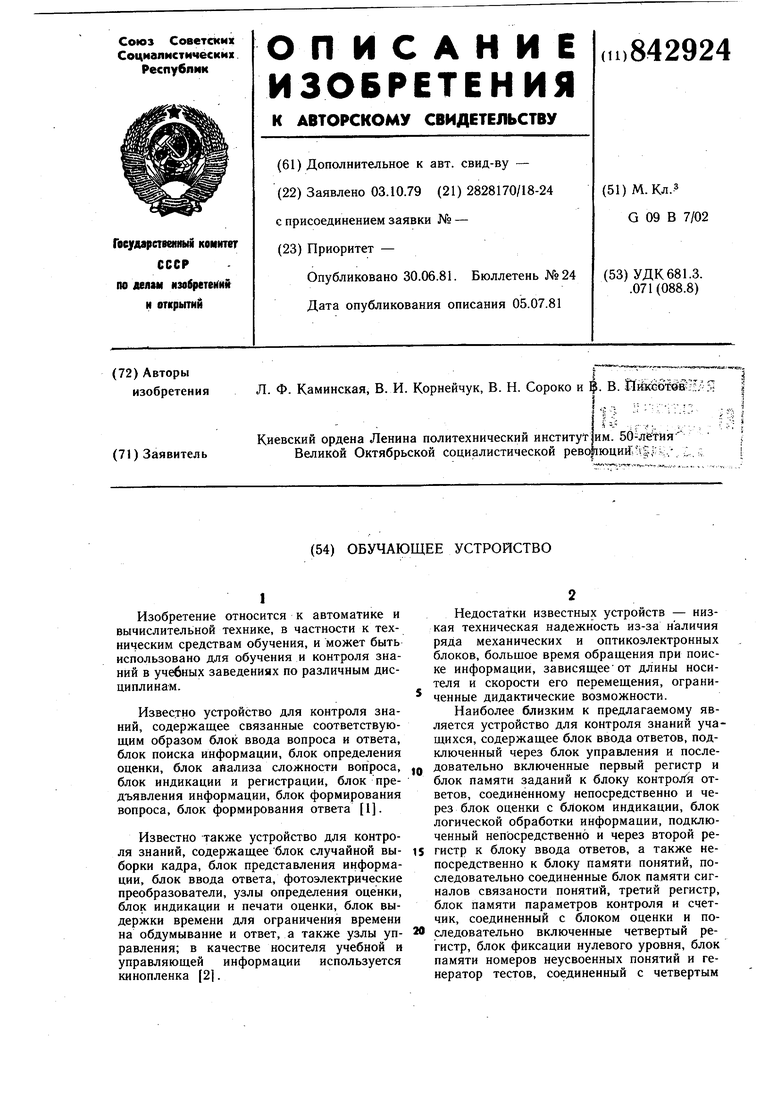

(54) ОБУЧАЮЩЕЕ УСТРОЙСТВО регистром, блоком памяти заданий и блоком индикации, подключенным к блоку памяти понятий, блок фиксации нулевого уровня соединен с блоком управления, блоком лосоелинен с блоком управления, блоком логической обработки подключен к блоку памяти номеров неусвоенных понятий, соединенному с четвертым регистром 3. Данное устройство повышает точность кон троля знаний, однако имеет ограниченные дидактические возможности, так как в процессе работы не учитывает индивидуальных особенностей обучаемых. Цель изобретения ;- расширение дидактических возможностей устройства за счет адаптации к индивидуальным особенностям обучаемых и учета структуры изучаемого курса. Указанная цель достигается тем, что в устройство, содержащее блоки памяти, регистры, пульт обучаемого, первый вход которого через первый блок элементов ИЛИ соединен с первыми выходами первого и второго блоков памяти, второй вход - с первым выходом первого регистра, первый выход - с первым входом второго регистра, второй выход - с первым входом третьего блока памяти, третий и четвертый выходы - соответственно с первым и вторым входами блока сравнения, третий вход которого подключен ко второму выходу первого блока памяти, выход третьего блока памяти соединен с первым входом первого регистра, выход четвертого блока памяти подключен ко входу третьего регистра, выход пятого блока памяти соединен с первым входом второго блока памяти, введены формирователь кодов, преобразователь кодов, два блока элементов И, блок инверторов, второй блок элементов ИЛИ, первый вход которого соединен с первым выходом блока сравнения, второй вход - с первым выходом первого блока элементов И, а выход - со вторым входом второго регистра, подключенного выходом ко входу первого блока памяти, первому входу формирователя кодов, входу четвертого блока памяти, первому входу первого блока элементов И и входу блока инверторов, выход которого соединен с первым входом второго блока элементов И и первым входом пятого блока памяти, второй и третий входы которого подключены соответственно к первому и второму выходам первого блока элементов И, соединенного вторым входом с первым выходом преобразователя кодов, второй выход которого подключен ко второму входу первого регистра, первый вход - к первому выходу третьего регистра, а третий вход - к первому выходу формирователя кодов, соединенного вторым выходом со вторым входом второго блока памяти, вторым и третьим входами - соответственно с первым и вторым выходами третьего регистра, четвертым входом - с четвертым выходом пулъта обучаемого, а пятым входом - со вторым выходом первого регистра, подключенного третьим выходом ко второму входу второго блока элементов И, выход которого соединен со вторым входом третьего блока памяти. Формирователь кодов содержит последовательно включенные дешифратор, узел сравнения и узел совпадения и последовательно соединенные триггер, первый эле-, мент И и пе-рвый счетчик, второй вход первого элемента И соединен с выходом дешифратора. Преобразователь кодов содержит первый инвертор, узел фиксации нулевого ког да и последовательно включенные элемент задержки, второй элемент И, четвертый регистр, второй счетчик, второй инвертор и шифратор, выход которого соединен со входом, узла фиксации нулевого кода, второй вход второго счетчика подключен к выходу первого инвертора. На фиг. 1 дана структура обучающего устройства; на фиг. 2 - схема формирователя кодов; на фиг. 3 - схема преобразователя кодов. Обучающее устройство содержит блок 1 ввода ответов, регистр 2 ответа, регистр 3 номера обучаемого, триггер 4 готовности, третий блок 5 памяти, блок б -памяти заданий, второй регистр 7, второй блок 8 элементов ИЛИ, блок 9 инверторов, четвертый блок Ю памяти, первый блок 11 памяти, первый блок 12 элементов И, преобразователь 13 кодов, пятый блок 14 памяти, второй , блок 15 памяти, формирователь 16 кодов, первый блок 17 элементов ИЛИ, блок 18 индикации, блок 19 сравнения, третий регистр 20, первый регистр 21 и второй блок 22 элементов И. Элементы и блоки 1, 2, 3-, 4,б и 18 входят в состав пульта обучаемого 23. .Формирователь 16 содержит первый счетчик 25, коммутатор 24, первый элемент И 26, узел 27 совпадения, узел 28 сравнения, дешифратор 29 и триггер 30. Преобразователь 13 кодов содержит первый инвертор 31, элемент 32 задержки, второй элемент И 33, четвертый регистр 34, узел 35 фиксации нулевого кода, второй счетчик 36, второй инвертор 37 и шифратор 38. Перед началом работы в блоки памяти 5,б, 10, 11, 14 и 15 заносится соответствующая информация из пульта преподавателя (на чертеже не показан). Блок 5 предназначен для- хранения кодов уровней способностей обучаемых, которые представляют собой коэффициенты усвоения информации, выраженные в процентах от числа понятий, которые должен повторить обучаемый перед усвоением нового. Блок 6 хранит последовательность номеров понятий курса, заданных преподавателем для изучения. Блок 10 содержит в каждой ячейке коды номеров понятий, связанных по смыслу с понятием, номер которого равен номеру

ячейки. Блок 11 содержит вопросы, каждый из которых контролирует свое понятие курса. Блок 14 предназначен для запоминания номеров понятий, неусвоенных обучаемым в ходе изучения курса, а блок 15 содержит текст курса, поделенный на структурные части - понятия.

Работа устройства состоит в следующем.

Обучаемый с помощью блока 1 пульта 23 В80ДНТ свой номер (состоящей, например, из номера курса, группы и порядкового номера обучаемого в группе). Введенный код запоминается в регистре 3 и поступает в блоки 5 н 6, из которых соответственно выбирается уровень обучаемого и задание. Эта информация поступает соответственно в регистры 21 и 7. Первый номер понятия в списке задания с выхода регистра 7 поступает в блок 10, из которого выбираются коды цепочки понятий, связанных с данным по смыслу, и число понятий в цепочке. Эта информация накапливается в регистре 20, с первого выхода которого код числа понятий в цепочке поступает на дешифратор 29 формирователя 16 и шифратор 38 преобразователя 13. На дешифратор 29 поступает также код уровня обучаемого с регистра 21. В резулыате с выхода дешифратора 29 снимается код числа понятий, которые необходимо дать обучаемому перед усвоением нового понятия, затем код поступает на узел 28 и через инверторы 31 записывается в счетчик 36 преобразователя 13. Кроме того, код сдешифратора 29 записывается через открытый элемент 26 в счетчик 25. С триггера 4 снимается сигнал, переводящий триггер 30 в состояние, запрещающее ввод информации через элемент 26. Коммутатор 24, управляемьш счетчиком 25, выбирает из регистра 20 заданное число номеров понятий и передает в блок 15, где по данным номерам выбирается информация, необходимая для обеспечения учебного процесса. Кодированная информация из блока 15 через блок 17 поступает на блок 18 и предъявляется обучаемому. Одновременно код номера понятия из регистра 7 поступает в качестве адреса в блок 11, из которого соответствующий данному понятию контрольный вопрос выводится через блок 17 в свободную зону блока 18.

После изучения предложенной информации обучаемый отвечает на вопрос, вводя код ответа через блок 1 в регистр 2. Закончив ответ,- обучаемый взводит триггер 4, чем обеспечивается начало сравнения схемой 19 кода ответа и эталонного кода, поступающего из блока 11. Если ответ обучаемого верен, то со схемы 19 снимается сигнал, поступающий через блок 8 на управляющий вход регистра 7, а также на сброс счетчика 25 и триггера 30. Информация в регистре 7 сдвигается на число разрядов, соответствующее длине кода номера понятия. Следующий в задании номер

понятия поступает в связанные с регистром 7 блоки и описанные уже операции повторяются.

Если ответ неверен,то импульс с блока 19 поступает в преобразователь 13, чем разрешается прием через инверторы 31 кода числа понятий от дешифратора 29. Этот же импульс, задержанный элементом 32, через элемент 33 поступает в регистр ,34, код с которого одновременно с инверсным кодом от дешифратора 29 поступает в вычитающий счетчик 36. В результате на счетчике 36 образуется уменьшенный на величину приращения (единицу) код, инверсия которого определяет новый уровень обучаемого, требуемый увеличения числа понятий, которые излагаются обучаемому из цепочки нового понятия. Код в счетчике 36 постоянно анализируется узлом 35 на нуль, и, если нуль обнаружен, то элемент 33 запрещает поступление приращений в регистр 34 и выдает на блок 12 разрешающий потенциал. В итоге через блок 12 с регистра 7 в блок 14 записывается номер основного понятия как неусвоенного обучаемым. После этого на вход регистра 7 поступает сдвигающий импульс. Если нуль в счетчике 36 не обнаружен, то код со счетчика 36 через инверторы 37 и шифратор 38 записывается как код нового уровня обучаемого в регистр 21. Этот код дешифрируется схемой 29 и поступает в узел 28. С узла 28 снимается сигнал, разрешающий передачу через узел 27 сигнала готовности на вход счетчика 25. После этого коммутатор 24 выбирает новый код номера понятия в цепочке, содержание которого с помощью блоков 15, 17 и -18 предъявляется обучаемому. При этом триггер 4 сбрасывается в исходное состояние.

Конец цикла обучения наступает после обработки всех понятий в задании. Этот момент (нуль в регистре 7) фиксируется блоком 9. В результате из регистра 21 код нового уровня обучаемого записывается че- . рез блок 22 в блок 5, а коды номеров неусвоенных понятий из блока 14 поступают в блок 15, из которого содержание этих понятий выводится обучаемому с помощью блока 18.

Предлагаемое устройство позволяет при обучении учитывать структуру учебного кур.са за счет анализа связей между понятиями курса, контролировать курс и адаптировать содержание курса к индивидуальным особенностям обучаемого (согласно его уровню усвоения материала).

Формула изобретения

1. Обучающее устройство, содержащее блоки памяти, регистры, пульт обучаемого, первый вход которого через первый блок элементов ИЛИ соединен с первыми выходами ггервого и второго блоков памяти, второй вход - с первым выходом первого регистра, первый выход - с первым входом второго регистра, второй выход - с первым входом третьего блока памяти, третий и четвертый выходы - соответственно с первым и вторым входами блока сравнения, третий вход которого подключен ко второму выходу первого блока памяти, выход третьего блока памяти соединен с первым входом первого регистра, выход четвертого блока памяти подключен ко входу третьего регистра, выход пятого блока памяти соединен с первым входом второго блока памяти, отличающееся тем, что, с целью расширения дидактических возможностей устройства за счет адаптации к индивидуальным особенностям обучаемого и учета структуры изучаемого курса, оно содержит формирователь кодов, преобразователь кодов, два блока элементов И, блок инверторов и второй блок элементов ИЛИ, первый выход которого соединен с первым выходом блока сравнения, второй вход - с первым выходом первого блока элементов И, а выход - со вторым входом второго регистра, подключенного выходом ко входу первого блока памяти, первому входу формирователя кодов, входу четвертого блока памяти, первому входу первого блока элементов И и -входу блока инверторов, выход которого соединен с первым входом второго блока, элементов И и первым входом пятого блока памяти, второй и третий входы которого подключены соответственно к первому и второму выходам первого блока элементов И, соединенного вторым входом с первым выходом преобразователя кодов, второй выход которого подключен ко второму входу первого регистра, первый вход - ко второму выходу блока сравнения, второй

вход - к первому выходу третьего регистра, а третий вход - к первому выходу формирователя , соединенного вторым выходом со вторым входом второго блока памяти, вторым и третьим входами - соответственно с первым и вторым выходами третьего регистра, четвертым входом - с четвертым выходом пульта обучаемого, а пятым входом - со вторым выходом первого регистра, подключенного третьим выходом Кб второму входу второго-блока элементов И, выход которого соединен со вторым входом третьего блока памяти.

2.Обучаощее устройство по п. 1, отличающееся тем, что формирователь кодов содержит последовательно включенные дешифратор, узел сравнения и узел совпадения и последовательно соединенные триггер, первый элемент И и первый счетчик, второй вход первого элемента И соединен с выходом дешифратора.

3.Обучающее устройство по пп. 1 и 2, отличающееся тем, что преобразователь кодов содержит первый инвертор, узел фиксации нулевого кода и последовательно включенные элемент задержки, второй элемент И, четвертый регистр, второй счетчик, второй инвертор, шифратор, выход второго счетчика соединен со входом узла фиксации нулевого кода, второй вход второго счетчика подключен к выходу первого инвертора.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 488246, кл. G 09 В 7/02, 1975.

2.Авторское свидетельство СССР № 287424, кл. G 09-В 7/02, 1969.

3.Авторское свидетельство СССР положительное решение по заявке № 2877721/18-24, кл. G 09 В 7/02, 18.05.79 (прототип).

(риг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обучения | 1981 |

|

SU963063A1 |

| Устройство для обучения | 1980 |

|

SU985814A1 |

| Обучающее устройство | 1981 |

|

SU974394A1 |

| Устройство для обучения | 1981 |

|

SU985813A1 |

| Устройство для контроля знаний учащихся | 1978 |

|

SU765864A1 |

| Устройство для контроля знаний обучаемых | 1983 |

|

SU1111192A1 |

| Устройство для контроля знаний обучаемых | 1981 |

|

SU985811A1 |

| Устройство для контроля знаний обучаемых | 1990 |

|

SU1758658A1 |

| Устройство для обучения | 1981 |

|

SU974395A1 |

| Устройство для контроля знаний обучаемых | 1981 |

|

SU1005152A1 |

Авторы

Даты

1981-06-30—Публикация

1979-10-03—Подача