(51) УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Обучающее устройство | 1979 |

|

SU842924A1 |

| Устройство для обучения | 1981 |

|

SU985813A1 |

| Обучающее устройство | 1981 |

|

SU974394A1 |

| Устройство для обучения | 1980 |

|

SU985814A1 |

| Устройство для обучения | 1981 |

|

SU985812A1 |

| Устройство для контроля знаний учащихся | 1978 |

|

SU765864A1 |

| Устройство для контроля знаний обучаемых | 1981 |

|

SU985811A1 |

| Аудиовизуальное обучающее устройство | 1986 |

|

SU1425758A1 |

| Устройство для контроля знаний обучаемых | 1982 |

|

SU1035633A1 |

| Устройство для обучения | 1981 |

|

SU974395A1 |

1

Изобретение относится к автоматике и вычислительной технике, в частности к техническим средствам обуче- ния, и быть использовано в качестве устройства для формирования учебных заданий по различным дисциплинам.

Известно устройство, содержащее связанные соответствующим образом пульт преподавателя, блок отсчета JQ времени, блоки технических средств обучения., пульты обучаемых, блок определения средней оценки, задатчик времени, блок деления, блок перемножения , блок индикации, блок коррекции is учебного процесса 1.

Известно устройство, содержащее связанные соответствующим образом устройство управления, устройство анализа ответов, блок определения статис- 20 тики правильных ответов, блок выдачи рекомендаций, блок памяти, блок ввода устройства управления и анализов ответа, устройство определения очередности ответов,блок определения качества усвоения, блок оценки ожидаемых значений параметров,.блок определения последовательности обучения t 2

Недостатками известных устройств являются невысокие дидактические возможности, так как в процессе работы не учитывается структура изучаемого курса.

Наиболее близким к предлагаемому является устройство, содержащее связанные соответствующим образом блок ввода, регистры ответа и номера обуча.емого, триггер готовности, первый, второй, третий, четвертый блоки памяти, блок, памяти заданий, первый и второй блоки элементов ИЛИ, первый и второй блоки элементов И, формирователь кодов, блок индикации, блок

инверторов 3j.

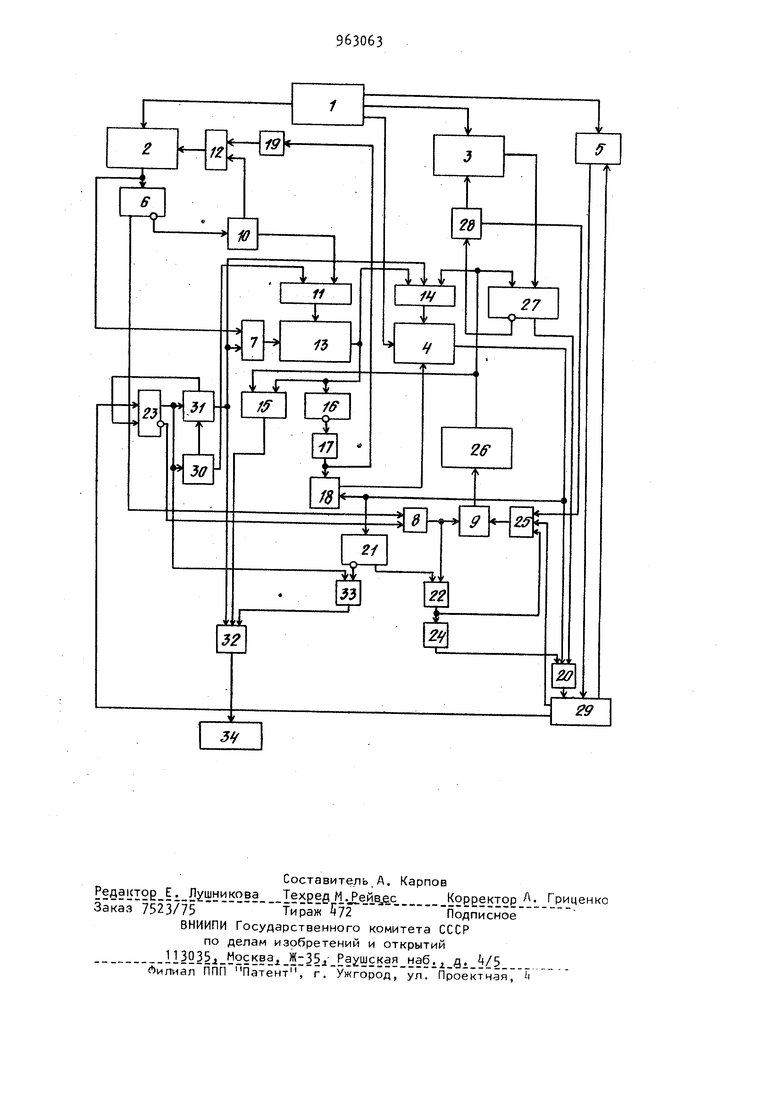

Устройство учитывает структуру курса, однако имеет ограниченные ди9630дактические возможности, так как в процессе работы не учитываются данные об индивидуальном усвоении каждым обучаемым структурных единиц курса, не учитывается реальный ресурс времени на обучение. о Цель изобретения - расширение дидактических возможностей устройства за счет оптимизации формирования учебного задания с учетом данных о струк- 10 туре учебного курса, важности структурных единиц курса, данных об индивидуальном усвоений каждым обучаемым структурных единиц курса, ресурс времени на обучение. Поставленная цель достигается тем что в устройство, содержащее последовательно включенные первый инвертор, первый элемент ИЛИ, первый блок памя ти, первый блок элементов ИЛИ и второй блок памяти, последовательно соединенный блок ввода учебной информации, третий блок памяти и первый блок элементов И, второй вход которо го через второй инвертор подключен к выходу первого элемента И, соединенному с первым входом второго элемента ИЛИ, последовательно включенные триггер, второй элемент И, второй блок элементов И и блок индикации, второй блок элементов ИЛИ, выхо которого соединен с вторым входом второго блока памяти, выход которого через третий блок элементов И подключен к второму входу второго блока элементов И, четвертый блок памяти, первый вход которого соединен с вторым выходом блока ввода учебной информации, третий выход которого подключен к второму входу первого бл ка памяти, введены последовательно соединенные первый формирователь импульсов, четвертый блок элементов И, первый счетчик, пятый блок памяти, пятый блок элементов И и второй счет чик, последовательно включенные сумматор и регистр, последовательно соединенные второй формирователь импульсов, элемент задержки и третий счетчик, третий формирователь импуль сов, вход которого соединен с выходом третьего блока памяти, первый вы ход - с вторым входом второго элемента И, второй выход - с первым вхо дом первого элемента И, второй вход которого подключен к ВЫХОДУ -четвеотого блока элементов И., второй вход которого соединен с вторым выходом триггера, первый вход которого под4ключен ко второму выходу сумматора, третий выход которого соединен с вторым входом второго элемента ИЛИ, а второй вход - с выходом первого блока элементов И, третий вход которого подключен к второму выходу пятого блока элементов И, второй вход которого соединен с выходом четвертого блока памяти, второй вход которого подключен к первому выходу второго счетчика, второй выход которого соединен с третьим входом второго элемента ИЛИ, выход которого подключен к второму входу первого счетчика, четвертый счетчик, вход которого соединен с вторым выходом первого формирователя импульсов, первый выход - с вторым входом первого элемента ИЛИ, второй выход - с первым входом второго блока элементов ИЛИ, последовательно включенные пятый и шестой счетчики, вход пятого счетчика и второй вход шестого счетчика соединены с выходом триггера, второй выход пятого счетчика подключен ко второму входу второго блока элементов ИЛИ, первый выход шестого счетчика соединен с вторым входом триггера, а вто|Ьой выход - с вторым входом первого блока элементов ИЛИ, третьим входом второго блока элементов И и первым входом третьего блока элементов И, 6торой вход которого подключен к выходу пятого блока памяти, третий бход - к ыыходу второго блока памяти, ё выход - к второму входу третьего блока памяти, третий вход которого соединен с выходом третьего счетчика, второй вход которого подключен к третьего блока памяти, выход элеМента задержки соединен с входом первого инвертора, выход пятого элемента памяти подключен ко второму входу третьего блока элементов И, вход второго формирователя импульсов соединен с выходом второго блока памяти, вход Первого формирователя импульсов подключен к выходу первого блока памяти, второй вход регистра соединен с четЬертым выходом блока ввода учебной информации. На чертеже изображена функциональная схема устройства для обучения. Устройство содержит блок 1 ввода учебной информации-, блок 2 памяти, блок 3 памяти, блок памяти, регистр 5 (ресурса времени), формироваteль 6 импульсов {фиксации нуля), блок 7 элементов ИЛИ, блок 8 элемен5ЭtOB И, счетчик 9, счетчик 10, блок 1 ёлементов ИЛИ, элемент ИЛИ 12, блок памяти, блок 1 элементов ИЛИ, блок 15 элементов И, формирователь 1о мпульсов (фиксации нуля), элемент 1 задержки, счетчик 18, инвертор 19, блок 20 элементов И, формирователь 2 импульсов (фиксации нуля), элемент И 22 триггер 23,инвертор 2,элемент ИЛИ 25, ёлок 2б памяти, блок 27 элементов И, Ьчетчик 28, сумматор 29, счетчик 30 счетчик 31, блок 32 элементов И, эле Цент И 33, блок 3 индикации. Перед началом работы устройства в блоки k, 13 и 26 памяти заносится (например, из центральной вычислительной машины) соответствующая информация о структуре учебного курса. В блоке 13, таким образом, хранится информация о структуре учебного курса, в блоке 26 хранятся номера понятий, составляющих курс в порядке их важности, т.е. по числу связей с дру гими понятиями, блок k содержит информацию о неусвоенных обучаемым поснятиях, причем структура этой информации такова, что каждое понятие относительно каждого обучаемого характеризуется числом неусвоенных понятий, связанных и предшествующих данно му, включая и данное понятие. Устройство работает следующим образом. С блока 1 в блоки 2. и 3 и регистр 5 вводится соответствующая информация . В блок 2 заносятся номера неусвоенных понятий по данным текущего этапа- контроля. В блок 3 заносятся номера, подлежащие обучению на последую щем этапе, в регистр 5 засылается чис ло понятий, которое может быть усвоено обучаемым (например, по опыту прошедших этапов обучения) за врегля, отведенное на подготовку к последующему этапу обучения. Кроме того, на первый адресный вход блока k поступает из блока 1 номер обучаемого. По окончании ввода исходной информации осуществляется цикл учета результатов контроля. Номер неусвоенного по результатам текущего контроля понятия через блок 7 поступает на пер вый адресный вход блока 13 памяти, а на второй адресный вход этого блока через блок 11 поступают коды с счетчика 10, обеспечивая последовател но считывание с выхода блока 13 номег ров понятий, связанных с неусвоенным З материалом и зависящими от неусвоенного. По каждому такому номеру, поступающему через блок Н на второй адресный вход блока , с выхода последнего считывается в счетчик 18 .число неусвоенных предшествующих понятий. Если номер понятия, считанный с блока 13, не равен нулю, то на обратном выходе формирователя 16 сфоо|мировывается сигнал единичного уровня, который пройдя через элемент 17 задержки, увеличит на единицу содержимое счетчика 18. после чего оно заносится в блок ч памяти на место счи ганного. Затем счетчиком 10 задаетСЯ адрес следующего, зависящего от Неусвоенного понятия, и-способом, аналогичным описанному выше, производится увеличение на единицу числа неусвоенных предшествующих понятий, хранимого в блоке k памяти, т.е. учет Неусвоенного на текущем этапе контроля понятия производится путем прибавления единицы к числу неусвоенных предшествующих понятий тех понятий, которые связаны и следуют за неусвоенным на пекущем этапе понятия понятием. Переполнение счетчика 10 появление нулевого кода на выходе блока 13 памяти формирует единичный сигt an на выходе элемента ИЛИ 12, по которому из первого блока 2 памяти выбирается номер следующего, неусвоенно о на текущем этапе контроля, понятй (например,, посредством сдвига), и оно учитывается аналогичным описанному выше образом. Когда номера всех неусвоенных на текущем этапе контроля понятий исчерпаны, на выходах блока 2 памяти сформируется нулевой код, и на выходе формирователя 6 сформируется сигнал единич1Чого уровня, которым через элемент И 8 защищен счет- : ник 9 и начинается цикл выбора оптимального учебного задания. Коды, сни-t маемые с выходов счетчика 9, последо- вательно поступают на адресный вход ; лока 26 памяти, с выхода которого считываются номера понятий в порядке их важности. Считанный с блока 2б код поступает через блок элементов ИЛИ йа адресный вход блока и на блок 27, Где он сравнивается последовательно ро всеми номерами понятий, хранящимися в блоке 3, перебор которых осув4ествляется посредством счетчика 28. В случае переполнения последнего, выдается сигнал, который через элемент ИЛИ 25 поступает на счетный вход счетчика 9. Считанный из блока код поступает на блок 20 элементов И и на формирователь 21 для фиксации нуля и, если считанный с- блока k код является нулевым, единичный сигнал с выхода формирователя 21 через открытый элемент И 2.2 поступает через инвертор 2k на блок 20, а также через элемент ИЛИ 25 на счетный вход счетчика 9. Таким образом, считанный из блоka 26 номер понятия проверяется: состоит ли он в списке, номеров понятия последующего этапа обучения и существуют для данного обучаемого неусвоенные понятия, предшествующие выбран ному из блока 2б, При выполнении ука занннх условий блок 20 оказывается открытым и число неусвоенных понятий предпествующих считанному из блока 2 снимаемое с выходов блока через от крытый блок 20, поступает на первый вход сумматора 29, на второй вход ко торого подается код из регистра 5. Если разность кодов отрицательна, то сумматором 20 формируется сигнал, который через элемент ИЛИ 25 поступа ет, на счетный вход счетчика 9. Если разность кодов ,положительна, то ее код, снимаемый с выходов сумматора 2 заносится в регистр 5 и сумматором 2 формируется сигнал прерывания цикла выбора оптимального учебного задания по которому начинается цикл выдачи учебного задания. Этот же сигнал, по ступая на вход триггера 23 устанавливает его в единичное состояние. Сигнал единочного уровня с прямого выхода триггера 23 запускает счетчики ЗП и 31, причем счетным сигналом для счетчика 31 является сигнал пере полнения счетчика 30, и открывает эл мент И 33. Нулевой сигнал с обратного выхода триггера 23 закрывает последовательно элементы И блока 8 и элемент И 22. Код с выходов счетчика 31 поступает через блок 7 на первый адресный вход блока . Код с выходов счетчика 30 подается через блок 11 на второй адресный вход блока 13. В результате, с выхода блока 13 на первый вход блока 15 послед вательно снимаются номера всех понятий, связанных с первым, вторым и т.д. понятием. На второй вход блока 15 считывается номер-понятия из 5лока 26. При совпадении указанных содов блоком 15 выдается сигнал на лок 32, Одновременно с последова тельным считыванием с выхода блока 13 номеров понятий, связанных и следующих за ( -ым, где 1,2,..,,/, а f число понятий курса. С выхода блока k считывается код числа, неусвоенных понятий 5 предшествующих (-ому понятию, который поступает на формирователь 21, с обратного выход которого в случае, если код, снимаемый с блока (, ненулевой, формируется единичный сигнал, которым открывается блок 32. Таким образом,, блок 32 оказывает- ся открытым, если на счетчике 31 зафиксирован номер неусвоенного понятия, предшествующего выбранному для изучения, В этом случае номер неусвоенного понятия с выходов счетчика 31 через открытый блок 32 поступает на блок Цикл выдачи учебного задания продолжается до тех пор, пока для понятия, выбранного для изучения, не будут исчерпаны все неусвоенные предшествующие понятия. Оканчивается цикл выдачи учебного задания сигналом переполнения счетчика 31, которым три|- гер 23 устанавливается в нуль и продолжается прерванный цикл выбора оптимального учебного задания, который оканчивается сигналом переполнения счетчика 9, когда исчерпаются все номера понятий, хранящиеся в блоке 3 или исчерпается ресурс времени. Таким образом, в предлагаемом устройстве учебные задания формируются опти/ альным образом с учетом структуры учебного курса, важности структурных единиц курса, данных об индивидуальном усвоении каждым обучаемым структурных единиц курса, ресурса времени, за счет чего достигается расширение дидактических возможностей по сравнению с известными устройствами . Формула изобретения Устройство для обучения, содержащее последовательно включенные первый инвертор, первый элемент ИЛИ, первый блок памяти, первый блок элементов ИЛИ и второй блок памяти, последовательно соединенные блок ввода учебной информации, третий ,блок памяти и первый блок элементов И, второй вход которого Мерез второй инвертор подключен к выходу первого элемента И, соединенному с первым входом второго

елемента ИЛИ, последовательно включенfibie триггер, второй элемент И, вто|)ой блок элементов И и блок индикаi MM, второй блок элементов ИЛИ, выход которого соединен с вторым входом вт(-5 рого блока памяти, выход которого чег рез третий блок элементов И подключен к второму входу второго блока (элементов И, четвертый блок памяти, первый вход которого соединен с вто- Ю рым выходом блока ввода учебной информации, третий выход которого под,| лючен ко второму входу первого блока памяти, отличающееся тем, |йто, с целью расширения дидактических S возможностей устройства за счет оптимизации учебных заданий, в него бведены последовательно соединенные Первый формирователь импульсов, четЬертый блок элементов И, первый счетам Мик, пятый блок памяти, пятый блок Ьлементов И и второй счетчик, последовательно включенные второй форми эователь импульсов, элемент задержки. И третий счетчик,третий формирователь. 25 импульсов, вход которого соединен f. выходом третьего блока памяти, вый выход - с вторым входом второго элемента И, второй выход - с первым входом первого элемента И, второй 30 вход которого соединен с выходом чет Ьертого блока элементов И, второй Вход которого соединен с вторым выхо Дом триггера, первый вход которого подключен к второму выходу сумматора j-35 третий выход которого соединен с вто Ьым входом второго элемента ИЛИ, а )второй вход - с выходом первого блока элементов И, третий вход которого родключен к второму выходу пятого бл6-40 ка элементов И, второй вход которого соединен с выходом четвертого блока Ьамяти, второй вход которого подключен к первому выходу второго счетчи.ka, второй выход которого соединен с 45 третьим входом второго элемента ИЛИ, выход которого Подключен к второму :

Входу первого счетчика, четвертый счетчик, вход которого соединен с вто|эым выходом первого формирователя имИульсов, первый выход - с вторым Bxo-f дом первого элемента ИЛИ, второй выход - t первым входом второго блока элементов ИЛИ, последовательно включенные пятый и шестой счетчики, входi пятого счетчика и второй вход шестого счетчика соединены с первым выходом триггера, второй выход пятого счетчи ка подключен к второму входу второго блока элементов ИЛИ, первый выход шестого счетчика соединен с вторым входом триггера, а второй выход - с вто- рым входом первого блока элементов ИЛИ третьим входом второго.блока элемен- тов И и первым входом третьего блока элементов И, второй вход которого подключен к выходу пятого блока памяти, третий вход - к выходу второго блока памяти, а выход - к второму входу третьего блока памяти, третий вход которого соединен с выходом третьего счетчика, второй вход которого подключен к выходу третьего блока памяти, выход элемента задержки соединен с входом первого инвертора, вуход пятого элемента памяти подключен к второму входу третьего блока элементов И, вход второго формирователя импульсов соединен с выходом второго блока памяти, вход первого формирователя им-; пульсов подключен к выходу первого блока памяти, второй вход регистра соединен с четвертым выходом блока ввода учебной информации.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-09-30—Публикация

1981-02-06—Подача