(54) УСТРОЙСТВО ДЛЯ ОВУЧЕНИЯ

Изобретение относится к автоматике и вычистштельной технике, в частаюсти к техническим средствам о чения, и может быть использовано в качестве устройства для управления выдачей учеб{адх заданий по различным дисциплинам.

Известно устройство, содержащее связаинью соответствующим образом пульт преподавателя, блок отсчета времени, задатчик времени, блок деления, блок ,Q перемножения, блок индикации, блок коррекции учебного процесса Cl .

Извес-гао устройство, содерясащее связанные соотаетствующим образсял у л ройсгвр управления, устройство анализа ,j ответов, блок определения статистики правильных ответов, блок вьщачи рёксялен- даций, блок памяти, блок ввода ycтpoйcnw ва управления и анализа ответов, устройство определения очередности ответов, 20 блок определения кв юства усвоения, блок сшешш ожидаемых значений параметров, блок определения последовательности сучения С23 .

Недостатками известных устройств являются ограниченные дидактические возможности, так как в процессе их функционирования не учитывается структура изучаемого курса.

Наиболее близкий к изобретению SIB- ляется устройство, содержащее связанные соответствукшщм образом блок ввода ответов, регистр ответа, регистр номера обучаемого, триггер готовности, пять блоков памяти, два блока элементов И; два блока элементов ИЛИ, пульт обучаемого, три регистра, блок ааксапяя нулевого уровня, формирователь кодов, блок индикации, блок сравнения, преобразователь кодов, блок инверторов Сз J.

Данное устройство учитывает структуру изучаемого курса, данные об индивидуальных способностях обучаемого, одаако не учитьтает временных характеристик забывания различных структурных единиц курса для каждого о гчаемого.

Учет таких тсарактеристик позволяет расширять дддактнческие возможности за :счвт ТОГО, что повторному предъявлению подлежит не фиксированная часть структурных едшшц курса, предшествующих изучаемому, а лишь те структурные един цы курса, уровень освоения которых вследствие естественного забывания нахо дится ниже критического, что приводит .к повышению качества обучения и повыше ВИЮ его скорсзсти (за счет уменьшения числа структурных единиц курса, подлежа ших повторению). Цель изобретения - расширение дидак тических возможностей устройства за счет учета временных характеристик естественного забывания, Указанная цель достигается тем, что в устройство дли обучения, содержащее пульт;обучаемого,, первый, второй, третий и четвертый выходы которого соединены соответственно с входом первого регистра, первым входом первого блока Сравнения, первым входом первого блока памяти и первым входом первого формирователя кодов, первый выход которого подключен к первым входам информационного табло и второго блока памяти и к второму входу первого блока памяти, а второй выход - к первому входу пульта обучаемого, второй вход которого соединен с первым выходом распределителя импульсов, второй вход первого формирователя кодов подключен к первому выходу первого блока сравнения, второй выход которого соединен с вторым входом информационного табло, введены второй блок сравнения и последовательно соединенные второй формирователь кодов, первьй блок элементов И, блок элементов ИЛИ, сумматор и узел счетчиков, второй вход и первый выход которого соединены соответственно с выходом и вторым вхо дом второго блока памяти, третий вход - с вторым выходам распределителя импул сов, второй выход - с: первым входом второго формирователя кодов, второй вхо которого подключен к выходу сумматора третий вход - к третьему вьссоду формир вателя импульсов, четвертый вход - к пятому выходу пульта обучаемого, пятый вход - к второму выходу формирователя т дпульсов, шестой вход - к четвертому выходу пульта оператора, седьмой вход к выходу первого блока сравнения, восьмой вход - к первому выходу первого блока памяти, второй выход - к третьему входу второго блока памяти и первом входу второго блока сравнения, третий выход - к второму входу первого блока Сравнения, второй вход второго блока сра&нения соединен с выходом первого регист ра, третий вход - с пятым выходом пуль та обучаемого, а выход - с первым вхо дом распределителя импульсов, второй вход которого подключен к четвертому выходу пульта обучаемого, а четвертый выход - к четвертому входу узла счетчиков и второму входу сумматора, тре-гай вход которого соединен с шестым выходом пульта обучаемого, второй вход блока элементов ИЛИ подключен к выходу второго блока памяти, второй вход первого блока элементов И соединен с вторым выходом первого блока памяти, причем первый формирователь кодов содержит первый элемент ИЛИ-НЕ, выход которого является вторым выходом формирователя, первьй элемент ИЛИ, первый и второй входы которого являются первым и вторым входами формирователя соответст венно, и последовательно включенные второй регистр, третий блок памяти и второй элемент ИЛИ-НЕ, выход которого соединен с первым входом второго регистр, ра, второй вход которого является первым входом формирователя, а вьпсод соедийен с входом первого элемента ИЛИ-flE, выход первого элемента ИЛИ подключен к второму входу третьего блока памяти, выход которого является первым выходом формирователя, а второй формирователь кодов содержит последовательно соединенные второй элемент ИЛИ, элемент задержки, э ретий элемент ИЛИ, второй блок элементов И, счетгчик и третий блок элементов И, последовательно соединенные элемент И и четвертый элемент ИЛИ, выход которого подключен к второму входу счетчика, и Третий регистр, выход которого соединен со вторым входом второго блока элементов И, второй вход четвертого элемента ИЛИ, первый вход элемента И, третий вход четвертого элемента ИЛИ, второй вхбд третьего блока элементов И, второй вход третьего элемента ИЛИ, первый и второй входы второго элемента ИЛИ и вход третьего регистра являются соответственно первым, вторым, третьим, четвертым, пятым, шестым, седьмым и восьмым входами формирователя, третий вход третьего блока элементов И и второй вход элемента И являют ся соответственно вторым и четвертцм входами формирователя, выходы второго элемента ИЛИ, счетчика и третьего бло. ка элементов И являются соответственна первьпл, вторым и третьим в Ь1Ходами форолирователя.

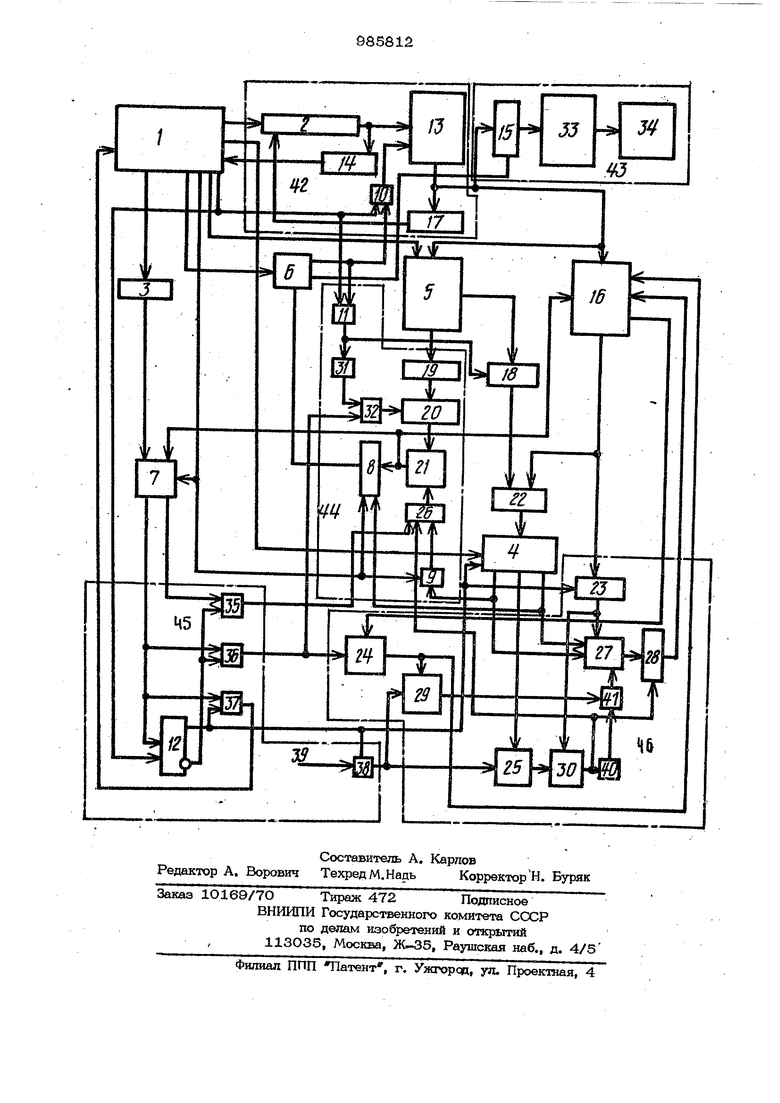

На чертеже представлена функциональная схема устройства.

Устройство для обучения содержит пульт 1 обучаемого, связанный с установочными входами регистров 2 и 3, сумматора 4, с адресными входами блока 5 памяти, с первыми входами блока 6 сравнения, с управл5Оошими входами блока 7 сравнения, блоком 8 элементов И элементом И 9. Кроме того, пульт 1 своим вь ходом подключен к элементу ИЛИ Ю, элеаменту ИЛИ 11, к входу установки в нуль триггера 12. Регистр 2 крайней группой своих разрядов соединен с адресными входами блока 13 памяти и элементом ИЛИ-НЕ 14, выход которого подключен к пульту 1. Блок 13 памяти выходами свякзан с блоком 15 элементов И, адресным входом блока 5 памяти, адресными входами блока 16 памяти, с входами элемента ИЛИ-НЕ 17, выходом подключенного к шине сдвига регистра 2. Блок .5 памяти одной группой своих выходов соединен с блоком 18 элементов И, а другой группой выходов подсоединен к установочным входам регистра 19, вьссоды которого подключены к входам блока 2О элементов И, который выходами связан с установочными входами счетчика 21, выход которого соединен с первыми входами блока 7 сравнения, входами блока 8 элементов И и адресными входами блока 16 памяти, который своими выходами подключен к входам блока 22 элементов ИЛИ и блока 23 элементов И, а вторыми выходами связан с установочными входами счетчика 24. Выходы блока 22 подсоединены к входам сумматора -4, выходы которого подключены к установочном входам счетчика 25, один знаковый

выход сумматора 4 связан через элемент И 9 и элемент ИЛИ 2 6 со счетным входсад счетчика 21, другой знаковьШ выход сумматора 4 соединен со входсял блока 8 элементов И. Кроме того, оба знаковых выхода сумматора 4 подключены к управляющим входам счетчика 27 связанного с установочными входами с блоком 23 элементов И, а выходами - с вхсэда- ми блока 28 элементов И, выход лоследне 1Х подсоединен к входам блока 16 памяти. Другими входами блок 16 связан с выходами счетчика 24, которые, KpofMe того, подключены к установочным входам счетчика 29. Выход блока 23 элементов И связан с установг«шыми входами счетчика 30, выход блока 8 элементе И соединен с входами блока 6 сраоо ения, ъыгход которого связан через элемент ИЛИ

10 с адресным входом блока 13 памяти и черекз элемент ИЛИ 11 с блоком 18 элементов И. Кроме того, выход элемента ИЛИ 11 через элемент 31 задержки и элемент ИЛИ 32 подключен к бяоку 2G элементов И, Блок 18 элементов И выходами соединен с блоком 22 элементов ИЛИ, другой выход блока 6 сравнени подсоединен к входам блока 15 элементов И, выходы которого подключены к адресным шинам блока 33 памяти, выходами связанного с блоком 34 индикаиии. Регистр 3 выходами псэдсоединен к вторым входам блока 7 сравнения, один вь ход которого подключен к входу элемента И 35, а другой - к входам элементов И 36 и 37 и счетному входу триггера 12 прямой выход которого связан с входов элемента И 37, входом блока 23 элементов И, управляющим входом сумматора 4, первым входом элемента И 38, второй вход которого соединен с шиной 39 тактовых импульсов, а выход - со сче-гаыми входами счетчиков 25, 29. Выход переполнения счетчика 25 связан со счетным входом счетчика ЗО, выход переполнения которого подключен к блоку 28 элементов И и через элемент ИЛИ 26 - к счетному входу счетчика 21, а через индикатор 4О - к входу элемента И 41, инверсный выход трипте- ра 12 подсоединен к входам элементов И 35 и 36. Выход элемента И 35 через элемент ИЛИ 26 связан со счетным входом счетчика 21, выход элемента И 36 подключен к счетному входу счетчика 24 и через элемент ИЛИ 32 - к блоку 20 элементоЕ И, выход элемента И 37 соединен с пультам 1 обучаемого. Регистр 2, элементы 1О, 14, 17 и блок 13 объединены в фс мирователе 42 кодов, блоки 15, 33 и 34 - в информационном табло 43, блоки 8, 2О, счетчик 21, регистр 19, элементи 9, 11, 26, 31, 32 - в формирователе 44 кодов, триггер 12 к элементы И 35 - 38 - в распределителе 45 импутаюов, блоки 23, 28, счетчики 24, 25, 27, 29, ЗО, инвертор 4О и элемент 41 И - в узле 46 счетчиков.

Перед началом работы устройства в блоки памяти (например, из центральной вычислительной машины) заносят информацию, несябхокщмую для выполнения устройством своих функций. В блоке 5 памяти хранится для каждого о чаемого дата изучения им каждой структурной единицы курса и оценка степени ее усвоения. В блоке 13 памяти содержится информация о Логических связяхмежду различными структурными единицами курса, причем эта информация может быть организована в виде списковой структуры. . В блоке 16 1хад« яти для каждой структурной единицы курса хранится информация о среднем времени перехода обучаемого с одного уровня усвоения на другой вследствие естественного процесса . забьгоания. Такая информация может иметь табличную организацию. В блоке 33 памяти содержится информация, подлежащая предъявлению. обучаемому. Устройство для обучения работает сле дующим образом. С пульта 1 в регистр 2 заносятся но мера структурных единиц курса, подлежащих изучению на текущем занятии. Код даты занятия заносится обучаемым с пул та 1 в сумматор 4. На пульте 1 набирается также код номера обучаемого, кот рый поступает на адресный вход блока 5 и код предельно допустимого уровня усвоения предшествующих изучаемым на занятии структурных единиц курса. Этот код поступает в блок 6 сравнения. По сигналу начала операции, выдаваемого с пульта 1 на элементы ИЛИ 10, 11 и вход установки в нуль триггера 12, с : блока 13 считывается код первого .из списка структурных единиц курса, непосредственно предществующего первой изучаемой структурной единице курса, номер которой, находящийся в крайней группе разрадов регистра 2, подается на адресный вход блока 13. Считанный из блока 13 код поступает на адресные вхо ды блоков 5 и 16. С одной группы выхо дов блока 5 считьюается в регистр 19 начальный уровень усвоения данной струк турной единицы курса обучаемым. С другой группы выходов блока 5 через открытый блок 18 поступает код времени изучения структурной единицы курса, который, поступая на сук«латор 4, вычитается из занесенного в сузиматор.4 кода текущего времени, так что в сумматоре 4 формируется код промежутка времени, прошедшего с момента изучения данной структурйой единицы курса. Сигнал начала операции, задержанный элементом 31, поступает через элемент ИЛИ 32 в блок 20 элементов И. Блок 18 элементов И при этом запирается. Через открытый блок 20 элементов И код начального уровня усвоения aaHocHiv ся в счетчик 21, с выходов которого поступает на один адресный вход блока 16. С первой группы выходов блока 16 читывается код t(|, j.jj - среднего вреени перехода вследствие естественного абывания с уровня i на уровень i -1, де i - уровень усвоения, код которого оступает на другие адресные входы блока 16, а у - номер структурной единицы урса, код которой поступает на адресные входы блока 16. Код t(,- i-i)/ выходов блока 16 чеез блок 22 элементов ИЛИ поступает в сумматор 4, где вычитается из кода прошедшего за период обучения времени т.е. в сумматоре 4 формируется раз ность. Ti,r.r%i-M Если полученная разность Т у положительна, то на одном знаковом выходе сумматора 4 формируется сигнал, который, пройдя через открытый с пульта 1 элемент И 9 и элемент ИЛИ 26, умень- шает содержимое счетчика 21 на единицу. Аналогично описанной вьние структуре с выходов блока 16 считывается код (i-f 1-2)1 сумматоре 4 вычисляется разность,. На К--М шаге этой процедуры оказывается, что Т(( J- отрицательно. На другом знаковом выходе сумматора 4 формируется сигнал, который, поступив на блок 8 элементов И, разрешает считывание со счгтчика 21 (прогнозируемого уровНя усвоения) j -и структурной единицы курса на текущий момент времени. Прогнозируемый уровень усвоения сравнивается блоком 6 с предельно допустимым. Если прогнозируемый уровень усвоения оказьюается ниже критического, то блокам 6 вьщается сигнал, открьтающий блок 15, через который код номера структурной единицы курса поступает на адресный вход блока 33 памя-ги,- с выхода которо го информадая, содержащаяся в забытой структурной единице курса поступает для предъявления в блок 34. При изучении j -и структурной единицы курса о саемый вьздачей с пульта 1 сигнала начала операции вызывает обработку по оггасан- ной выше процедуре следующей структурной единицы курса. Если прогнозируемый уровень усвоения вьице рредельно допустимого, то блоком 6 формируется сигнал, который, пройдя через элемент ИЛИ 1О в блок 13 памяти, вызьтает. считывание кода посл€;дующей структурной единицы

курса и обработку его в соответствии с описанной процедурой. Если же все предшествующие изучаемой структурные единицы курса обработаны, то с выходов блока 13 считывается нулевой код, который вызьгоает формирование на выходе элемента 17 сигнала сдвига, содержимого регист ри 2 на р разрадов, где р - число разрядов, отводимое для записи номера одной структурной единицы курса{ начинается обработка структурных единиц курса, предшествующих структурной единице, номер которой в результате сдвига оказался крайним. По окончании обработки описанным способом всех структурных единиц, подлежащих изучению, после очередного сдвига в крайней группе разрядов регистра 2 окажутся записанными нули. Элемент 14 формирует сигнал окончания режима изучения на пульт 1.

Помимо работы в режиме вьщачи учебных заданий устройство может работать .и в режиме коррекции временных характе ристик забывания в коде контроля уровня усвоения структурных единиц курса. , В режиме ко1}рекции с пульт 1 на регистр 3 заносится уровень усвоения , зафиксированный при проведении контроля, а на блок 7 вьздается с пульта 1 сигнал, разрешающий работу последнего и закрывающнй блок 8 влементов И и элеме1т И 9.

В сумматор 4 заносится код текущего времени. В регистр 2 записывается код контролируемой структурной единицы

курса. Повторно с пульта 1 вьздается сигнал начала операции, по которому в сумматоре 4 вычисляется код промежут ка времени между изучением и контролем, на вычитающий счетчик 21 заносится код начального J уровня усвоения, Посяед ний блоком 7 сравнивается с реальним уровнем усвоения, выявленным в результате контроля. Если разность Между начальным У1ювнем усвоения и уровнем усвоения, выявленным в результате конт. роля, пояожтгельна, то блок 7 формщ гет сигнал, открьтающий элемент И 35, который через элемент ИЛИ 26 выдает сигнал на счетный вход вычитакндетчэ счетчика 21. Код, гранимый на вычитающем -счетчике 21, уменьшаясь на единицу подается на адресный вход блока 16 и с последн.его - на сумматор 4, счгатывается код промежутка среднего щюмени уменьшения на единицу начального уровня. Кроме того, уменьшенныЕв код счетчика 21 рпять поступает на блок 7 срав. нения. В дальнейшем описанный цикл

яродолжается до тех пор, пока уровень усвоения, зафиксированный контролем, не окшкется равным уровню, код которого считывается из счетчика 21. В этом случае блоком 7 сравнений фо1 мируется сигнал начала коррекции, котори, пройд через открытый элемент И 36, лрибав:ляет к содержимому счетчика 24 единицу и, поступая через элемент ИЛИ 32 в блок 20 элементов И, обеспечивает сч:тывание с регистра 19 в счетчик 21 кода начального уровня усвоения и . В сумматоре 4 хранится код д i разности времени, прсш1едшего с момент изучения и прогнозируемо1Ч времени падения уровня усвоения учебного материала с Н ° к начал Нчх) до контролируемого. На счетчике 24 хранится число п , по котором проводится усреднение характеристик забывания. Импульсом с блока 7 сравнения трштер 12 устанавливается в единичное состояние, элементы И 35 и 36 закрываются, а с прямого выхода триггера 12 формируется сигнал, блокирукяций работу сумматора 4 и оИфывающий элемент И 38, через который тактовые импульсы со входа 39 поступают на счетные входи счетчиков 25 и 29, на которые занесены ооотватствевно код л-Ь и п . В счетчшЕ 30 заносится через ОФкрьггый сигвался 1 с прямого выхода трйггеря 12 и блока 23 элементов И код прогнозного промежугиса щюменн , ч А-Ь,,ч.1ад€Шш уровня от начального на единицу. Такой же код заносится и на реверсивный счетчик 27. В зависимости от знака кода /si суммеаорсм 4 в счет чяк. 27 выдается управляющий либо по первому знаковому выходу, либо по второму. В cooTBeTCTBffif с этям, счетчик 27 работает в режиме сложения щм1ходяшкх на его вход импульсов шга в режиме вычитаяяя.

На выходе обнуления счетчика 29 нмпулЫзы следуют с периодом

t «1 (31

.

где - период тактовых импульсов. Эти импульсы, через OTSpiimiifi элемент И 41, поступают ва счетш11й вхсэд счетчика 27. Число импульсов, поступивших на

счетяЕЫй вход счетчика 27, (жредв)1яе1ч::я промежутком времени появления импу1В са обнуления с выхода счетчщса ЗО, которое равно

i « (4)

„г44 Л

( Таким образом, число импульсов сЛ , поступивших на счетный вход счетчика 27, ршвно Л Ун-1 И представляет собой величину изменения среднего времени снижения уровня усвоен от начального на единицу, обеспечивающую минимум средней по о гчаемым погрешности. По окончании выдачи импуШ)сов на счетшлй вход счетчика 27, то ест при формировании импульса обнуления с выхода счетчика 30, последним открьюа- ется блок 28 элементов И и скорректиро ванный код , записьюается в блок 16 памяти. Этим же импульсом код, хра нящийся в счетчике 21, уменьшается на единицу и производится описанноым выше способом-корректировка дляД ди т.д. до тех пор, пока блоком 7 сравнения не зафиксируется равенство поступающих на его входы КОДОВ} блоком 7 вьздается сигнал на счеоиый вход триггера 12, сбрасывающий последний в нуль. При этом через элемент 37 на пульт 1 об чаемого выдается сигнал конца операшш корректировки. Таким образом, устройство для о%ченйя позволяетрасширить дидактические возможности по сравнению с прототипом за счет адаптивного учета временных характеристик естественного процесса . забывания каждой структурной единицы курса. Учет времешак характеристик забьгоания позволяет повьюить качество обучения, так как изучению предлагается лищь структурная единица учебного курса, а предшествующие усвоены о гчае- мым с уровнем, не ниже предельно допустимого. Кроме того, устройство для обучения позволяет Ш1ачительно сократить время обучения за счет повышения егчэ целенаправленности. Так, в извест ном устройстве время изучения определяется формулой t +IIti y(t, Ь) ;Т„ п: J fri V J V где m - число изучаемых структурных единиц кур9а; t.- - время изучения J -и структурной единицы курса; d - фиксированное число структурны единиц курса, предшествуиндих - л . j -му и подлежащих повторению D. - общее число структурных единиц курса, подлежащих повторению j - вероятность того, что предшествующая структурная единица курса, уровень усвоения которой ниже предельно допустимого, не вошла в число повторяемых. , В яредлагаемом устройстве время вения определяется формулой t - c(Lr. tnct-n %(vg.). где оЦ- число структурных единиц курса, используемых в процессе заняиш, прогнозируемый уровень усвоения которых ниже критического. Следовательно, устройство обеспечивает оптимальную вьщачу заданий, исключающую повторное изучение учебного материала и повторение структурных единиц курса, уровень усвоения которых обучаемым достаточно высок. Формула изобретения 1. Устройство для обучения, содержащее пульт обручаемого, первый, второй, третий и четвертый вьзкоды которого соединены соответственно с входом первого регистра, первым входом первого блока сравнения, первым входом первого блока памяти и первым входом первого формирователя кодов, первый выход которого подшпочен к первым входам информационного табло и второго блока памяти и к второму входу первого блока памяти, а второй выход - к первому входу пульта , обучаемого, второй вход которого соединен с первым входом распределителя импульсов, второй вход первого формирователи кодов подключен к первому выходу первого блока сравнения, второй выход которого соединен с вторым входом информационного табло, отличающееся тем, что, с целью расширения дидактических возможностей устройства, в него введены второй блок сравнения и последовательно соединенные второй формирователь кодов, первый cinoK элементов И, блок элементов ИЛИ, сумматор и узел счетчиков, второй вход и первьй выход которого соединены соответственно с выходом и вторым BXo«ON# второго блока памяти, третий вход - с вторым выходом распределителя импульсов, второй выход - с первым входом второго формирователя кодсе, второй вход которого подключен к выходу сумматора, третий вход - к третьему выходу формирователя импульсов, четвертый вход - к пятому выходу пульта обучаемого, пятый вход - 1к второму выходу формирователя импульсов, шестой кход - к четвертому выходу пульта оператора, седьмой вход - к выходу первого блока сравнения, восьмой вход - к первому выходу первого блока памяти, второй выход - к третьезму входу второго бтюка пазмшти и первому входу второго блока сравнения, третий выход к второму входу первого блока сравнения второй вхрд второго блока сравнения соединен с выходом первого регистра, третий вход - с пятым выходом пульта обучаемого, а выход - с первым входом рах предеяителя импульсст, второй вход которсго подключен к четвертому выходу дульта об учаемо1ю, а четвертый выход к четвертому входу узла счетчиков и вто рому входу сумматора, третий вход которого соединен с шестым выходом пультй обучаемого, второй вход блока элементов ИЛИ подключен к выходу второго блока памяти, второй вход пернюго блока элементов И соединен с вторым выходом первого блока памяти. 2. Устройство по п. 1, о т л и ч а - ю щ е е с я тем, что в нем первый формирователь кодов содержит первый элемент ИЛИ-ЛЕ, выход которого является вторым выходом форв шрователя, первьй Э1ле(мент ИЛИ, первый и второй входы которого являются первым и вторым входами формирователя соответственно, и последовательно включенные второй регистр, третий блок памяти и второй элемент ИЛИ-НЕ, выход которого соединен с первым входам второго регистра, второй вход которого является входом формирователя, а выход соединен с входом первого элемента ИЛИ-НЕ, выход первого элемента ИЛИ подключен квтоfCMy входу третьего блока памяти, выход KOTOpdiro 5шляется первым выходом формирователя. 3. Устройство по п. 1, о т Я и ч а ю щ е е с я тем, что в нем второй формирователь содержит пocлeдoвiaфc тельно соединенные второй элемент ИЛИ, элемент задержки, третий элемент ИЛИ, второй блок элементов И, счетчик и третий блок элементов И, последовательно соединенные элемент И н четвертый эп&мент ИЛИ, выход которого подключен к BTOpcsMy входу счетчика, и третий регистр выход которого соединен с вторым входом второго блока элементов И, второй вход четвертого элемента ИЛИ, первый вход элемента И, третий вход четвертого элемента ИЛИ, второй вхоп третьего блока элементов И, второй вход третьего элемента ИЛИ, первый и второй входы второго элемента ИЛИ и вход третьего регист ра являются соответственно первым, , третьим, четвертым, пятым, шестым, седьмым и восьмым входами формирователя, третий вход -фетьего блока элемен- тов И и второй вход элемента И ЯЁЛЯХУГ paf соответственно вторым и четдаертим входами формирователя, выходы второго элемента ИЛИ, счетчика и третьего бшо :ка з)1ементов И являются соответственно ;первым, вторым и третьим выходами фо1 1мирователя Источники информации, принятые во внимание пра экспертизе 1. Авторское спядетельство № 354445, кл. Q 09 В 7/ОО, 1970. 2.Авторское свидетельство СССР № 517О38, кл. а 09 В 7/О4, 1974. . 3.Авторское свидетельство по заявке № 2828X70/18-24, ЕЛ. G 09 В 7/02, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обучения | 1981 |

|

SU963063A1 |

| Устройство для обучения | 1981 |

|

SU974395A1 |

| Обучающее устройство | 1981 |

|

SU974394A1 |

| Многопультовый тренажер операторов систем управления | 1981 |

|

SU953651A1 |

| Устройство для обучения | 1981 |

|

SU985813A1 |

| Обучающее устройство | 1979 |

|

SU842924A1 |

| Устройство для обучения | 1985 |

|

SU1249565A1 |

| Устройство для контроля знаний обучаемых | 1981 |

|

SU985811A1 |

| Устройство для контроля знаний обучаемых | 1983 |

|

SU1176362A1 |

| Устройство для контроля знаний обучаемых | 1981 |

|

SU1012317A1 |

Авторы

Даты

1982-12-30—Публикация

1981-07-16—Подача