(5 ПЕРЕКШЧАТЕЛЬ ЛИНИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухканальная резервированная вычислительная система | 1989 |

|

SU1734251A1 |

| Устройство приоритетного доступа к магистрали | 1990 |

|

SU1839249A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1746379A1 |

| УСТРОЙСТВО ИМИТОЗАЩИТЫ ГРУППЫ КОНТРОЛИРУЕМЫХ ОБЪЕКТОВ | 2015 |

|

RU2595991C1 |

| СПОСОБ ДВУХТАКТНОЙ АССОЦИАТИВНОЙ МАРШРУТИЗАЦИИ | 1999 |

|

RU2140132C1 |

| Параллельный логический мультиконтроллер | 2016 |

|

RU2634199C1 |

| УСТРОЙСТВО ВЫЧИСЛЕНИЯ МНОГОПАРАМЕТРИЧЕСКОГО ИНТЕГРАЛЬНОГО ПОКАЗАТЕЛЯ | 2017 |

|

RU2661749C1 |

| ФОРМИРОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОСТИ РАЗНОПОЛЯРНЫХ ПРЯМОУГОЛЬНЫХ ИМПУЛЬСОВ С ИЗМЕНЯЕМОЙ ДЛИТЕЛЬНОСТЬЮ И ИНТЕРВАЛОМ | 2015 |

|

RU2582553C1 |

| Релейный триггер | 1980 |

|

SU869049A1 |

| Способ и устройство автоматизированного структурирования мультикультурных учебных групп | 2016 |

|

RU2618387C1 |

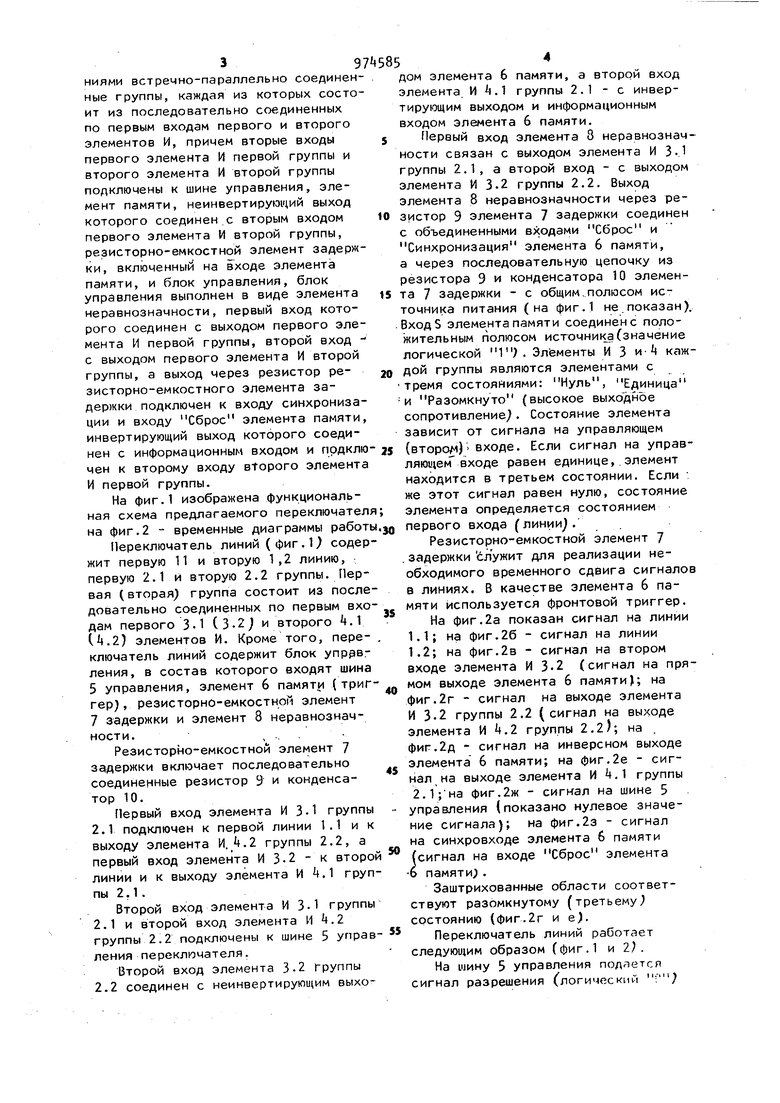

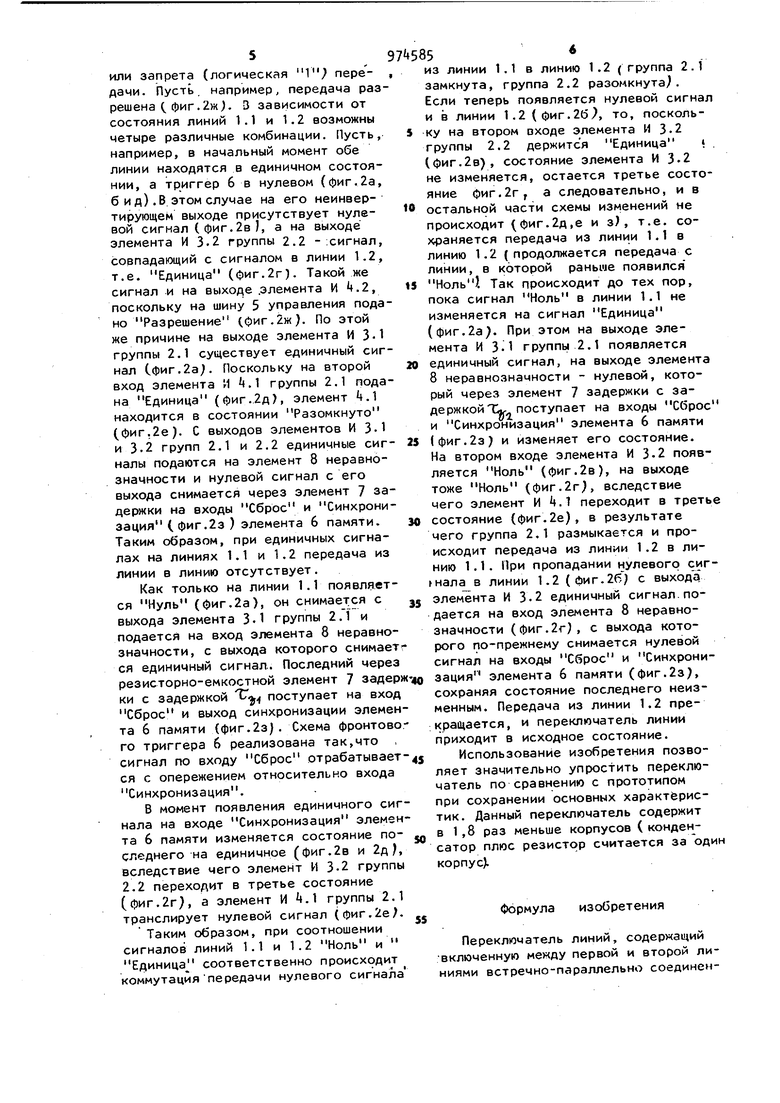

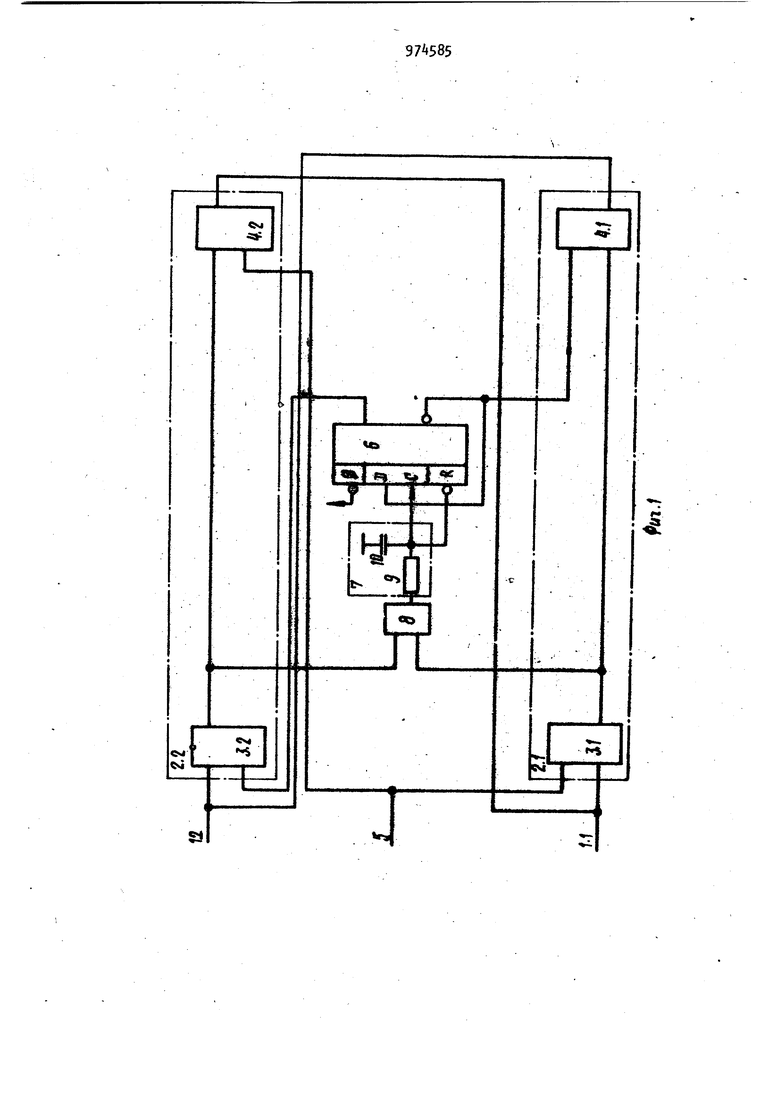

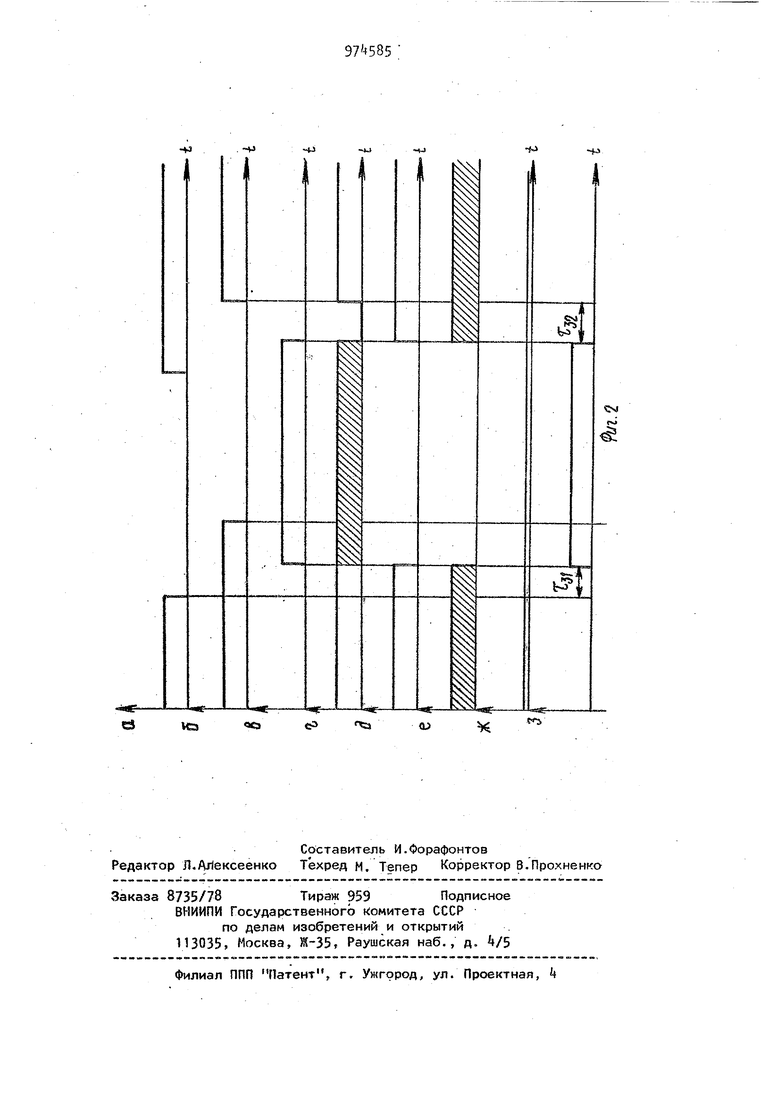

Изобретение относится к вычислительной технике и технике связи и может быть использовано для переклю чения магистралей в многомашинных вычислительных комплексах. Известен переключатель линий, содержащий включенные между первой и второй линиями встречно-параллель но соединенные группы, каждая из ко торых состоит из последовательно соединенных по первым входам первого и второго элементов И, причем st рые входы первого элемента И первой группы и второго элемента И второй группы подключены к шине управле ния f 1 ЛНедостатком известного устройств является низкая помехозащищенность, обусловленная отсутствием взаимной блокировки групп во время прохождения сигналов. . Известен также переключатель линий, содержащий включенные между первой и второй линиями встречнопараллельно соединенные группы, каж-, дая из которых состоит из последовательно соединенных по перёым входам первого и второго элементов И, причем вторые входы первого элемента И первой группы и второго элемента И второй группы подключены к шине управления, элемент памяти, неинвертирующцй выход которого соединен с вторым.входом первого элемента И второй группы, резисторно-емкостной . элемент задержки, включенный на |входе элемента памяти, и .блок управления 2j. Недостатком данного переключателя является большая сложность, обус ловленная наличием элементов памяти и задержки в каждой группе, элемента ИЛИ и согласующих инверторов. Цель изобретения - упрощение переключателя линий. Поставленная цель достигается тем, что в переключателе линий, содержащем включенные между первой и второй линиями встречно-параллельно соединен ные группы, каждая из которых состо ит из последовательно соединенных по первым входам первого и второго элементов И, причем вторые входы первого элемента И первой группы и второго элемента И второй группы подключены к шине управления, элемент памяти, неинвертирующий выход которого соединен.с вторым входом первого элемента И второй группы, резисторно-емкостной элемент задержки, включенный на входе элемента памяти, и блок управления, блок управления выполнен в виде элемента неравнозначности, первый вход которого соединен с выходом первого элемента И первой группы, второй вход с выходом первого элемента И второй группы, а выход через резистор резисторно-емкостного элемента задержки подключен к входу синхронизации и входу Сброс элемента памяти, инвертирующий выход которого соединен с информационным входом и прдключен к второму входу Btoporo элемента И первой группы. На фиг.1 изображена функциональная схема предлагаемого переключателя на фиг.2 - временные диаграммы работы Переключатель линий (фиг.1) содержит первую 11 и вторую 1,2 линию, первую 2.1 и вторую 2.2 группы. Первая (вторая) группа состоит из последовательно соединенных по первым входам первого 3.1 (3-2) и второго 4.1 (,Ц.2) элементов И. Кроме того, переключатель линий содержит блок упрэвления, в состав которого входят шина 5 управления, элемент 6 памяти (три|- гер), резисторно-емкостной элемент 7 задержки и элемент 8 неравнозначности. . . . Резисторно-емкостной элемент 7 задержки включает последовательно соединенные резистор 9 и конденсатор 10. Первый вход элемента И 3.1 группы 2.1 подключен к первой линии 1.1 и к выходу элемента И..2 группы 2.2, а первый вход элемента И 3-2 - к второй линии и к выходу элемента И k.l группы 2 . 1 . Второй вход элемента И 3-1 группы 2.1и второй вход элемента И 4.2 группы 2.2 подключены к шине 5 управления переключателя. Второй вход элемента 3.2 Группы 2.2соединен с неинвертирующим выхоЭдом элемента 6 памяти, а второй вход элемента И А.1 группы 2.1 - с инвертирующим выходом и информационным входом элемента 6 памяти. Первый вход элемента 8 неравнозначноет и связан с выходом элемента И 3..1 группы 2,1, а второй вход - с выходом элемента И 3.2 группы 2.2. Выход элемента 8 неравнозначности через резистор 9 элемента 7 задержки соединен с объединенными входами Сброс и Синхронизация элемента 6 памяти, а через последовательную цепочку из резистора 9 и конденсатора 10 элемента 7 задержки - с общим,полюсом источника питания (на фиг.1 не.показан). Вход$ элемента памяти соединен с положительным полюсом источника(значение логической 1). Элементы И 3 и-А каждой группы являются элементами с тремя состояниями: Нуль, Единица и Разомкнуто (высокое выходное сопротивление. Состояние элемента зависит от сигнала на управляющем (второ/)входе. Если сигнал на управляющем входе равен единице,.элемент находится в третьем состоянии. Если же этот сигнал равен нулю, состояние элемента определяется состоянием первого входа (линии. Резисторно-емкостной элемент 7 , задержки служит для реализации необходимого временного сдвига сигналов в линиях. В качестве элемента 6 памяти используется фронтовой триггер. На фиг.2а показан сигнал на линии 1.1; на фиг.26 - сигнал на линии 1.2; на фиг.2в - сигнал на втором входе элемента И 3.2 (сигнал на прямом выходе элемента 6 памяти); на фиг.2г - сигнал на выходе элемента И 3.2 группы 2.2 (сигнал на выходе элемента И .2 группы 2.2); на фиг.2д - сигнал на инверсном выходе элемента 6 памяти; на фиг.2е - сигнал на выходе элемента И 4.1 группы 2.1;на фиг.2ж - сигнал на шине 5 управления (показано нулевое значение сигнала); на фиг.2з - сигнал на синхровходе элемента б памяти (сигнал на входе Сброс элемента о памяти; . Заштрихованные области соответствуют разомкнутому (третьему состоянию (фиг.2г и е). Переключатель линий работает следуюи1им образом (фиг.1 и 2) . На шину 5 управления подлетел сигнал разрешения (логический ) или запрета (логическая 1 передачи. Пусть, например, передача разрешена ( фиг. 2ж). 3 зависимости от состояния линий 1.1 и 1.2 возможны четыре различные комбинации. Пусть, например, в начальный момент обе линии находятся в единичном состоянии, а триггер 6 в нулевом (фиг.2а, б ид) .В этом случае на его неинвертирующем выходе присутствует нулевой сигнал (фиг.2в), а на выходе элемента И 3.2 группы 2.2 - :сигнал, совпадающий с сигналом в линии 1.2, т.е. Единица (Оиг.2г). Такой же сигнал и на выходе .элемента И k.2, поскольку на шину 5 управления подано Разрешение фиг.2ж). По этой же причине на выходе элемента И 3-1 группы 2.1 существует единичный сигнал Сфиг.2а. Поскольку на второй вход элемента И 4.1 группы 2.1 подана Единица (фиг..2д), элемент +.1 находится в состоянии Разомкнуто (фиг.2е). С выходов элементов И 3.1 и 3.2 групп 2.1 и 2.2 единичные сигналы подаются на элемент 8 неравнозначности и нулевой сигнал с его выхода снимается через элемент 7 задержки на входы Сброс и Синхронизация ( фиг.2з ) элемента 6 памяти. Таким образом, при единичных сигналах на линиях 1.1 и 1.2 передача из линии в линию отсутствует. Как только на линии 1.1 появляется Нуль (фиг.2а), он снимается с выхода элемента 3.1 группы 2.1 и подается на вход элемента 8 неравнозначности, с выхода которого снимает ся единичный сигнал.. Последний через резисторно-емкостной элемент 7 задер с задержкой t поступает на вход Сброс и выход синхронизации элемен та 6 памяти (фиг.2з). Схема фронтово го триггера 6 реализована так,что , сигнал по входу Сброс отрабатывает ся с опережением относительно входа Синхронизация. В момент появления единичного си1- нала на входе Синхронизация элемен та 6 памяти изменяется состояние последнего на единичное (фиг.2в и 2д, вследствие чего элемент И 3.2 группы 2.2 переходит в третье состояние (фиг.2г), а элемент И .1 группы 2.1 транслирует нулевой сигнал (фиг.2е. Таким образом, при соотношении сигналов линий 1.1 и 1.2 Ноль и Единица соответственно происходит коммутацияпередачи нулевого сигнала 5 из линии 1.1 в линию 1.2 ( группа 2.1 замкнута, группа 2.2 разомкнута). Если теперь появляется нулевой сигнал и в линии 1.2 (фиг.2бЛ то, поскольку на втором оходе элемента И 3.2 группы 2.2 держится Единица « (Оиг.2в), состояние элемента И 3.2 не изменяется, остается третье состояние фиг.2г, а следовательно, и в остальной части схемы изменений не происходит (фиг.2д,е и з), т.е. сохраняется передача из линии 1.1 в линию 1.2 (продолжается передача с линии, в которой раньше появился Ноль). Так происходит до тех пор. пока сигнал Ноль в линии 1.1 не изменяется на сигнал Единица (фиг.2а). При этом на выходе элемента И группы 2.1 появляется единичный сигнал, на выходе элемента 8 неравнозначности - нулевой, который через элемент 7 задержки с заде ржкойТя, поступает на входы Сброс и Синхронизация элемента 6 памяти (фиг.2з) и изменяет его состояние. На втором входе элемента И 3.2 появляется Ноль (фиг.2в), на выходе тоже Ноль (фиг.2г}, вследствие чего элемент И Д.1 переходит в третье состояние (фиг.2е), в результате чего группа 2.1 размыкается и происходит передача из линии 1.2 в линию 1.1. При пропадании нулевого сигнала в линии 1.2 (фиг. с выхода элемента И 3.2 единичный сигнал, подается на вход элемента 8 неравнозначности (фиг.2г, с выхода которого по-прежнему снимается нулевой сигнал на входы Сброс и Синхронизация элемента 6 памяти (фиг.2з, сохраняя состояние последнего неизменным. Передача из линии 1.2 прекращается, и переключатель линии приходит в исходное состояние. Использование изобретения позволяет значительно yпpoctить переключатель по сравнению с прототипом при сохранении основных характеристик. Данный переключатель содержит в 1,8 раз меньше корпусов ( конденсатор плюс резистор считается за один корпус). ({юрмула изобретения Переключатель линий, содержащий включенную менду первой и второй линиями встречно-параллельно соединен797 58ные группы, каждая из которых сое- -тоиТ из последовательно соединенных по первым входам первого и второго элементов И, причем вторые вх9ды nepj00ГО элемента -И первой группы и второ-5 го элемента И второй группы подключен ны к шине уп авления, длемент памяти, неинвертирующий выход которого соединен с вторым входом пегрвого элемента И второй группы, резисторно-емкостной to элемент задержки, включен ый на входе элемента памяти, и блрк управления, от л и ч а ю щ и и : я тем, что, с целью упрощения, блок управления выполнен в виде элемента неравно- is значности, первый вход которого соединён с выходом первого элемента И первой группы, второй вход - с выходом первого элементна И В(торой группы, а выход через резистор резисторио;20 5,8 емкостного элемента задержки подключен к входу синхронизации и входу Сброс элемента, памяти, инвертируют щий выход которого соединен с информационным входом и подключен к второму входу второго элемента И первой группы. Источники информации, принятые йо внимание при экспертизе 1 .Dro3-FH/FP:Uri bus Switch. AorlJ, 1973, Document Но CSS-MO-F-101-19, .k-kO Line Log Is rlunit. 2. Техническая документация ПШ СМ «501 (переключатель шины)263.089. .496.33, блок элементов БЗ У управление расширителем). М., Институт электронных упрдвляюи их машин, 1980, альбом If 3, приложение 2 (прототип).

v

-4J

«p ea

Ma oci

-f-

-4J

crj

u

Авторы

Даты

1982-11-15—Публикация

1981-02-17—Подача