Изобретение относится к вычислительной технике. Устройство может быть использовано для мониторинга состояния сложных объектов, результатом которого является оценка многопараметрического интегрального показателя состояния объекта.

Известно контрольно-решающее устройство с оценкой достоверности прогнозирования качества канала связи (по авторскому свидетельству SU №1142895 (Н04В 3/46)), предназначенное для оценки параметров сигнала из канала связи, формирования прогнозируемой оценки и индикации результатов оценки. Устройство содержит блок выявления ошибок, блок текущей оценки, блок прогнозируемой оценки, первый и второй элементы задержки, первой и второй блоки проверки прогноза, элемент ИЛИ, счетчик, блок управления, формирователь измерительных интервалов, блок индикации, вычитающий счетчик, дополнительный элемент ИЛИ, дешифратор зон отсчета, дополнительный блок индикации. Устройство позволяет осуществлять последовательную сравнительную оценку множества однотипных элементов сложного объекта по заданным параметрам и принимать обоснованное решение по управлению сложным объектом.

Недостатком первого аналога является узкая область применения, обусловленная отсутствием возможности получения обобщенной (интегральной) оценки состояния одновременно контролируемых объектов по множеству заданных параметров сложного объекта.

Известно устройство поддержки принятия решений по предотвращению особых ситуаций при выполнении полета на летательном аппарате (по патенту RU №2417394 (G05B 23/02) от 18.05.2009 г.), содержащее блок выделения характерных состояний летательного аппарата и режимов полета, блок восприятия сигналов опасных ситуаций, блок выделения адреса экспертной рекомендации, блок памяти, блок приема, анализа и обработки контролируемых параметров, блок индикации и визуализации, который содержит лучевую диаграмму и выполнен с возможностью визуальной оценки, анализа и прогнозирования экипажем состояния «Экипаж - Воздушное судно» в каждый момент времени по тренду контролируемых параметров особых ситуаций, сформированному блоком приема, анализа и обработки контролируемых параметров.

Недостатком второго аналога является относительно низкая информативность и наглядность результатов оценки многопараметрического интегрального показателя состояния сложного объекта, обусловленная отображением результатов контроля и прогнозирования состояния объекта с помощью лучевой диаграммы. Лучевая диаграмма не отражает с приемлемой точностью результаты вычисления интегрального многопараметрического показателя состояния сложного объекта.

Наиболее близким по своей технической сущности (прототипом) к заявленному является устройство тестирования уровня инновационного интеллекта (по патенту №2522992 от 21.05.2014 года МПК G09В 7/00 (2006.01), позволяющее выполнять сравнительную оценку состояния сложных объектов по интегральному многопараметрическому показателю, который представляет собой свертку частных показателей в форме среднеквадратического значения нормированных частных показателей. Устройство содержит блок датчиков, блока кодирования ответов, блок вычисления частных показателей, блок индикации, блок управления, блок синхронизации, блок предварительных подсчетов баллов, блок вычисления обобщенного показателя. Устройство позволяет вычислять и представлять значения частных и обобщенного показателей в высокоинформативном и удобном для восприятия формате (на дискограмме единичной окружности), что дает принимающему решение лицу возможность без дополнительных вычислений и субъективных оценок определять состояние сложного объекта.

Однако, устройство-прототип имеет узкую область применения и, так как предполагает вычисление частных показателей только на основе специально разработанных тестовых заданий, требующих значительного времени анализа, обладает низкой информативностью результатов оценки параметров состояния объекта.

Заявленное устройство расширяет арсенал средств данного назначения.

Целью изобретения является расширение области применения устройства, повышение оперативности и информативности результатов вычисления интегрального многопараметрического показателя состояния сложного объекта.

Поставленная цель достигается тем, что в известное устройство измерения интегрального многопараметрического показателя, содержащее блок управления и синхронизации 1, снабженный F-разрядной шиной начальной установки счетчиков и регистров памяти, блок вычислителей 2, блок визуализации 5, D-разрядный второй 5.2 вход которого подключен к D-разрядному пятнадцатому 2.15 выходу блока вычислителей 2, а четвертый 5.4 вход подключен к одиннадцатому 1.11 выходу блока управления и синхронизации 1, десятиразрядный второй 1.2, третий 1.3, четвертый 1.4, пятый 1.5, шестой 1.6, седьмой 1.7 и восьмой 1.8 выходы которого подключены соответственно к десятиразрядному шестому 2.6, седьмому 2.7, восьмому 2.8, девятому 2.9, десятому 2.10, двенадцатому 2.12 и тринадцатому 2.13 входам блока вычислителей 2 дополнительно введены накапливающий сумматор 3 и делитель 4, A-разрядный пятый 4.5 выход, третий 4.3 и A-разрядный первый 4.1 входы которого подключены соответственно к A-разрядному первому 5.1 входу блока визуализации 5, десятому 1.10 выходу блока управления и синхронизации 1 и A-разрядному четвертому 3.4 выходу накапливающего сумматора 3, A-разрядный первый 3.1 вход накапливающего сумматора 3 подключен к A-разрядному четырнадцатому 2.14 выходу блока вычислителей 2, первый 1.1 выход блока управления и синхронизации 1 подключен к объединенным пятому 2.5 входу блока вычислителей 2, второму 3.2 входу накапливающего сумматора 3, второму 4.2 входу делителя 4 и третьему 5.3 входу блока визуализации 5, девятый 1.9 выход блока управления и синхронизации 1 подключен к третьему 3.3 входу накапливающего сумматора 3, A-разрядный двенадцатый 1.12 выход блока управления и синхронизации 1 подключен к объединенным A-разрядным одиннадцатому 2.11, четвертому 4.4 и пятому 5.5 входам соответственно блока вычислителей 2, делителя 4 и блока визуализации 5, блок вычислителей 2 снабжен C-разрядными первым 2.1, вторым 2.2, третьим 2.3 и четвертым 2.4 входами для ввода значений исходных параметров.

Блок управления и синхронизации (БУС) 1 состоит из первого 1.1 и второго 1.2 регистров памяти, компаратора 1.3, счетчика адреса 1.4, генератора тактовых импульсов 1.5, счетчика тактовых импульсов 1.6, триггерного ключа 1.7, демультиплексора 1.8, логических элементов «ИЛИ» 1.9 и 1.13, элемента задержки 1.10, кнопок 1.11 «Сброс» и 1.12 «Пуск». На объединенные первые входы 1.11.1 и 1.12.1 указанных кнопок подают напряжение с уровнем логической «1», а на объединенные третьи входы 1.11.3 и 1.12.3 подают напряжение логического «0». Выход 1.11.3 кнопки «Сброс» (1.11) подключен к вторым входам 1.4.2 счетчика адреса 1.4, 1.13.2 логического элемента 1.13 и является первым 1.1 выходом БУС 1. Выход 1.12.3 кнопки «Пуск» (1.12) подключен к третьему 1.9.3 входу логического элемента «ИЛИ» 1.9, первый 1.9.1 и второй 1.9.2 входы которого подключены соответственно к девятому 1.8.9 и семнадцатому 1.8.17 выходам демультиплексора 1.8, а четвертый 1.9.4 выход подключен к третьему входу 1.7.3 триггерного ключа 1.7. С первого 1.8.1 по десятый 1.8.10 выходы демультиплексора 1.8 образуют десятиразрядный второй 1.2 выход БУС 1. С одиннадцатого 1.8.11 по девятнадцатый 1.8.19 выходы демультиплексора 1.8 являются соответственно с третьего 1.3 по одиннадцатый 1.11 выходами БУС 1. К первому входу 1.7.1 триггерного ключа 1.7 подключен выход 1.5.1 генератора тактовых импульсов 1.5. Выход 1.7.4 триггерного ключа 1.7 подключен к третьему входу 1.6.3 счетчика тактовых импульсов 1.6 и второму входу 1.8.2 демультиплексора 1.8. R-разрядный третий 1.4.3 выход счетчика адреса 1.4 подключен к R-разрядным двадцать первому 1.8.21 входу демультиплексора 1.8 и третьим 1.1.3 и 1.2.3 входам соответственно первого 1.1 и второго 1.2 регистров памяти. G-разрядные первый 1.3.1 и второй 1.3.2 входы компаратора 1.3 подключены соответственно к G-разрядным четвертому выходу 1.1.4 первого регистра памяти 1.1 и первому выходу 1.6.1 счетчика тактовых импульсов 1.6. Выход 1.3.3 компаратора 1.3 подключен ко второму 1.7.2 входу триггерного ключа 1.7 и через элемент задержки 1.10 к первым входам 1.4.1 и 1.13.1 соответственно счетчика адреса 1.4 и логического элемента «ИЛИ» 1.13. Выход 1.13.3 логического элемента 1.13 подключен к второму входу 1.6.2 счетчика тактовых импульсов 1.6. A-разрядный выход 1.2.4 второго регистра памяти 1.2 является двенадцатым 1.12 выходом БУС 1. G-разрядный первый 1.1.1 выход первого регистра памяти 1.1, первый 1.1.1 и второй 1.1.2 входы первого регистра памяти 1.1, R-разрядный вход 1.2.3 второго регистра памяти 1.2, A-разрядный выход 1.2.4 второго регистра памяти 1.2, первый 1.2.1 и второй 1.2.2 входы второго регистра памяти 1.2 образуют F-разрядную шину начальной установки БУС 1.

Блок вычислителей 2 состоит из четырех 2.1-2.4 блоков вычисления формальных показателей (БВФП), делителя 2.5 и счетчика адреса 2.6, C-разрядные, где С=3А входы 2.1.1, 2.2.1, 2.3.1, 2.4.1 БВФП являются соответственно C-разрядными первым 2.1, вторым 2.2, третьим 2.3 и четвертым 2.4 входами блока вычислителей 2. Десятиразрядные третьи входы 2.1.3 первого 2.1, 2.2.3 второго 2.2, 2.3.3 третьего 2.3 и 2.4.3 четвертого 2.4 БВФП объединены и образуют десятиразрядный шестой 2.6 вход блока вычислителей 2. B-разрядные седьмые входы 2.1.7 первого 2.1, 2.2.7 второго 2.2, 2.3.7 третьего 2.3 и 2.4.7 четвертого 2.4 БВФП объединены и подключены к 5-разрядному третьему 2.6.3 выходу счетчика адреса 2.6. А-разрядные пятые выходы 2.1.5 первого 2.1, 2.2.5 второго 2.2, 2.3.5 третьего 2.3, 2.4.5 четвертого 2.4 БВФП объединены и подключены к A-разрядному четвертому 2.5.4 входу делителя 2.5. C-разрядные шестые выходы 2.1.6 первого 2.1, 2.2.6 второго 2.2, 2.3.6 третьего 2.3 и 2.4.6 четвертого 2.4 БВФП образуют D-разрядный, где D=3C, пятнадцатый 2.15 выход блока вычислителей 2. Вторые входы 2.1.2 первого 2.1, 2.2.2 второго 2.2, 2.3.2 третьего 2.3, 2.4.2 четвертого 2.4 БВФП и первый вход 2.6.1 счетчика адреса 2.6 объединены и являются пятым 2.5 входом блока вычислителей 2. Четвертые входы 2.1.4 первого 2.1, 2.2.4 второго 2.2, 2.3.4 третьего 2.3 и 2.4.4 четвертого 2.4 БВФП являются соответственно десятым 2.10, девятым 2.9, восьмым 2.8 и седьмым 2.7 входами блока вычислителей 2. A-разрядные первый вход 2.5.1 и третий выход 2.5.3 делителя 2.5 являются соответственно одиннадцатым входом 2.11 и четырнадцатым 2.14 выходом блока вычислителей 2. Вторые входы 2.5.2 и 2.6.2 делителя 2.5 и счетчика адреса 2.6 являются соответственно двенадцатым 2.12 и тринадцатым 2.13 входами блока вычислителей 2.

Блок вычисления формальных показателей (БВФП) 2.1 состоит из трех 2.1.1-2.1.3 блоков вычисления частных показателей (БВЧП), накапливающего сумматора 2.1.4 и регистра памяти 2.1.5. Первый A-разрядный вход 2.1.5.1 регистра памяти 2.1.5 подключен к четвертому А-разрядному выходу 2АЛЛ накапливающего сумматора 2.1.4. Пятый А-разрядный выход 2.1.5.5 и четвертый 2.1.5.4 вход регистра памяти 2.1.5 являются соответственно А-разрядным пятым 2.1.5 выходом и четвертым 2.1.4 входом БВФП 2.1. Объединенные А-разрядные десятые выходы 2.1.1.10 первого 2.1.1, 2.1.2.10 второго 2.1.2, 2.1.3.10 третьего 2.1.3 БВЧП объединены и подключены к A-разрядному первому 2.1.4.1 входу накапливающего сумматора 2.1.4. B-разрядные девятые входы 2.1.1.9 первого 2.1.1, 2.1.2.9 второго 2.1.2, 2.1.3.9 третьего 2.1.3 БВЧП объединены и являются B-разрядным седьмым 2.1.7 входом БВФП 2.1. A-разрядные первые входы 2.1.1.1 первого 2.1.1, 2.1.2.1 второго 2.1.2, 2.1.3.1 третьего 2.1.3 БВЧП образуют С-разрядный первый 2.1.1 вход БВФП 2.1. Вторые входы 2.1.1.2 первого 2.1.1, 2.1.2.2 второго 2.1.2, 2.1.3.2 третьего 2.1.3 БВЧП, 2.1.4.2 накапливающего сумматора 2.1.4, 2.1.5.2 регистра памяти 2.1.5 объединены и являются вторым 2.1.2 входом блока вычисления формальных показателей 2.1. Соответственно объединенные с третьего по седьмой 2.1.1.3-2.1.1.7 входы первого 2.1.1, с третьего по седьмой 2.1.2.3-2.1.2.7 входы второго 2.1.2, с третьего по седьмой 2.1.3.3-2.1.3.7 входы третьего 2.1.3 БВЧП, а также восьмые входы 2.1.1.8 первого 2.1.1, 2.1.2.8 второго 2.1.2 и 2.1.3.8 третьего 2.1.3 БВЧП, третьи входы 2.1.4.3 накапливающего сумматора 2.1.4 и 2.1.5.3 регистра памяти 2.1.5 образуют десятиразрядный вход 2.1.3 БВФП 2.1. A-разрядные десятые выходы 2.1.1.10 первого 2.1.1, 2.1.2.10 второго 2.1.2, 2.1.3.10 третьего 2.1.3 БВЧП образуют C-разрядный шестой 2.1.6 выход БВФП 2.1.

Блок вычисления частных показателей (БВЧП) 2.1.1 состоит из первого 2.1.1.1, второго 2.1.1.3, третьего 2.1.1.5, четвертого 2.1.1.7 регистров памяти, компаратора 2.1.1.2, делителя 2.1.1.4 и умножителя 2.1.1.6. А-разрядные первый 2.1.1.6.1 вход и четвертый 2.1.1.6.4 выход вычислителя корня квадратного 2.1.1.6 подключены соответственно к A-разрядным пятому выходу 2.1.1.5.5 третьего регистра памяти 2.1.1.5 и первому 2.1.1.7.1 входу четвертого регистра памяти 2.1.1.7. A-разрядный пятый 2.1.1.7.5 выход четвертого регистра памяти 2.1.1.7 является десятым 2.1.1.10 выходом БВЧП 2.1.1. A-разрядный пятый 2.1.1.4.5 выход делителя 2.1.1.4 подключен к А-разрядному первому 2.1.1.5.1 входу третьего регистра памяти 2.1.1.5. А-разрядный выход 2.1.1.3.4 второго регистра памяти 2.1.1.3 подключен к А-разрядным первому 2.1.1.4.1 входу делителя 2.1.1.4 и третьему 2.1.1.2.3 входу компаратора 2.1.1.2. Выход 2.1.1.2.4 компаратора подключен к второму 2.1.1.3.2 входу второго регистра памяти 2.1.1.3. A-разрядный пятый 2.1.1.1.5 выход первого регистра памяти 2.1.1.1 подключен к A-разрядным первому входу 2.1.1.2.1 компаратора 2.1.1.2, первому входу 2.1.1.3.1 второго регистра памяти 2.1.1.3 и четвертому входу 2.1.1.4.4 делителя 2.1.1.4. A-разрядный первый вход 2.1.1.1.1 первого регистра памяти 2.1.1.1 является первым 2.1.1.1 входом БВЧП 2.1.1. Объединенные B-разрядные четвертые входы 2.1.1.1.4 и 2.1.1.5.4 соответственно первого 2.1.1.1 и третьего 2.1.1.5 регистров памяти являются B-разрядным девятым 2.1.1.9 входом БВЧП 2.1.1. Объединенные третьи входы 2.1.1.1.3, 2.1.1.3.3, 2.1.1.4.3, 2.1.1.5.3, 2.1.1.6.3, 2.1.1.7.3 соответственно первого регистра памяти 2.1.1.1, второго регистра памяти 2.1.1.3, делителя 2.1.1.4, третьего регистра памяти 2.1.1.5, умножителя 2.1.1.6, четвертого регистра памяти 2.1.1.7 и второй 2.1.1.2.2 вход компаратора 2.1.1.2 объединены и являются вторым 2.1.1.2 входом БВЧП 2.1.1. Вторые входы 2.1.1.1.2 первого регистра памяти 2.1.1.1, 2.1.1.4.2 делителя 2.1.1.4, 2.1.1.5.2 третьего регистра памяти 2.1.1.5, 2.1.1.6.2 умножителя 2.1.1.6, второй 2.1.1.7.2 и четвертый 2.1.1.7.4 входы четвертого регистра памяти 2.1.1.7 являются соответственно третьим 2.1.1.3, четвертым 2.1.1.4, пятым 2.1.1.5, шестым 2.1.1.6, седьмым 2.1.1.7 и восьмым 2.1.1.8 входами БВЧП 2.1.1.

Блок визуализации 5 состоит из регистра памяти 5.1, цифрового индикатора 5.2, компаратора 5.3, цветового индикатора 5.4 и сегментного индикатора 5.5. A-разрядные входы сегментного индикатора 5.5 с первого 5.5.1 по двенадцатый 5.5.12 образуют D-разрядный второй вход 5.2 блока визуализации 5. A-разрядный четвертый выход 5.1.4 регистра памяти 5.1 подключен к объединенным A-разрядным первым входам 5.2.1 цифрового индикатора 5.2 и 5.3.1 компаратора 5.3. Выход 5.3.3 компаратора 5.3 подключен к входу 5.4.1 цветового индикатора 5.4. A-разрядный первый вход 5.1.1 регистра памяти 5.1 является A-разрядным первым 5.1 входом блока визуализации 5. Второй 5.1.2 и третий 5.1.3 входы регистра памяти 5.1 являются соответственно третьим 5.3 и четвертым 5.4 входами блока визуализации 5. A-разрядный второй вход 5.3.2 компаратора 5.3 является пятым 5.5 входом блока визуализации 5.

Указанные буквенные обозначения имеют следующий смысл:

А - количество разрядов кода, соответствующего максимальному значению измеряемого показателя состояния;

В - количество разрядов двоичного кода, соответствующего максимальному количеству ячеек регистров памяти, используемых для запоминания значений исходных параметров;

С - количество разрядов кода, соответствующего суммарной разрядности шины исходных параметров от одного источника информации (в данном случае С=3А);

D - количество разрядов кода, соответствующего суммарной разрядности шины данных от блока вычислителей к блоку визуализации (в данном случае D=4C);

Е - количество разрядов кода, соответствующего максимальному количеству частных показателей;

F - количество разрядов кода шины начальной установки блока управления и синхронизации;

R - количество разрядов двоичного кода, соответствующего максимальному количеству программируемых этапов работы устройства;

G - количество разрядов двоичного кода, соответствующего максимальному размеру серий тактовых импульсов, поступающих на элементы устройства от блока управления и синхронизации;

Н - количество разрядов кода, соответствующего суммарной разрядности шины данных от блока управления и синхронизации (в данном случае Н=А+В).

Благодаря новой совокупности существенных признаков при реализации устройства обеспечивается многоуровневая оценка состояния сложного МПО по значениям измеренных исходных показателей. За счет автоматизации всех вычислительных процедур и наглядности отображения результатов оценки на индикационном поле в виде дискограммы единичной окружности обеспечивается расширение области применения, повышение оперативности и информативности результатов оценки состояния сложного МПО путем вычисления интегрального многопараметрического показателя.

В основу вычисления многоуровневого интегрального многопараметрического показателя (ИМПП) объекта положен принцип двухмерного представления вычисляемых показателей на индикационном поле в виде дискограммы единичной окружности, радиус которой R0=1 (фиг. 9). При этом численные значения параметров каждого уровня вычисления являются исходными для следующего за ним уровня вычисления ИМПП.

На первом и последующих уровнях вычислений ИМПП значения показателей будут определяться частью площади или полной площадью соответствующего сектора дискограммы, с последующей их сверткой для вычисления промежуточного интегрального показателя более высокого уровня.

Для описания характеристик дискограммы использованы следующие обозначения:

ИМПП - интегральный многопараметрический показатель.

- промежуточный интегральный показатель, где n=l, 2, … N - текущий номер уровня вычисления ИМПП, а N - общее число уровней вычисления интегральных показателей; j=l, 2, … J - текущий номер промежуточного интегрального показателя на n-ом уровне вычисления ИМПП; J - общее число промежуточных интегральных показателей на n-ом уровне вычисления ИМПП.

- промежуточный интегральный показатель, где n=l, 2, … N - текущий номер уровня вычисления ИМПП, а N - общее число уровней вычисления интегральных показателей; j=l, 2, … J - текущий номер промежуточного интегрального показателя на n-ом уровне вычисления ИМПП; J - общее число промежуточных интегральных показателей на n-ом уровне вычисления ИМПП.

ЧПji - частный показатель, где j=l, 2, … J - текущий номер соответствующего промежуточного интегрального показателя, J - общее число промежуточных интегральных показателей на первом уровне вычисления ИМПП; i=l, 2, … I - текущий номер частного параметра, принадлежащего j-му промежуточному интегральному показателю на первом уровне вычисления ИМПП, I - общее число частных параметров, принадлежащих j-му промежуточному интегральному показателю на первом уровне вычисления ИМПП.

ИПji - исходный параметр, где j=l, 2, … J - текущий номер соответствующего промежуточного интегрального показателя, J - общее число промежуточных интегральных показателей на первом уровне вычисления ИМПП; i=l, 2, … I - текущий номер частного параметра, принадлежащего j-му промежуточному интегральному показателю на первом уровне вычисления ИМПП, I - общее число частных параметров, принадлежащих j-му промежуточному интегральному показателю на первом уровне вычисления ИМПП.

- нормированное значение исходного параметра.

- нормированное значение исходного параметра.

На индикационном поле (см. фиг. 9) с учетом принятого шага дискретизации Δr, нанесены М - вписанных концентрических окружностей (ВКО). Общее число ВКО М=1/Δr-1. При Δr=0,1 число ВКО М=1/0,1-1=9.

Радиус m-й концентрической окружности rm=1-mΔr. Например, r1=1-1×0,1=0,9; r2=0,8 и т.д. (см. фиг. 9).

Ниже рассмотрен пример вычисления ИМПП из четырех промежуточных интегральных показателей, каждый из которых является сверткой трех частных показателей:

Последовательность вычисления ИМПП следующая.

1. Из общего числа предварительно измеренных исходных параметров ИПji, определяющих соответствующие частные показатели первого уровня (n=1) ЧПji и промежуточные интегральные показатели второго уровня  , выделяют наибольший исходный параметр:

, выделяют наибольший исходный параметр:

2. Нормируют измеренные значения исходных параметров (1) на соответствующие максимальные значения (2).

3. Округляют нормированные значения частных показателей (3) с учетом принятого шага дискртизации Δr=0,1.

Пример: если  , то его округляют до

, то его округляют до  .

.

Каждое нормированное значение  фактически является радиусом rji ВКО на дискограмме, по которому можно вычислить площадь части сектора дискограммы, принадлежащего данному частному показателю.

фактически является радиусом rji ВКО на дискограмме, по которому можно вычислить площадь части сектора дискограммы, принадлежащего данному частному показателю.

4. Вычисляют частные показатели ЧПji.

Для этого рассчитывают площади частей секторов (1). Полная площадь единичной окружности дискограммы  .

.

Площадь одного сектора  . Площадь Sji(m) части i-го сектора, принадлежащего j-му частному показателю ЧПji на уровне m-ой ВКО с радиусом

. Площадь Sji(m) части i-го сектора, принадлежащего j-му частному показателю ЧПji на уровне m-ой ВКО с радиусом  - определяется соотношением:

- определяется соотношением:

Следовательно, частный показатель ЧПji, можно вычислить как отношение площади части i-го сектора на уровне m-ой ВКО Sji(m) к полной площади этого сектора Sc:

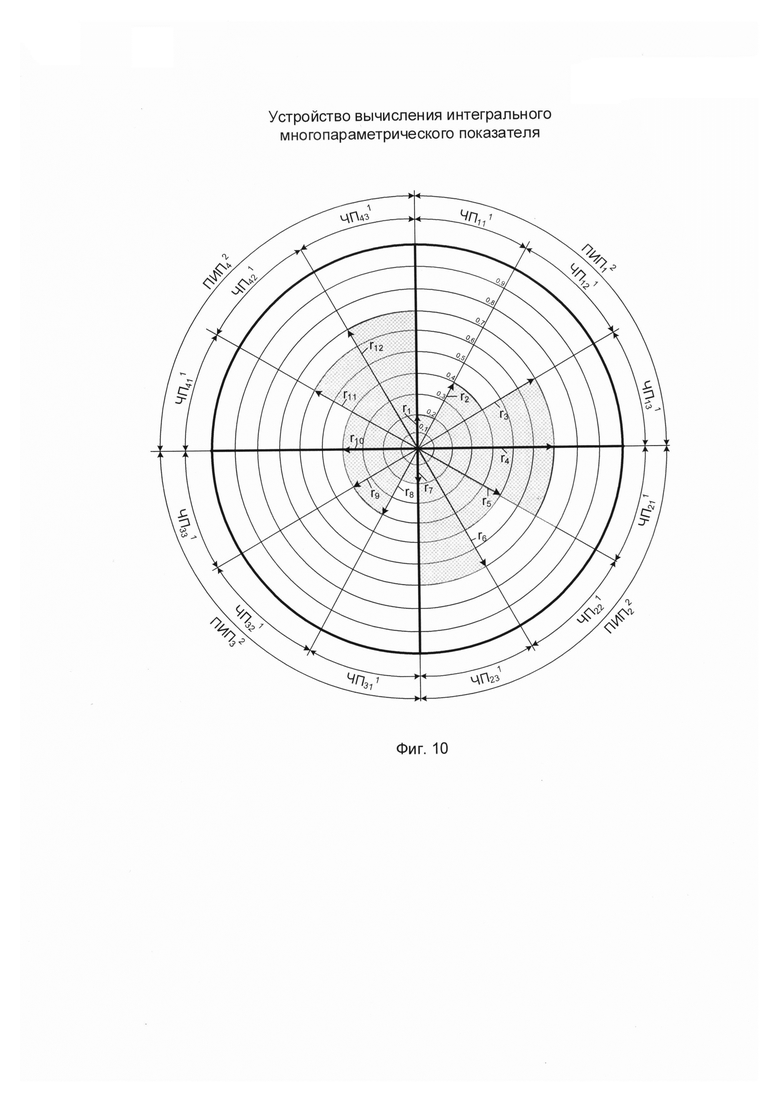

На фиг. 10 условно отражены площади частей всех секторов с радиусами rim ВКО:

Численные значения частных показателей ЧПij вычисляют по формуле (5).

Промежуточные интегральные показатели  второго уровня (n-2) определяют сверткой (I=3) значений ЧПji, принадлежащих каждому из них. Например,

второго уровня (n-2) определяют сверткой (I=3) значений ЧПji, принадлежащих каждому из них. Например,  при j=1 определяется значениями ЧП11, ЧП12, ЧП13.

при j=1 определяется значениями ЧП11, ЧП12, ЧП13.

Полная площадь сектора дискограммы SСД, охватываемая принадлежащими ему ЧП11, ЧП12, ЧП13, в рассматриваемом примере определяется формулой:

Часть площади этого сектора, заполненная на уровне ВКО с радиусами rj1, rj2, rj3:

Тогда значение  второго уровня определяется соотношением:

второго уровня определяется соотношением:

Значение ИМПП аналогично вычисляют как отношение части площади единичной окружности SЧД, охватывающей площади всех ЧПji к общей площади единичной окружности SД=1, т.е.:

Таким образом, состояние сложного многопараметрического объекта отображается посредством соотношения заштрихованных Sj и общей So площадей соответствующих секторов. Соотношение заштрихованной и полной площадей единичной окружности отражает уровень обобщенного показателя состояния объекта без привлечения каких-либо субъективных оценок исследователя.

В общем случае, в зависимости от степени сложности контролируемого объекта и количества исходных параметров может выполняться многоуровневая оценка состояния объекта. Интегральные показатели для каждого уровня оценки представляют собой свертку соответствующей группы показателей предыдущего уровня оценки, которая геометрически отображается заштрихованной частью соответствующего сектора на дискограмме.

Построенная дискрограмма единичной окружности и численное значение обобщенного показателя в сравнении с заданным критериальным значением позволяет обоснованно принимать решение о состоянии сложного объекта без дополнительных вычислений и субъективных оценок. Изобретение поясняется чертежами, на которых показаны:

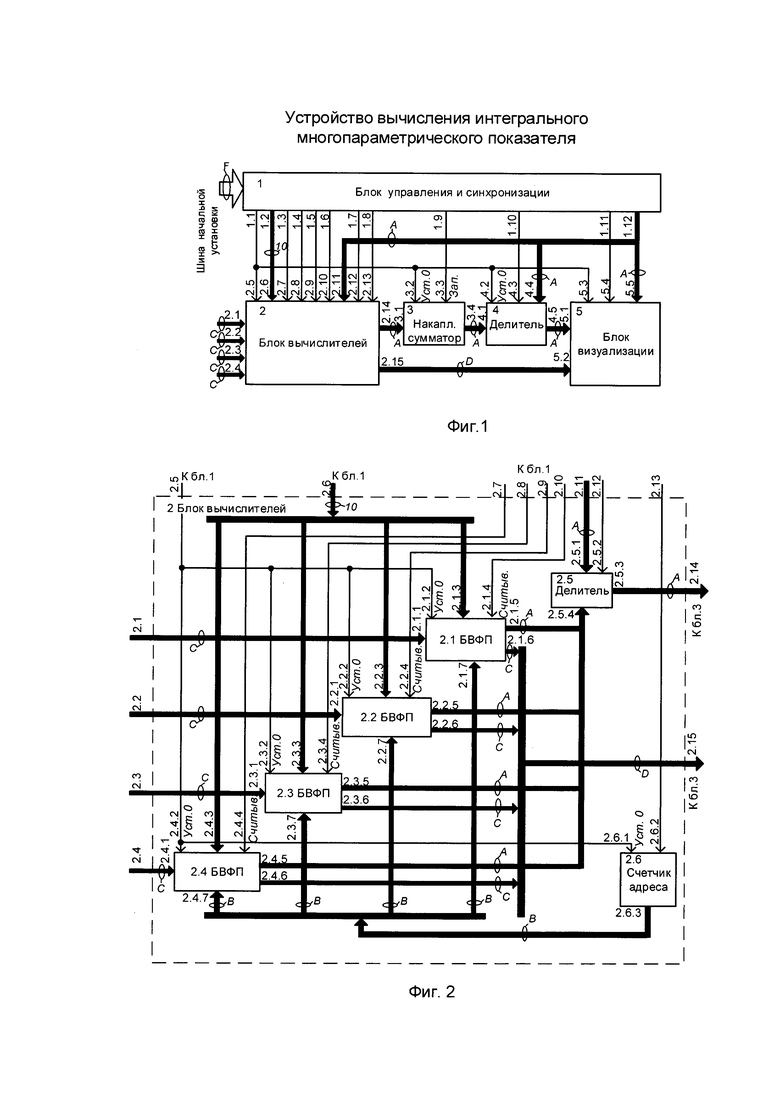

на фиг. 1 - структурная схема устройства;

на фиг. 2 - структурная схема блока вычислителей;

на фиг. 3 - структурная схема блока вычисления формальных показателей (БВФП);

на фиг. 4 - структурная схема блока вычисления частных показателей (БВЧП);

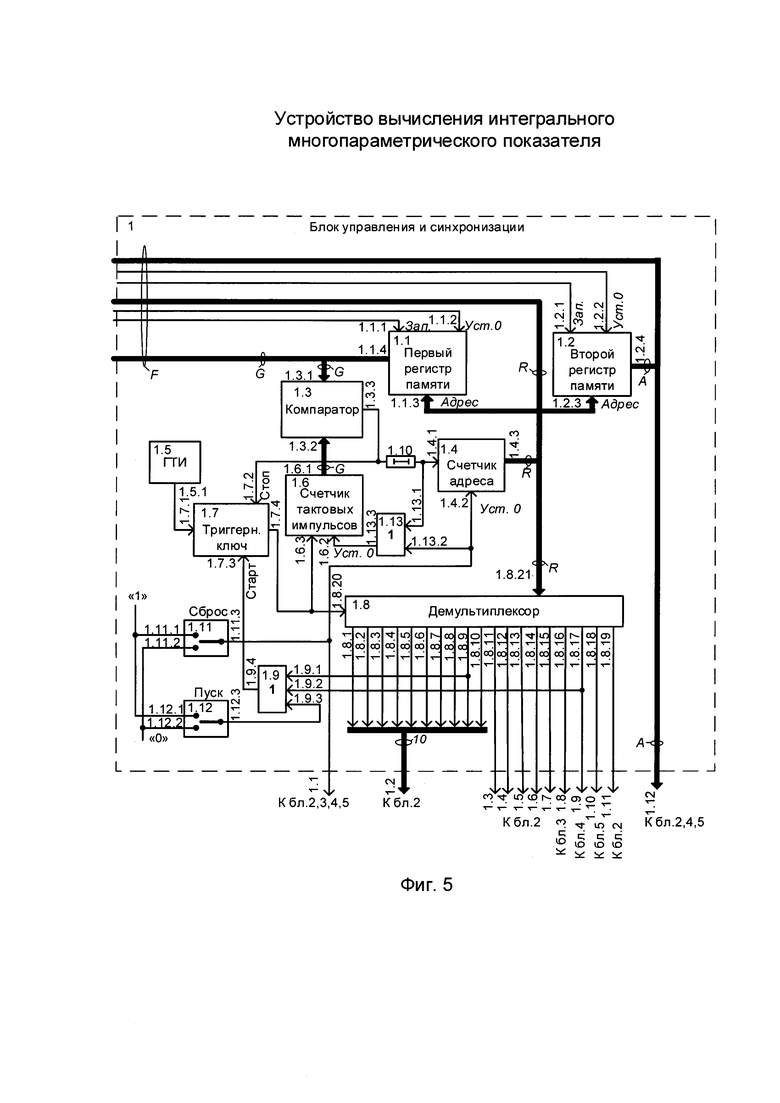

на фиг. 5 - структурная схема блока управления и синхронизации (БУС);

на фиг. 6 - структурная схема триггерного ключа;

на фиг. 7 - структурная схема блока визуализации;

на фиг. 8 - блок-схема алгоритма работы устройства;

на фиг. 9 - визуализация дискограммы единичной окружности;

на фиг. 10 - пример отображения на дискограмме единичной окружности результатов оценки частных и обобщенного показателя состояния контролируемого объекта.

Заявленное устройство, показанное на фиг. 1, содержит блок управления и синхронизации 1, блок вычислителей 2, накапливающий сумматор 3, регистр памяти 4, блок визуализации 5. На фиг. 1 показана также шина начальной установки устройства для ввода данных в регистры блока управления и синхронизации.

Все блоки устройства выполнены на стандартных потенциально-импульсных элементах.

Блок управления и синхронизации (БУС) 1 предназначен для хранения данных начальной установки, критериального значения интегрального показателя, а также для выдачи необходимых данных на основные блоки устройства. Реализация блока может быть различной, в частности, как показано на фиг. 5.

БУС 1 осуществляет выдачу данных в такие элементы устройства, как умножители, делители, компараторы. Блок управления и синхронизации 1 реализует принцип работы микропрограммного автомата [4, 5, 6]. Блок управления и синхронизации (БУС) 1 состоит из первого 1.1 и второго 1.2 регистров памяти, компаратора 1.3, счетчика адреса 1.4, генератора тактовых импульсов 1.5, счетчика тактовых импульсов 1.6, триггерного ключа 1.7, демультиплексора 1.8, логических элементов «ИЛИ» 1.9 и 1.13, элемента задержки 1.10, кнопок 1.11 «Сброс» и 1.12 «Пуск». На объединенные первые входы 1.11.1 и 1.12.1 указанных кнопок подают напряжение с уровнем логической «1», а на объединенные третьи входы 1.11.3 и 1.12.3 подают напряжение логического «0». Выход 1.11.3 кнопки «Сброс» подключен к вторым входам 1.4.2 счетчика адреса 1.4, 1.13.2 логического элемента 1.13 и является первым 1.1 выходом БУС 1. Выход 1.12.3 кнопки 1.12 «Пуск» подключен к третьему 1.9.3 входу логического элемента «ИЛИ» 1.9, первый 1.9.1 и второй 1.9.2 входы которого подключены соответственно к девятому 1.8.9 и семнадцатому 1.8.17 выходам демультиплексора 1.8, а четвертый 1.9.4 выход подключен к третьему входу 1.7.3 триггерного ключа 1.7. С первого 1.8.1 по десятый 1.8.10 выходы демультиплексора 1.8 образуют десятиразрядный второй 1.2 выход БУС 1. С одиннадцатого 1.8.11 по девятнадцатый 1.8.19 выходы демультиплексора 1.8 являются соответственно с третьего 1.3 по одиннадцатый 1.11 выходами БУС 1. К первому входу 1.7.1 триггерного ключа 1.7 подключен выход 1.5.1 генератора тактовых импульсов 1.5. Выход 1.7.4 триггерного ключа 1.7 подключен к третьему входу 1.6.3 счетчика тактовых импульсов 1.6 и двадцатому входу 1.8.20 демультиплексора 1.8. R-разрядный третий 1.4.3 выход счетчика адреса 1.4 подключен к R-разрядным двадцать первому 1.8.21 входу демультиплексора 1.8 и третьим 1.1.3 и 1.2.3 входам соответственно первого 1.1 и второго 1.2 регистров памяти. G-разрядные первый 1.3.1 и второй 1.3.2 входы компаратора 1.3 подключены соответственно к G-разрядным четвертому выходу 1.1.4 первого регистра памяти 1.1 и первому выходу 1.6.1 счетчика тактовых импульсов 1.6. Выход 1.3.3 компаратора 1.3 подключен ко второму 1.7.2 входу триггерного ключа 1.7 и через элемент задержки 1.10 к первым входам 1.4.1 и 1.13.1 соответственно счетчика адреса 1.4 и логического элемента «ИЛИ» 1.13. Выход 1.13.3 логического элемента 1.13 подключен к второму входу 1.6.2 счетчика тактовых импульсов 1.6. A-разрядный выход 1.2.4 второго регистра памяти 1.2 является двенадцатым 1.12 выходом БУС 1. G-разрядный первый 1.1.1 выход первого регистра памяти 1.1, первый 1.1.1 и второй 1.1.2 входы первого регистра памяти 1.1, R-разрядный вход 1.2.3 второго регистра памяти 1.2, A-разрядный выход 1.2.4 второго регистра памяти 1.2, первый 1.2.1 и второй 1.2.2 входы второго регистра памяти 1.2 образуют F-разрядную шину начальной установки БУС 1.

Триггерный ключ пропускает импульсы равной длительности. Триггерный ключ 1.7.2 может быть реализован различным образом, в частности, как показано на фиг. 6. Он состоит из первого 1.7.1.1 и второго 1.7.1.3 RS-триггеров, элемента инверсии 1.7.1.2 и элемента «И» 1.7.1.4. Выход первого триггера 1.7.1.1 подключен к D-входу второго триггера 1.7.1.3. Выход второго триггера 1.7.1.3 подключен ко второму входу элемента «И» 1.7.1.4. Синхронизирующий вход второго триггера 1.7.1.3 подключен к выходу элемента инверсии 1.7.1.2. Входы элемента инверсии 1.7.1.2 и элемента «И» 1.7.1.4 объединены и образуют первый информационный вход (1.7.1) триггерного ключа 1.7.2 Инверсный R-вход первого триггера 1.7.1.1 является вторым (1.7.2) управляющим входом «Стоп» триггерного ключа 1.7.2. Синхронизирующий вход первого триггера 1.7.1.1 является третьим (1.7.3) управляющим входом «Старт» триггерного ключа. Выход элемента «И» 1.7.1.4 является четвертым (1.7.4) информационным выходом триггерного ключа 1.7.2.

Все элементы БУС 1 известны и описаны в доступной литературе [1, 2].

Блок вычислителей 2 предназначен для реализации унифицированных вычислительных процедур в процессе определения интегрального многопараметрического показателя. Блок вычислителей 2 может быть реализован различным образом, например, как показано на фиг. 2. В данном случае блок вычислителей 2 состоит из четырех 2.1-2.4 блоков вычисления формальных показателей (БВФП), делителя 2.5 и счетчика адреса 2.6. С-разрядные, где С=3А входы 2.1.1, 2.2.1, 2.3.1, 2.4.1 БВФП являются соответственно С-разрядными первым 2.1, вторым 2.2, третьим 2.3 и четвертым 2.4 входами блока вычислителей 2. Десятиразрядные третьи входы 2.1.3 первого 2.1, 2.2.3 второго 2.2, 2.3.3 третьего 2.3 и 2.4.3 четвертого 2.4 БВФП объединены и образуют десятиразрядный шестой 2.6 вход блока вычислителей 2. B-разрядные седьмые входы 2.1.7 первого 2.1, 2.2.7 второго 2.2, 2.3.7 третьего 2.3 и 2.4.7 четвертого 2.4 БВФП объединены и подключены к 5-разрядному третьему 2.6.3 выходу счетчика адреса 2.6. А-разрядные пятые выходы 2.1.5 первого 2.1, 2.2.5 второго 2.2, 2.3.5 третьего 2.3, 2.4.5 четвертого 2.4 БВФП объединены и подключены к A-разрядному четвертому 2.5.4 входу делителя 2.5. С-разрядные шестые выходы 2.1.6 первого 2.1, 2.2.6 второго 2.2, 2.3.26 третьего 2.3 и 2.4.6 четвертого 2.4 БВФП образуют D-разрядный, где D=3C, пятнадцатый 2.15 выход блока вычислителей 2. Вторые входы 2.1.2 первого 2.1, 2.2.2 второго 2.2, 2.3.2 третьего 2.3, 2.4.2 четвертого 2.4 БВФП и первый вход 2.6.1 счетчика адреса 2.6 объединены и являются пятым 2.5 входом блока вычислителей 2. Четвертые входы 2.1.4 первого 2.1, 2.2.4 второго 2.2, 2.3.4 третьего 2.3 и 2.4.4 четвертого 2.4 БВФП являются соответственно десятым 2.10, девятым 2.9, восьмым 2.8 и седьмым 2.7 входами блока вычислителей 2. A-разрядный первый вход 2.5.1 и третий 2.5.3 выход делителя 2.5 являются соответственно одиннадцатым 2.11 входом и четырнадцатым 2.14 выходом блока вычислителей 2. Вторые входы 2.5.2 делителят 2.5 и 2.6.2 счетчика адреса 2.6 являются соответственно двенадцатым 2.12 и тринадцатым 2.13 входами блока вычислителей 2.

Все элементы блока вычислителей 2 известны и описаны в доступной литературе [1, 2].

БВФП 2.1-2.4 являются однотипными, их количество соответствует количеству элементов, составляющих сложный многопараметрический объект (МПО). БВФП предназначен для автоматизации вычислений формальных (промежуточных) показателей путем обеспечения одновременной работы БВЧП, суммирования и запоминания значений частных показателей.

БВФП может быть реализован различным образом, например, как показано на фиг. 3. В данном случае БВФП состоит из трех 2.1.1-2.1.3 блоков вычисления частных показателей (БВЧП), накапливающего сумматора 2.1.4 и регистра памяти 2.1.5. В общем случае количество БВЧП соответствует количеству оцениваемых частных показателей, которые учитывают для оценки состояния элемента сложного многопараметрического объекта. Первый А-разрядный вход 2.1.5.1 регистра памяти 2.1.5 подключен к четвертому A-разрядному выходу 2.1.4.4 накапливающего сумматора 2.1.4. Пятый A-разрядный выход 2.1.5.5 и четвертый 2.1.5.4 вход регистра памяти 2.1.5 являются соответственно A-разрядным пятым 2.1.5 выходом и четвертым 2.1.4 входом БВФП 2.1. Объединенные A-разрядные десятые выходы 2.1.1.10 первого 2.1.1, 2.1.2.10 второго 2.1.2, 2.1.3.10 третьего 2.1.3 БВЧП объединены и подключены к A-разрядному первому 2.1.4.1 входу накапливающего сумматора 2.1.4. B-разрядные девятые входы 2.1.1.9 первого 2.1.1, 2.1.2.9 второго 2.1.2, 2.1.3.9 третьего 2.1.3 БВЧП объединены и являются B-разрядным седьмым 2.1.7 входом БВФП 2.1. A-разрядные первые входы 2.1.1.1 первого 2.1.1, 2.1.2.1 второго 2.1.2, 2.1.3.1 третьего 2.1.3 БВЧП образуют С-разрядный первый 2.1.1 вход БВФП 2.1. Вторые входы 2.1.1.2 первого 2.1.1, 2.1.2.2 второго 2.1.2, 2.1.3.2 третьего 2.1.3 БВЧП, 2.1.4.2 накапливающего сумматора 2.1.4, 2.1.5.2 регистра памяти 2.1.5 объединены и являются вторым 2.1.2 входом блока вычисления формальных показателей 2.1. Соответственно объединенные с третьего по седьмой 2.1.1.3-2.1.1.7 входы первого 2.1.1, с третьего по седьмой 2.1.2.3-2.1.2.7 входы второго 2.1.2, с третьего по седьмой 2.1.3.3-2.1.3.7 входы третьего 2.1.3 БВЧП, а также восьмые входы 2.1.1.8 первого 2.1.1, 2.1.2.8 второго 2.1.2 и 2.1.3.8 третьего 2.1.3 БВЧП, третьи входы 2.1.4.3 накапливающего сумматора 2.1.4 и 2.1.5.3 регистра памяти 2.1.5 образуют десятиразрядный вход 2.1.3 БВФП 2.1. A-разрядные десятые выходы 2.1.1.10 первого 2.1.1, 2.1.2.10 второго 2.1.2, 2.1.3.10 третьего 2.1.3 БВЧП образуют С-разрядный шестой 2.1.6 выход БВФП 2.1.

БВЧП предназначен для запоминания, нормализации поступающих на его вход в двоичном коде измеренных значений исходных показателей, характеризующих состояние элемента МПО, вычисления и запоминания средневадратического значения измеренных исходных показателей, которое является частным показателем состояния элемента МПО. Все БВЧП являются однотипными.

БВЧП может быть реализован различным образом, например, как показано на фиг. 4. В данном случае он состоит из первого 2.1.1.1, второго 2.1.1.3, третьего 2.1.1.5, четвертого 2.1.1.7 регистров памяти, компаратора 2.1.1.2, делителя 2.1.1.4 и умножителя 2.1.1.6. A-разрядные первый 2.1.1.6.1 вход и четвертый 2.1.1.6.4 выход умножителя 2.1.1.6 подключены соответственно к A-разрядным пятому выходу 2.1.1.5.5 третьего регистра памяти 2.1.1.5 и первому 2.1.1.7.1 входу четвертого регистра памяти 2.1.1.7. A-разрядный пятый 2.1.1.7.5 выход четвертого регистра памяти 2.1.1.7 является десятым 2.1.1.10 выходом БВЧП 2.1.1. A-разрядный пятый 2.1.1.4.5 выход делителя 2.1.1.4 подключен к A-разрядному первому 2.1.1.5.1 входу третьего регистра памяти 2.1.1.5. A-разрядный выход 2.1.1.3.4 второго регистра памяти 2.1.1.3 подключен к A-разрядным первому 2.1.1.4.1 входу делителя 2.1.1.4 и третьему 2.1.1.2.3 входу компаратора 2.1.1.2. Выход 2.1.1.2.4 компаратора подключен к второму 2.1.1.3.2 входу второго регистра памяти 2.1.1.3. A-разрядный пятый 2.1.1.1.5 выход первого регистра памяти 2.1.1.1 подключен к A-разрядным первому входу 2.1.1.2.1 компаратора 2.1.1.2, первому входу 2.1.1.3.1 второго регистра памяти 2.1.1.3 и четвертому входу 2.1.1.4.4 делителя 2.1.1.4. A-разрядный первый вход 2.1.1.1.1 первого регистра памяти 2.1.1.1 является первым 2.1.1.1 входом БВЧП 2.1.1. Объединенные B-разрядные четвертые входы 2.1.1.1.4 и 2.1.1.5.4 соответственно первого 2.1.1.1 и третьего 2.1.1.5 регистров памяти являются 5-разрядным девятым 2.1.1.9 входом БВЧП 2.1.1. Объединенные третьи входы 2.1.1.1.3, 2.1.1.3.3, 2.1.1.4.3, 2.1.1.5.3, 2.1.1.6.3, 2.1.1.7.3 соответственно первого регистра памяти 2.1.1.1, второго регистра памяти 2.1.1.3, делителя 2.1.1.4, третьего регистра памяти 2.1.1.5, умножителя 2.1.1.6, четвертого регистра памяти 2.1.1.7 и второй 2.1.1.2.2 вход компаратора 2.1.1.2 объединены и являются вторым 2.1.1.2 входом БВЧП 2.1.1. Вторые входы 2.1.1.1.2 первого регистра памяти 2.1.1.1, 2.1.1.4.2 делителя 2.1.1.4, 2.1.1.5.2 третьего регистра памяти 2.1.1.5, 2.1.1.6.2 умножителя 2.1.1.6, второй 2.1.1.7.2 и четвертый 2.1.1.7.4 входы четвертого регистра памяти 2.1.1.7 являются соответственно третьим 2.1.1.3, четвертым 2.1.1.4, пятым 2.1.1.5, шестым 2.1.1.6, седьмым 2.1.1.7 и восьмым 2.1.1.8 входами БВЧП 2.1.1.

Блок визуализации 5 предназначен для сравнения значения обобщенного показателя с заданным критериальным значением, отображения результатов оценки частных показателей состояния объекта в виде дискограммы единичной окружности (фиг. 9, 10). Для его реализации могут использоваться сегментный жидкокристаллический индикатор, цифровой и цветовой индикаторы. Все элементы блока визуализации известны и описаны в доступной литературе [1, 2].

Блок визуализации 5 может быть реализован различным образом, например, как показано на фиг. 7. В данном случае блок визуализации 5 состоит из регистра памяти 5.1, цифрового индикатора 5.2, компаратора 5.3, цветового индикатора 5.4 и сегментного индикатора 5.5. А-разрядные входы сегментного индикатора 5.5 с первого 5.5.1 по двенадцатый 5.5.12 образуют D-разрядный второй вход 5.2 блока визуализации 5. A-разрядный четвертый выход 5.1.4 регистра памяти 5.1 подключен к объединенным A-разрядным первым входам 5.2.1 цифрового индикатора 5.2 и 5.3.1 компаратора 5.3. Выход 5.3.3 компаратора 5.3 подключен к входу 5.4.1 цветового индикатора 5.4. A-разрядный первый вход 5.1.1 регистра памяти 5.1 является А-разрядным первым 5.1 входом блока визуализации 5. Второй 5.1.2 и третий 5.1.3 входы регистра памяти 5.1 являются соответственно третьим 5.3 и четвертым 5.4 входами блока визуализации 5. A-разрядный второй вход 5.3.2 компаратора 5.3 является пятым 5.5 входом блока визуализации 5.

Устройство работает следующим образом (см. также соответствующие позиции блок-схемы на фиг. 8).

Предварительно в блок управления и синхронизации БУС 1 через «Шину начальной установки» записывают данные, необходимые для согласования работы элементов устройства, а также критериальное значение обобщенного показателя. При этом в первый регистр памяти 1.1 БУС 1 записывают размер и последовательность следования серий тактовых импульсов, во второй регистр памяти 1.2 записывают критериальное значение обобщенного показателя и количество оцениваемых частных показателей состояния объекта.

Устройство готовится к работе нажатием кнопки «Сброс» 1.11 БУС 1 (позиция 1), при этом все счетчики и накопительные сумматоры устройства устанавливают в исходное (нулевое) состояние (позиция 2). Устройство переходит в режим «Ожидание пуска» (позиция 3).

Запуск устройства осуществляется однократным нажатием на кнопку «Пуск» 1.12 БУС 1 (позиция 4), при этом открывается триггерный ключ 1.7 и тактовые импульсы от генератора тактовых импульсов (ГТИ) 1.5 поступают на третий (1.6.3) вход счетчика тактовых импульсов 1.6. При этом счетчик тактовых импульсов 1.6 формирует двоичный код, который подается на второй вход (1.3.2) компаратора 1.3 БУС 1. Из начального адреса регистра памяти 1.1 на первый (1.3.1) вход компаратора 1.3 БУС 1 подается двоичный код первого этапа работы устройства. При совпадении двоичных кодов на входах компаратора 1.3 с его выхода (1.3.3) через элемент задержки 1.10 поступает потенциал логической единицы на вход (1.4.1) счетчика адреса 1.4 БУС 1. Счетчик адреса 1.4 изменяет свое состояние, и с его R-разрядного выхода (1.4.1) поступает двоичный код, соответствующего этапа работы устройства на R-разрядный двадцать первый вход (1.8.21) демультиплексора 1.8. Через двадцатый вход (1.8.20) демультиплексора 1.8 тактовые импульсы поступают на соответствующие выходы демультиплексора 1.8, которые определяются кодом на его R-разрядном двадцать первом входе (1.8.21).

На первом этапе с входов 2.1-2.4 блока вычислителей 2 считывают измеренные значения исходных параметров и записывают в первые регистры 2.1.1.1-2.4.3.1 соответственно 2.1.1-2.4.3 БВЧП (позиция 5). При этом с 10-разрядного выхода 1.2 БУС 1 на вход 2.6 блока вычислителей 2 поступают тактовые импульсы, синхронизирующие работу БВЧП. Поступающие с выхода 1.8 БУС 1 на вход 2.13 блока вычислителей 2 тактовые импульсы устанавливают значения на 5-разрядном выходе 2.6.3 счетчика адреса 2.6, которое определяет ячейки памяти регистров памяти 2.1.1.1-2.4.3.1 для записи двоичных кодов измеренных значений исходных параметров состояния объекта. Одновременно на этом этапе с помощью компараторов 2.1.1.2-2.4.3.2 определяют и записывают во вторые регистры памяти 2.1.1.3-2.4.3.3 максимальные из поступающих на входы БВЧП значений исходных параметров.

Таким образом, реализуется операция определения максимальных значений исходных параметров для каждого частного показателя:

Указанная операция выполняется одновременно во всех БВФП и БВЧП. В конце первого этапа работы устройства первые регистры памяти 2.1.1.1-2.4.3.1 содержат записанные двоичные коды измеренных значений исходных параметров, а вторые регистры 2.1.1.3-2.4.3.3 содержат наибольшие из значений исходных параметров состояния объекта. Первый этап заканчивают при появлении на выходе компаратора 1.3 БУС 1 потенциала логической единицы (позиция 6), с помощью которого останавливают подачу тактовых импульсов через триггерный ключ 1.7, обнуляют счетчик таковых импульсов 1.6 и переводят в следующее состояние счетчик адреса 1.4 БУС 1 (позиция 7).

На втором этапе с помощью счетчика адреса 2.6 и делителей 2.1.1.4-2.4.3.4 вычисляют нормированные значения исходных параметров и записывают в третьи регистры 2.1.1.5-2.4.3.5 БВЧП 2.1.1-2.4.3 (позиция 8).

На данном этапе выполняется операция путем деления:

Указанная операция выполняется одновременно во всех БВФП и БВЧП. Второй этап заканчивают при появлении на выходе компаратора 1.3 БУС 1 потенциала логической единицы (позиция 9), с помощью которого останавливают подачу тактовых импульсов через триггерный ключ 1.7, обнуляют счетчик таковых импульсов 1.6 и переводят в следующее состояние первый счетчик адреса 1.4 БУС 1 (позиция 10). Округление нормированных значений исходных параметров происходит в соответствии с выбранной разрядностью двоичного кода, с помощью которого кодируются значения исходных параметров.

На третьем этапе с помощью счетчика 2.6 и умножителей 2.1.1.6-2.4.3.6 и четвертых регистров памяти 2.1.1.7-2.4.3.7 БВЧП 2.1.1-2.4.3 вычисляют и запоминают значения частных показателей состояния (позиция 11).

На данном этапе реализуется операция возведения в квадрат:

Указанная операция выполняется одновременно во всех БВФП и БФЧП. Третий этап заканчивают при появлении на выходе компаратора 1.3 БУС 1 потенциала логической единицы (позиция 12), с помощью которого останавливают подачу тактовых импульсов через триггерный ключ 1.7, обнуляют счетчик таковых импульсов 1.6 и переводят в следующее состояние первый счетчик адреса 1.4 БУС 1 (позиция 13).

На четвертом этапе с помощью четвертых регистров памяти 2.1.1.7-2.4.1.7 накапливающих сумматоров 2.1.4-2.4.4 вычисляют значения формальных промежуточных показателей, двоичные коды которых запоминают в регистрах памяти 2.1.5-2.4.5 БВФП 2.1-2.4 (позиция 14).

На данном этапе реализуется операция сложения:

Указанная операция выполняется одновременно во всех БВФП и БФЧП. Четвертый этап заканчивают при появлении на выходе компаратора 1.3 БУС 1 потенциала логической единицы (позиция 15), с помощью которого останавливают подачу тактовых импульсов через триггерный ключ 1.7, обнуляют счетчик таковых импульсов 1.6 и переводят в следующее состояние первый счетчик адреса 1.4 БУС 1 (позиция 16).

На пятом этапе работы устройства с помощью регистров памяти 2.1.5-2.4.5 БВФП делителя 2.5 блока вычислителей 2 и накапливающего сумматора 3 определяют значения промежуточных интегральных показателей (позиция 17).

На данном этапе реализуется операция вычисления среднеарифметического путем деления записанных в регистрах памяти 2.1.5-2.4.5 БВФП 2.1-2.4 значений формальных промежуточных показателей на соответствующий делитель:

Таким образом, операция выполняется путем одновременных циклов считывания значений  из каждого БВФП, деления на константу, записи в регистры памяти 2.1.5-2.4.5 БВФП 2.1-2.4, последовательного считывания значений ПИП и сложения их в накапливающем сумматоре 3 (позиция 18), т.е. осуществляют операцию сложения:

из каждого БВФП, деления на константу, записи в регистры памяти 2.1.5-2.4.5 БВФП 2.1-2.4, последовательного считывания значений ПИП и сложения их в накапливающем сумматоре 3 (позиция 18), т.е. осуществляют операцию сложения:

Вычисленное значение формального интегрального многопараметрического показателя (ИМППФ) сохраняется в накапливающем сумматоре 3.

Пятый этап заканчивают при появлении на выходе компаратора 1.3 БУС 1 потенциала логической единицы (позиция 19), с помощью которого останавливают подачу тактовых импульсов через триггерный ключ 1.7, обнуляют счетчик таковых импульсов 1.6 и переводят в следующее состояние первый счетчик адреса 1.4 БУС 1 (позиция 20).

На шестом этапе с помощью накапливающего сумматора 3 и делителя 4 определяют значение интегрального многопараметрического показателя (позиция 21). В данном цикле реализуется операция вычисления среднеарифметического путем деления полученного ранее и записанного в накапливающем сумматоре 3 значения формального интегрального показателя на соответствующий делитель:

Результат вычисления ИМПП записывают в регистр памяти 5.1 БВ 5. Шестой этап заканчивают при появлении на выходе компаратора 1.3 БУС 1 потенциала логической единицы (позиция 22), с помощью которого останавливают подачу тактовых импульсов через триггерный ключ 1.7, обнуляют счетчик таковых импульсов 1.6 и переводят в следующее состояние первый счетчик адреса 1.4 БУС 1 (позиция 23).

На седьмом этапе с помощью регистра памяти 5.1 и компаратора 5.3 блока визуализации 5 значение ИМПП сравнивают с критериальным значением, двоичный код которого поступает на второй вход 5.3.2 компаратора 5.3 с выхода 1.12 БУС 1. Отображают на сегментном индикаторе значения частных показателей закрашиванием соответствующих секторов окружности и включают цветовой индикатор при превышении (снижении) значения ИМПП относительно заданного критериального значения. Результаты вычислений и сравнения отображают в виде дискограммы единичной окружности и в цифровом виде (фиг. 10) с помощью индикаторов 5.2, 5.4, 5.5 (позиция 24).

Таким образом, устройство позволяет оценивать состояние сложного объекта за счет многоуровневой без ограничения числа уровней оценки показателей состояния и получения обобщенного показателя в виде аддитивной свертки нормированных среднеквадратических значений исходных параметров состояния сложного объекта. С помощью нормализации значений измеренных исходных параметров уменьшается влияние случайных выбросов на достоверность результатов оценки обобщенного показателя состояния объекта. Параллельное выполнение вычислительных операций обеспечивает оперативность оценки, а за счет отображения результатов оценки в виде дискограммы единичной окружности достигается наглядность и обеспечивается возможность объективного мониторинга состояния сложного многопараметрического объекта.

СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ ИНФОРМАЦИИ.

1. Наумкина Л.Г. Цифровая схемотехника. Конспект лекций по дисциплине «Схемотехника». - М.: Издательство «Горная книга», Издательство Московского горного университета, 2008. - 308 с.

2. Подъяков Е.А., Орлик В.В. Импульсные и цифровые устройства: Учебное пособие. - Новосибирск: Изд-во НГТУ, 2005. - 116 с.

3. Описание изобретения к авторскому свидетельству СССР №957209 от 07.09.89 «Устройство для извлечения квадратного корня» авторов А.Н. Флоренсов, В.И. Потапов, М.Ю. Плотников (Омский политехнический институт).

4. Самофалов К.Г., Романкевич A.M., и др. Прикладная теория цифровых автоматов. - Киев. «Вища школа» 1987.

5. Соловьев Г.Н. Арифметические устройства ЭВМ. - М. «Энергия». 1978.

6. Савельев А.Я. Прикладная теория цифровых автоматов - М. «Высшая школа». 1987.

7. Вишнякова Н.Ф. Креативная психопедагогика. Психология творческого обучения. - Минск: РИВШ при БГУ. 1995. С 126.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ РОЛЕВОЙ ФУНКЦИИ УЧАСТНИКА ТВОРЧЕСКОГО КОЛЛЕКТИВА | 2013 |

|

RU2541431C1 |

| ПРИБОР ДЛЯ РЕЙТИНГОВОЙ ОЦЕНКИ УРОВНЯ ГОТОВНОСТИ К ИННОВАЦИОННОЙ ДЕЯТЕЛЬНОСТИ | 2014 |

|

RU2548478C1 |

| Способ и устройство автоматизированного структурирования мультикультурных учебных групп | 2016 |

|

RU2618387C1 |

| Система автоматической коммутации каналов связи и управления для средств радиотехнического обеспечения полетов | 2019 |

|

RU2723005C1 |

| ТЕСТЕР УРОВНЯ ИННОВАЦИОННОГО ИНТЕЛЛЕКТА ЛИЧНОСТИ | 2013 |

|

RU2522992C1 |

| ПОТОЛОЧНАЯ КОНСОЛЬ ДЛЯ КАБИНЫ ТЯЖЕЛЫХ КОММЕРЧЕСКИХ ТРАНСПОРТНЫХ СРЕДСТВ | 2019 |

|

RU2714835C1 |

| СПОСОБ ОЦЕНКИ КАЧЕСТВА КАНАЛА ПЕРЕДАЧИ ДАННЫХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2085045C1 |

| СПОСОБ ДИАГНОСТИКИ СОСТОЯНИЯ ПЛОДА И МАТЕРИ В АНТЕНАТАЛЬНЫЙ ПЕРИОД БЕРЕМЕННОСТИ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2012 |

|

RU2497445C1 |

| Оптико-электронный комплекс для оптического обнаружения, сопровождения и распознавания наземных и воздушных объектов | 2019 |

|

RU2701177C1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

Изобретение относится к вычислительной технике и может быть использовано для мониторинга состояния сложных объектов, результатом которого является оценка многопараметрического интегрального показателя состояния объекта. Техническим результатом является расширение области применения устройства, повышение оперативности и информативности результатов вычисления интегрального многопараметрического показателя состояния сложного объекта. Устройство состоит из блока управления и синхронизации, блока вычислителей, накапливающего сумматора, регистра памяти, блока визуализации, шины начальной установки устройства для ввода данных в регистры блока управления и синхронизации. 5 з.п. ф-лы, 10 ил.

1. Устройство вычисления интегрального многопараметрического показателя, содержащее блок управления и синхронизации (БУС) (1), снабженный F-разрядной шиной начальной установки счетчиков и регистров памяти, блок вычислителей (2), блок визуализации (5), D-разрядный второй (5.2) вход которого подключен к D-разрядному пятнадцатому (2.15) выходу блока вычислителей (2), а четвертый (5.4) вход подключен к одиннадцатому (1.11) выходу БУС (1), десятиразрядный второй (1.2), третий (1.3), четвертый (1.4), пятый (1.5), шестой (1.6), седьмой (1.7) и восьмой (1.8) выходы БУС 1 подключены соответственно к десятиразрядному шестому (2.6), седьмому (2.7), восьмому (2.8), девятому (2.9), десятому (2.10), двенадцатому (2.12) и тринадцатому (2.13) входам блока вычислителей (2), отличающееся тем, что дополнительно введены накапливающий сумматор (3) и делитель (4), A-разрядный пятый (4.5) выход, третий (4.3) и A-разрядный первый (4.1) входы которого подключены соответственно к A-разрядному первому (5.1) входу блока визуализации (5), десятому (1.10) выходу БУС (1) и A-разрядному четвертому (3.4) выходу накапливающего сумматора 3, A-разрядный первый (3.1) вход накапливающего сумматора (3) подключен к А-разрядному четырнадцатому (2.14) выходу блока вычислителей (2), первый (1.1) выход БУС (1) подключен к объединенным пятому (2.5) входу блока вычислителей (2), второму (3.2) входу накапливающего сумматора (3), второму (4.2) входу делителя (4) и третьему (5.3) входу блока визуализации (5), девятый (1.9) выход БУС (1) подключен к третьему (3.3) входу накапливающего сумматора 3, A-разрядный двенадцатый (1.12) выход БУС (1) подключен к объединенным А-разрядным одиннадцатому (2.11), четвертому (4.4) и пятому (5.5) входам соответственно блока вычислителей (2), делителя (4) и блока визуализации (5), блок вычислителей (2) снабжен С-разрядными первым (2.1), вторым (2.2), третьим (2.3) и четвертым (2.4) входами для ввода значений первичных параметров.

2. Устройство по п. 1, отличающееся тем, что БУС (1) состоит из первого (1.1) и второго (1.2) регистров памяти, компаратора (1.3), счетчика адреса (1.4), генератора тактовых импульсов (ГТИ) (1.5), счетчика тактовых импульсов (1.6), триггерного ключа (1.7), демультиплексора (1.8), логических элементов «ИЛИ» (1.9) и (1.13), элемента задержки (1.10), кнопок (1.11) «Сброс» и (1.12) «Пуск», на объединенные первые входы (1.11.1, 1.12.1) которых подают напряжение с уровнем логической «1», а на объединенные третьи входы (1.11.3, 1.12.3) подают напряжение логического «0», выход (1.11.3) кнопки «Сброс» (1.11) подключен к вторым входам (1.4.2) счетчика адреса 1.4, (1.13.2) логического элемента «ИЛИ» 1.13 и является первым (1.1) выходом БУС 1, выход (1.12.3) кнопки «Пуск» (1.12) подключен к третьему (1.9.3) входу логического элемента «ИЛИ» (1.9), первый (1.9.1) и второй (1.9.2) входы которого подключены соответственно к девятому (1.8.9) и семнадцатому (1.8.17) выходам демультиплексора (1.8), а четвертый (1.9.4) выход подключен к третьему входу (1.7.3) триггерного ключа (1.7), с первого (1.8.1) по десятый (1.8.10) выходы демультиплексора (1.8) образуют десятиразрядный второй (1.2) выход БУС (1), с одиннадцатого (1.8.11) по девятнадцатый (1.8.19) и семнадцатый (1.8.17) выходы демультиплексора (1.8) являются соответственно с третьего (1.3) по одиннадцатый (1.11) выходами БУС (1), к первому входу (1.7.1) триггерного ключа (1.7) подключен выход (1.5.1) генератора тактовых импульсов (1.5), выход (1.7.4) триггерного ключа (1.7) подключен к третьему входу (1.6.3) счетчика тактовых импульсов (1.6) и двадцатому входу (1.8.20) демультиплексора (1.8), R-разрядный третий (1.4.3) выход счетчика адреса (1.4) подключен к R-разрядным двадцать первому (1.8.21) входу демультиплексора (1.8) и третьим (1.1.3) и (1.2.3) входам соответственно первого (1.1) и второго (1.2) регистров памяти, G-разрядные первый (1.3.1) и второй (1.3.2) входы компаратора (1.3) подключены соответственно к G-разрядным четвертому выходу (1.1.4) первого регистра памяти (1.1) и первому выходу (1.6.1) счетчика тактовых импульсов (1.6), выход (1.3.3) компаратора (1.3) подключен ко второму (1.7.2) входу триггерного ключа 1.7 и через элемент задержки 1.10 к первым входам (1.4.1) и (1.13.1) соответственно первого счетчика адреса (1.4) и логического элемента «ИЛИ» (1.13), выход (1.13.3) которого подключен к второму входу (1.6.2) счетчика тактовых импульсов (1.6), А-разрядный выход (1.2.4) второго регистра памяти (1.2) является двенадцатым (1.12) выходом БУС (1), G-разрядный первый (1.1.1) выход первого регистра памяти (1.1), первый (1.1.1) и второй (1.1.2) входы первого регистра памяти (1.1), R-разрядный вход (1.2.3) второго регистра памяти (1.2), A-разрядный выход (1.2.4) второго регистра памяти (1.2), первый (1.2.1) и второй (1.2.2) входы второго регистра памяти (1.2) образуют F-разрядную шину начальной установки блока управления и синхронизации.

3. Устройство по п. 1, отличающееся тем, что блок вычислителей (2) состоит из четырех (2.1-2.4) блоков вычисления формальных показателей (БВФП), делителя (2.5) и счетчика адреса (2.6), С-разрядные, где С=3А, входы (2.1.1, 2.2.1, 2.3.1, 2.4.1) БВФП (2.1-2.4) являются соответственно С-разрядными первым (2.1), вторым (2.2), третьим (2.3) и четвертым (2.4) входами блока вычислителей (2), десятиразрядные третьи входы (2.1.3) первого (2.1), (2.2.3) второго (2.2), (2.3.3) третьего (2.3) и (2.4.3) четвертого (2.4) БВФП объединены и образуют десятиразрядный шестой (2.6) вход блока вычислителей (2), B-разрядные седьмые входы (2.1.7) первого (2.1), (2.2.7) второго (2.2), (2.3.7) третьего (2.3) и (2.4.7) четвертого (2.4) БВФП объединены и подключены к B-разрядному третьему (2.6.3) выходу счетчика адреса (2.6), A-разрядные пятые выходы (2.1.5) первого (2.1), (2.2.5) второго (2.2), (2.3.5) третьего (2.3), (2.4.5) четвертого (2.4) БВФП объединены и подключены к A-разрядному четвертому (2.5.4) входу делителя (2.5), С-разрядные шестые выходы (2.1.6) первого (2.1), (2.2.6) второго (2.2), (2.3.6) третьего (2.3) и (2.4.6) четвертого (2.4) БВФП образуют D-разрядный, где D=3C, пятнадцатый (2.2) выход блока вычислителей (2), вторые входы (2.1.2) первого (2.1), (2.2.2) второго (2.2), (2.3.2) третьего (2.3), (2.4.2) четвертого (2.4) БВФП и первый вход (2.6.1) счетчика адреса 2.6 объединены и являются пятым (2.5) входом блока вычислителей (2), четвертые входы (2.1.4) первого (2.1), (2.2.4) второго (2.2), (2.3.4) третьего (2.3) и (2.4.4) четвертого (2.4) БВФП являются соответственно десятым (2.10), девятым (2.9), восьмым (2.8) и седьмым (2.7) входами блока вычислителей (2), A-разрядные первые вход (2.5.1) и третий выход (2.5.3) делителя (2.5) являются соответственно одиннадцатым входом (2.11) и четырнадцатым (2.14) выходом блока вычислителей (2), вторые входы (2.5.2) и (2.6.2) делителя (2.5) и счетчика адреса (2.6) являются соответственно двенадцатым (2.12) и тринадцатым (2.13) входами блока вычислителей (2).

4. Устройство по п. 1, отличающееся тем, что блок вычисления формальных показателей (БВФП) (2.1) состоит из трех (2.1.1-2.1.3) блоков вычисления частных показателей (БВЧП), накапливающего сумматора (2.1.4) и регистра памяти (2.1.5), первый A-разрядный вход (2.1.5.1) которого подключен к четвертому A-разрядному выходу (2.1.4.4) накапливающего сумматора (2.1.4), пятый A-разрядный выход (2.1.5.5) и четвертый (2.1.5.4) вход регистра памяти (2.1.5) являются соответственно A-разрядным пятым (2.1.1) выходом и четвертым (2.1.4) входом БВФП (2.1), объединенные A-разрядные десятые выходы (2.1.1.10) первого (2.1.1), (2.1.2.10) второго (2.1.2) и (2.1.3.10) третьего (2.1.3) БВЧП подключены к A-разрядному первому (2.1.4.1) входу накапливающего сумматора (2.1.4), B-разрядные девятые входы (2.1.1.9) первого (2.1.1), (2.1.2.9) второго (2.1.2) и (2.1.3.9) третьего (2.1.3) БВЧП объединены и являются B-разрядным седьмым (2.1.7) входом БВФП (2.1), A-разрядные первые входы (2.1.1.1) первого (2.1.1), (2.1.2.1) второго (2.1.2), (2.1.3.1) третьего (2.1.3) БВЧП образуют С-разрядный первый (2.1.1) вход БВФП (2.1), вторые входы (2.1.1.2) первого (2.1.1), (2.1.2.2) второго (2.1.2) и (2.1.3.2) третьего (2.1.3) БВЧП, (2.1.4.2) накапливающего сумматора (2.1.4), (2.1.5.2) регистра памяти (2.1.5) объединены и являются вторым (2.1.2) входом БВФП (2.1), соответственно объединенные с третьего по седьмой (2.1.1.3-2.1.1.7) входы первого (2.1.1), с третьего по седьмой (2.1.2.3-2.1.2.7) входы второго (2.1.2), с третьего по седьмой (2.1.3.3-2.1.3.7) входы третьего (2.1.3) БВЧП, а также восьмые входы (2.1.1.8) первого (2.1.1), (2.1.2.8) второго (2.1.2) и (2.1.3.8) третьего (2.1.3) БВЧП, третьи входы (2.1.4.3) накапливающего сумматора (2.1.4) и (2.1.5.3) регистра памяти (2.1.5) образуют десятиразрядный вход (2.1.3) БВФП (2.1), A-разрядные десятые выходы (2.1.1.10) первого (2.1.1), (2.1.2.10) второго (2.1.2), (2.1.3.10) третьего (2.1.3) БВЧП образуют С-разрядный шестой (2.1.6) выход БВФП (2.1).

5. Устройство по п. 1, отличающееся тем, что блок вычисления частных показателей (БВЧП) (2.1.1) состоит из первого (2.1.1.1), второго (2.1.1.3), третьего (2.1.1.5), четвертого (2.1.1.7) регистров памяти, компаратора (2.1.1.2), делителя (2.1.1.4) и умножителя (2.1.1.6), А-разрядные первый (2.1.1.6.1) вход и четвертый (2.1.1.6.4) выход которого подключены соответственно к A-разрядным пятому выходу (2.1.1.5.5) третьего регистра памяти (2.1.1.5) и первому (2.1.1.7.1) входу четвертого регистра памяти (2.1.1.7), A-разрядный пятый (2.1.1.7.5) выход четвертого регистра памяти (2.1.1.7) является десятым (2.1.1.10) выходом БВЧП (2.1.1), A-разрядный пятый (2.1.1.4.5) выход делителя (2.1.1.4) подключен к A-разрядному первому (2.1.1.5.1) входу третьего регистра памяти (2.1.1.5), A-разрядный выход (2.1.1.3.4) второго регистра памяти (2.1.1.3) подключен к A-разрядным первому (2.1.1.4.1) входу делителя (2.1.1.4) и третьему (2.1.1.2.3) входу компаратора (2.1.1.2), выход (2.1.1.2.4) компаратора подключен к второму (2.1.1.3.2) входу второго регистра памяти (2.1.1.3), А-разрядный пятый (2.1.1.1.5) выход первого регистра памяти (2.1.1.1) подключен к A-разрядным первому входу (2.1.1.2.1) компаратора (2.1.1.2), первому входу (2.1.1.3.1) второго регистра памяти (2.1.1.3) и четвертому входу (2.1.1.4.4) делителя (2.1.1.4), A-разрядный первый вход (2.1.1.1.1) первого регистра памяти (2.1.1.1) является первым (2.1.1.1) входом БВЧП (2.1.1), объединенные B-разрядные четвертые входы (2.1.1.1.4) и (2.1.1.5.4) соответственно первого (2.1.1.1) и третьего (2.1.1.5) регистров памяти являются B-разрядным девятым (2.1.1.9) входом БВЧП (2.1.1), объединенные третьи входы (2.1.1.1.3, 2.1.1.3.3, 2.1.1.4.3, 2.1.1.5.3, 2.1.1.6.3, 2.1.1.7.3) соответственно первого регистра памяти (2.1.1.1), второго регистра памяти (2.1.1.3), делителя (2.1.1.4), третьего регистра памяти (2.1.1.5), умножителя (2.1.1.6), четвертого регистра памяти (2.1.1.7) и второй (2.1.1.2.2) вход компаратора (2.1.1.2) объединены и являются вторым (2.1.1.2) входом БВЧП (2.1.1), вторые входы (2.1.1.1.2) первого регистра памяти (2.1.1.1), (2.1.1.4.2) делителя (2.1.1.4), (2.1.1.5.2) третьего регистра памяти (2.1.1.5), (2.1.1.6.2) умножителя (2.1.1.6), второй (2.1.1.7.2) и четвертый (2.1.1.7.4) входы четвертого регистра памяти (2.1.1.7) являются соответственно третьим (2.1.1.3), четвертым (2.1.1.4), пятым (2.1.1.5), шестым (2.1.1.6), седьмым (2.1.1.7) и восьмым (2.1.1.8) входами БВЧП (2.1.1).

6. Устройство по п. 1, отличающееся тем, что блок визуализации (5) состоит из регистра памяти (5.1), цифрового индикатора (5.2), компаратора (5.3), цветового индикатора (5.4) и сегментного индикатора (5.5), А-разрядные входы которого с первого (5.5.1) по двенадцатый (5.5.12) образуют D-разрядный второй вход (5.2) блока визуализации (5), А-разрядный четвертый выход (5.1.4) регистра памяти (5.1) подключен к объединенным А-разрядным первым входам (5.2.1) цифрового индикатора (5.2) и (5.3.1) компаратора (5.3), выход (5.3.3) которого подключен к входу (5.4.1) цветового индикатора (5.4), A-разрядный первый вход (5.1.1) регистра памяти (5.1) является A-разрядным первым (5.1) входом блока визуализации (5), второй (5.1.2) и третий (5.1.3) входы регистра памяти (5.1) являются соответственно третьим (5.3) и четвертым (5.4) входами блока визуализации (5), A-разрядный второй вход (5.3.2) компаратора (5.3) является пятым (5.5) входом блока визуализации (5).

| СПОСОБ КОМПЛЕКСНОГО МОНИТОРИНГА СОСТОЯНИЯ ДИНАМИЧЕСКИХ ОБЪЕКТОВ И СИСТЕМ | 2014 |

|

RU2574083C2 |

| СПОСОБ АВТОМАТИЗИРОВАННОЙ ОБРАБОТКИ И АНАЛИЗА ТЕЛЕМЕТРИЧЕСКОЙ ИНФОРМАЦИИ МНОГОПАРАМЕТРИЧЕСКОГО ОБЪЕКТА И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2557477C2 |

| СПОСОБ КОНТРОЛЯ СОСТОЯНИЯ МНОГОПАРАМЕТРИЧЕСКОГО ОБЪЕКТА | 2007 |

|

RU2364926C2 |

| СПОСОБ ОПЕРАТИВНОГО ДИНАМИЧЕСКОГО АНАЛИЗА СОСТОЯНИЙ МНОГОПАРАМЕТРИЧЕСКОГО ОБЪЕКТА | 1998 |

|

RU2134897C1 |

| US 2014306641 A1, 16.10.2014 | |||

| US 2010280801 A1, 04.11.2010 | |||

| US 2008005707 A1, 03.01.2008. | |||

Авторы

Даты

2018-07-19—Публикация

2017-09-11—Подача