инверторау выход которого через формирователь кода подключен к каналу свяэи выход элемента задержки соединен с информационными входами третьего и четвертого ключей, выход четвертого ключа через блок оперативной памяти соединен с вторым входом второго вычитателя, выход третьего ключа соединен с вторым входом первого вычитателя, на приемной стороне введены дешифратор, блок оперативной памяти, второй, тре-тий и четвертый

ключи и инвертор, информационный вход второго ключи и вход дешифратора подключены к каналу связи, выход второго ключа через блок оперативной памяти соединен с информационными входами третьего и четвертого ключей, выход инвертора соединен с входами управления второго и третьего ключей, выход дешифратора соединен с входом управления четвертого ключа и входом инвертора,выходы третьего и четвертого ключей соединены с входом декодера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ассоциативного сжатия информации | 1983 |

|

SU1120390A1 |

| Устройство для передачи и приема информации | 1987 |

|

SU1449989A1 |

| Устройство для передачи и приема информации | 1986 |

|

SU1399797A1 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1983 |

|

SU1152016A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1193713A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1218415A1 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1078455A1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

УСТРОЙСТВО ДЛЯ АССОЦИАТИВНОГО СЖАТИЯ ИНФОРМАЦИИ, содержащее на передающей стороне в каждом канале обработки последовательно соединенные nepBt умножитель и сумматор и второй умножитель, блок буферной памяти, выходы которого соединены с первыми входами первых и вторых умножителей соответствуннцих каналов обработки, выходы вторых умножителей каналов обработки соединены с соответствующими входами сумматора, выход которого соединен с первым входом вычитателя, второй вход которого соединен с вторьлуш входами первых умножителей каналов .обработки, выход которого соединен с входами нормализатора и квадратурного сумматора, . выход квадратурного сумматора соединен с входом порогового элемента, первый выход которого соединен с первым управлянщим входом блока ключей, второй выход соединен с управляющими входами первого и второго ключей и с вторым управляющим входом блока ключей, информационные входаг которого соединены с вторыми входами вторых соответствуюпщх- умножителей каналов обработки, выходы блока ключей и первого ключа соединены с соот% ветствующими входами кодера, вькод которого подключен к каналу связи, выход нормализатора соединен с информационными входами первого и второго ключей, выход второго ключа соединен с входом блока буферной памяти, а на приемной стороне содержащее последовательно соединенные формирователь импульсов, ключ и блок буферной памяти, выходы которого соединены через умножители с соответствующими первыми входами сумматора, выход которого является выходом устройства и соединен с первым входом формирователя импульсов, декодер, первый выход которого соединен с вторьми входами (Л Формирователя импульсов, ключа и сумматора, второй выход декодера соединен с входом регистра памяти, выходы . которого соединены с вторыми входами соответствующих умножителей, отличающееся тем, что, с целью повышения точности и информативности устройства, в него введены на передающей стороне блок оперативной памяти, второй вычитатель, второй квадратурньй сумматор, третий и четвертый ключи, второй npporoBbrii элемент, элемент задержки, инвертор, формирователь кода и в каждом канале обработки - пороговый .элемент - выход которого соединен с вторым входом второго умножителя, вход соединен с выходом сумматора, первый вход второго вычитателя и вход элемента задержки объединены и являются входом устройства, выход второго вычитателя через последовательно соединенные второй квадратурный сумматор и второй пороговый элемент соединен с входами управления третьего и четвертого ключей и входом.

Изобретение относится к телемеханике и системам передачи данных.

Цель изобретения - повышение точности и информативности устройства,

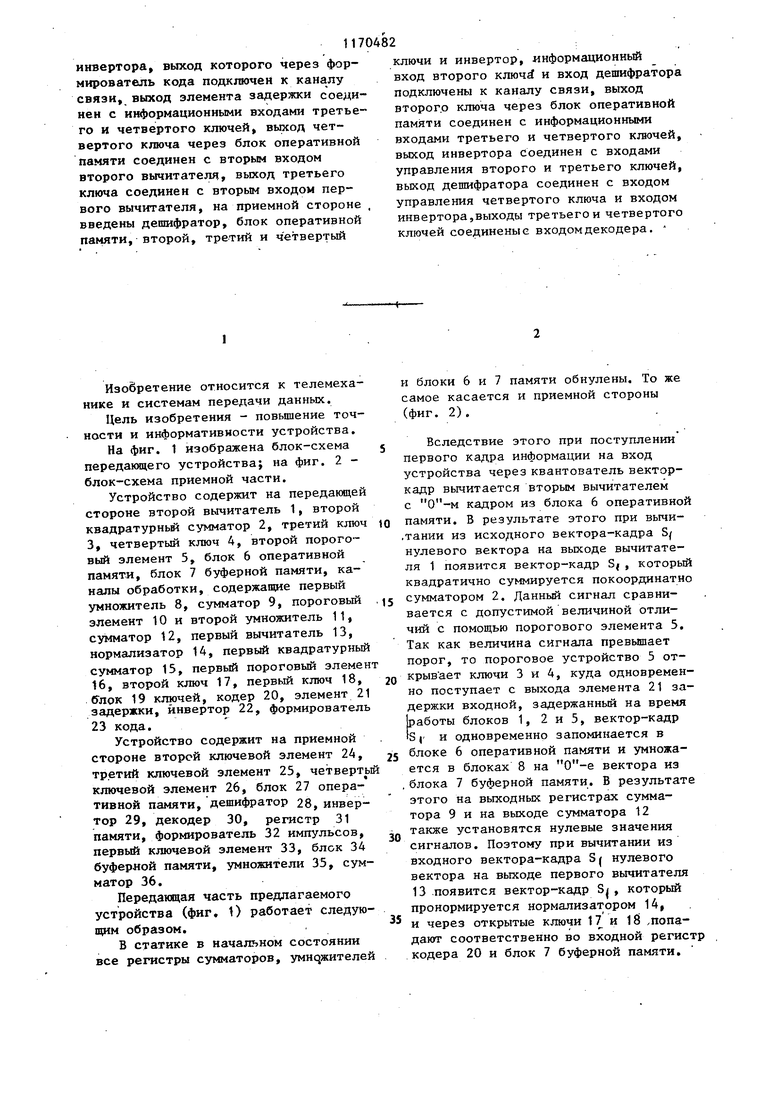

На фиг. 1 изображена блок-схема передающего устройства; на фиг. 2 блок-схема приемной части.

Устройство содержит на передающей стороне второй вычитатель 1, второй квадратурньй сумматор 2, третий ключ 3, четвертый ключ 4, второй пороговый элемент 5, блок 6 оперативной памяти, блок 7 буферной памяти, каналы обработки, содержащие первый умножитель 8, сумматор 9, пороговый элемент 10 и второй умножитель 11, сумматор 12, первый вычитатель 13, нормализатор 14, первый квадратурный сумматор 15, первый пороговый элемен 16, второй ключ 17, первьй ключ 18, блок 19 ключей, кодер 20, элемент 21 задержки, инвертор 22, формирователь 23 кода.

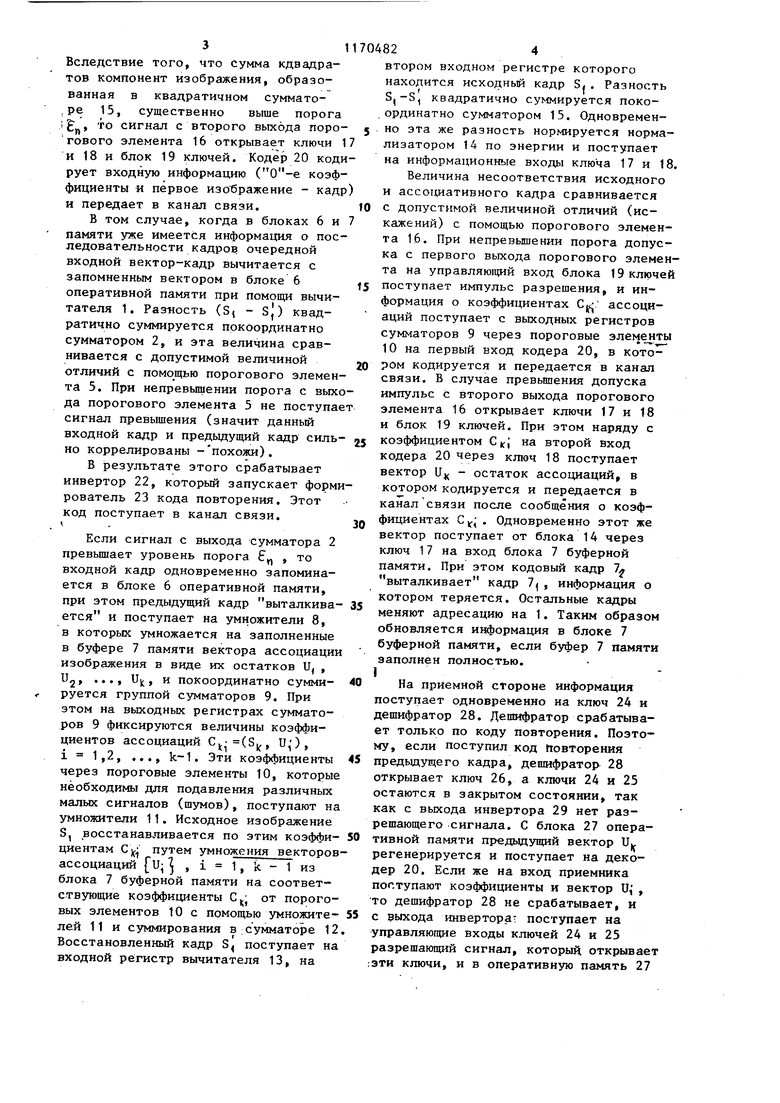

Устройство содержит на приемной стороне второй ключевой элемент 24, третий ключевой элемент 25, четвертьй ключевой элемент 26, блок 27 оперативной памяти,дешифратор 28, инвертор 29, декодер 30, регистр 31 памяти, формирователь 32 импульсов, первый ключевой элемент 33, блок 34 буферной памяти, умножители 35, сумматор 36.

Передакяцая часть предлагаемого устройства (фиг, О работает следующим образом.

В статике в начальном состоянии все регистры сумматоров, yмнqжитeлeй

и блоки 6 и 7 памяти обнулены. То же самое касается и приемной стороны (фиг. 2).

Вследствие этого при поступлении первого кадра информации на вход устройства через квантователь векторкадр вычитается вторым вычитателем с кадром из блока 6 оперативной памяти. В результате этого при вычи.тании из исходного вектора-кадра S нулевого вектора на выходе вычитателя 1 появится вектор-кадр S(, который квадратично суммируется покоординатно сумматором 2. Данный сигнал сравнивается с допустимой величиной отличий с помощью порогового элемента 5. Так как величина сигнала превышает порог, то пороговое устройство 5 открывает ключи 3 и 4, куда одновременно поступает с выхода элемента 21 задержки входной, задержанный на время 1работы блоков 1, 2 и 5, вектор-кадр s J и одновременно запоминается в блоке 6 оперативной памяти и умножается в блоках 8 на вектора из .блока 7 буферной памяти. В результате этого на выходных регистрах сумматора 9 и на выходе сумматора 12 также установятся нулевые значения сигналов. Поэтому при вычитании из входного вектора-кадра Sj нулевого вектора на выходе первого вычитателя 13 .появится вектор-кадр 8, который пронормируется нормализатором 14, и через открытые ключи 17 и 18 .попадают соответственно во входной регист кодера 20 и блок 7 буферной памяти.

Вследствие того, что сумма кдвадратов компонент изображения, образованная в квадратичном суммато.ре 15, существенно выше порога i g , то сигнал с второго выхода порогового элемента 16 открывает ключи 1 и 18 и блок 19 ключей. Кодер 20 кодирует входную информацию ( коэффициенты и первое изображение - кадр и передает в канал связи.

В том случае, когда в блоках 6 и памяти уже имеется информация о последовательности кадров очередной входной вектор-кадр вычитается с запомненным вектором в блоке 6 оперативной памяти при помощи вычитателя 1. Разность (S S,) квадратично суммируется покоординатно сумматором 2, и эта величина сравнивается с допустимой величиной отличий с порогового элемента 5. При непревьщгении порога с выхода порогового элемента 5 не поступае сигнал превышения (значит данный входной кадр и предыдущий кадр сильно коррелированы -похожи).

В результате этого срабатывает инвертор 22, который запускает формирователь 23 кода повторения. Этот

код поступает в канал связи.

I .

Если сигнал с выхода сумматора 2 превьпиает уровень порога Е , то входной кадр одновременно запоминается в блоке 6 оперативной памяти, при этом предыдущий кадр выталкивается и поступает на умножители 8, в которых умножается на заполненные в буфере 7 памяти вектора ассоциации изображения в виде их остатков U , Uj, «.., U|, и покоординатно суммируется группой сумматоров 9. При этом на выходных регистрах сумматоров 9 фиксируются величины коэффициентов ассоциаций (8|, U,), i 1,2, ... k-1. Эти коэффициенты через пороговые элементы 10, которые необходимы для подавления различных малых сигналов (шумов), поступают на умножители 11. Исходное изображение S, восстанавливается по этим коэффициентам C)f| путем умножения векторовассоциаций , i 1 , k - 1 из блока 7 буферной памяти на соответствующие коэффициенты от пороговых элементов 10 с помощью умножителей 11 и суммирования в:сумматоре 12 Восстановленный кадр S поступает на входной регистр вычитателя 13, на

втором входном регистре которого находится исходньй кадр S/. Разность S|-S, квадратично суммируется покоординатно сумматором 15. Одновременно эта же разность нормируется нормализатором 14 по энергии и поступает на информационные входы ключа 17 и 1

Величина несоответствия исходного и ассоциативного кадра сравнивается с допустимой величиной отличий (искажений) с помощью порогового элемента 16. При непревьшении порога допуска с первого выхода порогового элемета на управляю1ций вход блока 19 ключе поступает импульс разрешения, и информация о коэффициентах С|, ассоциаций поступает с выходных регистров сумматоров 9 через пороговые элемент 10 на первый вход кодера 20, в котором кодируется и передается в канал связи. В случае превьшения допуска импульс с второго выхода порогового элемента 16 открывает ключи 17 и 18 и блок 19 ключей. При этом наряду с коэффициентом на второй вход кодера 20 через ключ 18 поступает вектор и - остаток ассоциаций, в котором кодируется и передается в канал связи после сообщения о коэффициентах С , . Одновременно этот же вектор поступает от блока 14 через ключ 17 на вход блока 7 буферной памяти. При этом кодовый кадр 7 выталкивает кадр 7, информация о котором теряется. Остальные кадры меняют адресацию на 1. Таким образом обновляется информация в блоке 7 буферной памяти, если буфер 7 памяти заполнен полностью.

I

На приемной стороне информация

поступает одновременно на ключ 24 и дешифратор 28. Дешифратор срабатывает только по коду повторения. Поэтому, если поступил код Повторения предыдущего кадра, дешифратор 28 открывает ключ 26, а ключи 24 и 25 остаются в закрытом состоянии так как с выхода инвертора 29 нет разрешающего сигнала. С блока 27 оперативной памяти П1 едьщущий вектор V регенерируется и поступает на декодер 20. Если же на вход приемника поступают коэффициенты и вектор U, , то дешифратор 28 не срабатывает, и с выхода инвертора: поступает на управляющие входы ключей 24 и 25 разрешающий сигнал, который открывает :эти ключи, и В оперативную память 27

записывается входная информация и затем через открытый, ключ 25 поступает на декодер. С помощью декодера 30 информация декодируется и разделяется на вектор отсчетов козффициентов Скь , отсчеты которого запоминаются на регистре 31 памяти коэффициентов , и на векторкадр УХв случае отсутствия вектора U первого выхода декодера снимаются отсчеты, по которым формирователь 32 блокируется до тех пор, пока не появятся не отсчеты на вьгходе декодера 30. При этом ключ 33 находится в закрытом состоянии. Векторы и;, i 1, k -1, запомненные ранее в блоке 4 буферной памяти, умножаются группой умножителей 35 на коэффициенты из регистра 31 памяти, после чего результаты суммируются сумматором 36, на выходе которого образуется передаваемый кадр изображения

и,к

при

KI

IC-1

и.

Z

UK 0. S - ., -

.1 После появления информации на выходе сумматора 36 формирователь 32 в том случае если он не блокирован, формирует импульс записи. При наличии вектора U, О он складывается на сумматоре 36 вместе с линейной комбиКМ

.2:

Cj,. и- . Так как

в этом

нацией

tc

случае формирователь 32 не блокирован, то по наличию информации на выходе сумматора 36 импульс разрешения с выхода формирователя 32 открывает ключ 33, и вектор U с выходного регистра декодера записьюается в блок 34 буферной памяти. Хранение информации в буферной памяти 34 организуется аналогично как и на передающей стороне в блоке 7 буферной памяти.

| УСТРОЙСТВО для СЖАТИЯ ВХОДНОЙ ИНФОРМАЦИИ | 0 |

|

SU324638A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для ассоциативного сжатия информации | 1983 |

|

SU1120390A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1985-07-30—Публикация

1984-02-14—Подача