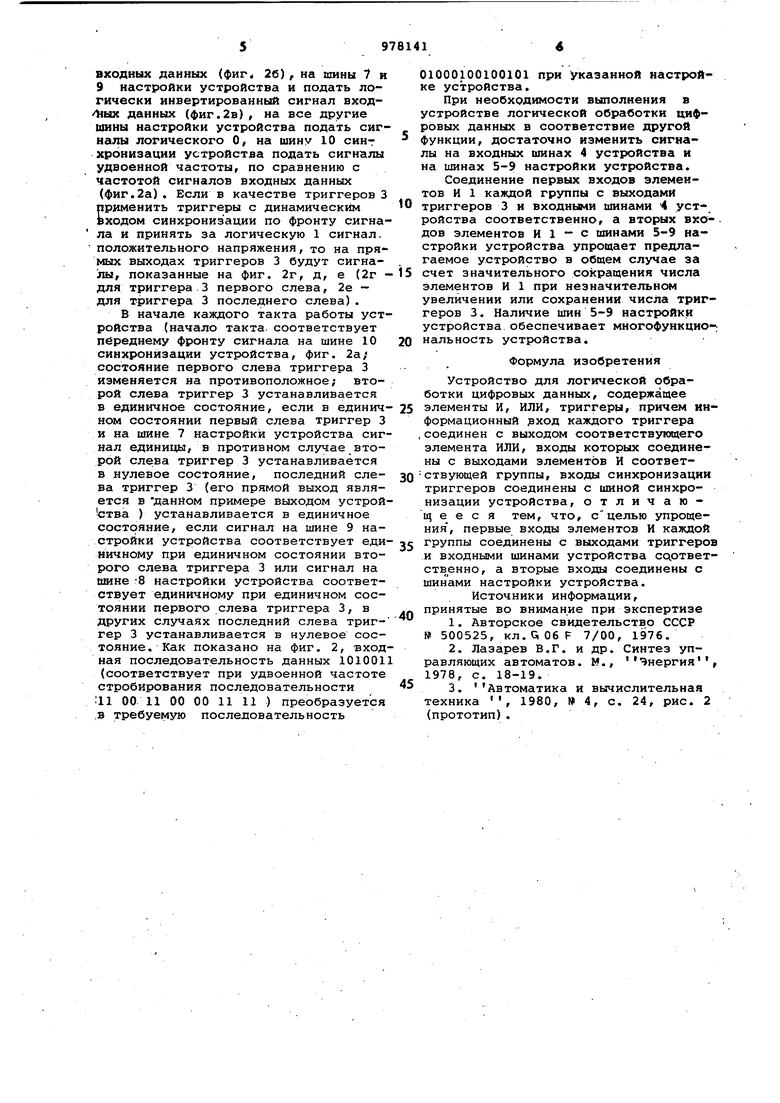

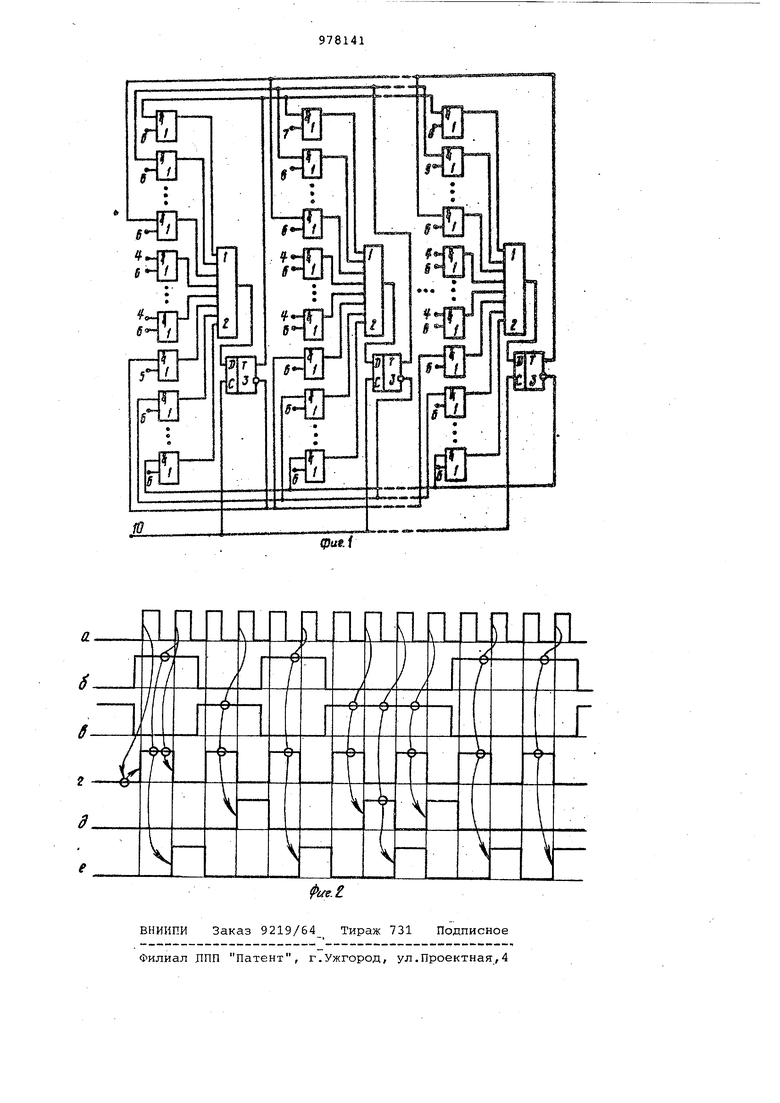

Изобретение относится к вычислительной технике и предназначено для обработки цифровых данных. Известно устройство для логическо обработки цифровых данных, выполненное в виде многофункционального логи ческого модуля, содержащего элементы И, выходы которых соединены с входам элемента ИЛИ, а входы соединены с входными шинами непосредственно и че рез инверторы 1. При построении устройства с внутренней памятью для логической обработки цифровых данных (автоматов) при применении такого многофункционального логического модуля необходимо в устройство вводить элементы памяти, из-за большой избыточности реализующего оборудования устройство получается сложным. Известны дискретные устройства автоматы с так называемой стандартной структурой. Они состоят из части устройства с элементами памяти и ком бинационной части, в которой сосредоточены логические элементы логичес кого преобразователя. В каждом такте работы дискретного устройства на выводах логического преобразователя в 9ависимости от входных сигналов и сигналов на выходах элементов памяти вырабатываются сигналы, часть из которых является выходными сигналами дискретного устройства в данном такте работы, другая часть сигналов передается на входы элементов памяти и будет использована в следующем такте работы дискретного устройства 2. При двоичном кодировании внутренних состояний .автомата в общем случае значительно усложняется логический преобразователь, а при единичном или противогоночном кодировании внутренних состояний усложняется логический преобразователь и увеличивается количество элементов памяти. Устройство в целом отличается сложностью из-за большого количества элементов реализующего оборудования и связей между элементами. Наиболее близким по технической сущности к предлагаемому является устройство для логической обработки цифровых данных на программируемых логических матрицах (ПЛМ) с логической структурой И-ИЛИ. Оно содержит триггеры, элементы И (матрицу И), элементы ИЛИ (матрицу ИЛИ), информационный вход каждого триггера соединен с выходом соответствующего элемента ИЛИ, входы которых соединены с выходами элементов И, входы синхронизаци триггеров соединены с шиной временно го сигнала, которая является шийой синхронизации устройства 3. Недостаток такого устройства закл чается в большой избыточности элемен тов И в ПЛМ, которые не используются при реализации в конкретном устройстве, что усложняет устройство в целом Объясняется это тем, что изготовленная ПЛМ до ее программирования-представляет достаточно универсальную структуру, ориентированную на одновременную , реализацию возможно большего числа нулевых Функций, представленных в дизьюнктивной нормальной форме. После программирования ПЛМ для конкретного применения, ее перенастройка и перенастройка всего устройства На выполнение других фyнkций затруднительны или невозможны. Цель изобретения - упрощение и обеспечение многофункциональности устройства. Поставленная цель достигается тем что в устройстве для логической обработки цифровых данных, содержащем элементы И, ИЛИ, триггеры, причем информационный вход каадого. триггера соединен с выводом соответствующего элемента ИЛИ, входы которых соедине ны с выходами элементов И соответствующей группы, в.хоДы синхронизации триггеров соединены с шиной синхронизации устройства, первые .входы элемен тов И каждой группы соединены с выходами триггеров и входными шинами устройства соответственно, а вторые входы соединены с шинами настройки устройства. о На фиг. 1 представлена схема предлатаемого устройства для логической обработки цифровых данных, на фиг.2 - временная диаграмма работы у.стройс;тва в примере настройкц, на выполне1 ие функции кодопреобразования. Устройство (фиг. 1) состоит из элементов И 1, элементов ИЛИ 2, триггеров 3, входных шин 4 устройства, шин 5-9 настройки устройства и шины 10 синхронизации устройства. Информационйый вход каждого триггера 3 соединен с выходом соответствующего эле мента ИЛИ 2, входы которого соединены с выходами элементов И 1 соответ|ствующей группы. Вход синхронизации каждого из триггеров 3 соединен с шиной 10 синхронизации устройства. Первые входы элементов И 1 каждой группы соединены соответственно с выходами триггеров 3 и входными шинами 4 устройства. Второй вход каждого элемента И 1 соединен с соответствующей ему одной отдельной-шиной :5,6,7,8 или 9 настройки устройства. Шина 10 синхронизации устройства предназначена для обеспечения одновременной передачи сигналов на триггеры 3 через элементы И 1, ИЛИ 2 от прямых, инверсных выходов триггеров 3 и входных шин 4 устройства в зависимости от сигналов на шинах 5-9 настройки устройства. В качестве сигналов на шинах 5-9 настройки устройства могут быть как Сигналы постоянного значения (разрешающие - единицы, запрещающие - нули), так и сигналы переменного значения (двоичные последовательности). Сигналами на входных шинйх 4 устройства могут быть сигналш постоянного или переменного значения как независимые (внешние но отношению к данному устройству) , так и зависимые (с выходов триггеров 3) . Каждый следуниций сигнал на шине 10 синхронизации устройства может быть подан после завершения переходного процесса в устройстве от предыдущего сигнала на этой шине, -т.е. минимальный такт должен быть больше времени срабатывания и установления сигнала в последовательной цепи из элементов И 1, ИЛИ 2, триггера 3. Изменение сигналов, на шинах 5-9 насЛгройки устройства и изменение независимых сигналов на входных шинах 4 устройства, приводящие к изменению сигнала на информационных входах триггеров 3, должны осуществляться вне интервала времени активного действия сигнала на шине 10 синхронизации устройства , т.е. вне действующего фронта импульса сигнала на шине 10 син1 ронизации устройства для триггеров 3 с динамическими входами синхронизации и вне разрешаюцего уровня сигнала на шине 10 синхронизацией устройства для триггеров 3 с потенциальными входами синхронизации. Выполнение этих условий необходимо для обеспечения однозначности в работе устройства. Совокупность состояний триггеров 3 образует внутреннее состояние устройства . Под действием очередного сигнала на шине 10 синхронизации устройства устройство переходит в очередное внутреннее состояние, при этом выходными сигналами устройства являются сигналы на одном или нескольких выходах триггеров 3. Сигналами на входных шинах -4 устройства и на шинах 5-9 настройки устройства настраивают устройство на выполнение конкретных функций логической обработки цифровых данных. Более подробно рассмотрим работу устройства на примере его настройки на выполнение функции синхронного кодопреобразования входных двоичных Данных в известный код модифицированной фазовой модуляции. Для этого нужно на шину 5 настройки устройства, подать сигнал логической 1, на шину 8 настройки устройства подать сигнал входных данных фиг 26) , на шины 7 и 9 настройки устройства и подать логически инвертированный сигнал входных данных (фиг.2в), на все другие шины настройки устройства подать сигналы логического О, на шину 10 синг хронизации устройства подать сигналы удвоенной частоты, по сравнению с частотой сигналов входных данных (фиг.2а). Бели в качестве триггеров 3 применить триггеры с динамическим входом синхронизации по фронту сигна ла и принять за логическую 1 сигнал. положительного Напряжения, то на прямых выходах триггеров 3 будут сигналы, показанные на фиг. 2г, д, е (2г для триггера 3 первого слева, 2е - для триггера 3 последнего слева). В начале каждого такта работы уст ройства (начало такта соответствует переднему фронту сигнала на шине 10 синхронизации устройства, фиг. 2а/ состояние первого слева триггера 3 изменяется на противоположное; второй слева триггер 3 устанавливается в единичное состояние, если в единич ном состоянии первый слева триггер 3 и на шине 7 настройки устройства сиг нал единицы, в противном случае второй слева триггер 3 устанавливается в нулевое состояние, последний елева триггер 3 (его прямой выход является в данйом примере выходом устрой ства ) устанавливается в единичное состояние, если сигнал на шине 9 настройки устройства соответствует еди ничному при единичном состоянии второго слева триггера 3 или сигнал на шине -8 настройки устройства соответствует единичному при единичном состоянии первого слева триггера 3, в других случаях последний слева триггер 3 устанавливается в нулевое состояние. Как показано на фиг. 2, вход ная последовательность данных 101001 (соответствует при удвоенной частоте стробирования последовательности ;il 00 11 00 00 11 11 ) преобразуется ,ъ требуемую последовательность 1000100100101 при указанной настройке устройства. При необходимости выполнения в устройстве логической обработки цифровых данных в соответствие другой функции, достаточно изменить сигналы на входных шинах 4 устройства и на шинах 5-9 настройки устройства. Соединение первых входов элементов И 1 каждой группы с выходами триггеров 3 и входными шинами 4 устройства соответственно, а вторых вхо-. дов элементов И 1 - с шинами 5-9 настройки устройства упрощает предлагаемое устройство в общем случае за счет значительного сокращения числа элементов И 1 при незначительном увеличении или сохранении числа триггеров 3. Наличие шин 5-9 настройки устройства обеспечивает многофункцио-; нальность устройства. Формула изобретения Устройство для логической обработки цифровых данных, содержащее элементы И, ИЛИ, триггеры, причем информационный рход каждого триггера соединен с выходом соответствующего элемента ИЛИ, входы которых соединены с выходами элементов И соответствующей группы, входы синхронизации триггеров соединены с шиной синхронизации устройства, отличающееся тем, что, сцелью упрощения, первые входы элементов И каждой группы соединены с выходами триггеров и входными шинами устройства соответственно, а вторые входы соединены с шинами настройки устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 500525, кл. Gi 06 F 7/00, 1976. 2.Лазарев В.Г. и др. Синтез управляющих автоматов. М., Энергия, 1978, с. 18-19. 3.Автоматика и вычислительная техника , 1980, 4, с. 24, рис. 2 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемая логическая матрица | 1986 |

|

SU1381481A1 |

| Программируемая логическая матрица | 1983 |

|

SU1159066A1 |

| Устройство для записи сигналов цифровой информации | 1982 |

|

SU1046765A1 |

| Программируемое логическое устройство | 1984 |

|

SU1257702A1 |

| МОДУЛЬ ВВОДА-ВЫВОДА СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1991 |

|

RU2032201C1 |

| Устройство для отладки многомодульной ЦВМ | 1987 |

|

SU1564630A1 |

| Устройство воспроизведения информации с оптического носителя | 1986 |

|

SU1345248A1 |

| Устройство для контроля параметров | 1985 |

|

SU1295420A1 |

| Устройство восстановления синхронизации сигналов воспроизведения,записанных способом модифицирования фазовой модуляции | 1984 |

|

SU1205190A1 |

| Устройство фазовой синхронизации для дискового накопителя цифровых данных | 1988 |

|

SU1615799A1 |

Авторы

Даты

1982-11-30—Публикация

1981-02-03—Подача