J7

сл

с

00 4;:

оо

Изобретение относится к вьмисли- тельной технике и может быть использовано, например, в устройствах управления .

Цель изобретения - уменьшение времени диагностирования программируемой логической матрицы (ПЛМ) за счет совмещения во времени процесса проверки составляющих ПЛМ элементов И и элементов ИЛИ.

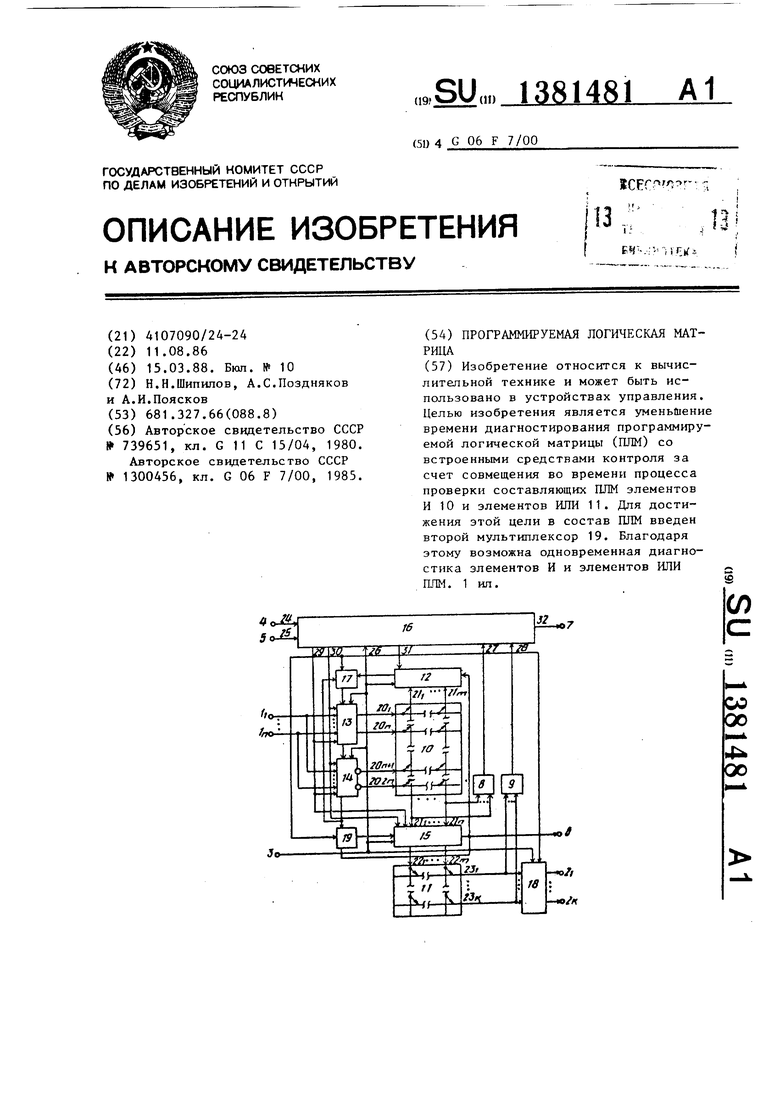

На чертеже изображена схема программируемой логической матрицы.

Программируемая логическая матрица (ПЛМ) содержит информационные входы I, информационные выходы 2, вход 3 синхронизации, первый 4 и второй 5 входы задания режима работы, выход 6 диагностической информации, контрольный выход 7, первьш 8 и второй 9 блоки контроля, элементы И 10 и элементы 1ШИ 11, которые выполнены в виде матриц элементов связи, первый буферный регистр 12 сдвига, первый 13 и второй 14 входные регистры сдвига, второй буферный регистр 15 сдвига, блок 16 управления, первьм мультиплексор 17, выходной регистр 18, второй мульт1тлексор 19, входы 20 и выходы 21 матрицы 10 (элементов И 10), входы 22 и выходы 23 матрицы 11 (эле- ментов 1-ШИ 11), первьм 24, второй 25 и третш 26 входы блока 16 управления, которые являются входами 4 и 5 задания режима работы и входом 3 синхронизации ПЛМ соответственно, четвертый 27 и пятьм 28 входы блока 16 управления, первый 29, второй 30 и третий 31 выходы блока 16 управления и четвертый выход 32 блока 16 управления, который является контрольным выходом 7. ШТМ.

С целью предотвращения гонок регистры 12-15 и 18 выполняются по двухступенчатой схеме или на D-триг герах типа защелка, имеющих асинхронные установочные входы.

Режим работы ПЛМ определяется соответствующим набором сигналов на ее входах 4 и 5. ПЛМ может функционировать в режиме преобразования входной информации, в режиме ускоренной самопроверки, в режиме уточненной самопроверки и в режиме полно проверки. При этом последние три режима являются режимами диагностирования ПЛМ.

Для реализации необходимьгх функций по преобразованию входной инфор

0

5

0

5

0

5

0

5

мации ШМ подвергается предварительной настройке путем селективногЬ отключения или подключения элементов связи в матрицах 10 и 11 любым известным способом (например, разрезанием или выплавлением перемычек, разрушении переходов, засылкой настроечной информации в элементы связи, обладающие памятью и т.п.). Средства настройки ПЛМ на чертеже не показаны.

Программируемая логическая матрица работает следующим образом.

В режиме преобразования входной информации на выходе 29 блока 16 Управления формируется сигнал, запрещающий сдвиги и разрешающий парал- лельньш прием информации в регистры 13-15, в результате чего на выходе 31 устанавливается сигнал, запрещающий сдвиги в регистре 12 и разрешающий прием информации в регистр 18. Исходное состояние регистров 12-14 и 18 может быть произвольным. На входы 1 ПЛМ подается п-разрядное входное слово, подлежащее преобразованию в k-разрядное выходное слово. По первому синхроимпульсу, поступающему на вход 3 ПЛМ, входное слово принимается в регистры 13 и 14. При этом в регистр 13 заносятся прямые, а в регистр 14 инверсные значения всех разрядов этого слова. С инверсных выходов регистра 13 на входы 20,-20 матрицы 10 подаются инверсные значения разрядов принятого слова, а с инверсных выходов 20( -20, регистра 14 - прямые значения разрядов того же слова. В соответствии с настройкой матрицы 10 на ее выходах 21 фор- Нируется т-разрядное промежуточное слово. По второму синхроимпульсу это слово принимается в регистр 12 и в регистр 15. С выходов регистра 15 промежуточное слово поступает на входы 22 матрицы 11. В соответствии с настройкой матрицы 11 т-разрядное промежуточное слово преобразуется в k-разрядное выходное слово, которое передается с выходов 23 матрицы 11 на входы регистра 18. По третьему синхроимпульсу выходное k-разрядное слово принимается в регистр 18 и выдается на информационные выходы 2 ПЛМ. Каждое выходное слово, соответствующее входному слову, поступившему на входы 1 ПЛМ в р-ом такте, появляется на выходах 2 ПЛМ в (р+2)- ом такте. При этом в любом р-ом так-

те матрицей 10 осуществляется преобразование р-го входного слова в р-е промежуточное слово, матрицей 1 1 преобразование (р-1)-го промежуточного слова в (р-1)-е выходное слово, а регистр 18 хранит (р-2)-е выходное слово. Таким образом, преобразование входной информации в ПЛМ выполняется по принципу конвейерной обработки слов.

Режим ускоренной самопроверки может быть использован для определения технического состояния ПЛМ непосредственно на месте ее применения. Переход в режим ускоренной самопроверки из режима преобразования входной информации вьтолняется соответствующей сменой сигналов на входах А и 5 ПЛМ. В результате такой смены сигналов на выходе 30 блока 16 управления появляется одиночный импульс, устанавливающий один из разрядов регистров 13- 14 и один из разрядов регистра 15 в единичное состояние, а остальные разяды данньк регистров - в нулевое состояние. На выходе 29 блока 16 управления на все время ускоренной саопроверки устанавливается сигнал, разрешающий сдвиги и запрещающий параллельный прием информации в регистры 13-15. На выходе 31 блока 16 управления формируется сигнал, запрещающий сдвиги в регистре 12 и разрешающий параллельный прием информации в регистр 18, последовательную переачу информации из регистра 14 через мультиплексор 17 в регистр 13, а таке последовательную передачу информации из младшего разряда регистра 15 через мультиплексор 19 в старший разряд регистра 15. В результате образуются два кольцевых регистра сдвига, один из которых состоит из регистров 13-14, а другой - из регистра 15.

По каждому синхроимпульсу со вхоа 3 ПЛМ в образованных кольцевых регистрах происходит циклический сдвиг единицы на один разряд.

При продвижении единицы через регистры 13-14 производится последовательный опрос входов, т.е. горизонтальных шин, матри1у 1 Ю. С инверсных выходов регистров 13-14 на i-ю опра- шиваемую шину матрицы 10 поступает нулевой сигнал, а на остальные шины - единичные сигналы. В результате опроса i-ro входа матрицы 10 на ее выходах 21 появляется i-e промежуточ10

5

0

5

0

5

0

5

0

5

ное слово, состоящее из основных и контрольных разрядов. Для формирования контрольных разрядов используется часть столбцов матрицы 10 (например, один ш-й столбец). Содержимое контрольных разрядов в каждом промежуточном слове определяется содержимым основных разрядов этого слова и применяемым видом контроля. Так, например, при использовании контроля по четности количество подключенных в ходе настройки элементов связи в каждой строке матрицы 10 может быть дополнено до четного. В этом случае каждое промежуточное слово, появляющееся при опросе на выходах 21 матрицы 10, должно содержать четное количество нулей.

Сформированное промежуточное слово поступает с выходов матрицы 10 в блок 8 контроля. Если ошибок нет, то на выходе блока 8 контроля и на выходе 32 блока 16 управления устанавливаются сигналы отсутствия ошибки. При этом сигналы на выходах 29-31 блока 16 управления не меняются. По очередному синхроимпульсу i-e промежуточное слово принимается с выходов 21 матрицы 10 в регистр 12, а содержимое регистров 13-14 циклически сдвигается на один разряд. В следующем такте производится опрос (i+1)-ro входа матрицы 10 и т.д. Самопроверка матрицы 10 занимает 2п тактов. С началом (2п+1)-го такта происходит пересылка единицы из младшего разряда регистра 14 через мультиплексор 17 в старший разряд регистра 13 и цикл самопроверки матрицы 10 повторяется заново.

Одновременно с самопроверкой матрицы 10 выполняется самопроверка матрицы 11 по тому же принципу. При продвижении единицы по регистру 15 производится последовательный опрос входов, т.е. вертикальных шин, матри- цы I1. В каждом J-OM такте (j 1,m) с прямых выходов регистра 15 на j-й вход матрицы 11 поступает единичный сигнал, а на остальные входы - нулевые сигналы. В результате опроса j-ro входа матрицы 11 на ее выходах 23 появляется выходное слово, состоящее, как и промежуточные слова, из основных и контрольньлх разрядов. Это слово поступает в блок 9 контроля. Если нет ошибки, то на выходе блока 9 контроля и на выходе 32 блока 16 управления устанавливаются сигналы отсутствия ошибки. При этом сигналы на выходах 29-31 блока 16 управления не меняются. По очередному синхроимпульсу j-e выходное слово принимается с выходов 23 матрицы 11 в регистр 18, а содержимое регистра 15 циклически сдвигается на один разряд. В следующем такте производится опрос (j+1)-ro входа матрицы 11 и т.д. Самопроверка матрицы 11 занимает m тактов. С началом (т+1)-го такта происходит пересылка единицы из младшего разряда регистра 15 через мультиплексор 19 в старший разряд регистра 15 и цикл самопроверки матрицы 11 повторяется заново.

Если в текущем такте ускоренной самопроверки матриц 10 и 11 любым из блоков 8 или 9 контроля обнаруживается ошибка, то на контрольном выходе 7 ПЛМ формируется сигнал неисправности, свидетельствующий об обнаружении дефектов в ПЛМ.

Ускоренная самопроверка ПЛМ продолжается до тех пор, пока не будет изменен набор сигналов на входах 4 и 5 ПЛМ. О работоспособном состоянии ПЛМ свидетельствует при этом отсутствие сигналов неисправности на контрольном выходе 7.

Режим уточненной самопроверки может быть использован для поиска дефектов с целью их последующего устранения или обхода путем перенастройки ПЛМ. Отличие работы ПЛМ в режиме уточненной самопроверки от работы в режиме ускоренной самопроверки состоит, в следующем.

Если в текущем такте опроса матриц 10 и ,1 1 любым из блоков 8 или 9 контроля обнаруживается некорректность поступающего на его входы слова, то на выходе этого блока появляется сигнал ошибки, а на контрольном выходе 7 ПЛМ - сигнал неисправности. По очередному синхроимпульсу содержимое регистров 13-14 и 15 циклически сдвигается на один разряд. Тем самым подготавливается к опросу очередной вход матрицы 10 и очередной вход матрицы 11. Одновременно производится прием промежуточного слова с выходов 21 матрицы 10 в регистр 12 и выходного слова с выходов матрицы 11 в регистр 18.. На выходе 31 блока 16 управления появляется сиг нал прерывания. Этим сигналом запрещается

параллельный прием информации в регистр 12, Разрешаются сдвиги в регистре 12, а также передача информации последовательным кодом из регистра 12 через мультиплексор 17 в регистр 13 и из регистра 14 через мультиплексор 19 в регистр 15. Тем же сигналом запрещается прием информации

в регистр 18. В результате образуется один кольцевой регистр сдвига, состоящий из последовательно соединенных . регистров 12-15. Далее по каждому очередному синхроимпульсу производится циклический сдвиг информации в регистрах 12-15. По мере сдвига эта информация выдается последовательным кодом из регистра 15 на выход 6 ПШ. Сигнал прерывания удерживается на выходе 31 блока 16 управления в течение 2 (п+т) тактов. За указан- ньм промежуток времени на выход 6 ПЛМ выдается диагностическая последовательность из 2 (п+т) двоичных

цифр. Первые m цифр этой последовательности содержат циклически сдвинутую на один разряд информацию о сигналах, имевших место в момент обнаружения ошибки на входах 22 матрицы 11, следующие 2п цифр - циклически сдвинутую на один разряд информацию о сигналах, имевших место в момент обнаружения ошибки на входах 20 матрицы 10, а последние m цифр - промежуточное слово, имевшее место в тот же момент времени на выходах 21 матрицы 10. Выходное слово, снятое в момент обнаружения ошибки с выходов 23 матрицы 11, сохраняется в регистре 18.

Таким образом, за 2 (п+т) тактов прерывания на выходы 6 и 2 ПЛМ вьща- ется информация о состоянии всех входов и всех выходов элементов И матрицы 10 и элементов ИЛИ матрицы 11. Анализ этой информации позволяет локализовать любые дефекты настройки, обнаруженные блоками 8 и 9 контроля, с точностью до отдельных элементов связи матриц 10 и 11.

После вьщачи диагностической информации, т.е. после 2 (п+т) тактов циклического сдвига, содержимое каж- дого из регистров 12-15 автоматически восстанавливается (становится таким

же, каким оно было на момент выдачи сигнала прерывания блоком 16 управления). На выходе 31 блока 16 управления взамен сигнала прерывания уста-;

навливается сигнал, запрещающий сдвиги в регистре 12, разрешающий параллельный прием в регистры 12 и 18 и циклические сдвиги в кольцевых реги- страх 13-14 и 15. Тем самым осуществляется возврат в прерванную точку на продолжение одновременного опроса матриц 10 и 11.

Работа ПЛМ в режиме уточненной са мопроверки повторяется до тех пор, пока не будет изменен набор сигналов на входах 4 и 5.

Режим полной проверки ПЛМ ориентирован на случай, когда достовер- ность результатов диагностирования должна быть особо высокой. Он может применяться, например, при организации диагностирования ПЛМ, предназначенных для использования в составе невосстанавливаемых устройств пы- числительной техники.

В режиме полной проверки блок 16 управления производит периодическую смену сигналов на своем выходе 31 независимо от результатов работы бл ов 8 и 9 контроля. В течение одного такта на выходе 31 блока 16 управления удерживается сигнал, разрешающий опрос матриц 10 и 11, а в течечие следующих 2 (п+га) тактов сигнал прерывания, обеспечивающий вьщачу полученной ftp и опросе матриц 10 и 11 диагностической информации из ПЛМ. При этом последовательность воздействий, поступающих в тактах опроса на входы 20 матрицы 10, имеет вид

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемая логическая матрица | 1983 |

|

SU1159066A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| МОДУЛЬ ВВОДА-ВЫВОДА СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1991 |

|

RU2032201C1 |

| Ассоциативный матричный процессор | 1981 |

|

SU1005065A1 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1388949A1 |

| Устройство для обнаружения и исправления ошибок в доменной памяти | 1985 |

|

SU1275540A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Программируемый сопроцессор | 1988 |

|

SU1675880A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах управления. Целью изобретения является уменьшение времени диагностирования программируемой логической матрицы (ПЛМ) со встроенными средствами контроля за счет совмещения во времени процесса проверки составляющих ПЛМ элементов И 10 и элементов ИЛИ 11. Для достижения этой цели в состав ПЛМ введен второй мультиплексор 19. Благодаря этому возможна одновременная диагностика элементов И и элементов ИЛИ ШТМ. 1 ип. Q

2п воздействий

и представляет собой для каждого Аналогично, последовательность из элементов И матрицы 10 полный воздействий в тактах опроса на вхо- веряющий тест, позволяющий обнару- дах 22 матрицы 11 имеет вид жить любые константные неисправности этих элементов.

m воздействии

и представляет собой для каждого из элементов ИЛИ матрицы 11 полный проверяющий тест, позволяющий обнаружить любые константные неисправности этих элементов.

Следовательно, введенные в ПЛМ средства обеспечивают в данном режиме генерацию полных проверяющих тес- тов одновременно для элементов матрицы 10 и матрицы 11, совмещенное во времени выполнение этих тестов, а также выдачу результатов выполнения тестов на выходы 6 и 2 ПЛМ. Выдача из ПЛМ результатов выполнения тестов делает возможным выявление любых константных неисправностей элементов И и ИЛИ, в том числе и тех неисправностей, которые не обнаруживаются бло- ками 8 и 9 контроля.

Циклы полной проверки ПЛМ повторяются до тех пор, пока не будет изменен набор сигналов на входах 4 и 5.

Формула изобретения

Программируемая логическая матрица, содержащая элементы И, элементы

5

0 5 0

5

ИЛ1, первый и второй блоки контроля, входы которых соединены с выходами элементов И и ИЛИ соответственно, первый и второй входные, первьй и второй буферные и выходной регистры сдвига, блок управления и первый мультиплексор, причем входы параллельного приема информации первого и второго входных регистров сдвига являются информационными входами про- грамм1фувмой логической матрицы, а выходы соединены соответственно с входами элементов И, входы параллельного приема информации первого и второго буферных регистров сдвига соединены с выходами элементов И, выходы второго буферного регистра сдвига - с входами элементов ИЛИ, выходы которых соединены с входами параллельного приема информации выходного регистра, выходы которого являются информационными выходами программируемой логической матрицы, последовательные выходы первого буферного и первого входного регистров сдвига соединены соответственно с первым информационным входом первого мультиплексора и с последовательным информационным входом второго входного регистра сдвига, последовательный вьсход второго буферного регистра сдвига соединен с последовательным информационным входом первого буферного регистра сдвига и является выходом диагностической информации программиру- емой логической матрицы, выход первого мультиплексора соединен с последовательным информационным входом первого входного регистра сдвига, первый и второй входы блока управле- ния являются соответственно первым и вторым входами задания режима работы программируемой логической матрицы, третий вход блока управления является входом синхронизации программиру- емой логической матрицы и соединен с входами синхронизации всех регистров, четвертый и пятый входы блока управления соединены соответственно с выходами первого ,и второго блоков контроля, первый и второй выходы, блока управления соединены соответственно с управляющими и установочными входами первого и второго входных и второго буферного регистров сдвига, третий выход - е управляющими входами первого мультиплексора, первого буферного и выходного регистров сдвига, а четвертый выход является контрольным выходом программируемой логической матрицы, отличающаяся тем, что, с целью уменьшения времени диагностирования программируемой логической матрицы, в нее введен второй мультиплексор, первый информационный вход которого соединен с последовательным выходом второго входного регистра сдвига и вторым информационным входом первого мультиплексора, второй информационный вход - с последовательным выходом второго бу,ферного регистра сдвига, управляющий вход - с управляющим входом первого мультиплексора, а выход - с последовательным информационным входом второго буферного регистра сдвига.

| Программируемая логическая матрица | 1976 |

|

SU739651A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Авторское свидетельство СССР 1300456, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-15—Публикация

1986-08-11—Подача