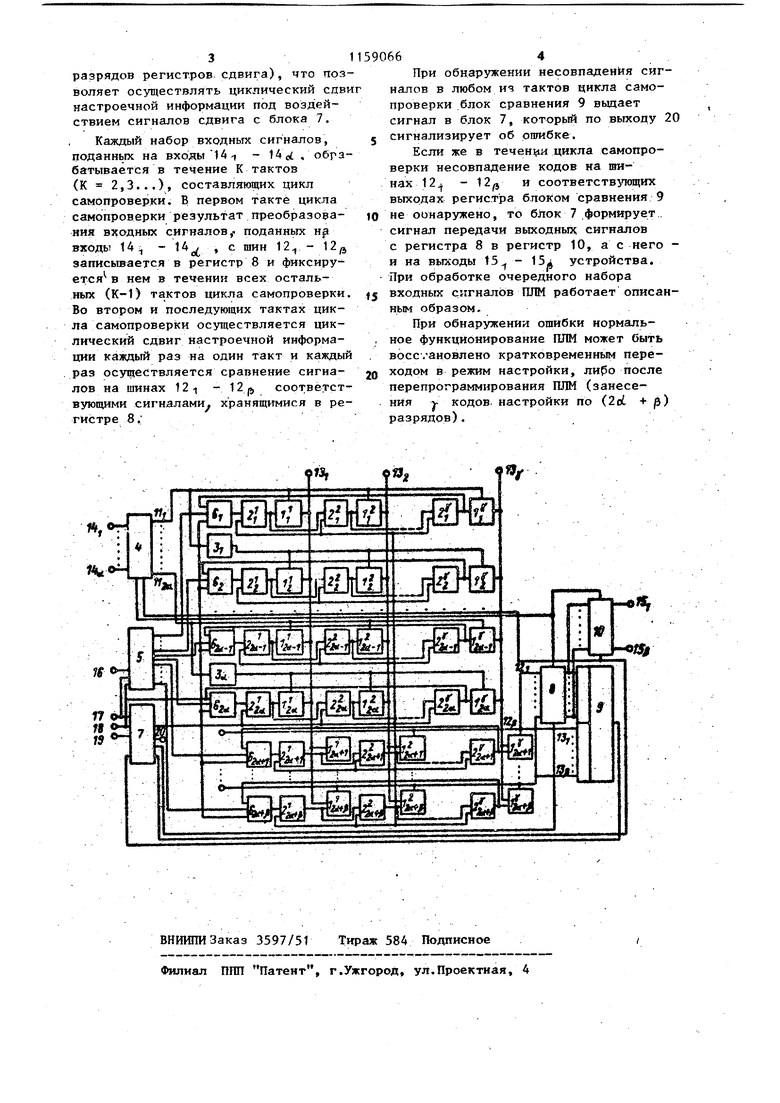

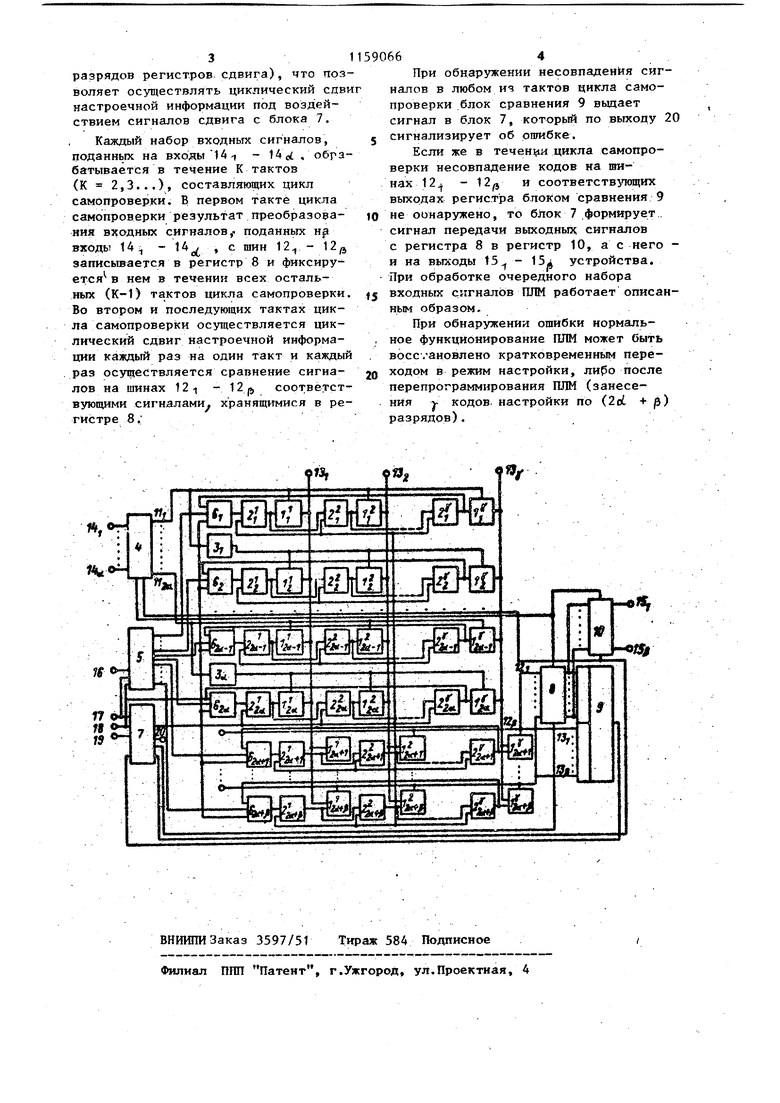

, Изобретение относитсяк вычислительной технике и может быть использовано в устройствах управления и специализированных вычислителях, в которых предусмотрен режим самопроверки. Целью изобретения являefcя повы-. шениё надежности программируемой логической матрицы (ПЛИ) путем введе ния средств самопроверки. На чертеже представлена схема предлагаемого устройства. ПЛМ содержит элементы связи пер2ot и второй матриц, (2oC + /i) элементов памяти 5, ci- инверторов 3, первый (входной) регистр 4, второй регистр 5, предна наченный для ввода настроечной инфор мации, коммутаторы 6, блок управ ления 7, третий (буферный) регистр В блок сравнения 9, четвертый (выходной) регистр 10. Элементы связи первой матрицы подключены к 2oi-roризонтальным шинам 11, а элементь связи второй матрицы - к д-горизонтальным шинам 12, у-вертикальных шин 13 являются общими для первой и второй матриц. Информационные входы .первого регистра 4 и выходы четвертого регистра 10 являются соответственно информационными вхо. дами 14 и выходами 15 ПЛМ, вход вто .рого регистра 5 является входом 16 настроечной информации ПЛМ. Блок управления 7 имеет четыре входа и четыре выхода: первый вход соединен с выходом блока сравнения 9, второй 17, третий 18 и четвертый 19 входы являютст соответственно синхр входом ПЛМ, управляющим входом ПЛМ и входом установки режима самопроверки, первый выход соединен со вто рьми входами элементов памяти 2, второй выход является выходом 20 сигнала ошибки, третий выход соединен с управляющими входами первого 4 и четвертого 10 регистров, а четвертый выход - с управляющим входом третьего регистра 8. Информация, записанная в элементах памяти 2, фиксируется в соответ ствуницих элементах ,вязи 1, каждый из которых вьшолнен, например, на двух МДП транзисторах. Каждая строка элементов памяти представляет собой кольцевой регистр сдвига, упрйвляемый сигналами с первого выхо да блока управления 7. В основе при ципа самопроверки лежит сравнение к дов на выходах второй матрицы, получаемых при сдвиге на К (2 К - и определяется сигналом на входе 19) разрядов. В ПЛМ без дефектов сравниваемые коды должны быть одинаковыми. Режимы работы ПЛМ следующие: режим настройки (ввода настроечной информации) и режим обработки входной информации. В исходном состоянии на входах 16, 17, 18, 14, выходах 15 и 20 - нулевые сигналы. Соответственно в регистре 5 хранятся нулевые коды, элементы памяти 2 - 2(2ot+/5) состоянии. В режиме настройки на вход 18 поступает елиничный сигнал, устанавливающий регистры 8 и 10 в нулевое состояние. При этом в (.2aL р ) разрядный регистр 5 разрешается прием настроечной информации со входа 16 под воздействием сигналов синхронизации на входе 17. Коммутаторы 6 - подключают (в режиме настройки) выходы регистра 5 к входам элементов памяти 2 - ) являющихся первыми разрядами (Zot + + /1) регистров сдвига. Настроечная информация, определяющая функции- ПЛМ, представляется в виде кодов разрядностью (2at +/), таким образом после записи кодов в элементы памяти 2. - 2/,,..,, про„ ) цесс настройки заканчивается. Настроечная информация поразрядно поступает на вход 16 синхронно с сигналами со входа 17. После ввода. (2оС о, ) разрядов кода настройки в ре-истр 5 блок 7 выдает сигналj. разрешающий перезапись информации из регистра 5 в элементы памяти 2, , предварительно информация из элементов 2 - 2 (i 1л,1 ) переписывается в э.пемен2 У - 2 ( (происходит ты синхронный сдвиг информации в зиг информации в (2оС ) регистрах сдвига). В Течение (2dL / ) у тактов вводится J- кодов настройки. В режиме обработки входной информации на вход 18 поступает нулевой сигнал, коммутаторы 6, - 6 2ai-t отключают входы элементов памяти 2 i (4-ft) разрядов регистров сдвига от соответствующих выхог дов регистра 5 и соединяют эти. входы с выходами соответствующих 2( элементов памяти (старших 3 разрядов регистров сдвига), что поз воляет осуществлять циклический сдв настроечной информации под воздействием сигналов сдвига с блока 7. Каждый набор входных сигналов, подаиньк на входы14 - 14ci , обра ба:тывается в течение К тактов (К 2,3...), составляющих цикл самопроверки. В первом такте цикла самопроверки результат преобразования входных сигналов , поданных нр входы 14 °™ 2 - 12,j записьшается в регистр 8 и фиксируется в нем в течении всех остальных (К-1) тактов цикла самопроверки Во втором и последующих тактах цикла самопроверки осуществляется циклический сдвиг настроечной информации каждый раз на один такт и каждый раз осуществляется сравнение сигналов на шинах 12-, - 12 соответствующими сигналами хранящимися в регистре 8.; 664 При обнаружении несовпадения сигналов в любом ич тактов цикла самопроверки блок сравнения 9 вьщает сигнал в блок 7, которьтй по выходу 20 сигнализирует об рпгабке. Если же в течении цикла самопроверки несовпадение кодов на шинах 12 - 12 и соответствпощих выходах регистра блоком сравнения 9 не оонаружено, то блок 7 формирует . сигнал передачи вьжодных сигналов с регистра 8 в регистр 10, а с него и на выходы t5 - 15.J устройства. При обработке очередного набора входных сигналов ШТМ работает описанным образом. При обнаружении ошибки нормальнов функционирование ПЛМ может быть восс/ановлено кратковременным переходом в режим настройки, лиро после перепрограммирования ПЛМ (занесения |- кодов настройки по (2ot р) разрядов).

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемая логическая матрица | 1986 |

|

SU1381481A1 |

| Программируемое логическое устройство | 1984 |

|

SU1257702A1 |

| Программируемое запоминающее устройство | 1985 |

|

SU1282219A1 |

| Трехкаскадная коммутирующая система | 1984 |

|

SU1226481A1 |

| Трехкаскадная коммутирующая система | 1989 |

|

SU1622886A1 |

| ТРЕХКАСКАДНАЯ КОММУТАЦИОННАЯ СИСТЕМА | 2007 |

|

RU2359313C2 |

| МОДУЛЬ ВВОДА-ВЫВОДА СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1991 |

|

RU2032201C1 |

| Программируемый сопроцессор | 1988 |

|

SU1675880A1 |

| Контроллер памяти команд | 1988 |

|

SU1617440A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1667069A1 |

ГГРОГРАМ№ РУЕМАЯ ЛОГИЧЕСКАЯ МАТРИЦА, содержащая первую матрицу 2 ti-f элементов связи, где 2 cL - число строк данной матрицы, а - число термов программируемой логической матрицы, вторую матрицу yjу элементов свяэи, где д- число строк Д9ННОЙ матрицы,

| Программируемая логическая матрица | 1976 |

|

SU739651A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Программируемая логическая матрица | 1980 |

|

SU935945A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-05-30—Публикация

1983-06-13—Подача