со

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство усиления | 1985 |

|

SU1338001A1 |

| Устройство усиления | 1989 |

|

SU1617629A1 |

| Вычислительное устройство | 1985 |

|

SU1282163A1 |

| Множительно-делительное устройство | 1987 |

|

SU1543426A1 |

| Устройство регулирования уровня сигнала | 1982 |

|

SU1104653A1 |

| Вычислительное устройство | 1987 |

|

SU1462364A1 |

| Вычислительное устройство | 1987 |

|

SU1539798A1 |

| Логарифмическое вычислительное устройство | 1987 |

|

SU1543425A1 |

| Среднеквадратичный детектор | 1985 |

|

SU1277004A1 |

| Аналоговое логарифмическое вычислительное устройство | 1983 |

|

SU1137486A2 |

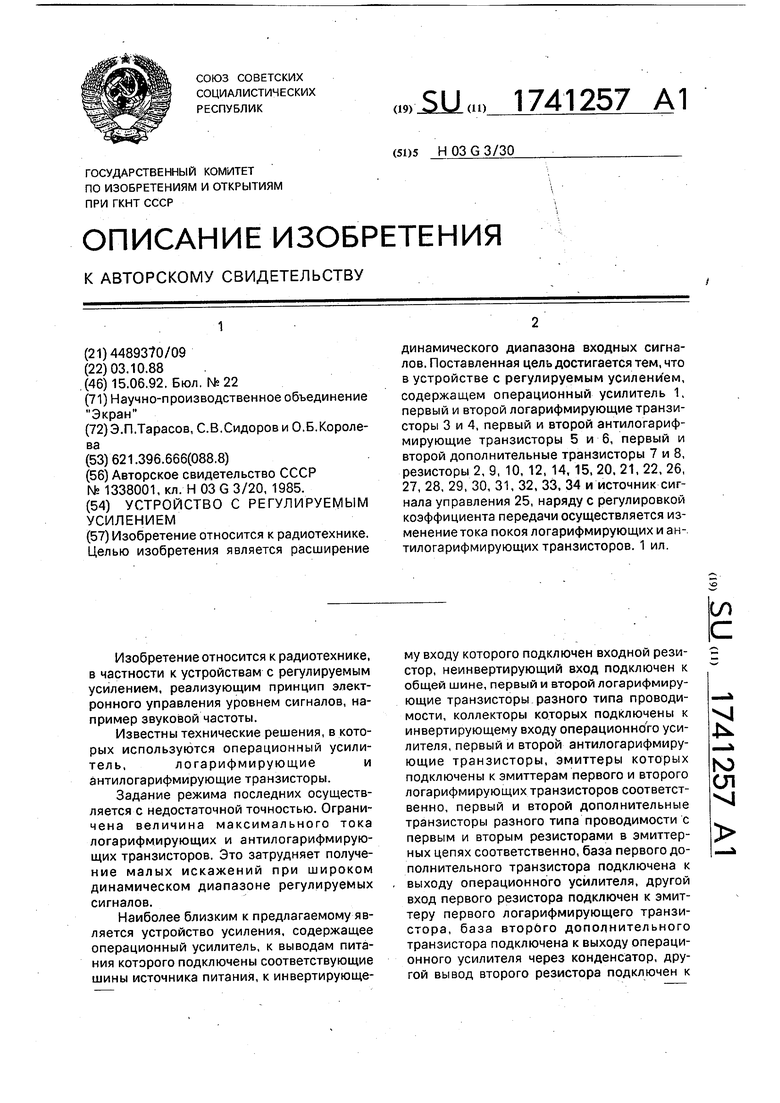

Изобретение относится к радиотехнике. Целью изобретения является расширение динамического диапазона входных сигналов. Поставленная цель достигается тем, что в устройстве с регулируемым усилением, содержащем операционный усилитель 1, первый и второй логарифмирующие транзисторы 3 и 4, первый и второй антилогариф- мирующие транзисторы 5 и 6, первый и второй дополнительные транзисторы 7 и 8, резисторы 2, 9, 10, 12, 14, 15, 20. 21, 22, 26, 27, 28, 29, 30, 31, 32, 33, 34 и источник сигнала управления 25, наряду с регулировкой коэффициента передачи осуществляется изменение тока покоя логарифмирующих и ан- тилогарифмирующих транзисторов. 1 ил

Изобретение относится к радиотехнике, в частности к устройствам с регулируемым усилением, реализующим принцип электронного управления уровнем сигналов, например звуковой частоты.

Известны технические решения, в которых используются операционный усилитель,логарифмирующиеи антилогарифмирующие транзисторы.

Задание режима последних осуществляется с недостаточной точностью. Ограничена величина максимального тока логарифмирующих и антилогарифмирую- щих транзисторов. Это затрудняет получение малых искажений при широком динамическом диапазоне регулируемых сигналов.

Наиболее близким к предлагаемому является устройство усиления, содержащее операционный усилитель, к выводам питания которого подключены соответствующие шины источника питания, к инвертирующему входу которого подключен входной резистор, неинвертирующий вход подключен к общей шине, первый и второй логарифмирующие транзисторы разного типа проводимости, коллекторы которых подключены к инвертирующему входу операционного усилителя, первый и второй антилогарифмирующие транзисторы, эмиттеры которых подключены к эмиттерам первого и второго логарифмирующих транзисторов соответственно, первый и второй дополнительные транзисторы разного типа проводимости с первым и вторым резисторами в эмиттер- ных цепях соответственно, база первого дополнительного транзистора подключена к выходу операционного усилителя, другой вход первого резистора подключен к эмиттеру первого логарифмирующего транзистора, база второго дополнительного транзистора подключена к выходу операционного усилителя через конденсатор, другой вывод второго резистора подключен к

VI

4

Ю СЛ VJ

эмиттеру второго логарифмирующего транзистора, последовательно соединенные третий резистор, другой вывод которого подключен к первой шине источника питания, и первый диод, последовательно соеди- ненные четвертый и пятый резисторы, другой вывод пятого резистора подключен ко второй шине источника питания, шестой резистор, включенный между коллектором второго дополнительного транзистора и первой шиной источника питания, третий дополнительный транзистор, эмиттер и коллектор которого подключены соответственно к коллектору второго дополнительного транзистора и через конденсатор к выходу операционного усилителя, база - к точке соединения первого диода с четвертым резистором, токоограничивающий транзистор, база которого подключена к точке соединения четвертого и пятого резисторов, эмиттер - к коллектору первого дополнительного транзистора, коллектор - к второй шине источника питания, транзистор защиты, база которого подключена к точке соединения третьего резистора с первым диодом, эмиттер - к кол лектору, второго дополнительного транзистора, коллектор - к первой шине источника питания, последовательно соединенные второй диод и седьмой резистор, включенные между коллектором первого дополнительного транзистора и второй шиной источника питания, четвертый дополнительный транзистор с восьмым резистором в цепи эмиттера, база и коллектор которого подключены к коллектору первого дополнительного транзистора и через конденсатор - к выходу операционного усилителя соответственно, другой вывод восьмого резистора подключен ко второй шине источника питания, а также источник управляющего сигнала.

В данном устройстве максимально возможный ток логарифмирующих транзисторов практически не ограничивается (т.е. ограничивается значениями максимально допустимых токов этих транзисторов или реверсами источника питания). Это позволяет добиться в устройстве большой перегрузочной способности по регулируемым сигналам. Дополнительными транзисторами задается и стабилизируется исходный ток покоя логарифмирующих и антилога- рифмирующих транзисторов с высокой точностью. Последнее говорит о возможности получения малых значений тока покоя, необходимого для снижения уровня шума устройства, но достаточного для получения и малых нелинейных искажений.

Нелинейные искажения при малых значениях токов покоя логарифмирующих и ан- тилогарифмирующих транзисторов могут возникать в соответствующие полупериоды

регулируемых сигналов, когда токи транзисторов становятся меньше исходных значений. Если эти токи становятся нулевыми, в транзисторе возникает отечка тока, которую можно избежать точным заданием необхо0 димой величины тока покоя. В прототипе при реализации особо высокой перегрузки по входу (особенно, например, при уменьшенном сопротивлении входного резистора, что полезно для увеличения

5 максимального коэффициента передачи устройства) с введением соответствующего большого затухания уменьшением токов ан- тилогарифмирующих транзисторов становится важным снижение гармонических

0 искажений в логарифмирующих транзисторах, работающих при больших входных токах устройства. Это означает снижение мощности гармонических составляющих регулируемых сигналов в логарифмирующих

5 транзисторах с тем, чтобы они мало были заметны на фоне малых по мощности сигналов (антилогарифмирующих транзисторов) на выходе устройства куда они проникают. Для расширения динамического диапа0 зона входных сигналов в устройство с регулируемым усилением введены девятый и десятый резисторы, каждый из которых включены между общей шиной и базой соответственно второго антилогарифмирую5 щего транзистора и базой первого логарифмирующего транзистора, Г-образ- ный аттенюатор, в продольном плече которого включен одиннадцатый резистор, а в поперечном - две параллельно включенные

0 цепи, первая из которых выполнена в виде последовательно соединенных двенадцатого и тринадцатого резисторов, точка соединения которых подключена к базе первого антилогарифмирующего транзистора, вто5 рая - в виде последовательно соединенных четырнадцатого и пятнадцатого резисторов, точка соединения которых подключена к базе второго логарифмирующего транзистора, шестнадцатый резистор, включен0 ный между другим выводом первого диода и другим выводом четвертого резистора, последовательно соединенные третий диод и семнадцатый резистор, включенные между выходом источника управляющего сигнала,

5 подключенным также к входу Г-образного аттенюатора, и точкой соединения шестнадцатого резистора с четвертым.

Принципиальная электрическая схема устройства с регулируемым усилением показана на чертеже.

Устройство с регулируемым усилением содержит операционный усилитель 1, входной резистор 2, первый и второй логарифмирующие транзисторы 3 и 4, первый и второй антилогарифмирующие транзисторы 5 и 6, первый и второй дополнительные транзисторы 7 и 8, первый и второй резисторы 9 и 10, конденсатор 11, третий резистор 12, первый диод 13, четвертый и пятый резисторы 14 и 15, третий и четвертый дополнительные транзисторы 16 и 17, токоограничивающий транзистор 18, транзистор 19 защиты, шестой, седьмой и восьмой резисторы 20, 21 и 22, второй диод 23, источник 24 питания, источник 25 сигнала управления, девятый - семнадцатый резисторы 26 - 34, третий диод 35. Клемма 36 является выходом устройства, к которому подключены коллекторы антилогарифмиру- ющих транзисторов 5,6.

В режиме покоя примем исходное напряжение источника 25 сигнала управления нулевым. Соответственно напряжение на базах логарифмирующих и антилогарифми- рующих транзисторов 3-6 также будет нуле- вым относительно общей шины. Напряжения смещения на эмиттерных переходах этих транзисторов можно считать одинаковыми, как и их токи.Суммарный ток эмиттеров транзисторов 3 и 5 соответствует эмиттерному току первого дополнительного транзистора 7, а суммарный ток эмиттеров транзисторов 4 и 6 - эмиттерному току второго дополнительного транзистора 8. Абсо- лютная величина и стабильность эмиттерных токов транзисторов 7 и 8 определяется параметрами соответствующих цепей отрицательной обратной связи по постоянному току, действие которой обеспечивается с использованием третьего и четвертого дополнительных транзисторов

16и 17. Величины коллекторного тока транзистора 7 и эмиттерного тока транзистора

17определяются сопротивлениями седьмого резистора 21 и восьмого резистора 22, падения напряжения на которых практически одинаковы. Суммарный ток коллектора транзистора 8 и эмиттера транзистора 16 задается падением напряжения на сопротивлении третьего резистора 12. При этом коллекторные токи транзисторов 16 и 17 практически соответствуют друг другу. Ток через резистор 12 (а также первый диод 13) определяется выбором суммарного сопротивления четвертого, пятого и шестнадцатого резисторов 14,15 и 33. Потенциал общей точки соединения выводов резисторов 14 и 33 (относительно общей шины) должен примерно соответствовать напряжению открывания третьего диода 35. При подаче

переменного тока через входной резистор 2 возникающие токи логарифмирующих и ан- тилогарифмирующих транзисторов 3 и 5, 4 и 6 соответственно равны.

При положительном напряжении источника 25 третий диод 35 закрыт. Через делители из одиннадцатого - пятнадцатого резисторов 28-32 на базы транзисторов 4 и 5 поступает положительное управляющее

0 напряжение. Для правильного управления транзисторами 3 - 6 и осуществления ими своих функций сопротивления резисторов 26, 27, 29 и 32 должны быть одинаковыми и относительно малыми (меньше сопротивле5 ния базы логарифмирующего или антилога- рифмирующеготранзистора).

Получающееся изменение режимов транзисторов 3-6 приводит к увеличению коэффициента передачи устройства. При этом токи

0 транзисторов 5 и 6 возрастают, но только до величины исходных токов транзисторов 7 и 8, поэтому коэффициент передачи устройст- - ва возрастает практически за счет уменьшения токов транзисторов 3 и 4. Это

5 способствует получению низкого уровня шума на выходе устройства, причем нелинейные искажения также малы, поскольку уменьшен входной ток через входной резистор 2.

0

При отрицательном напряжении источника 25 диод 35 открывается. Возникающий постоянный ток через семнадцатый резистор 34 приводит к возрастанию тока сме5 щения через резисторы 12,33 и уменьшению тока через резисторы 14,15. Результатом является увеличение исходных токов транзисторов 7 и 8, значения которых достигают и возросшие токи логарифмиру0 ющих транзисторов 3,4, причем коэффициент передачи устройства уменьшается. Дальнейшее снижение последнего, т.е. введение затухания регулирующих сигналов, обеспечивается уменьшением токов анти5 логарифмирующих транзисторов 5 и 6. Бла- годаря этому увеличение токов логарифмирующих транзисторов 3,4 не может влиять на уровень шума на выходе устройства, в то время как существенно

0 снижаются гармонические искажения или повышается точность в логарифмировании. Это особенно важно, т.к. ток через входной резистор 2 оказывается максимальным, соответствующим перегрузке по входу устрой5 ства, и особенно важным является снижение мощности гармонических составляющих искажений, которые, проникая в выходной сигнал очень низкого уровня при затухании (-40 дБ и более), мало влияют на искажение всего устройства.

Под влиянием постоянного тока через резистор 34 (и диод 35) изменение режима смещения дополнительных транзисторов 7,8,16,17 сказывается одновременно (и одинаково) на логарифмирующих и антилога- рифмирующих транзисторах 3,4 и 5,6, поэтому не влияет на коэффициент передачи устройства.

Пример. Изобретение реализовано в усилительном модуле управляемом УМУ5, на основе которого строится звуковой канал профессиональной звукотехнической аппаратуры. На выходе модуля включен инвертирующий операционный усилитель с отрицательной обратной связью по напряжению параллельного типа. Сопротивление резистора обратной связи принято равным 46,4 кОм, как и для входного резистора 2. При нулевом напряжении источника сигнала 25 управления коэффициент передачи ус- тройства по напряжению (усиление) определяется отношением сопротивлений названных резисторов и равен 1 (0 дБ). Исходный ток покоя первого и второго дополнительных транзисторов 7,8 составляет 40 мкА. Максимальное входное и выходное напряжение 8 В.

В диапазоне частот 20-20000 Гц гармонические искажения не превышают 0,057о. Уровень шума на выходе относительно 0,775 В (0 дБ) составляет около 90 дБ (измерение со взвешивающим фильтром по кривой А).

Максимальное усиление по напряжению +30 дБ, максимальное затухание - 100 дБ (при напряжении источника сигнала управления +3 В и - 10 В соответственно). Гармонические искажения на средних частотах не превышают 0,1%, на крайних - 0,2%. При введении затухания суммарный исходный ток покоя логарифмирующих и ан- тилогарифмирующих транзисторов возрастает в (2-3) раза.

Формула изобретения

Устройство с регулируемым усилением, содержащее операционный усилитель, к выводам питания которого подключены соответствующие шины источника питания, к инвертирующему входу которого подключен входной резистор, неинвертирующий вход подключен к общей шине, первый и второй логарифмирующие транзисторы разного типа проводимости, коллекторы которых подключены к инвертирующему входу операционного усилителя, первый и второй антилогарифмирующие транзисторы, эмиттеры которых подключены к эмиттерам первого и второго логарифмирующих транзисторов соответственно, первый и второй дополнительные транзисторы разного типа проводимости с первым и вторым резисторами в эмиттерных цепях соответственно, база первого дополнительного транзистора подключена к выходу

5 операционного усилителя, другой вывод первого резистора подключен к эмиттеру первого логарифмирующего транзистора, база второго дополнительного транзистора подключена к выходу операционного усили0 теля через конденсатор, другой вывод второго резистора подключен к эмиттеру второго логарифмирующего транзистора, последовательно соединенные третий резистор, другой вывод которого подключен к

5 первой шине источника питания, и первый диод, последовательно соединенные четвертый и пятый резисторы, другой вывод пятого резистора подключен к второй шине источника питания, шестой резистор, вклю0 ченный между коллектором второго дополнительного транзистора и первой шиной источника питания, третий дополнительный транзистор, эмиттер и коллектор которого подключены соответственно к коллектору и

5 базе второго дополнительного транзистора, база - к точке соединения первого диода с четвертым резистором, токоограничиваю- щий транзистор, база которого подключена к точке соединения четвертого и пятого ре0 зисторов, эмиттер - к коллектору первого дополнительного транзистора, коллектор - к второй шине источника питания, транзистор защиты, база которого подключена к точке соединения третьего резистора с пер5 вым диодом, эмиттер - к коллектору второго дополнительного транзистора, коллектор - к первой шине источника питания, последовательно соединенные второй диод и седьмой резистор, включенные между

0 коллектором первого дополнительного транзистора и второй шиной источника питания, четвертый дополнительный транзистор с восьмым резистором в цепи эмиттера, база и коллектор которого под5 ключены к коллектору первого дополнительного транзистора и к коллектору третьего дополнительного транзистора соответственно, другой вывод восьмого резистора подключен к второй шине источника пита0 ния, а также источник управляющего смгна ла, отличающееся тем, что, с целью расширения динамического диапазона входных сигналов, в него введены девятый и десятый резисторы, каждый из которых

5 включен между общей шиной и базой соот ветственно второго антилогарифмирующего транзистора и базой первого

логарифмирующего транзистора, Г-образный аттенюатор, в продольном плече которого включен одиннадцатый резистор, а в

поперечном -две параллельно включенные цепи, первая из которых выполнена в виде последовательно соединенных двенадцатого и тринадцатого резисторов, точка соединения которых подключена к базе первого антилогарифмирующего транзистора, вторая - в виде последовательно соединенных четырнадцатого и пятнадцатого резисторов, точка соединения которых подключена к базе второго

0

логарифмирующего транзистора, шестнадцатый резистор, включенный между другим выводом первого диода и другим выводом четвертого резистора, последовательно соединенные третий диод и семнадцатый резистор, включенные между выходом источника управляющего сигнала, подключенным также к входу Г-образного аттенюатора, и точкой соединения шестнадцатого резистора с четвертым.

| Устройство усиления | 1985 |

|

SU1338001A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-06-15—Публикация

1988-10-03—Подача