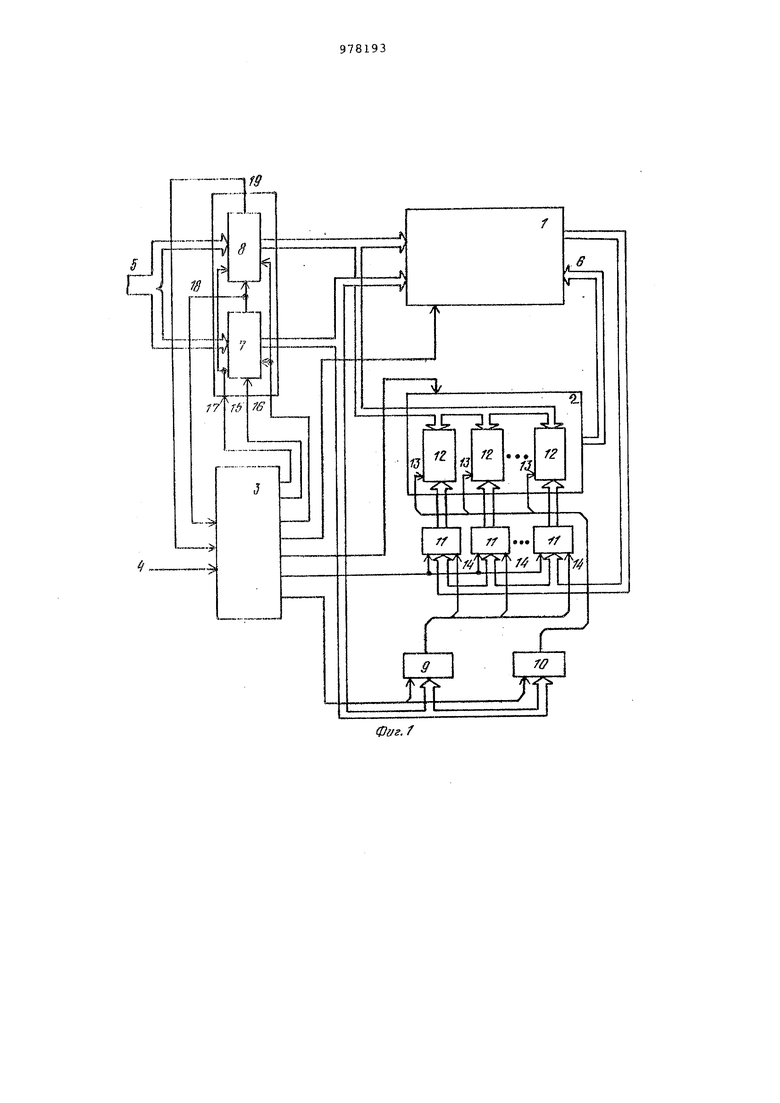

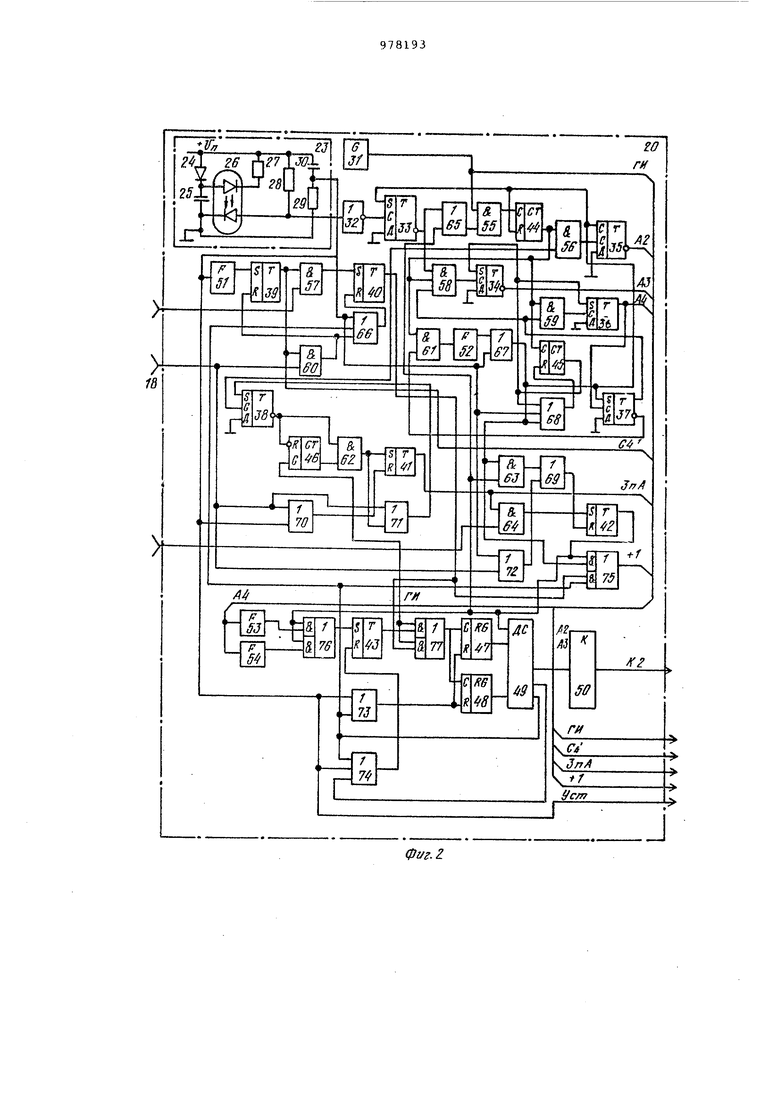

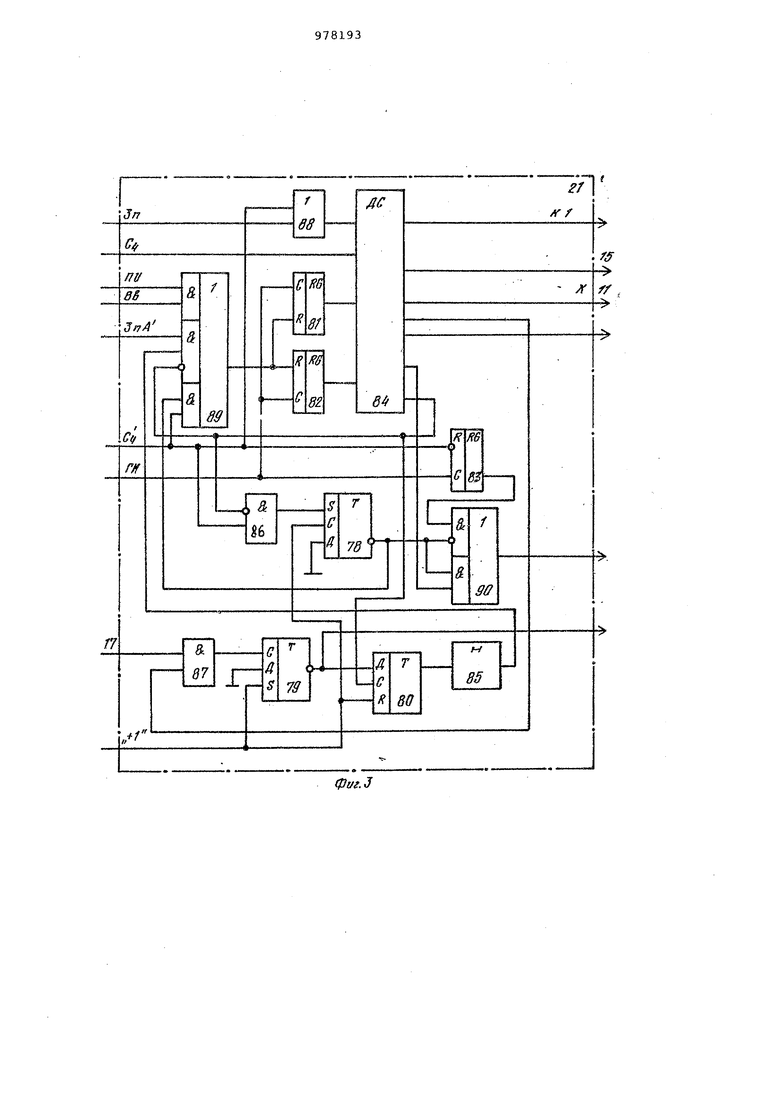

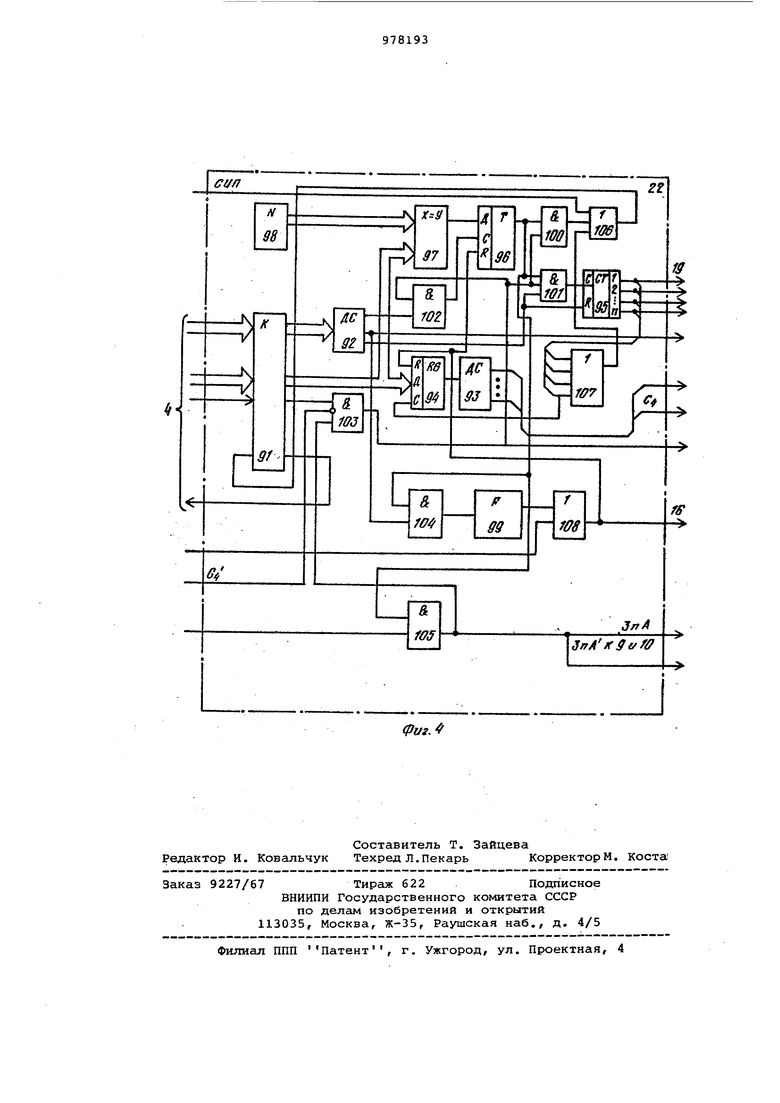

входы регистров соединены соответст венно с информационными входеиии- дополнительного блока памяти и выхода ми основного блока памяти, адресные входы которого подключены к разрядн выходам первого и второго счетчиков адресные входы дополнительного блок памяти и информационные входы блоко декодирования информации соединены соответственно с разрядными выходам второго и первого счетчиков, выходы первого и второго блоков Д{акодирова ния информации подк.пн:ченьт соответст венно к входам разрешения записи ре rvscTpoB и к входам разрешения, обраще ния дополнительного блока памяти, входы синхронизации блоков декодирования информации, регистров и дополнргтельиого блока памяти и тактовые входы и входы управления предварител ной Зстановкой счетчиков соединены соответственно с другими выходами блока, управления у одни из входов которого подк.яючены ic выходам переполнения счетчиков, входы предварительной установки которых являются адрес ными входами устройства„ Па фиг, 1 представлена структурная схема устройства; на фиг. 2-4 функциональные схемы блока управле Устройство содержит (фиг. 1) основной 1 и дополнительный 2 блоки , блок 3 управления со входом 4 обращения, адресные входы 5 и инфо мационные входы б основного блока памятиf первый 7 и второй 8 счетчики, первый 9 и второй 10 блоки декодирования информации и регистры 11, Дополнительный блок памяти разделен на п одинаковых частей 12 разрядностью к каждая (где пик- целые чиола), Устройство содержит также входы 13 разрешения обращения дополнительного блока памяти, входы 14 разрешения записи регистров, тактовы входы 15 и входы 16 обнуления и 17 управления предварительной установко счетчиков, выходы 18 и 19 переполнения первого и второго счетчиков соответственно. Блок управления состоит из блока 20 (фиг. 2) управления дополнительным блоком памяти,-блока 21 (фиг. 3) управления основным блоком памяти и блока 22 обращения (фиг. 4). Блок управления дополнительным блоком памяти содержит узел 23 контроля питающего напряжения, состоящего из диода 24, конденсатора 25, тиристорного оптрона 26, резисторов 27-29 и конденсатора 30, генератор импульсов 31, элемент НЕ 32, Д-триггеры 33-38,RS-триггеры 39-43, счетчики 44-46, сдвиговые регистры 47,48 блок декодирования 49, ключи 50 согласования уровней, формирователи 5154 импульсов и элементы И 55-64, ИШ 65-74 и 2И-ИЛИ 75-77 „ Блок управления основнь1м блоком памяти содержит Д триггеры 78-80, сдвиговые регистры 81-83, блок 84 декодирования, элемент 85 задержки и элементы И 86,87,ИЛИ 88 и И-ИЛИ 89,90., Блок обращения состоит из ключей 91 согласования уровней сигналов, блоков декодирования 92, 93, регистра 94 команд, счетчика 95, Д-триггера 96, схемы 97 сравнения номера устройства, узла 98 набора номера устройстве., формирователя 99 импульсов и элементов И 100-105, и ИЛИ 106-108. Основной блок 1 памяти может быть ыполнен на быстродействующих полу- , проводниковых микросхема х памяти, а ополнительный блок 2 памяти - на электрически пepeпpoгpa Lмиpyer4ЫX поупостоянных запоминающих элементах а основе МНОП-структур. Устройство работает следующим образом, В случае снижения напряжения питания до определенной величины блок 3 управления запрещает обращение к устройству, переключает блоки 1 и 2 па.мяти в режимы чтения и записи соответственно и подает на вход 16 счетчиков 7 и 8 импульс обнуления. После этого блок 3 посылает импульсы тактов на вход 15 счетчика 7 и разрешает работу блока 9. Информация по каждому из п первых адресов блока 1 памяти переписывается в соответствующие регистры 11, При этом выбор нужного регистра 11 осуществляется блоком 9, а синхронизация записи - блоком 3. При появлении импульса переполнения на. выходе 18 счетчика .7, чтосоответствует заполнению последнего из п регистров 11, блок 3 прекращает подачу импульсов тактов и производит пепезапись содержимого регистров 11 параллельно в п частей 12 блока. 2 памяти в соответствии с выставленным на выходах счетчика 8 адресным кодом, который в данном случае обеспечивает запись информации в первые ячейки каждой из п частей 12. При этом блок 3 запрещает работу блока 9, а блок 10 устанавливается в режим одновременного разрешения обращения ко всем частям 12 блока 2, По окончании записи блок 3 повторяет описанный выше цикл, причем содержимое счетчика 8 увеличивается на единицу каждым импульсов переполнения счетчика 7. Появление импульса переполнения на выходе 19 счетчика 8 свидетельствует об окончании.перезаписиСодержимого блока 1 в блок 2. Блок 3 прекращает подачу импульсов тактов и запрещает работу блоков 9 -и 10. Блок 2 памяти хранит информацию при отсутствии питающего напряжения.

При достижении напряжением питания минимально допустимой величины блок 3 обнуляет счетчики 7 и 8 по входу 16, переключает блоки 1 и 2 памяти в режимы записи и чтения соответственно, а затем подает импульсы тактов на вход 15 счетчика 7 и переключает блок 10 в режим декодирования При этом блок 3 осуществляет последовательное считывание информации из блока 2 в блок 1. Появление импульса переполнения на выходе 19 счетчика 8 свидетельствует об окончании перезаписи информации из блока 2 в блок 1. Блок 3 запрещает работу блоков 9 и 10 и разрешает любой режим обращения к запоминающему устройству В Данном устройстве периферийные по отнощению к нему устройства имеют прямой доступ только к блоку 1 памяЬи, при этом начальный адрес ячейки, к которой происходит обращение, за писывается в счетчики 7 и 8. по входг1М 5 адреса по импульсу предварительной установки, вырабатываемому блоком 3 управления.

Так как перезапись информации из регистров 11 в блок 2 производится параллельно в п частей 12 блока 2, а длительность цикла считывания блока 1 много, меньше длительности цикла записи в блок 2, то время, необходимое для перезаписи информации, равно Т , где К - разрядность адреса каждой части 12, блока 2. Время перезаписи зависит от разрядности частей 12 блока 2, т.е. в конечном итоге от дискретности разбиения поля памяти блока 2. Объем памяти блока 2 определяется объемом данных, которые необходимо сохранить при отключении питания и может быть равным объему памяти блока 1, причем объем переписываемых данных определяется местом подключения вь 1хода 18 переполнения счетчика 7 ко входу счетчика 8. Дискретность разбиения блока;2 определяется требуемым временем пе:резаписи.

: Таким образом, время перезаписи информации не зависит от разрядности регистров 11 и общего объема памяти устройства, что позволяет увеличивать информационную емкость устрой-: ства и; сочетать быстродействие основного блока 1 памяти с возможностью хранения информации в блоке 2 памяти при отключении питания, причем ресурс циклов перезаписи блока 2 расходуется только в моменты отключения питания, за счет чего повышается надежность устройства.

Технико-экономическое преимущество предлагаемого устройства заключается в более высокой надежности и возможности повышения информационной емкости по сравнению с прототипом.

Формула изобретения

Энергонезависимое оперативное за0поминающее устройство, содержащее основной блок памяти, первый счетчик и дополнительный блок памяти, выходы которого соединены с информационными входами основного блока памяти, причем управляющие входы блоков памяти,

5 входы установки в нулевое состояние и тактовый вход счетчика соединены с одними из выходов блока управления, отличающееся тем, что, с целью повышения надежности и инфор0мационной емкости устройства, в него введены второй счетчик, блоки декодирования информации и регистры, причем выход переполнения первого счетчика подключен к счетному входу

5 второго счетчика, выходы и информационные входы Регистров соединены соответственно с информационными входами дополнительного блока памяти и выходами основного блока памяти,

0 адресные входы которого подключены к разрядным выходам первого и второго счетчиков, адресные входы дополнительного блока памяти и информационные

входы блоков декодирования информа5ции соединены соответстаенно с разрядными Выходами второго и первого счетчиков, выходы первого и второго блоков декодирования информации подключены соответственно к входам раз0решения записи регистров и к входам разрешения обращения дополнительного блока памяти, входы синхронизации блоков декодирования информации, регистров и дополнительного блока па5мяти и тактовые входы и входы управления предварительной установкой счетчиков соединены соответственно с другими выходами блока управления, одни из входов которого подключены к выхо0дам переполнения счетчиков, входы предварительной установки которых являются адресными входами устройства.

Источники информации,

5 принятые во внимание при экспертизе

1.Патент ФРГ № 2415029,

кл. G 11 С 7/00, опублик. 1977.

2.Авторское свидетельство СССР № 590824, кл. G 11 С 11/00, 1976 (прототип).

8

18

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Устройство для коррекции программ | 1983 |

|

SU1141416A1 |

| Динамическое запоминающее устройство с восстановлением информации | 1989 |

|

SU1689990A1 |

| Программируемая линия задержки | 1982 |

|

SU1193789A1 |

| Устройство сравнения чисел с допусками | 1987 |

|

SU1509870A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для сортировки информации | 1987 |

|

SU1509871A1 |

| Запоминающее устройство | 1980 |

|

SU898506A1 |

| Адаптивный статистический анализатор | 1980 |

|

SU877564A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

.

Авторы

Даты

1982-11-30—Публикация

1981-04-22—Подача