УСТРОЙСТВО ЦИФРОВОГО СОПРОВОЖДЕНИЯ

(54) ФАЗЫ ПЕРИОДИЧЕСКОГО СИГНАЛА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цифрового сопровождения фазы периодического сигнала | 1981 |

|

SU978364A1 |

| Устройство цифрового сопровождения фазы периодического сигнала | 1985 |

|

SU1376241A2 |

| Устройство цифрового сопровождения фазы периодического сигнала | 1979 |

|

SU902266A1 |

| Цифровой преобразователь частоты | 1981 |

|

SU1054875A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| Автоматический цифровой измеритель коэффициента гармоник | 1980 |

|

SU911363A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Двухотчетный преобразователь углового перемещения в цифровой код | 1975 |

|

SU526932A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

Изобретение относится к электротехнике и может быть использовано в фазометрах, регутшрующих и управляющих устройствах электрических и радиотехнических систем для получения информации о мгновенном текущем значении фазы периодического сигнала.

Известно цифровое устройство для измерения мгновенных значений фазы периодически повторяющихся процессов, основанное на заполнении счетчика импульсами образцовой частотыв течение измеряемого интервала времени, т.е. в течение периода процесса. На цифровых выходах счетчика образуются мгновенные значения коаа, соответствующие фазе периодического процесса. Такое устройство содержит соединенные последовательно генератор импульсов обра цовой частоты и счетчик, а также детекг тор нулей периодического сигнала, вход которого является входом устройства, а выход подключен к входу установки счетчика импульсов 1}.

Это устройство формирует информацию о текущей фазе периодического процесса с высокой точностью и быстродействием, но обеспечивает точность только при строгом взаимном соответствщ эталонной частоты и частоты сопровожудаемого переодического сигнала. Недоотатком устройства является также редкое увеличение погрешности сопровождения при отклонении частоты переодического

10 процесса от основной частоты, на которую настроено это устройство.

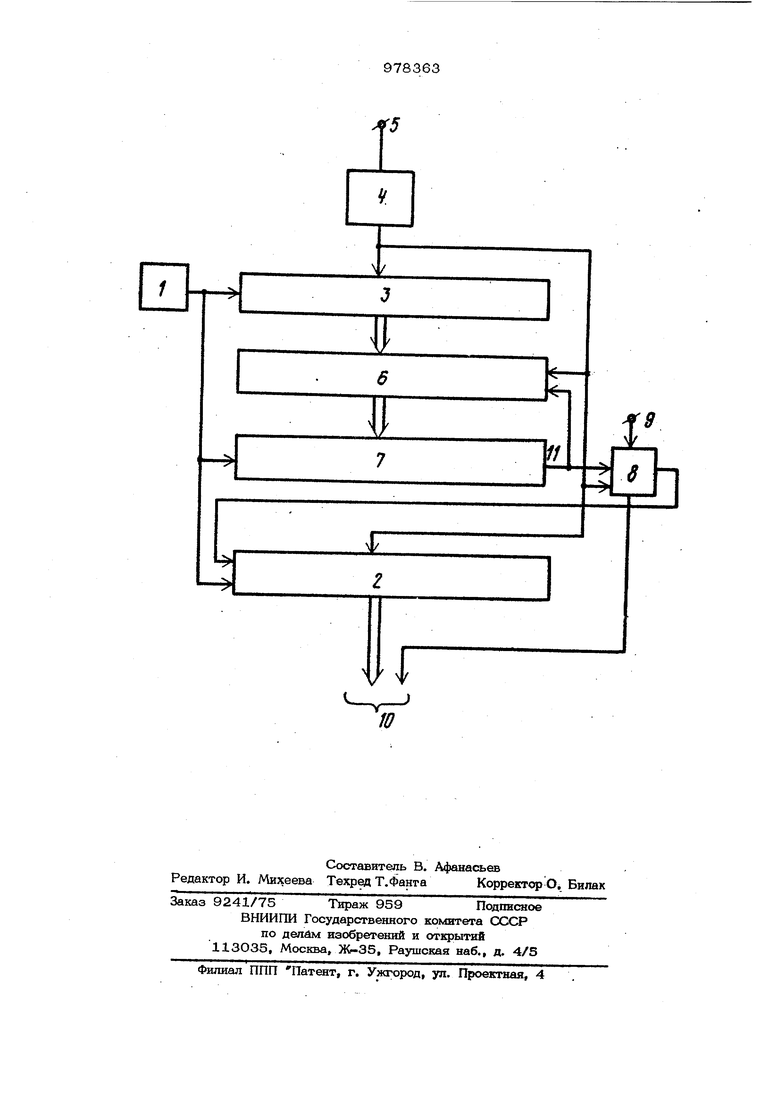

Наиболее близким к предлагаемому является устройство цифрового сопровоя дения фазы периодического сигнала, со15держащее последовательно соединенные генератор импульсов, измерительных счет чиков импульсов, регистр памяти, параллельный сумматор-накопитель, суммато р импульсных последовательностей, на вто20рой вход которого подключен выход генератора импульсов, и счетчик импульсов, выходы которого явпяются выходами ухггч ройства, а также содержащее детектор 397 нулей периодического сигнала, вход которого является входом устройства, а вы ход подключен к входам установки об&их счетчиков и входу управления регист ра памяти. При этом выход сумматора импульсных последовательностей соединен с входом стробирования параллельного сумматора-накопителя. Устройство обеспечивает точное цифровой обеспечение фазы периодического сигнала, в том числе и при значительных отклонениях частоты сопровождаемого периодического сигнала от основной частоты, на которое настроено устройст во. В конкретной реализации отклонение частот допустимо до 50% 23. Однако описанное устройство обладает пониженным быстродействием из-за принщтиального наличия в тракте прохождения сигнала сумматора импульсных последовательностей, работающего в 2тактном режиме. Следовательно, оно обладает и пониженной точностью сопровожудения фазы при высоких частотах сопровождаемого периодического сигнала. Целью изобретения шзляется повыщ&ние быстродействия и точности. Указанная цель достигается тем, что устройство цифрового сопровождепия фазы периодического сигнала, содержащее соединенные последовательно измеритель, лый счетчик импульсов, блок памя1И, параллельный сумматор-накопитель, а также счетчики импульсов, выход которого является выходом устройства, генератор импульсов, соединенный со. счетными входами обоих счетчиков и входом параллельного сумматора-накопителя, детектор нулей периодического сигнала, вход которого является входом устройства, а выход указанного детектора соединен с первым управлхпощим входом блока памяти и входами установки обоих счетчиков, снабм сно дополнительньтм разрядом параллель ного сумматора-накопителя, первый выход указанного дополнительного разряда является одним из выходов устройства, а второй выход дополнительного разряда соединен с третьим входом счетчика импульсов, при этом выход параллельного сумматора-накопителя соещшен с втбрым управляюшим входом блока памяти и первым входом дополнительного разряда, второй выход которого соедюсен с выходо детектора нулей периодического сигнала. На чертеже представлена схема предльгаемого устройства. Устройство цифрового сся1рово)кдення фазы периодического сигнала содержит 34 генератор 1 импульсов, выходной счетчик 2 импульсов, измерительный счетчик 3 импульсов, детектор 4 нулей периодического сигнала, вход 5 устройства, блок 6 памяти, параллельный сумматорнакопитель 7, дополнительный разряд 8 параллельного сумматора-накопителя, вход 9 дополнительного разряда, выход 10 устройства, шина 11 переноса с выхода параллельного сумматор(3-накопителя в дополнительный разряд. Устройство работает следующим образом. На вход 5 поступает периодический сигнал с периодом Т. Детектор 4 нулей при переходе сигнала через нуль от - к + вырабатывает импульс, по которому содержимое измерительного счетчика 3 импульсов записывается в блок 6 памяти, а затем измерительный счетчик 3 импульсов, выходной счетчик 2 импульсов и дополнительный разряд 8 сумматора-накопителя устанавливаются в начальное, в данном случае нулевое положение. Таким образом, в этот момент содержимое счетчиков 2 и 3 соответст- вует нулевому значению фазы периодического сигнала, а на выходе 10 устройства существует нулевое значение цифрового кода. Генератор 1 вырабатывает импульсную последовательность с частотой F, вырабатываемую исходя из разрядности измерительного счетчика 3 импульсов и допустимого отклонения периода Т входного сигнала так, чтобы при максимальном периоде входного сигнала счетчик 3 не бьш переполнен. В промежутке между импульсами установки измерительный счетчик продвигается частотой F. За период Т входного сигнала счетчик 3 принимает FT импульсов, В первый регистр блока 6 памяти число из счетчика 3 импульсов записывается в обратном коде, в результате i получается разность Д5--5-П, где - емкость счетчика 3. Одновременно по импульсу детектора 4 нулей в другой регистр блока 6 памяти зешисывается число 2-ikS (удвоенное значение разности). Это удвоение может быть сделано, например, путем сдвига входов второго регистра памяти на один разряд при подключении их к входу блока 6 памяти. Учитывая функциональную простоту операции удвоения значения двоичного числа и разнообразия возмож-. ных технических реализаций (например, сдвиг по входу, сдвиг в регистре, сдвиг по выходу, коммутация и т.д.), эта оп& рация в функциональную схему не введен Таким образом, после прихода импул иа с детектора 4 нулей в блоке памяти находится два числа & и 2д5. Импульсы частоты Р с выхода. ген&ратора 1 поступают на счетный вход счетчика 2 импульсов и стробирующий вход параллельного сумматора-накопителя 7. Одновременно на параллельный вход сумматора-накопителя 7, емкость которого равна емкости счетчика 3 импульсов, из блока 6 памяти подается двоичное число, равное рассогласованию. Следовательно, каждым импульсом частоты Р величина накопленной суммы в параллельном сумматоре-накопителе 7 увеличивается на Д5. В то же время на вход 9 дополнительного разряда 8 сумматора-накопителя постоянно подается единица. При непрерывном стробировании параллельного сумматора накопителя 7 дополнительный разряд 8 работает в режиме двоичного счетчика. Импульсы п&реноса из дополнительного разряда 8 поступают на второй вход {вход переноса) счетчика 2 импульсов, обеспечивая функционирование первого (младшего) разряда счетчика 2 импульсов в режиме второго разряда композиционного счетчика. Одновременно при непрерывном стробировании параллельного сумматорагакопителя 7 накопленная в нем сумма увеличивается. Наступает момент, когда йа шине 11 переноса в дополнительный разряд 8 появляется сигнал. Шина 11 подсоединена также к второму (адресному) входу блока 6 памяти. По сигналу переноса на выходах бло ка 6 образуется число 2л, которое . очередным строб-импульсом суммируется с содержимым сумматора-накопителя 7. При этом содержимое разрадов (кроме дополнительного разряда) сумматора-накопителя 7 переходит через нулевое значе1ше, сигнал переноса по шине 11 исче зает, и цикл заполнения параллельного сумматора-накопителя 7 возобновляется. Таким образом, при каждом переполнении сумматора-накопителя 7 в него дополнительно вводится число Л5, которое является начальным при последующем цикле его заполнения. При наличии остатка в момент переполнения исходной величиной является сумма остатка и Л& (В дальнейшем для упрощения понимания работы схемы описание дается без учета остатка). Количество импульсов, стробич рующих параллельный сумматор-накопи тель 7 в очередном цикле наполнения, равно ).. где cut - целая часть выражения, сто. ящего в скобках; 5- емкость параллельного сумматоранакопителя 7, без учета дополнительного разр5вда, после введения дополнительного (начального) числа ЛS. Период гаполнеия этих разрядов сумматора-накопителя 7 равен -г - гг ; 5F с учетом (1) Т --Т|й.5.(4) При этом общее количество циклов переполнения разрядов параллельного сумматора-накопителя 7 ( без дополнитель- , ного разряда 8) за период входного сипнала Т составляет К Т|Тд--Д5 Таким образом, на шине 11 переноса из параллельного сумматора-накопителя 7сигнала переноса за период Т образуется 5раз. Как показано выше, при подаче единицы на вход 9 дополнительного разрада 8сумматора-накопителя 7 этот разряд работает в режиме счетчика (при отсутствии сигнала переноса). Дополнительный разрад 8 и счетчик 2 вместе образуют композиционный счетчик, первым разряддом которого является дополнительный раэряд 8, а вторым - первый разрад счетчика 2 импульсол и т.д. Работая в режиме счетчика, за период Т этот композиционный счетчик принимает ( 5 - Л S) импульсов и на его параллельном выходе 1О образуется цифровая последовательность. При появлении сигнала переноса на шине 11 эта система перестает работать как счетчик, В момент появления стро&импульса из генератора 1 импульсов вследствие наличия сигнала переноса в дополнительный разряд 8, т.е. в младший разряд композиционного счетчика, добавляется единица. Счетчик делает скачок на дополнительную единицу, тем самым компенсируя накопленную ошибку сопровождения, т.е. синхронизируя значения цифровых сигналов выходной цифровой последовательности со значениями фазы сопровождаемого периодического сигнала. Количество скачков равно числу сигналов переноса в дополнительный разряд из параллельного сумматоранакопителя 7, так как равно Д9. Счедовательно, число на выходе 10 устройства не зависит от величины периода входного сигнала и частоты заполнени F при установившейся частоте входного сигнала. Темп поступления корректирующего сигйала из параллельного сумматора-на. копителя 7IB дополнительный разряд 8 обеспечивает точность цифрового сопровожде1шя фазы не хуже ±1 дискреты. Таким образом, на выходе 10 устройства формируется цифровая развертка, син ронизированная и совмещенная с началом и концом периода входного сигнала. Мгн венное значение этой развертки соответ ствует текущему значению фазы входного сигнала с погрещностью, не превышающей единицы младшего разряда устройства. Предлагаемое устройство работает в одногакгном режиме и позволяет по сравнению с прототипом использовать в два раза более высокую частоту стробирования F , что либо повышает в два раза точность соровождения, либо расширяет вдвое диапазон частот сопровождав мых сигналов. В рассмотренном примере реализации устройства детектор 4 нулей идентифицирует за период входного сигнала тбэлько одно известное зн&чение фазы - переход ,от - к . В этот момент значение фазы входного сигнала равно нулю. Для .некоторых периодических сигналов имеется возможность в течение периода идентифицировать несколько моментов, когда фаза входного сигнала точно известна. Например, для синусоидального периодического сигнала детектор нулей может легко идентифицировать переход сигнала как от - к +, так и от + к -, когда значение фазы входного сигнала равно 180°. В случае идентификации . нескольких известных точек фаз входного сигнала точность цифрового сопровождения предлагаемым устройством повышав ся, так как текущие погрешности интерполяции (внутри идентифицируемого периоца) и дискретизации уменьшаются. Нр для того, чтобы реализовать эту возможност даже для двух известных точек (от к + и от + к -) в предлагаемое устройство необходимо ввести дополнител ную аппаратуру, т.е. увеличить в 2 раза объем блока памяти, предусмотреть воэможность различной установки начального значения (О и 180 и т.д.). Устройство может быть реализовано на одной БИС. На предложенных принципах можно строить обладающие повышенной точностью и быстродействием цифровые узлы элек- тронншх и радиотехнических систем, синхронизатора, устройства фазовой обработки различных периодических сигналов. Фор м.у ла изобретения Устройство цифрового сопровождения фазы периодического сигнала, содержащее соединенные последовательно измерительный счетчик иivшyльcoв, блок памяти, параллельный сумматор-накопитель, а также счетчик импульсов, выход которого является выходом устройства, гене- ратор импульсов, соединенный со счетными входами обоих счетчиков и входом параллельного сумматора-накопителя, детектор нулей периодического сигнала, вход кото- рого является входом устройства, а выход указанного детектора соединен с nepvвым управляющим входом блока памяти и входами установки обоих счетчиков, отличающееся тем, что, с целью повышения быстродействия и точности, оно снабжено дополнительным разрядом параллельного сумматора-накопителя, первый выход указанного дополнительного разряда является одним из выходов устройства, а второй выход дополнительного разряда соединен с третьим входом счетчика импульсов, при этом выход параллельного сумматора-|Накопвьтеля соединен с вторым управляющим входом блока памяти и первым входом дополнительного разряда, второй вход которого соединен с выходом детектора нулей периодического сигнала. Источники информации, принятые во внимание при экспертизе 1.Цифровые электроизмерительные приборы. Под ред. Шляндина. М. Энергия, 1972, с. 92-151. 2.Авторское свидетельство СССР по заявке № 2794547/09, кл. НОЗЬ 7/00, 1979.

Авторы

Даты

1982-11-30—Публикация

1981-06-23—Подача