() УСТРОЙСТВО ЦИФРОВОГО СОПРОВОЖДЕНИЯ ФАЗЫ ПЕРИОДИЧЕСКОГО СИГНАЛА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цифрового сопровождения фазы периодического сигнала | 1981 |

|

SU978363A1 |

| Устройство цифрового сопровождения фазы периодического сигнала | 1985 |

|

SU1376241A2 |

| Устройство цифрового сопровождения фазы периодического сигнала | 1979 |

|

SU902266A1 |

| Цифровой преобразователь частоты | 1981 |

|

SU1054875A1 |

| Синтезатор частот | 1987 |

|

SU1417165A1 |

| Цифровой фазометр | 1980 |

|

SU932423A1 |

| Цифровой измеритель скорости перемещения | 1983 |

|

SU1165997A2 |

| Цифровой измеритель периода | 1978 |

|

SU771563A1 |

| Цифровой функциональный преобразователь | 1990 |

|

SU1751736A1 |

| СПОСОБ КОГЕРЕНТНОГО НАКОПЛЕНИЯ РАДИОИМПУЛЬСОВ | 2003 |

|

RU2293347C2 |

1

Изобретение относится к электронике и мо«ет быть использовано в регулирующих и управляющих устройствах электрических и радиотехнических систем для получения информации о мгновенном текущем значении фазы периодического сигнала.

Известно цифровое устройство для измерения мгновенных значений фазы периодически повторяющихся процессов, j содержащее соединенные последовательно генератор импульсов образцовой частоты и счетчик, а также детектор нулей периодического сигнала, вход которого является входом устройства, 5 а выход подключен к входу установки счетчика импульсов J.

Такое устройство формирует информацию о текущей фазе периодического процесса с высокой точностью и быст- 20 родействием, но обеспечивает, точность только при строгом взаимном соответствии образцовой частоты и частоты сопровождаемого периодического сигнала. Недостатком устройства является также резкое увеличение погрешности сопровождения при отклонении частоты периодического процесса от основной частоты, на которую настроено устройство.

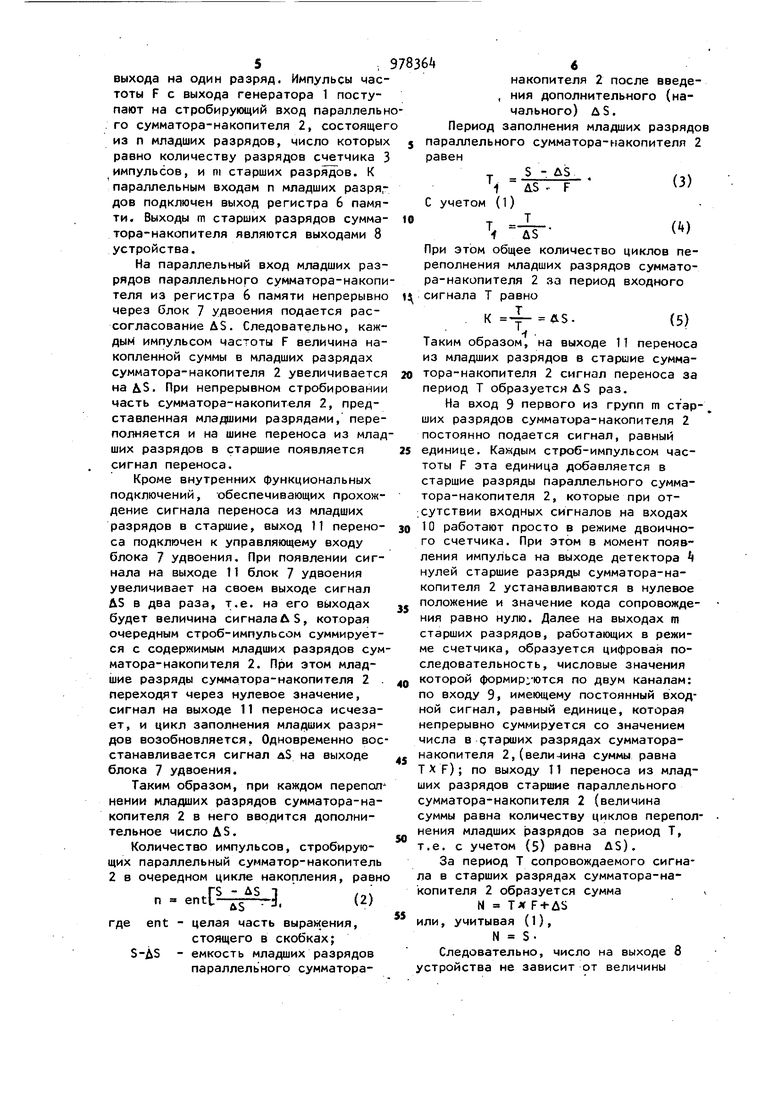

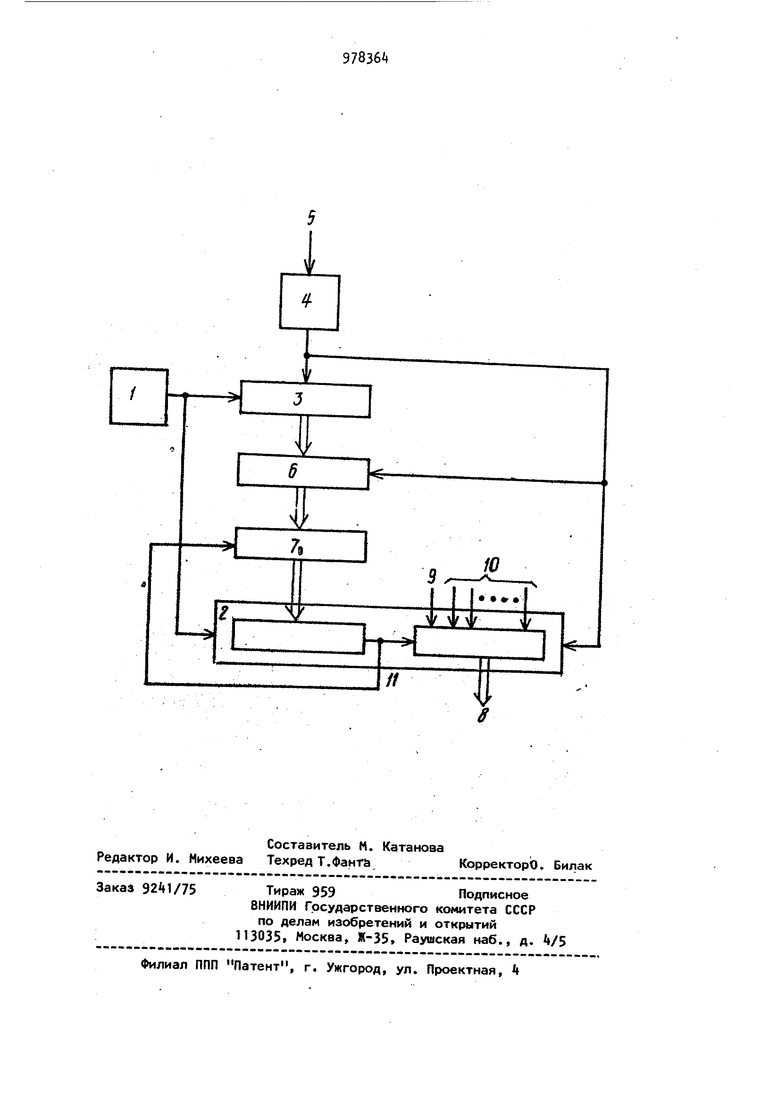

Наиболее близким к предлагаемому является устройство цифрового сопровождения фазы периодического сигнала ,. содержащее последовательно соединенные генератор импульсов, измерительный счетчик импульсов, регистр памяти, параллельный сумматор-накопитель, сумматор импульсных последовательностей, на второй вход которого подключен выход генератора импульсов, и счетчик импульсов, выходы которого являются выходами устройства, а также содержащее детектор нулей периодического сигнала, вход которого является входом устройства, а выход подключен к входам установки обоих счетчиков и входу управления регистра памяти. При этом выход сумма-. 3Э тора импульсных последовательностей соединен с входом стробирования параллельного сумматора-накопителя. Устройство обеспечивает точное цифровое сопровождение фазы периодического сигнала, в том числе и при значительных отклонениях частоты сопровождаемого периодического сигнала от о сновной частоты, на которую настроено устройство (в конкретной реа лизации отклонение частот допустимо до±50 о)Г. Однако описанное устройство обла, дает пониженным быстродействием изза принципиального наличия в тракте, прохождения сигнала сумматора импульсных последовательностей, работающего в 2-та1 товом режиме. Следовательно, оно обладает и пониженной точностью сопровождения фазы при высоких частотах сопровождаемого перио дического сигнала. Целью изoбpeteния является повышение быстродействия и точности, уст ройства. Поставленная цель достигается тем что в устройство цифрового сопровождения фазы периодического сигнала, с держащее параллельный сумматор-накопит„ель с п младшими и m старшими разрядами, соединенные последовательно измерительный счетчик импульсов и регистр пампти, генератор импульсов, выход которого подключен к входу измерительного счетчика импульсов и входу стробирования параллельного су матора-накопителя, детектор нулей пе риодического сигнала, вход которого соединен с выходной клеммой устройства, а выход - с входами установки измерительного счетчика импульсов и параллельного сумматора-накопителя и управляющим входом регистра памяти, введен блок удвоения, параллельный вход которого подключен к выходу регистра памяти, а выход подклюмен к параллельному входу п младших разрядов параллельного сумматора-накопите ля, при этом выход переноса из младших разрядов в старшие параллельного сумматора-накопителя подключен к управляющему входу блока удвоения, выход m старших разрядов параллельного сумматра-накопителя соединен с выход нь1ми клеммами устройства, а их параллельные входы - с клеммами дополнительных входов устройства. На чертеже показана схема устройства цифрового сопровождения фазы периодического сигнала. Устройство содержит генератор 1 импульсов, параллельный сумматор-накопитель 2, измерительный счетчик 3 импульсов, детектор k нулей периодического сигнала, вход 5 устройства, регистр б памяти, блок 7 удвоения, выход 8 устройства, вход 9 первого из m старших разрядов параллельного сумматора-накопителя, входы 10 других старших разрядов параллельного сумматора-накопителя, выход 11 переноса из младших разрядов в старшие параллельного сумматора-накопителя. Устройство работает следующим образом. На вход 5 поступает периодический сигнал с периодом Т. Детектор 4 нулей периодического сигнала при переходе сигнала через нуль от - к + вырабатывает импульс, по которому содержимое измерительного счетчика 3 импульсов записывается в регистр 6 памяти, а затем счетчик 3 устанавливается в начальное, в данном случае нулевое положение. Таким образом, в этот момент содержимое измерительного счетчика 3 соответствует нулевому значению фазы периодического сигнала. Генератор 1 импульсов вырабатывает импульсную последовательность с частотой F, выбираемой исходя из разрядности счетчика 3 импульсов и допустимого отклонения периода входного сигнала Т, так, чтобы при максимальном периоде входного сигнала измерительный счетчик 3 не был переполнен. 8 промежутке между импульсами установки счетчик 3 импульсов заполняется импульсами частоты F. Таким образом, за период Т входного сигнала счетчик 3 примет .РлТ импульсов. В регистр 6 памяти число из счетчика 3 записывается в обратном коде, в результате получается разность S - (1) где S - емкость счетчика 3. На выходе регистра 6 памяти включен блок 7 удвоения, который при отсутствии сигнала на своем входе управления просто транслирует число. AS на входы младших разрядов параллельного сумматора-накопителя 2. При появлении сигнала управления удвоения осуществляет удвоение величины сигнала рассогласования AS путем сдвига своих входов относительно 5, выхода на один разряд. Импульсы частоты F с выхода генератора 1 поступают на стробирующий вход параллельн го сумматора-накопителя 2, состоящег из п младших разрядов, число которых равно количеству разрядов счетчика 3 импульсов, и m старших разрядов. К параллельным входам п младших разрядов подключен выход регистра 6 памяти. Выходы m старших разрядов сумматора-накопителя являются выходами 8 устройства. На параллельный вход младших разрядов параллельного сумматора-накопи теля из регистра 6 памяти непрерывно через блок 7 удвоения подается рассогласование Д5. Следовательно, каждым импульсом частоты F величина накопленной суммы в младших разрядах сумматора-накопителя 2 увеличивается на AS. При непрерывном стробировании часть сумматора-накопителя 2, представленная младшими разрядами, переполняется и на шине переноса из млад ших разрядов в старшие появляется сигнал переноса. Кроме внутренних функциональных подключений, обеспечивающих прохождение сигнала переноса из младших разрядов в старшие, выход 11 переноса подключен к управляющему входу блока 7 удвоения. При появлении сигнала на выходе 11 блок 7 удвоения увеличивает на своем выходе сигнал Д5 в два раза, т.е. на его выходах будет величина сигналаЛЗ, которая очередным строб-импульсом суммируется с содержимым младших разрядов сум матора-накопителя 2. При этом младшие разряды сумматора-накопителя 2 . переходят через нулевое значение, сигнал на выходе 11 переноса исчезает, и цикл заполнения младших разрядов возобновляется, Одновременно вос станавливается сигнал д$ на выходе блока 7 удвоения. Таким образом, при каждом перепал нении младших разрядов сумматора-накопителя 2 в него вводится дополнительное число Д5. Количество импульсов, стробйрующих параллельный сумматор-накопитель 2 в очередном цикле накопления, равн . ent - целая часть выражения, стоящего в скобках; S-AS - емкость младших разрядов параллельного сумматора6накопителя 2 после введе, ния дополнительного (начального) Д5. Период заполнения младших разрядов параллельного сумматора-накопителя 2 равен S - Л5 . 1 Д5 . F С учетом (1) . ir- При этом общее количество циклов переполнения младших разрядов сумматора-накопителя 2 за период входного сигнала Т равно К .(5) Таким образом, на выходе 11 переноса из младших разрядов в старшие сумматора-накопителя 2 сигнал переноса за период Т образуется AS раз. На вход 9 первого из групп m стар- ших разрядов сумматора-накопителя 2 постоянно подается сигнал, равный единице. Кандым строб-импульсом частоты F эта единица добавляется в старшие разряды параллельного сумматора-накопителя 2, которые при отсутствии входных сигналов на входах 10 работают просто в режиме двоичного счетчика. При этом в момент появления импульса на выходе детектора i нулей старшие разряды сумматора-накопителя 2 устанавливаются в нулевое положение и значение кода сопровождения равно нулю. Далее на выходах m старших разрядов, работающих в режиме счетчика, образуется цифровая последовательность, числовые значения которой формируются по двум каналам: по входу 9, имеющему постоянный входной сигнал, равный единице, которая непрерывно суммируется со значением числа в старших разрядах сумматоранакопителя 2,(величина суммы равна Т X F); по выходу 11 переноса из младших разрядов старшие параллельного сумматора-накопителя 2 (величина суммы равна количеству циклов переполнения младших {зазрядов за период Т, т.е. с учетом (5) равна ДБ). За период Т сопровождаемого сигнала в старших разрядах сумматора-накопителя 2 образуется сумма N F-huS или, учитывая (1), N S. Следовательно, число на выходе 8 устройства не зависит от величины периода входного сигнала и 1 астоты заполнения при установившейся частоте входного сигнала. Темп поступления корректирующего воздействия из младших разрядов сумматора-накопителя 2 а старшие обеспечивает точность цифрового сопровождения фазы не хуже первого разряда m старших разрядов устройства. Таким образом, на выходе 8 устройства формируется цифровая развертка, синхронизированная и совмещенная с началом и концом периода входного сигнала. Мгновенное значение этой развертки соответствует текущему зна чению фазы входного сигнала с погрешностью, не превышающей единицы младшего разряда устройства. Предлагаемое устройство работает 9 однотактном режиме и позволяет по сравнению с прототипом использовать в два раза более высокую частоту стробирования, что повышает также в два раза или точность цифрового сопровождения, 1ли верхнюю границу частот сопровождаемого сигнала. Если на дополнительный вход 10 старших разрядов сумматора-накопителя 2 подать число К, то разовое подсуммирование числа К позволяет скачкообразно сдвигать на К значение выходного сигнала. Формула изоЬретения Устройство цифрового сопровождени фазы периодического сигнала, содержа щее параллельный сумматор-накопитель с п младшими и m старшими разрядами соединенные последовательно измерительный счетчик импульсов и регистр памяти, генератор импульсов, выход которого соединен с входом измерительного счетчика импульсов и .входом стробирования параллельного сумматоранакопителя, детектор нулей перио- дического сигнала, вход которого соединен с входной клеммой устройства, а выход - с входами установки измерительного счетчика импульсов, параллельного сумматора-накопителя и управляющим входом регистра памяти, отличающееся тем, что, с целью повышения быстродействия и точности, в него введены блок удвоения, параллельный вход которого соединен с выходом регистра памяти, а выход с параллельным входом п млаших разрядов параллельного сумматора-накопителя, при этом выход переноса из мяадших разрядов в старшие разряды параллельного сумматора-накопителя соеди-. нен с управляющим входом блока удвоения, выходы m старших разрядов параллельного сумматора-накопителя соединены .с выходными клеммами устройства, а их параллельные входы соединены с клеммами дополнительных входов устройства. Источники информации, принятые во внимание при экспертизе 1.Шляндин С.М. Цифровые электроизмерительные приборы. М., Энергия, 197, с. 126. 2.Авторское свидетельство СССР по заявке № , кл. Н 03 L 7/00, 1Э79.

6

Ф УАУ F

ьч

//

Авторы

Даты

1982-11-30—Публикация

1981-06-23—Подача