(5) УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ ОТ ДАТЧИКОВ ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поиска дефектов дискретных блоков | 1990 |

|

SU1714610A1 |

| Устройство для сбора,обработки и отражения информации | 1972 |

|

SU451997A1 |

| Устройство для считывания информации с перфоносителя | 1986 |

|

SU1388914A1 |

| Устройство для генерирования кодов заданного веса | 1985 |

|

SU1275413A1 |

| Устройство для моделирования дискретных систем | 1985 |

|

SU1295411A1 |

| Устройство для управления многоканальной измерительной системой | 1983 |

|

SU1149255A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1476466A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Генератор случайных чисел | 1983 |

|

SU1124294A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

1

Изобретение относится к вычислительной технике и может быть исполь-. зовано для ввода двоичных сигналов от датчиков в устройство последовательной обработки информации типа программно-логического регулятора.

Известно устройство для последовательного опроса иctoчникoв информации , содержащее узлы выбора каналов, коммутатор источников, коммутатор приемников, триггеры, элементы И, НЕ, ИЛИ, ИЛИ-НЕ 1 .

Недостатком такого устройства является аппаратурная сложность.

Наиболее близким к предлагаемому техническому решению является многоканальное устройство ввода информации.

Известное устройство содержит генератор тактовых импульсов, счетчик и коммутатор. Первый выход гене-, ратора тактовых импульсов соединен с входом счетчика. Выход счетчика соединен с адресными входами запоминающего блока и коммутатора, информационные входы которого соединены с входами устройства, а выход коммутатора через линию связи соединен с информационным входом запоминающего блока, вход синхронизации которого соединен с вторым выходом генератора тактовых импульсов.

Работа известного устройства про,Q исходит следукмцим Ьбразом.

В каждом такте импульс с первого выхода тактового-генератора увеличивает содержимое счетчика на единицу, что вызывает прохождение на вход комJ5 мутатора сигнала с того входа устройства, номер которого соответствует содержимому счетчика. Этот сигнал поступает на информационный вход запоминающего блока. Затем импульс

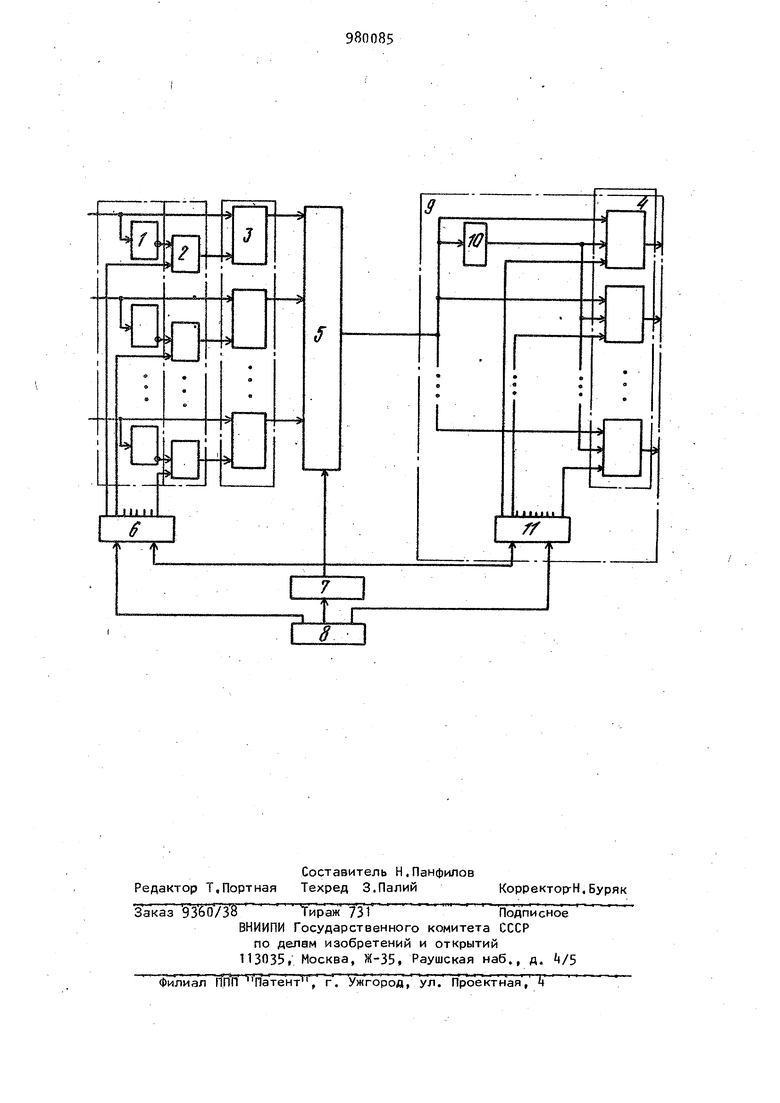

20 с второго выхода тактового генератора, задержанный относительно импульса с первого выхода генератора, поступает на вход синхронизации запоминающего блока, и сигнал с выхода 3 9 коммутатора записывается в ту ячейку запоминающего блока, адрес которой соответствует содержимому счетчика. В следующем такте аналогичным образом осуществляется передача сигнала со следующего по номеру входа устройства в соответствующую ячейку за пo 4 нaющeгo блока на приемной сторо не. Опрос входов устройства осуществляется последовательно в циклическом режиме,Г. J. Недостатком известного устройства является необходимость выполнения требования, чтобы длительность сигнала на каждом входе устройства была не менее длительности цикла. В противном случае этот сигнал может быть пропущен при опросе входов и не передан на приемную сторону Цель изобретения - повышение надежности устройства за счет исключения пропуска сигналов с малой дли тельностью Поставленная цель достигается тем, что в устройство для ввода информации от датчиков, содержащее генератор тактовых импульсов, комму татор, первый вход которого соединен с выходом счетчика и первым вхо дом первого дешифратора, второй вхо которого соединен с. первым выходом генератора тактовых импульсов, а выходы первого дешифратора соединен с первыми входами триггеров первой группы, вторые входы которых соедииены с выходом элемента НЕ, вход по следнего соединен с третьими входами триггеров первой группы и выходо коммутатора, выходы триггеров первой группы являются выходами устрой ства, введены группа элементов НЕ, вторая группа триггеров, элемент И и дешифратор, первый и второ входы которого соединены соответ ственно с выходом счетчика и вторым выходом генератора тактовых импульсов, входы коммутатора соединены с выходами триггеров второй группы, первые входы которых соединены с . входами элементов НЕ группы и являются входами устройства, вторые вхо ды триггеров соединены с выходами элементов И первые входы которых соединены с выходами второго дешифратора, а вторые входы соедине ны с выходами элементоы НЕ гру пы. На чертеже приведена схема устройства, Устройство для ввода информации содержит группу элементов НЕ 1, элементы И 2, первую группу 3 триггеров, вторую группу k триггеров, коммутатор 5« дешифратор 6, счетчик 7, генератор 8 тактовых импульсов и блок 9 памяти, элемент НЕ 10, второй дешифратор 11. Работа устройства происходит следующим образом„. Появляющийся на любом.и.з входов устройства сигнал ( независимо от того, потенциальный он или импульсный устанавливает в единичное состояние соответствующий триггер в группе 3, при этом длительность импульсного сигнала может быть достаточно малой, ограниченной тодько величиной, достаточной для срабатывания триггера. Опрос входов происходит последовательно в циклическом режиме по сигналам, формируемым на первом выходе генератора 8 тактовых импульсов. Адрес опрашиваемого входа задается содержимым счетчика 7, код с выхода которого подается на адресные входы коммутатора 5, дешифраторов-6 и 11. По заданному адресу коммутатор 5 подключает к линии связи требуемый выход, и сигнал с этого выхода поступает на информационный вход блока 9 памяти, связанный с первыми входами триггера группы t непосредственно и с вторыми входами триггеров группы через элемент НЕ 10. Импульс с второго выхода генератора 8, задержанный, по времени относительно импульса с первого выхода, поступая на вход синхронизации блока 9 памяти, стробирует дешифратор 11, благодаря чему на соответствующем выходе, дешифратора 11 появляется сигнал, поступающий на синхронизирующий вход того из триггеров группы, который соответствует опрашиваемому входу. Если на информационном входе блока 9 памяти имеет место логическая М, то соответствующий триггер группы устанавливается в единичное состояние по второму входу. Опрос остальных входов и передача сигналов с них осуществляется аналогичным образом, причем после опроса всех входов цикл повторяется. При появлении сигнала на одном входов он фиксируется соответстизвующим триггером группы 3 и будет передан в блок 9 памяти, либо в текущем, либо в следующем цикле опро са. Если к моменту очередного опро са сигнал на данном входе закончил ся, то на первом входе соответствующего элемента И появляется разрешающий потенциал. Импульс с третьего выхода генератора 8, задержанный относительно импульса с второго выхода генератора 8, стробирует дешифратор 6, сигнал с выхода которого через элемент И 2 сбрасывает соответствующий триггер группы 3 в нулевое состояние. Таким образом, возможна передача даже очень коротких импульсов, так как триггеры группы 3 растягивают их длительность до момента очередиого опроса„ Предлагаемое техническое решение позволяет повысить надежность функционирования устройства за счет исключения пропуска сигналов малой длительности при опросе его входов Это, в свою очередь, исключает потерю, сигналов на входе устройства обработки и препятствует тем самым формированию неправильных, команд управления на управляемую систему, что могло бы нарушить режим ее работы или привести.к аварийной ситуации . Формула изобретения Устройство для ввода информации от датчиков, содержащее генератор тактовых импульсов, коммутатор, пер 856 вый вход которого соединен с выходом счетчика и первым входом первого дешифратора, второй вход которого соединен с первым выходом генератора тактовых импульсов, а выходы .первого дешифратора,соединены с первыми входами триггеров первой группы, вторые входы которых соединены с вы,ходом элемента НЕ, вход поспеднего соединен с третьими входами трй1- геров первой группы и выходом коммутатора, выходы триггеров первой группы являются выходами устройства, отличающееся тем, что, с цепью повышения надежности, в него введены группа элементов НЕ, вторая группа триггеров, элемент И и второйдешифратор,, первый и второй входы которого соединены соответственно с выходом счетчика и вторым выходом генератора тактовых импульсов, входы коммутатора соединены с выходами триггеров второй группы, первые входы которых соединены с входами элементов НЕ группы и являются входами устройства, вторые входы триггеров соединены с выходами элементов И, первые входы которых соединены с выходами второго дешифратора, а вторые входы -соединены с выходами элементов НЕ группы., Источники информации, принятые во внимание при экспертизе 1« Авторское свидетельство СССР № 792253, кл. G 06 F , 1978. 2. Патент Японии № 51-37 98, кл. G Об F 9/18, опублик, 1976 (прототип).

Авторы

Даты

1982-12-07—Публикация

1981-06-12—Подача