4 О

О

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Устройство для поиска дефектов дискретных блоков | 1985 |

|

SU1379784A1 |

| Устройство для диагностирования дискретных блоков | 1986 |

|

SU1520516A1 |

| Устройство для поиска дефектов цифровых блоков | 1987 |

|

SU1520519A1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Устройство для тестового контроля цифровых блоков | 1983 |

|

SU1149779A1 |

| Устройство для поиска дефектов цифровых узлов | 1985 |

|

SU1302282A2 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1278855A1 |

| Устройство для контроля и диагностики дискретных блоков | 1985 |

|

SU1254488A1 |

| Устройство для контроля параллельных микропроцессорных интерфейсов | 1982 |

|

SU1040489A1 |

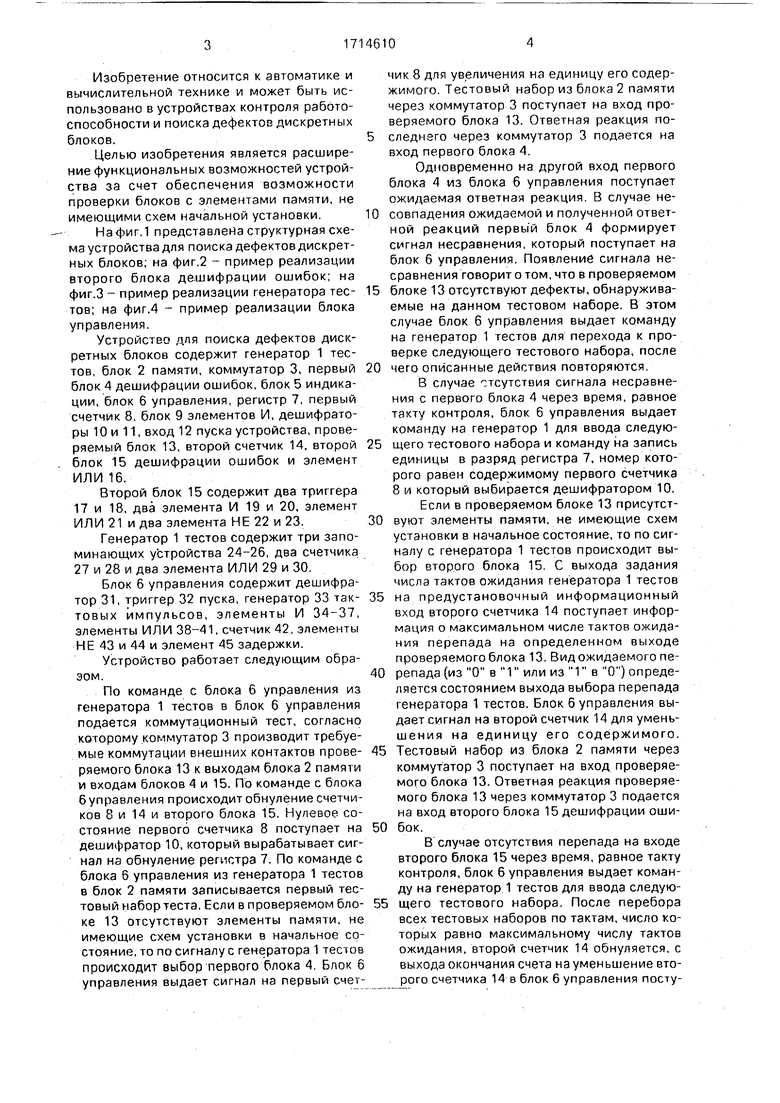

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах контроля работоспособности и поиска дефектов дискретных блоков. Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения возможности проверки блоков с элементами памяти, не имеющими схем начальной установки. Устройство для поиска дефектов дискретных блоков содержит генератор 1 тестов, блок 2 памяти, коммутатор 3. блок 4 дешифрации ошибок, блок 5 индикации, блок 6 управления, регистр 7. первый счетчик 8, блок 9 элементов И. дешифраторы 10 и 11.вход 12 пуска устройства, проверяемый блок. 13, второй счетчик 14. второй блок 15 дешифрации ошибок, элемент ИЛИ 16. 4 ил.(Лс

Фие.1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах контроля работоспособности и поиска дефектов дискретных блоков.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения возможности проверки блоков с элементами памяти, не имеющими схем начальной установки.

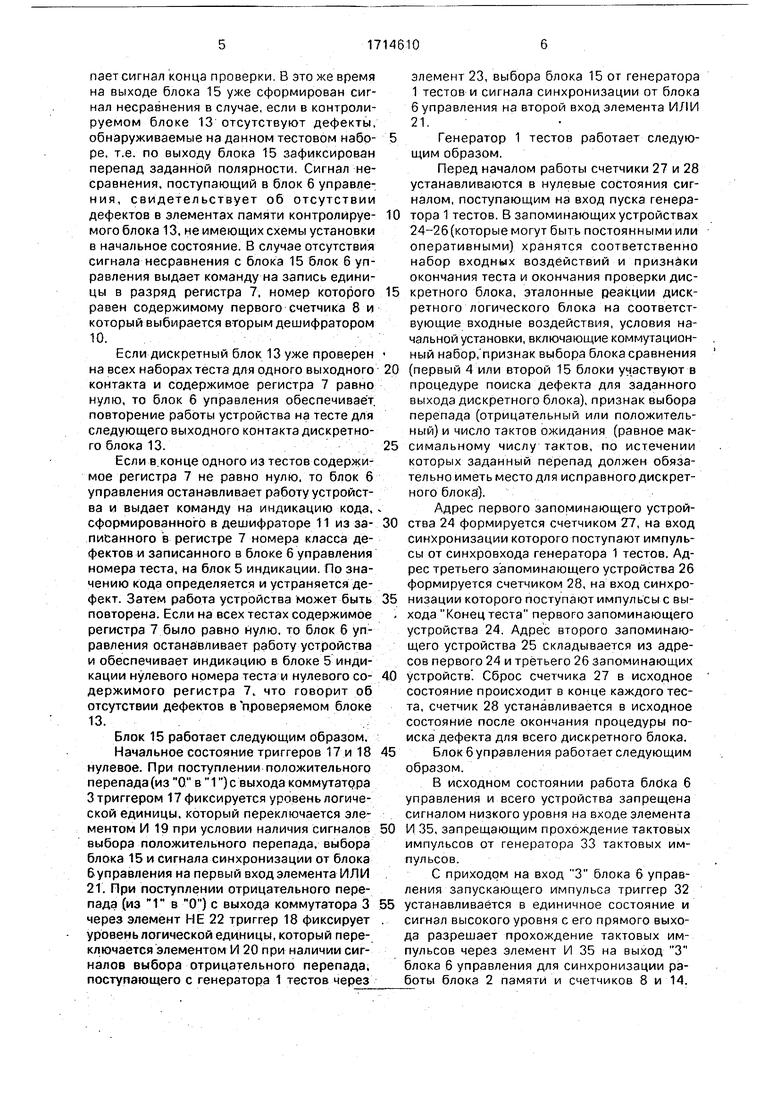

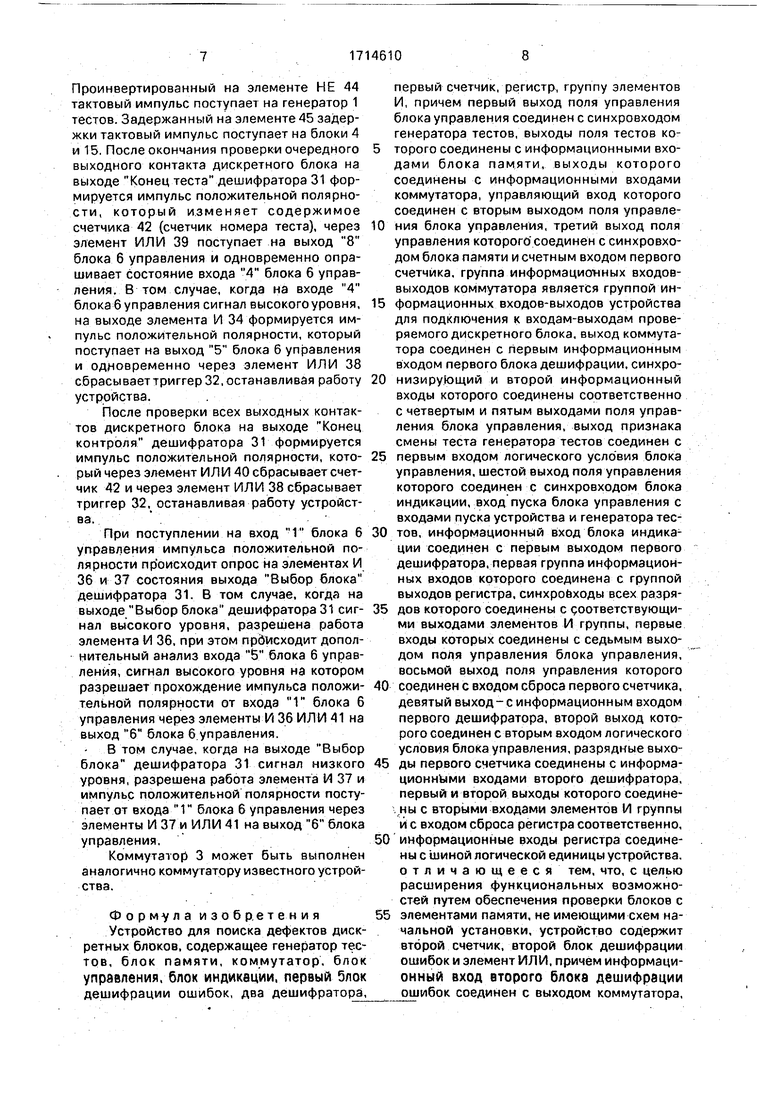

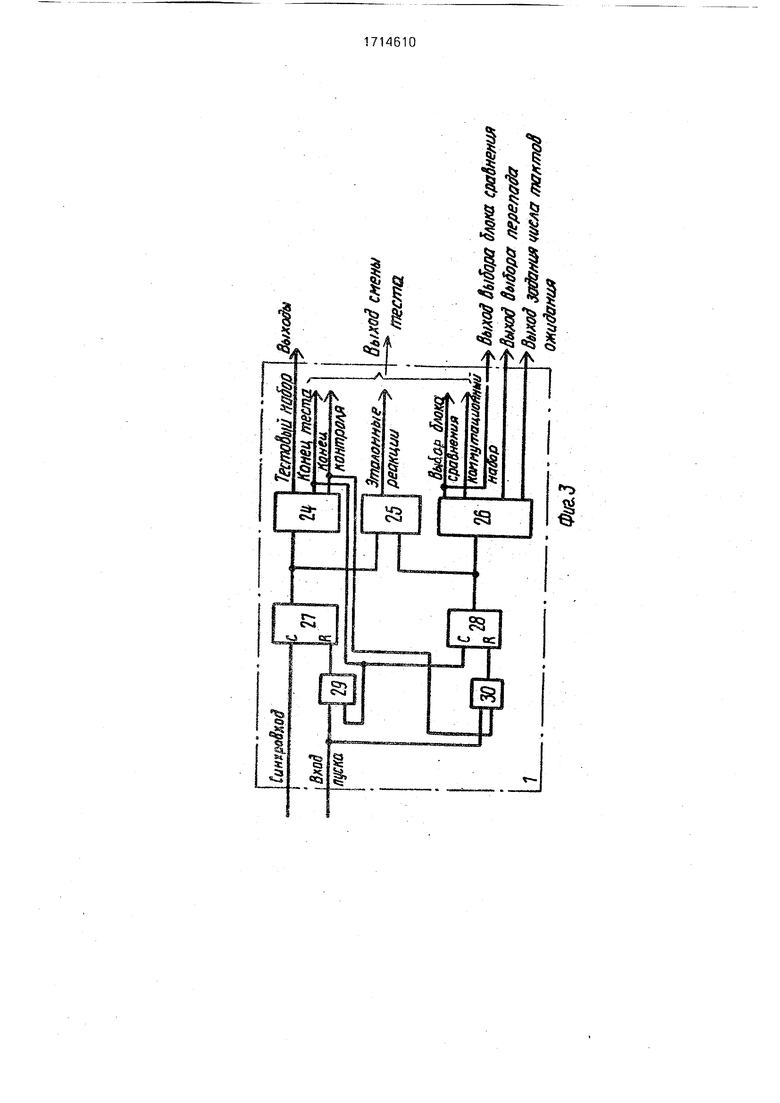

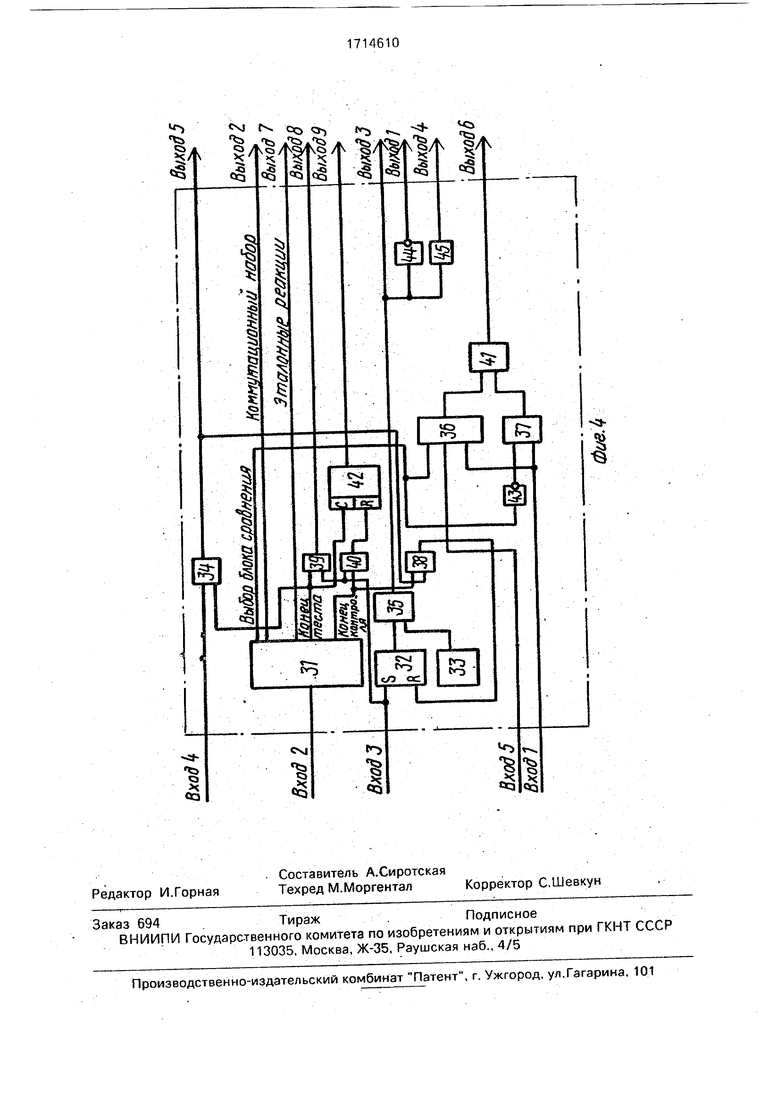

Нафиг,1 представлена структурная схема устройства для поиска дефектов дискретных блоков; на фиг.2 - пример реализации второго блока дешифрации ошибок; на фиг.З - пример реализации генератора тестов; на фиг.4 - пример реализации блока управления.

Устройство для поиска дефектов дискретных блоков содержит генератор 1 тестов, блок 2 памяти, коммутатор 3, первый блок 4 дешифрации ошибок, блок 5 индикации, блок 6 управления, регистр 7, первый счетчик 8, блок 9 элементов И. дешифраторы 10 и 11, вход 12 пуска устройства, проверяемый блок 13, второй счетчик 14. второй блок 15 дешифрации ошибок и зламент ИЛИ 16.

Второй блок 15 содержит два триггера 17 и 18, два элемента И 19 и 20, элемент ИЛИ 21 и два элемента НЕ 22 и 23.

Генератор 1 тестов содержит три запоминающих устройства 24-26, два счетчика 27 и 28 и два элемента ИЛИ 29 и 30.

Блок 6 управления содержит дешифратор 31, триггер 32 пуска, генератор 33 тактовых импульсов, элементы И 34-37, элементы ИЛИ 38-41, счетчик 42, элементы НЕ 43 и 44 и элемент 45 задержки.

Устройство работает следующим образом.

По команде с блока 6 управления из генератора 1 тестов в блок 6 управления подается коммутационный тест, согласно которому коммутатор 3 производит требуемые коммутации внешних контактов проверяемого блока 13 к выходам блока 2 памяти и входам блоков 4 и 15. По команде с блока 6управления происходит обнуление счетчиков 8 и 14 и второго блока 15. Нулевое состояние первого счетчика 8 поступает на дешифратор 10, который вырабатывает сигнал на обнуление регистра 7. По команде с блока 6 управления из генератора 1 тестов в блок 2 памяти записывается первый тестовый набор теста. Если в проверяемом блоке 13 отсутствуют элементы памяти, не имеющие схем установки в начальное состояние, то по сигналу с генератора 1 тестов происходит выбор первого блока 4, Блок 6 управления выдает сигнал на первый счетчик 8 для увеличения на единицу его содержимого. Тестовый набор из блока 2 памяти через коммутатор 3 поступает на вход проверяемого блока 13. Ответная реакция последнего через коммутатор 3 подается на вход первого блока 4.

Одновременно на другой вход первого блока 4 из блока 6 управления поступает ожидаемая ответная реакция. В случае несовпадения ожидаемой и полученной ответной реакций первый блок 4 формирует сигнал несравнения, который поступает на блок 6 управления. Появление сигнала несравнения говорит о том, что в проверяемом

5 блоке 13 отсутствуют дефекты, обнаруживаемые на данном тестовом наборе. В этом случае блок 6 управления выдает команду на генератор 1 тестов для перехода к проверке следующего тестового набора, после

0 чего описанные действия повторяются.

В случае отсутствия сигнала несравнения с первого блока 4 через время, равное такту контроля, блок 6 управления выдает команду на генератор 1 для ввода следую5 щего тестового набора и команду на запись единицы в разряд регистра 7. номер которого равен содержимому первого счетчика 8 и который выбирается дешифратором 10. Если в проверяемом блоке 13 присутствуют элементы памяти, не имеющие схем установки в начальное состояние, то по сигналу с генератора 1 тестов происходит выбор второго блока 15. С выхода задания числа тактов ожидания генератора 1 тестов

5 на предустановочный информационный вход второго счетчика 14 поступает информация о максимальном числе тактов ожидания перепада на определенном выходе проверяемого блока 13. Вид ожидаемого перепада (из О в 1 или из 1 в О) определяется состоянием выхода выбора перепада генератора 1 тестов. Блок 6 управления выдает сигнал на второй счетчик 14 для уменьшения на единицу его содержимого.

5 Тестовый набор из блока 2 памяти через коммутатор 3 поступает на вход проверяемого блока 13. Ответная реакция проверяемого блока 13 через коммутатор 3 подается на вход второго блока 15 дешифрации оши0 бок.

В случае отсутствия перепада на входе второго блока 15 через время, равное такту контроля, блок 6 управления выдает команду на генератор 1 тестов для ввода следующего тестового набора. После перебора всех тестовых наборов по тактам, число которых равно максимальному числу тактов ожидания, второй счетчик 14 обнуляется, с выхода окончания счета на уменьшение второго счетчика 14 в блок 6 управления поступает сигнал конца проверки. В это же время на выходе блока 15 уже сформирован сигнал несравнения в случае, если в контролируемом блоке 13 отсутствуют дефекты, обнаруживаемые на данном тестовом наборе, т.е. по выходу блока 15 зафиксирован перепад заданной полярности. Сигнал несравнения, поступающий в блок 6 управления, свидетельствует об отсутствии дефектов в элементах памяти контролируемого блока 13. не имеющих схемы установки в начальное состояние. В случае отсутствия сигнала несравнения с блока 15 блок 6 управления выдает команду на запись единицы в разряд регистра 7. номер которого равен содержимому первого счетчика 8 и который выбирается вторым дешифратором 10. Если дискретный блок 13 уже проверен на всех наборах теста для одного выходного контакта и содержимое регистра 7 равно нулю, то блок 6 управления обеспечивает, повторение работы устройства на тесте для следующего выходного контакта дискретного блока 13. Если в.конце одного из тестов содержимое регистра 7 не равно нулю, то блок 6 управления останавливает работу устройства и выдает команду на индикацию кода, сформированного в дешифраторе 11 из записанного в регистре 7 номера класса дефектов и записанного в блоке 6 управления номера теста, на блок 5 индикации. По значению кода определяется и устраняется дефект. Затем работа устройства может быть повторена. Если на всех тестах содержимое регистра 7 было равно нулю, то блок 6 управления останавливает работу устройства и обеспечивает индикацию в блоке 5 индикации нулевого номера теста и нулевого содержимого регистра 7, что говорит об отсутствии дефектов в проверяемом блоке 13. Блок 15 работает следующим образом. Начальное состояние триггеров 17 и 18 нулевое. При поступлении положительного перепада(из О в 1)с выхода коммутатора 3 триггером 17 фиксируется уровень логической единицы, который переключается элементом И 19 при условии наличия сигналов выбора положительного перепада, выбора блока 15 и сигнала синхронизации от блока &управления на первый вход элемента ИЛИ 21. При поступлении отрицательного перепада (из 1 в О) с выхода коммутатора 3 через элемент НЕ 22 триггер 18 фиксирует уровень логической единицы, который переключается элементом И 20 при наличии сигналов выбора отрицательного перепада, поступающего с генератора 1 тестов через элемент 23, выбора блока 15 от генератора 1 тестов и сигнала синхронизации от блока 6 управления на второй вход элемента И/1И 21. Генератор 1 тестов работает следующим образом. Перед началом работы счетчики 27 и 28 устанавливаются в нулевые состояния сигналом, поступающим на вход пуска генератора 1 тестов. В запоминающих устройствах 24-26(которые могут быть постоянными или оперативными) хранятся соответственно набор входных воздействий и признаки окончания теста и окончания проверки дискретного блока, эталонные реакции дискретного логического блока на соответствующие входные воздействия, условия начальной установки, включающие коммутационный набор.признак выбора блока сравнения (первый 4 или второй 15 блоки участвуют в про.цедуре поиска дефекта для заданного выхода дискретного блока), признак выбора перепада (отрицательный или положительный) и число тактов ожидания (равное максимальному числу тактов. п.о истечении которых заданный перепад должен обязательно иметь место для исправногодискретного блока). Адрес первого запоминающего устройства 24 формируется счетчиком 27. на вход синхронизации которого поступают импульсы от синхровхода генератора 1 тестов. Адрес третьего запоминающего устройства 26 формируется счетчиком 28, на вход синхронизации которого поступают импульсы с выхода Конец теста первого запоминающего устройства 24. Адрес второго запоминающего устройства 25 складывается из адресов первого 24 и третьего 26 запоминающих устройств . Сброс счетчика 27 в исходное состояние происходит в конце каждого теста, счетчик 28 устанавливается в исходное состояние после окончания процедуры поиска дефекта для всего дискретного блока. Блок 6 управления работает следующим образом. В исходном состоянии работа блока 6 управления и всего устройства запрещена сигналом низкого уровня на входе элемента И 35. запрещающим прохождение тактовых импульсов от генератора 33 тактовых импульсов. С приходом на вход 3 блока 6 управения запускающего импульса триггер 32 станавливается в единичное состояние и игнал высокого уровня с его прямого выхоа разрешает прохождение тактовых импульсов через элемент 1/1 35 на выход 3 блока 6 управления для синхронизации работы блока 2 памяти и счетчиков 8 и 14.

Проинвертированный на элементе НЕ 44 тактовый импульс поступает на генератор 1 тестов. Задержанный на элементе 45 задержки тактовый импульс поступает на блоки 4 и 15. После окончания проверки очередного выходного контакта дискретного блока на выходе Конец теста дешифратора 31 формируется импульс положительной полярности, который изменяет содержимое счетчика 42 (счетчик номера теста), через элемент ИЛИ 39 поступает на выход 8 блока б управления и одновременно опрашивает состояние входа 4 блока 6 управления. В том случае, когда на входе 4 блока б управления сигнал высокого уровня, на выходе элемента И 34 формируется импульс положительной полярности, который поступает на выход 5 блока б управления и одновременно через элемент ИЛИ 38 сбрасывает триггер 32, останавливая работу устройства.

После проверки всех выходных контактов дискретного блока на выходе Конец контроля дешифратора 31 формируется импульс положительной полярности, который через элемент ИЛИ 40 сбрасывает счетчик 42 и через элемент ИЛИ 38 сбрасывает триггер 32, останавливая работу устройства.

При поступлении на вход 1 блока б управления импульса положительной полярности происходит опрос на элементах И 36 и 37 состояния выхода Выбор блока дешифратора 31. В том случае, когда на выходе Выбор блока дешифратора 31 сигнал высокого уровня, разрешена работа элемента И 36, при этом происходит дополнительный анализ входа 5 блока б управления, сигнал высокого уровня на котором разрешает прохождение импульса положительной полярности от входа 1 блока б управления через элементы И 36 ИЛИ 41 на выход б блока б управления. - В том случае, когда на выходе Выбор блока дешифратора 31 сигнал низкого уровня, разрешена работа элемента И 37 и импульс положительной полярности поступает от входа Г блока б управления через элементы И 37 и ИЛИ 41 на выход б блока управления.

Коммутатор 3 может быть выполнен аналогично коммугатору известного устройства.

Ф о рм п а изобретения Устройство для поиска дефектов дискретных блоков, содержащее генератор тестов, блок памяти, коммутатор, блок управления, блок индикации, первый блок дешифрации ошибок, два дешифратора.

первый счетчик, регистр, группу элементов И, причем первый выход поля управления блока управления соединен с синхровходом генератора тестов, выходы поля тестов которого соединены с информационными входами блока памяти, выходы которого соединены с информационными входами коммутатора, управляющий вход которого соединен с вторым выходом поля управления блока управления, третий выход поля управления которогосоединен с синхровходом блока памяти и счетным входом первого счетчика, группа информационных входоввыходов коммутатора является группой информационных входов-выходов устройства для подключения к входам-выходам проверяемого дискретного блока, выход коммутатора соединен с первым информационным входом первого блока дешифрации, синхро0 низируИэщий и второй информационный входы которого соединены соответственно с четвертым и пятым выходами поля управления блока управления, выход признака смены теста генератора тестов соединен с

5 первым входом логического условия блока управления, шестой выход поля управления которого соединен с синхровходом блока индикации, вход пуска блока управления с входами пуска устройства и генератора тестов, информационный вход блока индикации соединен с первым выходом первого дешифратора, первая группа информационных входов которого соединена с группой выходов регистра, синхробходы всех разрядов которого соединены с соответствующими выходами элементов И группы, первые входы которых соединены с седьмым выходом поля управления блока управления, восьмой выход поля управления которого

0 соединен с входом сброса первого счетчика, девятый выход-с информационным входом первого дешифратора, второй выход которого соединен с вторым входом логического условия блока управления, разрядные выходы первого счетчика соединены с информационными входами второго дешифратора, первый и второй выходы которого соедине.,ны с вторыми входами элементов И группы и с входом сброса регистра соответственно,

0 информационные входы регистра соединены с шиной логической единицы устройства, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения проверки блоков с

5 элементами памяти, не имеющими схем начальной установки, устройство содержит второй счетчик, второй блок дешифрации ошибок и элемент ИЛИ, причем информационный ВХОД второго блока дешифрации ошибок соединен с выходом коммутатора.

вход синхронизации - с четвертым выходом поля управления блока управления, третий вход логического условия которого соединен с выходом элемента ИЛИ, первый и второй входы которого соединены с выходами первого и второго блоков дешифрации ошибок соответственно, вход сброса второго счетчика соединен с восьмым выходом поля управления блока управления и соединен с входом блокировки второго блока дешифрации ошибок, четвертый вход логиче; CKOlO условия блока управления соединен с

ftnfi.3

ОтШ

9К

Jf0.J

и

гъ

18

6tnSA,l

23ФЬш

выходом заема второго счетчика, информационный вход которого соединен с выходами поля задания числа тактов ожидания генератора тестов, выход выбора перепада которого соединен с вторым информационным входом второго блока дешифрации ошибок, сметный вход второго счетчика соединен с третьим выходом поля управления блока управления, входы разрешения первого и второго блоков дешифрации ошибок 0с выходом режима контроля генератора те стов.

19

KSK.16

21

20

Фиг: г

| Устройство для поиска дефектов цифровых узлов | 1980 |

|

SU962957A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-02-23—Публикация

1990-05-14—Подача