(54) УСТРОЙСТВО для КОНТРОЛЯ РАСПРЕДЕЛИТЕЛЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного выбора асинхронных сигналов | 1984 |

|

SU1215113A1 |

| Устройство для контроля мажоритарных блоков | 1981 |

|

SU1015389A1 |

| Устройство для контроля распределителя | 1982 |

|

SU1057960A1 |

| Резервированный делитель частоты | 1979 |

|

SU822375A1 |

| Устройство для контроля работы счетчика с потенциальными выходами | 1978 |

|

SU750738A1 |

| Устройство для контроля счетчика | 1980 |

|

SU884148A1 |

| Устройство для контроля счетчиков | 1977 |

|

SU741268A2 |

| Устройство для передачи и приема информации | 1982 |

|

SU1037318A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1608672A1 |

| Преобразователь последовательного кода в параллельный | 1986 |

|

SU1383508A1 |

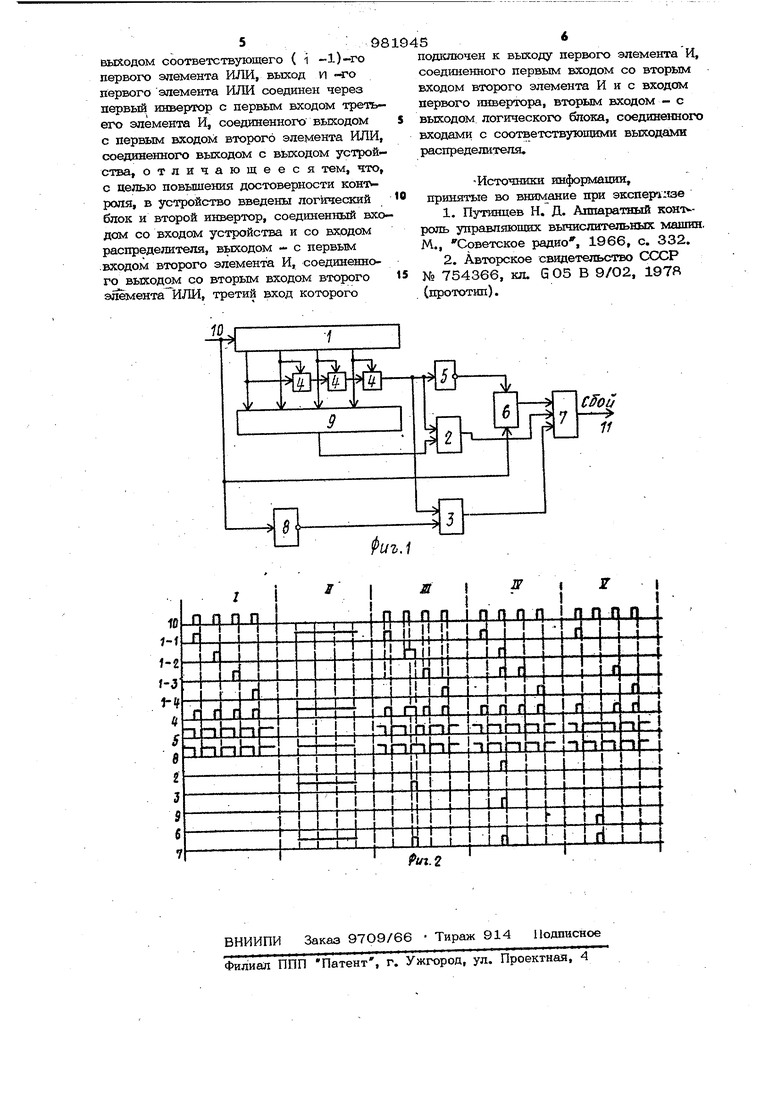

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля распределителей импульсов. Известно устройство для контроля распределителя, содержащее сумматор по модулю два 1 . Однако устройство не обеспечивает обнаруяшние неисправности в виде зави ния распределителя в некотором одном состоянии, когда выходной импульс распределителя имеет длительнрстъ большую чем входной синхроимпульс. Наиболее близким техническим решением к изобретению япвляется устройство для контроля распределителя, содерзкаще элементы ИЛИ, И, инвертор и триггер , Недостатком известного устройства является недостаточаьая достоверность контроля за счет тсяго, что оно не формирует сигнал неисправности если на однсад из выходов распредеш теля (в процессе его работы) имеет место за висание сигнала, т.е. сформирован импульс непредусмотренной дли;1Гельности, Целью предлагаемого изобретения является повышение достоверности контроля. Поставленная цельдостигается тем, что в устройство для контроля распределителя на Y вьгходов, содержащее первый и второй элементы И и ц первых элементов ИЛИ, причем первый вход каждого 1 первого элемента ИЛИ соединен с ( 1 +1)-м выходом распределителя второй вход каждого -j -го первого элемента ИЛИ, кроме первого, с выходом ( i -1)-го элемента ИЛИ, выход первого элемента ИЛИ соединен через первый инвертор с первым входом третьего элемента И, соединенного выходом с первым входом второго элемента ИЛИ, соединенного с выходом устройства, введены логический блок и второй шшертор, соединенный входом со входом устройства и со входом распределителя, выходом - с первым входом вто рого элемента И, соединенного выходом со вторым входом второго элемента ИЛИ третий вход KOTOpoix) подключен к выход первого элемента И, соединенного первы входом со вторым входом второго элемента И и с входом первого инвертора, вторым входом - с выходом логического блока, соединенного входами с соответ ствующкми выходами распределителя На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - временна диаграмма его работы. Устройство содержит распределитель 1 на И выходов, первый 2 и второй 3 элементы И, первые элементы ИЛИ 4, первый инвертор 5, третий элемент И 6 второй элемент ИЛИ 7, второй инвертор 8,-логический блок 9, вход 1О и выход .11, Устройство работает следующим обра зом. Ошибки в работе распределителя 1 выявляются в процессе его основной работы путем анализа импу-льсов, формирующихся на выходах распределителя 1 с помощью тактовых, шущульсов (ТИ), поступающих на вход 10. На временных диафрагмах фиг. 2 ука заны сигналы 1-1, 1-2, 1-3,- 1-4- на выходах распределителя 1 и сигналы 4, Q, 8, 2, 3, 9, 6, 7 и 10 соответственно на выходах блоков 4, 5, 8, 2, З, 9,6, 7 и на входе 10. Поступая на вход 1О, ТИ формируют на выходах 1-1 - 1-4 распредеяителя 1 и; шyльcы. При правильной работе распределителя 1 сигаал Сбой на выходе 11 не формируется, так казс элементы И2, ИЗ и И6 закрыты (фиг. 2, 1). Если в исходном состоянии после подачи сигнала Сброс импульсы ТИ на вход 10 не поступают и на какомлибо выходе распределителя 1, например на первом ( фиг . 211 ) присутствует сигнал, то он через последовательно соединенные элементы ИЛИ 4 поступает на вход элемента И 3, на другой вход которого с выхода инвертора 8 также .поступает высокий потенциал. В результате на выходе элемента И 3 по5тляет ся сигнал, которяй на выходе элемента ИЛИ 7 сформирует сигнал Сбой. При этом элементы И 2 и И 6 зажрыты, так как на вход элемента И 2 nocTjTiaeT низкий потенциал с выхода логического блока 9, а на входе И 6 отсутствует ТИ. Если на какоМ либо вькоде распреде- лнте.ля 1, nanpj.JMep на BTopoMs сформируется ймпульс непредусмотренной длительности (зависание выхода то, поступив на вход элемента И 3, он совпадает по времени с высоким потенциалом, который образуется на выходе инвертора 8,в моменты отсу1х;тБия ТИ на входе 1О и поступает на другчэй вход эпемента И 3 (фиг. 2, И} ), В результате формируется сигнал Сбой,, Логичесшй блок 9 вьщает на выходе единицу, если на двух и более его входах имеются едша;-чз-1ые сигналы, В процессе работы распределителя возмолша ситуаций, когда выходные сигналы появляются одновременно на нескаш KIDC выходах. распределител.я 1, например на втором и третьем (фиг. 2 W ). В этом на выходе логического блока 9пояБляе.1х:я сигнал, который по времени совпадает с с.1Егналом с элемента ИЯ1-1 4. Поэтому на выходе элемента И 2 появляется сигнала, который на выходе элемента ИЛИ 7 с(5юрмирует ситнал ЪБОЙ. В этом случае, если в процессе работы распределителя 1 под действием ТИ на каком-либо выходе распределителя Ij JiarrpiCviep на втором, сигнал не сформировался (фиг. 2 V ), на выходе элемента ШШ 4 сигнал отсутствует, поэтому с выхода 1швертора 5 вьюокий потенциал поступит iia вход элемента И 6. Одновреме1шо на другой вход элемент И 6 поступит импульс ТИ. Совпадение по времени утшзалкых сигналов на элементе И 6 приведет к появленшсЗ на выходе элемента ИЛИ 7 сигнала CBOfL Таиш образом, введение блока 9, инвертора 8 и новых связей позволяет выявить наряду с неисправностью вида зависание ряд других неисправностей характерньух для практшси эксплуатации распределителей, что повышает достоверность кан-гропя, Формула изобретения Устройство для контроля распределителя на VI выходов, содержащее первый и второй элементы И и vi первых элементов ИЛИ, причем первый вход каждого 1 -го первого элемента ИЛИ соединен с -( j + 1)-м выходом распределителя, второй вход каждого -i -го первого элемента ИЛИ, кроме первого, соединен с выходом соответствующего ( i -1)-го первого элемента ИЛИ, выход ц -го первого элемента ИЛИ соединен через первый инвертор с первым входом третьего элемента И, соединенного выходом с первым входом второго элемента ИЛИ, соединенного выходом с выходом устройства, отличающееся тем, что, с целью повыщения достоверности конт рояя, в устройство введены лог1янеский блок и второй инвертор, соединенный вхо дом со входом устройства и со входом распределителя, вьгходом - с первым .входом второго элемента И, соединенного выходом со вторым входом второго элемента ИЛИ, третий вход которого подключен к выходу первого элемента И, соединенного первым входом со вторым входом второго элемента Икс входом первого инвертора, вторым входом - с выходом логического блока, соединенного входами с соответствующими выходами распределителя. -Источники информагога, принятые во внимание при экспертизе 1.Путшщев Н. Д. Аппаратный конт роль управляющих вычислительных машин. М., Советское радио, 1966, с. 332. 2.Авторское свидетельство СССР № 754366, кл. G 05 В 9/02, 197Я (прототип).

Авторы

Даты

1982-12-15—Публикация

1981-06-04—Подача